JP2011233783A - 半導体発光素子、半導体発光素子の保護膜及びその作製方法 - Google Patents

半導体発光素子、半導体発光素子の保護膜及びその作製方法 Download PDFInfo

- Publication number

- JP2011233783A JP2011233783A JP2010104442A JP2010104442A JP2011233783A JP 2011233783 A JP2011233783 A JP 2011233783A JP 2010104442 A JP2010104442 A JP 2010104442A JP 2010104442 A JP2010104442 A JP 2010104442A JP 2011233783 A JP2011233783 A JP 2011233783A

- Authority

- JP

- Japan

- Prior art keywords

- film

- protective film

- semiconductor light

- sin

- emitting device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 104

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 26

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims abstract description 11

- 229910052581 Si3N4 Inorganic materials 0.000 claims abstract description 10

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims abstract description 10

- 229910052814 silicon oxide Inorganic materials 0.000 claims abstract description 10

- 239000000758 substrate Substances 0.000 claims abstract description 9

- 230000001681 protective effect Effects 0.000 claims description 120

- 238000000034 method Methods 0.000 claims description 15

- 229910052751 metal Inorganic materials 0.000 claims description 9

- 239000002184 metal Substances 0.000 claims description 9

- 229910008051 Si-OH Inorganic materials 0.000 claims description 7

- 229910006358 Si—OH Inorganic materials 0.000 claims description 7

- 229910052709 silver Inorganic materials 0.000 claims description 5

- 239000004332 silver Substances 0.000 claims description 4

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 abstract description 65

- 238000002834 transmittance Methods 0.000 abstract description 38

- 238000013508 migration Methods 0.000 abstract description 28

- 239000010410 layer Substances 0.000 description 67

- 230000005012 migration Effects 0.000 description 27

- 230000015572 biosynthetic process Effects 0.000 description 13

- 230000002265 prevention Effects 0.000 description 13

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 9

- 238000005530 etching Methods 0.000 description 7

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 7

- 238000000605 extraction Methods 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- 238000001771 vacuum deposition Methods 0.000 description 5

- 238000003475 lamination Methods 0.000 description 4

- 239000000463 material Substances 0.000 description 3

- 230000003405 preventing effect Effects 0.000 description 3

- 238000004458 analytical method Methods 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- FQMNUIZEFUVPNU-UHFFFAOYSA-N cobalt iron Chemical compound [Fe].[Co].[Co] FQMNUIZEFUVPNU-UHFFFAOYSA-N 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000003795 desorption Methods 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- XZWYZXLIPXDOLR-UHFFFAOYSA-N metformin Chemical compound CN(C)C(=N)NC(N)=N XZWYZXLIPXDOLR-UHFFFAOYSA-N 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000004611 spectroscopical analysis Methods 0.000 description 1

- 238000000927 vapour-phase epitaxy Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/44—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the coatings, e.g. passivation layer or anti-reflective coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/49105—Connecting at different heights

- H01L2224/49107—Connecting at different heights on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2933/00—Details relating to devices covered by the group H01L33/00 but not provided for in its subgroups

- H01L2933/0008—Processes

- H01L2933/0025—Processes relating to coatings

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/24—Structurally defined web or sheet [e.g., overall dimension, etc.]

- Y10T428/24942—Structurally defined web or sheet [e.g., overall dimension, etc.] including components having same physical characteristic in differing degree

- Y10T428/2495—Thickness [relative or absolute]

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/24—Structurally defined web or sheet [e.g., overall dimension, etc.]

- Y10T428/24942—Structurally defined web or sheet [e.g., overall dimension, etc.] including components having same physical characteristic in differing degree

- Y10T428/2495—Thickness [relative or absolute]

- Y10T428/24967—Absolute thicknesses specified

- Y10T428/24975—No layer or component greater than 5 mils thick

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Led Devices (AREA)

Abstract

【課題】高いマイグレーション防止性、高い透過率、低い成膜コストの全てを満たす半導体発光素子、半導体発光素子の保護膜及びその作製方法を提供する。

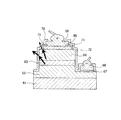

【解決手段】基板11上に形成された複数の半導体層12〜14と、複数の半導体層12〜14の電極となる電極部15、16及び電極部17、18とを有する半導体発光素子において、その保護膜として、複数の半導体層12〜14、電極部15、16及び電極部17、18の周囲を膜厚35nm以上の窒化珪素からなるSiN膜31で被覆し、SiN膜31の周囲をSiN膜31の膜厚より厚い酸化珪素からなるSiO膜32で被覆する。

【選択図】図1

【解決手段】基板11上に形成された複数の半導体層12〜14と、複数の半導体層12〜14の電極となる電極部15、16及び電極部17、18とを有する半導体発光素子において、その保護膜として、複数の半導体層12〜14、電極部15、16及び電極部17、18の周囲を膜厚35nm以上の窒化珪素からなるSiN膜31で被覆し、SiN膜31の周囲をSiN膜31の膜厚より厚い酸化珪素からなるSiO膜32で被覆する。

【選択図】図1

Description

本発明は、半導体発光素子、半導体発光素子の保護膜及びその作製方法に関する。

半導体発光素子として、省エネで長寿命を実現できる白色LED(Light Emitting Diode)は、新しい屋内・屋外照明材料として期待されている。

現在、省エネと長寿命を両立できる白色LEDは、省電力タイプに限られている。そのため、低消費電力で長寿命なメリットを生かしつつ、既存照明の置き換えをするには、低出力のLEDチップを複数個使用しなければならず、コストが高くなる原因となっていた。

照明の使用LEDチップ数を減らすには、1チップあたりの光出力を上げる必要がある。しかしながら、素子に大電力を投入すると、電極部に用いられているAgのマイグレーションが加速され、短絡が発生しやすくなり、素子の信頼性が低下する。よって、高出力素子で信頼性を得るためには、Agのマイグレーションを抑制する必要がある。

Agは水分と反応することでマイグレーションが加速するので、Agを水分から守る保護膜をLED素子に用いると、マイグレーションが抑制でき、高出力素子の信頼性改善に有効である。一方、この保護膜には、素子内で発生した光を効率よく素子外部まで取り出せるように、高い光透過性が求められる。

ここで、従来例1として、特許文献1のLED素子構造を図5に示して、その問題点を説明する。なお、図5中、符号61は基板、62はn型半導体層、63は活性層、64はp型半導体層、65はp電極、66はpパッド、67はn電極、68はnパッド、71はSiN膜、72はSiO膜である。このp電極65は、Ag/Ni/Ptからなる多層構造である。又、図中の矢印は、透過光の様子を示している。

図5に示す従来のLED素子構造においては、保護膜として、防水性の高いSiN膜71をp電極65の周辺部にのみ用い、その後、全体にSiO膜72を成膜している。上記素子構造においては、SiN膜71をp電極65の周辺部のみ形成するため、SiO膜72を成膜する前に、全体についたSiN71膜を一部除去する工程が必要となり、成膜コストが高くなる。又、p電極65中のAgが半導体側面まで拡散した場合、SiO膜72では防水性が低いため、マイグレーションが進行し易い。又、一般的に、SiN膜71はSiO膜72より光の透過率が低いため、p電極65の周辺で透過率が低くなり、外部への光取出し効率が低下する。

又、従来例2として、特許文献2のLED素子構造を図6に示して、その問題点を説明する。なお、図6において、図5と同等の構成については同じ符号を付す。又、図中の矢印は、透過光の様子を示している。但し、符号81はSiN膜である。

図6に示す従来のLED素子構造においては、保護膜として、素子全体に防水性の高いSiN膜81を用いている。上記素子構造においては、素子全体が透過率の低いSiN膜81で覆われているため、素子から外部への光取出し効率が低下する。又、SiN膜81は、一般的に、SiO膜よりも絶縁耐圧が低いため、絶縁性を確保するには膜厚を厚くする必要があり、成膜に時間がかかり成膜コストが高くなる。

このように、従来のLED素子構造においては、高いマイグレーション防止性、高い透過率、低い成膜コストの全てを満たすことが困難であり、高輝度構造の実現には課題があった。

本発明は上記課題に鑑みなされたもので、高いマイグレーション防止性、高い透過率、低い成膜コストの全てを満たす半導体発光素子、半導体発光素子の保護膜及びその作製方法を提供することを目的とする。

上記課題を解決する第1の発明に係る半導体発光素子の保護膜は、

基板上に形成された複数の半導体層と、前記複数の半導体層の電極となる複数の電極部とを有する半導体発光素子において、当該半導体発光素子を保護する保護膜であって、

前記保護膜として、前記複数の半導体層及び前記複数の電極部の周囲を被覆する第1の保護膜と、前記第1の保護膜の周囲を被覆する第2の保護膜とを設けると共に、

前記第1の保護膜を、膜厚35nm以上の窒化珪素とし、

前記第2の保護膜を、前記第1の保護膜の膜厚より厚い酸化珪素としたことを特徴とする。

基板上に形成された複数の半導体層と、前記複数の半導体層の電極となる複数の電極部とを有する半導体発光素子において、当該半導体発光素子を保護する保護膜であって、

前記保護膜として、前記複数の半導体層及び前記複数の電極部の周囲を被覆する第1の保護膜と、前記第1の保護膜の周囲を被覆する第2の保護膜とを設けると共に、

前記第1の保護膜を、膜厚35nm以上の窒化珪素とし、

前記第2の保護膜を、前記第1の保護膜の膜厚より厚い酸化珪素としたことを特徴とする。

上記課題を解決する第2の発明に係る半導体発光素子の保護膜は、

上記第1の発明に記載の半導体発光素子の保護膜において、

更に、前記第2の保護膜の周囲を被覆する第3の保護膜を設けると共に、

前記第3の保護膜を、膜厚35nm以上の窒化珪素としたことを特徴とする。

上記第1の発明に記載の半導体発光素子の保護膜において、

更に、前記第2の保護膜の周囲を被覆する第3の保護膜を設けると共に、

前記第3の保護膜を、膜厚35nm以上の窒化珪素としたことを特徴とする。

上記課題を解決する第3の発明に係る半導体発光素子の保護膜は、

上記第2の発明に記載の半導体発光素子の保護膜において、

前記第2の保護膜を、膜中のSi−OH結合量が1.3×1021[個/cm3]以下の酸化珪素とすると共に、当該場合の前記第1の保護膜の膜厚を、17.5nm以上としたことを特徴とする。

上記第2の発明に記載の半導体発光素子の保護膜において、

前記第2の保護膜を、膜中のSi−OH結合量が1.3×1021[個/cm3]以下の酸化珪素とすると共に、当該場合の前記第1の保護膜の膜厚を、17.5nm以上としたことを特徴とする。

上記課題を解決する第4の発明に係る半導体発光素子の保護膜は、

上記第1〜第3のいずれか1つの発明に記載の半導体発光素子の保護膜において、

前記複数の電極部の少なくとも1つが銀を含有する金属からなることを特徴とする。

上記第1〜第3のいずれか1つの発明に記載の半導体発光素子の保護膜において、

前記複数の電極部の少なくとも1つが銀を含有する金属からなることを特徴とする。

上記課題を解決する第5の発明に係る半導体発光素子は、

上記第1〜第4のいずれか1つの発明に記載の半導体発光素子の保護膜を用いたことを特徴とする。

上記第1〜第4のいずれか1つの発明に記載の半導体発光素子の保護膜を用いたことを特徴とする。

上記課題を解決する第6の発明に係る半導体発光素子の保護膜の作製方法は、

基板上に形成された複数の半導体層と、前記複数の半導体層の電極となる複数の電極部とを有する半導体発光素子において、当該半導体発光素子を保護する保護膜の作製方法であって、

前記保護膜として、前記複数の半導体層及び前記複数の電極部の周囲を被覆する第1の保護膜と、前記第1の保護膜の周囲を被覆する第2の保護膜とを設け、

前記第1の保護膜を、膜厚35nm以上の窒化珪素から形成し、

前記第2の保護膜を、前記第1の保護膜の膜厚より厚い酸化珪素から形成することを特徴とする。

基板上に形成された複数の半導体層と、前記複数の半導体層の電極となる複数の電極部とを有する半導体発光素子において、当該半導体発光素子を保護する保護膜の作製方法であって、

前記保護膜として、前記複数の半導体層及び前記複数の電極部の周囲を被覆する第1の保護膜と、前記第1の保護膜の周囲を被覆する第2の保護膜とを設け、

前記第1の保護膜を、膜厚35nm以上の窒化珪素から形成し、

前記第2の保護膜を、前記第1の保護膜の膜厚より厚い酸化珪素から形成することを特徴とする。

上記課題を解決する第7の発明に係る半導体発光素子の保護膜の作製方法は、

上記第6の発明に記載の半導体発光素子の製造方法において、

更に、前記第2の保護膜の周囲を被覆する第3の保護膜を設け、膜厚35nm以上の窒化珪素から形成することを特徴とする。

上記第6の発明に記載の半導体発光素子の製造方法において、

更に、前記第2の保護膜の周囲を被覆する第3の保護膜を設け、膜厚35nm以上の窒化珪素から形成することを特徴とする。

上記課題を解決する第8の発明に係る半導体発光素子の保護膜の作製方法は、

上記第7の発明に記載の半導体発光素子の製造方法において、

前記第2の保護膜を、膜中のSi−OH結合量が1.3×1021[個/cm3]以下の酸化珪素から形成すると共に、当該場合の前記第1の保護膜の膜厚を、17.5nm以上とすることを特徴とする。

上記第7の発明に記載の半導体発光素子の製造方法において、

前記第2の保護膜を、膜中のSi−OH結合量が1.3×1021[個/cm3]以下の酸化珪素から形成すると共に、当該場合の前記第1の保護膜の膜厚を、17.5nm以上とすることを特徴とする。

上記課題を解決する第9の発明に係る半導体発光素子の保護膜の作製方法は、

上記第6〜第8のいずれか1つの発明に記載の半導体発光素子の製造方法において、

前記複数の電極部の少なくとも1つが銀を含有する金属からなることを特徴とする。

上記第6〜第8のいずれか1つの発明に記載の半導体発光素子の製造方法において、

前記複数の電極部の少なくとも1つが銀を含有する金属からなることを特徴とする。

本発明によれば、半導体発光素子において、高いマイグレーション防止性、高い透過率、低い成膜コストの全てを満たすことができ、高輝度構造が実現する。

以下、本発明に係る半導体発光素子、半導体発光素子の保護膜及びその作製方法について、その実施形態のいくつかを図1〜図4を参照して説明する。なお、以下に示す実施例では、半導体発光素子としてLEDを用いた例について説明する。

(実施例1)

図1は、本実施例のLEDの素子構造を示す断面図である。図中の矢印は、透過光の様子を示している。又、図2は、後述するSiN膜における防水性と膜厚との関係を示すグラフである。

図1は、本実施例のLEDの素子構造を示す断面図である。図中の矢印は、透過光の様子を示している。又、図2は、後述するSiN膜における防水性と膜厚との関係を示すグラフである。

本実施例のLEDは、サファイアからなる基板11上に、n型GaNからなるn型半導体層12、GaNとInGaNを交互に積層した多重量子井戸構造からなる活性層13、p型GaNからなるp型半導体層14が順次積層された半導体層の素子構造である。なお、n型半導体層12、p型半導体層14は、各々、n型コンタクト層、p型コンタクト層を含む構造となっている。

そして、積層されたp型半導体層14、活性層13及びn型半導体層12の一部を、エッチングにより除去することにより、n型半導体層12のn型コンタクト層を露出し、その露出した部分に、半導体層側からW/Ptを順次積層して、n電極17を形成する。一方、p型半導体層14のp型コンタクト層の上面には、半導体層側からAg/Ni/Pt順次積層して、p電極15を形成している。又、バンプ形成のため、p電極15上には、Auからなるpパッド16を形成し、n電極17上には、Auからなるnパッド18を形成している。このように、p電極15及びpパッド16、そして、n電極17及びnパッド18を、各々、積層した半導体層に対する電極部としている。

上述した素子構造において、pパッド16及びnパッド18におけるバンプのための開口部を除き、半導体層(n型半導体層12、活性層13及びp型半導体層14)及び電極部(p電極15及びpパッド16、n電極17及びnパッド18)の周囲を被覆するように、絶縁性を有するSiNからなるSiN膜31(第1の保護膜)を積層し、次に、SiN膜31の周囲を被覆するように、絶縁性を有するSiOからなるSiO膜32(第2の保護膜)を積層している。つまり、第1層目をSiN膜31、第2層目をSiO膜32とした2層構造の保護膜を形成している。このように、Agを含有するp電極15の周囲だけでなく、素子全体の周囲を、SiN膜31及びSiO膜32の2層構造により保護する構造となる。

これらのSiN膜31、SiO膜32は、プラズマCVD法で形成されており、特に、高密度プラズマを用いたプラズマCVD法(装置)が好適である。なお、同様のSiN膜、SiO膜を形成できれば、他の方法、例えば、スパッタリング法(装置)、真空蒸着法(装置)等を用いることもできる。

前述したように、SiNからなる保護膜は、防水性は高いが、透過率が低く、絶縁耐圧が劣るという問題がある。

そこで、本実施例においては、SiN膜31を、防水性を保てる膜厚とすると共に、このSiN膜31の外側に、防水性は劣るが、透過率が高く、絶縁耐圧が高いSiO膜32を積層する構造としている。

ここで、図2のグラフを参照して、SiN膜31における防水性と膜厚の関係を説明する。なお、図2における防水性とは、サンプルとして、コバルト−鉄の膜上に、評価対象のSiN膜、膜中水分量の多いSiO膜を順次形成し、形成したサンプルにおいて、コバルト−鉄の磁化劣化を測定することで、評価対象のSiN膜の防水性を評価したものである。ここでは、プラズマCVD法により形成したSiN膜を評価した。

図2のグラフに示すように、SiN膜の膜厚が35nm未満の場合は、膜厚が薄くなるに従って、防水性が低下しているが、SiN膜の膜厚が35nm以上の場合は、防水性が良好であることがわかる。従って、本実施例では、SiN膜31の膜厚を、防水性が得られる35nm以上としている。

又、SiO膜32は、SiN膜31との合計の膜厚が、素子を物理的に保護可能な膜厚、つまり、素子の半導体層に傷をつけさせない膜厚としている。具体的には、合計の膜厚を、一般的なLEDで使用されている400〜1000nmとしている。このとき、SiO膜32の膜厚は、SiN膜31の膜厚より厚くしている。

上記素子構造においては、ごく一部(パッド開口部)を除き、素子全体がSiN膜31に覆われているので、素子の側壁において、内部への水分の侵入を防いで、p電極15中のAgのマイグレーションを抑制することができ、高いマイグレーション防止性が得られる。又、SiN膜31の膜厚を厚くする必要もなく、そのエッチングも不要であるので、成膜コストを抑えることができる。

マイグレーション防止性、透過率、成膜コスト及び高輝度構造の実現性について、前述した従来例1、従来例2と比較すると、表1に示すようになる。なお、表1においては、後述する実施例2、実施例3も併記している。

表1に示すように、本実施例におけるマイグレーション防止性は、素子全体がSiN膜31に覆われているので、従来例1より高く、素子の信頼性が向上する。

又、本実施例における透過率は、膜厚500nm、光の波長350nmの条件で比較した場合(本実施例のSiN膜31の膜厚は35nm、その透過率90%)、その保護膜全体の透過率は99.3%である。これは、従来例2より高く、従来例1と略同等であり(p電極付近の透過率も考慮した場合)、光取出し効率が改善する。

又、本実施例における成膜コストは、SiO膜32の積層により、絶縁耐圧が高く、保護膜全体の厚みを薄くできるので、エッチング工程が必要な従来例1や膜厚が厚くなる従来例2より、低くなっている。

このように、本実施例では、高いマイグレーション防止性と高い透過率、そして、低い成膜コストの全てをみたすことが可能となり、高輝度構造の実現性が従来と比べ向上した。

(実施例2)

図3は、本実施例のLEDの素子構造を示す断面図である。なお、図3において、実施例1(図1参照)で示した構成と同等の構成については同じ符号を付し、重複する説明は省略する。又、図中の矢印は、透過光の様子を示している。

図3は、本実施例のLEDの素子構造を示す断面図である。なお、図3において、実施例1(図1参照)で示した構成と同等の構成については同じ符号を付し、重複する説明は省略する。又、図中の矢印は、透過光の様子を示している。

本実施例のLEDは、半導体層の素子構造は、実施例1(図1参照)で示したLEDと同等の構成である。又、実施例1と同様に、pパッド16及びnパッド18におけるバンプのための開口部を除き、半導体層及び電極部の周囲を被覆するように、保護膜を形成しているが、この保護膜の構成が、実施例1とは相違する。

具体的には、保護膜として、絶縁性を有するSiNからなるSiN膜41(第1の保護膜)と、絶縁性を有するSiOからなるSiO膜42(第2の保護膜)と、絶縁性を有するSiNからなるSiN膜43(第3の保護膜)とを順次積層している。つまり、第1層目をSiN膜41、第2層目をSiO膜42、第3層目をSiN膜43とした3層構造の保護膜を形成している。このように、Agを含有するp電極15の周囲だけでなく、素子全体の周囲を、SiN膜41、SiO膜42及びSiN膜43の3層構造により保護する構造となる。

これらのSiN膜41、SiO膜42及びSiN膜43は、プラズマCVD法で形成されており、特に、高密度プラズマを用いたプラズマCVD法(装置)が好適である。なお、同様のSiN膜、SiO膜を形成できれば、他の方法、例えば、スパッタリング法(装置)、真空蒸着法(装置)等を用いることもできる。

前述したように、SiNからなる保護膜は、防水性は高いが、透過率が低く、絶縁耐圧が劣るという問題がある。又、SiOからなる保護膜は、元々水を通しやすく、更に、保持もしやすいため、膜中に一度水分を多く含むと、水分の供給源となり、その内側にSiNからなる保護膜を形成しても、その膜厚が薄いと、僅かではあるが、保護膜を透過して、素子側に水が浸入する問題がある。

そこで、本実施例においては、図2で説明したように、SiN膜41を、防水性を保てる膜厚35nm以上とすると共に、このSiN膜41の外側に、防水性は劣るが、透過率が高く、絶縁耐圧が高いSiO膜42を積層し、更に、SiO膜42の外側に、防水性を保てる膜厚35nm以上のSiN膜43を積層する構造としている。

又、SiO膜42は、SiN膜41及びSiN膜43との合計の膜厚が、素子を物理的に保護可能な膜厚、つまり、素子の半導体層に傷をつけさせない膜厚としている。具体的には、合計の膜厚を、一般的なLEDで使用されている400〜1000nmとしている。このとき、SiO膜42の膜厚は、SiN膜41、43の膜厚より厚くしている。

上記素子構造においては、ごく一部(パッド開口部)を除き、素子全体がSiN膜41に覆われているので、素子の側壁において、内部への水分の侵入を防いで、p電極15中のAgのマイグレーションを抑制することができ、高いマイグレーション防止性が得られる。更に、本実施例の場合、SiO膜42の外側に更にSiN膜43を設けているので、保護膜内部、特に、SiO膜42の内部に侵入する水分を低減することができ、そのため、素子側に侵入する水分を低減することができる。その結果、実施例1に比べて、更に、マイグレーション防止性を向上させることができた。又、SiN膜41、43の膜厚を従来のように厚くする必要もなく、そのエッチングも不要であるので、成膜コストを抑えることができる。

そして、表1に示すように、本実施例におけるマイグレーション防止性は、従来例1より高く、又、実施例1よりも高く、素子の信頼性が更に向上する。

又、本実施例における透過率は、膜厚500nm、光の波長350nmの条件で比較した場合(本実施例のSiN膜41、43の膜厚は35nm、その透過率90%)、保護膜全体の透過率は98.5%である。この透過率は、実施例1より若干下がっているが、従来例2より高く、従来例1と略同等であり(p電極付近の透過率も考慮した場合)、光取出し効率が改善する。これは、実施例1と同様に、透過率の低いSiN膜41、43の膜厚が保護膜全体の膜厚に対し薄く、透過率の高いSiO膜42の膜厚が厚いため、保護膜全体で高い透過率を得ることができるからである。

又、本実施例における成膜コストは、SiN膜43を更に積層するので、実施例1よりは若干高くなるが、保護膜全体としては、SiO膜42の積層により、絶縁耐圧が高く、保護膜全体の厚みを薄くできるので、エッチング工程が必要な従来例1や膜厚が厚くなる従来例2より、低くなっている。

このように、本実施例では、高いマイグレーション防止性と高い透過率、そして、低い成膜コストの全てをみたすことが可能となり、高輝度構造の実現性が従来と比べ向上した。

(実施例3)

図4は、本実施例のLEDの素子構造を示す断面図である。なお、図4において、実施例1(図1参照)で示した構成と同等の構成については同じ符号を付し、重複する説明は省略する。又、図中の矢印は、透過光の様子を示している。

図4は、本実施例のLEDの素子構造を示す断面図である。なお、図4において、実施例1(図1参照)で示した構成と同等の構成については同じ符号を付し、重複する説明は省略する。又、図中の矢印は、透過光の様子を示している。

本実施例のLEDは、半導体層の素子構造は、実施例1(図1参照)で示したLEDと同等の構成である。又、実施例1と同様に、pパッド16及びnパッド18におけるバンプのための開口部を除き、半導体層及び電極部の周囲を被覆するように、保護膜を形成しているが、この保護膜の構成が、実施例1とは相違する。更に、実施例2とは、SiO膜の膜質が相違する。

具体的には、保護膜として、絶縁性を有するSiNからなるSiN膜51(第1の保護膜)と、絶縁性を有し、膜中水分量が少ないSiOからなるSiO膜52(第2の保護膜)と、絶縁性を有するSiNからなるSiN膜53(第3の保護膜)とを順次積層している。つまり、第1層目をSiN膜51、第2層目をSiO膜52、第3層目をSiN膜53とした3層構造の保護膜を形成している。このように、Agを含有するp電極15の周囲だけでなく、素子全体の周囲を、SiN膜51、SiO膜52及びSiN膜53の3層構造により保護する構造となる。

これらのSiN膜51、SiO膜52及びSiN膜53は、プラズマCVD法で形成されており、特に、高密度プラズマを用いたプラズマCVD法(装置)が好適である。なお、同様のSiN膜、SiO膜を形成できれば、他の方法、例えば、スパッタリング法(装置)、真空蒸着法(装置)等を用いることもできる。

前述したように、SiNからなる保護膜は、防水性は高いが、透過率が低く、絶縁耐圧が劣るという問題がある。又、SiOからなる保護膜は、元々水を通しやすく、更に、保持もしやすいため、膜中に一度水分を多く含むと、水分の供給源となり、その内側にSiNからなる保護膜を形成しても、その膜厚が薄いと、僅かではあるが、保護膜を透過して、半導体層側に水が浸入する問題がある。

そこで、本実施例においては、SiN膜51、SiO膜52及びSiN膜53の3層構造において、SiO膜52として、膜中水分量が少ないSiO膜を用いている。即ち、SiO膜として、Si−OH結合量(3738cm-1付近に発生するSi−OH結合のピーク面積から求めた)が、IR分析(赤外線分析)の測定により、1.3×1021[個/cm3]以下となる膜質とすれば、昇温脱離ガス分析(TDS:Thermal Desorption Spectroscopy)の測定でも、膜中の水分量は十分低い値を示す。下記表2に、実施例1、実施例2で用いた通常のSiO膜と本実施例で用いる低水分量のSiO膜との比較を示す。通常のSiO膜のSi−OH結合量及び水分量は、2.6×1021[個/cm3]であるのに対して、本実施例の低水分SiO膜では、共に、その1/2の量となっている。

実施例2においては、第3層にSiN膜43を設けているので、SiO膜42への外部からの水侵入はほとんどなくなったが、SiO膜42はもともと水分を多く含むため、SiO膜42から素子側への水分拡散を防止する第1層のSiN膜41の膜厚を薄くすることができなかった。これに対して、表2に示すように、本実施例でのSiO膜の膜中水分量は、通常のSiO膜の1/2となるので、素子側への水分拡散を防止するSiN膜51を薄くすること、具体的には、図2で説明した防水性を保てる最低膜厚35nmを、その1/2である17.5nmとすることができ、これにより、実施例2より高い透過率を得ることができる。

そして、本実施例においても、SiN膜51の外側に透過率が高く、絶縁耐圧が高いSiO膜52を積層し、更に、SiO膜52の外側にSiN膜53を積層する3層構造としているが、SiO膜52の膜中水分量が少ないので、SiN膜51を、上述したように、膜厚17.5nm以上としている。更に、SiO膜52の外側に、図2で説明したように、防水性を保てる膜厚35nm以上のSiN膜53を積層する構造としている。

又、SiN膜51、SiO膜52及びSiN膜53との合計の膜厚が、素子を物理的に保護可能な膜厚、つまり、素子の半導体層に傷をつけさせない膜厚としており、具体的には、合計の膜厚を、一般的なLEDで使用されている400〜1000nmとしている。このとき、SiO膜52の膜厚は、SiN膜51、53の膜厚より厚くしている。

上記素子構造においては、ごく一部(パッド開口部)を除き、素子全体がSiN膜51に覆われているので、素子の側壁において、内部への水分の侵入を防いで、p電極15中のAgのマイグレーションを抑制することができ、高いマイグレーション防止性が得られる。本実施例の場合、SiN51の膜厚は、実施例2のSiN膜41より薄いが、上述したように、SiO膜52自体の膜中水分が少ないので、十分に高いマイグレーション防止性が得られる。更に、本実施例の場合、SiO膜52自体の膜中水分量が低く、その外側に更にSiN膜53を設けているので、保護膜内部、特に、SiO膜52の内部に侵入する水分を低減することができ、そのため、素子側に侵入する水分を低減することができる。その結果、実施例1に比べて、更に、マイグレーション防止性を向上させることができた。又、SiN膜51、53の膜厚を従来のように厚くする必要もなく、そのエッチングも不要であるので、成膜コストを抑えることができる。

そして、表1に示すように、本実施例におけるマイグレーション防止性は、従来例1より高く、又、実施例1よりも高く、素子の信頼性が更に向上する。

又、本実施例における透過率は、膜厚500nm、光の波長350nmの条件で比較した場合(本実施例のSiN膜51、53の膜厚は35nm、その透過率90%)、保護膜全体の透過率は98.9%である。この透過率は、実施例1より若干下がっているが、実施例2より若干高く、又、従来例2より高く、従来例1と略同等であり(p電極付近の透過率も考慮した場合)、光取出し効率が改善する。これは、実施例1、2と同様に、透過率の低いSiN膜51、53の膜厚が保護膜全体の膜厚に対し薄く、透過率の高いSiO膜52の膜厚が厚いため、保護膜全体で高い透過率を得ることができるからである。

又、本実施例における成膜コストは、SiN膜53を更に積層するので、実施例1よりは若干高くなるが、SiN膜51の膜厚が薄いので、実施例2よりは若干低い。保護膜全体としては、SiO膜52の積層により、絶縁耐圧が高く、保護膜全体の厚みを薄くできるので、エッチング工程が必要な従来例1や膜厚が厚くなる従来例2より、低くなっている。

このように、本実施例では、高いマイグレーション防止性と高い透過率、そして、低い成膜コストの全てをみたすことが可能となり、高輝度構造の実現性が従来と比べ向上した。

なお、上記実施例1〜3において、LEDの半導体層の材料、構成は、上述した構成に限らず、他の材料、構成でもよい。例えば、各半導体層は、III族原子であるIn、Al、Ga等とV族原子であるNとからなる窒化物半導体等でもよい。又、活性層13は、多重量子井戸構造に限らず、単一の量子井戸構造や歪量子井戸構造等でもよい。又、基板11も、サファイア基板に限らず、GaN基板などでもよい。又、各半導体層の製造方法も、公知の製造方法、例えば、有機金属気相成長(MOVPE:Metal Organic Vapor Phase Epitaxy)や有機金属化学気相成長法(MOCVD:Metal Organic Chemical Vapor Deposition)等を用いることができる。

又、p電極15は多層構造となっているが、マイグレーションのおそれがあるAg、Cu等の金属を含んでいれば、Ni、Pt以外の他の金属を含む構成でもよい。又、その製造方法は、公知の製造方法、例えば、スパッタリング法や真空蒸着法等を用いることができ、積層後、例えば、リフトオフ法によって、所望のパターンに形成している。従来は、Ag等のマイグレーションを考慮して、Ag層等の上下の層を他の金属で構成する多層構造(サンドイッチ構造)とすることがあったが、上記実施例1〜3の保護膜で素子全体を覆っているので、このようなサンド構造を必ずしも採用しなくても、Ag等のマイグレーションを十分に抑制可能である。

又、pパッド16、n電極17、nパッド18は、単層構造又は多層構造となっており、その製造方法は、p電極15と同様に、公知の製造方法、例えば、スパッタリング法や真空蒸着法等を用いることができ、積層後、例えば、リフトオフ法によって、所望のパターンに形成している。

なお、窒化珪素は、代表的なものとして、Si3N4があり、その組成比に応じて、SixNyと表記することもあるが、ここでは表記を簡単にするため、SiNと記載した。同様に、酸化珪素は、代表的なものとして、SiO2があり、その組成比に応じて、SixOyと表記することもあるが、ここでは表記を簡単にするため、SiOと記載した。

本発明は、半導体発光素子に適用するものであり、特に、白色LEDに好適なものである。

11 基板

12 n型半導体層

13 活性層

14 p型半導体層

15 p電極(電極部)

16 pパッド(電極部)

17 n電極(電極部)

18 nパッド(電極部)

31、41、51 SiN膜(第1の保護膜)

32、42、52 SiO膜(第2の保護膜)

43、53 SiN膜(第3の保護膜)

12 n型半導体層

13 活性層

14 p型半導体層

15 p電極(電極部)

16 pパッド(電極部)

17 n電極(電極部)

18 nパッド(電極部)

31、41、51 SiN膜(第1の保護膜)

32、42、52 SiO膜(第2の保護膜)

43、53 SiN膜(第3の保護膜)

Claims (9)

- 基板上に形成された複数の半導体層と、前記複数の半導体層の電極となる複数の電極部とを有する半導体発光素子において、当該半導体発光素子を保護する保護膜であって、

前記保護膜として、前記複数の半導体層及び前記複数の電極部の周囲を被覆する第1の保護膜と、前記第1の保護膜の周囲を被覆する第2の保護膜とを設けると共に、

前記第1の保護膜を、膜厚35nm以上の窒化珪素とし、

前記第2の保護膜を、前記第1の保護膜の膜厚より厚い酸化珪素としたことを特徴とする半導体発光素子の保護膜。 - 請求項1に記載の半導体発光素子の保護膜において、

更に、前記第2の保護膜の周囲を被覆する第3の保護膜を設けると共に、

前記第3の保護膜を、膜厚35nm以上の窒化珪素としたことを特徴とする半導体発光素子の保護膜。 - 請求項2に記載の半導体発光素子の保護膜において、

前記第2の保護膜を、膜中のSi−OH結合量が1.3×1021[個/cm3]以下の酸化珪素とすると共に、当該場合の前記第1の保護膜の膜厚を、17.5nm以上としたことを特徴とする半導体発光素子の保護膜。 - 請求項1から請求項3のいずれか1つに記載の半導体発光素子の保護膜において、

前記複数の電極部の少なくとも1つが銀を含有する金属からなることを特徴とする半導体発光素子の保護膜。 - 請求項1から請求項4のいずれか1つに記載の半導体発光素子の保護膜を用いたことを特徴とする半導体発光素子。

- 基板上に形成された複数の半導体層と、前記複数の半導体層の電極となる複数の電極部とを有する半導体発光素子において、当該半導体発光素子を保護する保護膜の作製方法であって、

前記保護膜として、前記複数の半導体層及び前記複数の電極部の周囲を被覆する第1の保護膜と、前記第1の保護膜の周囲を被覆する第2の保護膜とを設け、

前記第1の保護膜を、膜厚35nm以上の窒化珪素から形成し、

前記第2の保護膜を、前記第1の保護膜の膜厚より厚い酸化珪素から形成することを特徴とする半導体発光素子の保護膜の作製方法。 - 請求項6に記載の半導体発光素子の保護膜の作製方法において、

更に、前記第2の保護膜の周囲を被覆する第3の保護膜を設け、膜厚35nm以上の窒化珪素から形成することを特徴とする半導体発光素子の保護膜の作製方法。 - 請求項7に記載の半導体発光素子の保護膜の作製方法において、

前記第2の保護膜を、膜中のSi−OH結合量が1.3×1021[個/cm3]以下の酸化珪素から形成すると共に、当該場合の前記第1の保護膜の膜厚を、17.5nm以上とすることを特徴とする半導体発光素子の保護膜の作製方法。 - 請求項6から請求項8のいずれか1つに記載の半導体発光素子の保護膜の作製方法において、

前記複数の電極部の少なくとも1つが銀を含有する金属からなることを特徴とする半導体発光素子の保護膜の作製方法。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010104442A JP2011233783A (ja) | 2010-04-28 | 2010-04-28 | 半導体発光素子、半導体発光素子の保護膜及びその作製方法 |

| US13/582,225 US20130049063A1 (en) | 2010-04-28 | 2011-02-10 | Semiconductor light-emitting element, protective film for semiconductor light-emitting element, and process for production of the protective film |

| PCT/JP2011/052813 WO2011135888A1 (ja) | 2010-04-28 | 2011-02-10 | 半導体発光素子、半導体発光素子の保護膜及びその作製方法 |

| KR1020127022724A KR20120120389A (ko) | 2010-04-28 | 2011-02-10 | 반도체 발광 소자, 반도체 발광 소자의 보호막 및 그 제작 방법 |

| EP11774673A EP2565945A1 (en) | 2010-04-28 | 2011-02-10 | Semiconductor light-emitting element, protective film for semiconductor light-emitting element, and process for production of the protective film |

| TW100105983A TW201228036A (en) | 2010-04-28 | 2011-02-23 | Semiconductor light-emitting device, protection film thereof, and its manufacturing method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010104442A JP2011233783A (ja) | 2010-04-28 | 2010-04-28 | 半導体発光素子、半導体発光素子の保護膜及びその作製方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011233783A true JP2011233783A (ja) | 2011-11-17 |

| JP2011233783A5 JP2011233783A5 (ja) | 2013-06-06 |

Family

ID=44861209

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010104442A Pending JP2011233783A (ja) | 2010-04-28 | 2010-04-28 | 半導体発光素子、半導体発光素子の保護膜及びその作製方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20130049063A1 (ja) |

| EP (1) | EP2565945A1 (ja) |

| JP (1) | JP2011233783A (ja) |

| KR (1) | KR20120120389A (ja) |

| TW (1) | TW201228036A (ja) |

| WO (1) | WO2011135888A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113284999A (zh) * | 2021-03-29 | 2021-08-20 | 华灿光电(苏州)有限公司 | 发光二极管芯片及其制备方法 |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5857786B2 (ja) * | 2012-02-21 | 2016-02-10 | 日亜化学工業株式会社 | 半導体発光素子の製造方法 |

| DE102016105056A1 (de) * | 2016-03-18 | 2017-09-21 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optoelektronischen Halbleiterchips und optoelektronischer Halbleiterchip |

| US10505072B2 (en) * | 2016-12-16 | 2019-12-10 | Nichia Corporation | Method for manufacturing light emitting element |

| DE102018101815A1 (de) | 2018-01-26 | 2019-08-01 | Osram Opto Semiconductors Gmbh | Optoelektronisches Halbleiterbauelement und Verfahren zur Herstellung eines optoelektronischen Halbleiterbauelements |

| JP6570702B1 (ja) | 2018-05-29 | 2019-09-04 | 日機装株式会社 | 半導体発光素子および半導体発光素子の製造方法 |

| CN109037407B (zh) * | 2018-08-03 | 2024-04-23 | 厦门乾照光电股份有限公司 | 半导体发光芯片及其制造方法 |

| JP7023899B2 (ja) * | 2019-07-29 | 2022-02-22 | 日機装株式会社 | 半導体発光素子 |

| CN114122084B (zh) * | 2021-11-09 | 2024-04-30 | 深圳市华星光电半导体显示技术有限公司 | 顶发射oled显示面板 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0856056A (ja) * | 1994-04-06 | 1996-02-27 | At & T Corp | SiO▲x▼層を含む製品及びその製品の作製法 |

| JP2001160650A (ja) * | 1999-09-24 | 2001-06-12 | Sanyo Electric Co Ltd | 半導体発光素子 |

| JP2005310937A (ja) * | 2004-04-20 | 2005-11-04 | Hitachi Cable Ltd | 発光ダイオードアレイ |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0622858B2 (en) * | 1993-04-28 | 2004-09-29 | Nichia Corporation | Gallium nitride-based III-V group compound semiconductor device and method of producing the same |

| JPH07240535A (ja) * | 1994-02-28 | 1995-09-12 | Kyocera Corp | 薄膜パターンの形成方法 |

| JP3292044B2 (ja) * | 1996-05-31 | 2002-06-17 | 豊田合成株式会社 | p伝導形3族窒化物半導体の電極パッド及びそれを有した素子及び素子の製造方法 |

| US6936859B1 (en) * | 1998-05-13 | 2005-08-30 | Toyoda Gosei Co., Ltd. | Light-emitting semiconductor device using group III nitride compound |

| US6711191B1 (en) * | 1999-03-04 | 2004-03-23 | Nichia Corporation | Nitride semiconductor laser device |

| US20020017652A1 (en) * | 2000-08-08 | 2002-02-14 | Stefan Illek | Semiconductor chip for optoelectronics |

| US6445007B1 (en) * | 2001-03-19 | 2002-09-03 | Uni Light Technology Inc. | Light emitting diodes with spreading and improving light emitting area |

| JP2003031840A (ja) * | 2001-07-11 | 2003-01-31 | Hitachi Cable Ltd | 発光ダイオードアレイ |

| US20030189215A1 (en) * | 2002-04-09 | 2003-10-09 | Jong-Lam Lee | Method of fabricating vertical structure leds |

| US6841802B2 (en) * | 2002-06-26 | 2005-01-11 | Oriol, Inc. | Thin film light emitting diode |

| JP3795007B2 (ja) * | 2002-11-27 | 2006-07-12 | 松下電器産業株式会社 | 半導体発光素子及びその製造方法 |

| US6744196B1 (en) * | 2002-12-11 | 2004-06-01 | Oriol, Inc. | Thin film LED |

| KR100593886B1 (ko) * | 2003-06-24 | 2006-07-03 | 삼성전기주식회사 | 질화갈륨계 반도체 발광소자의 제조방법 |

| WO2005008795A1 (en) * | 2003-07-18 | 2005-01-27 | Epivalley Co., Ltd. | Nitride semiconductor light emitting device |

| US7166483B2 (en) * | 2004-06-17 | 2007-01-23 | Tekcore Co., Ltd. | High brightness light-emitting device and manufacturing process of the light-emitting device |

| JP2006041403A (ja) | 2004-07-29 | 2006-02-09 | Nichia Chem Ind Ltd | 半導体発光素子 |

| JP2007189097A (ja) | 2006-01-13 | 2007-07-26 | Nichia Chem Ind Ltd | 半導体発光素子 |

| JP2007288089A (ja) * | 2006-04-20 | 2007-11-01 | Opnext Japan Inc | 光素子および光モジュール |

| JP4172515B2 (ja) * | 2006-10-18 | 2008-10-29 | ソニー株式会社 | 発光素子の製造方法 |

| TWI344709B (en) * | 2007-06-14 | 2011-07-01 | Epistar Corp | Light emitting device |

| JP5057398B2 (ja) * | 2008-08-05 | 2012-10-24 | シャープ株式会社 | 窒化物半導体発光素子およびその製造方法 |

| KR101081135B1 (ko) * | 2010-03-15 | 2011-11-07 | 엘지이노텍 주식회사 | 발광 소자, 발광 소자 제조방법 및 발광 소자 패키지 |

| JP2011233784A (ja) * | 2010-04-28 | 2011-11-17 | Mitsubishi Heavy Ind Ltd | 半導体発光素子、半導体発光素子の保護膜及びその作製方法 |

| TW201145614A (en) * | 2010-06-03 | 2011-12-16 | Toshiba Kk | Method for manufacturing light-emitting device and light-emitting device manufactured by the same |

-

2010

- 2010-04-28 JP JP2010104442A patent/JP2011233783A/ja active Pending

-

2011

- 2011-02-10 KR KR1020127022724A patent/KR20120120389A/ko not_active Application Discontinuation

- 2011-02-10 US US13/582,225 patent/US20130049063A1/en not_active Abandoned

- 2011-02-10 WO PCT/JP2011/052813 patent/WO2011135888A1/ja active Application Filing

- 2011-02-10 EP EP11774673A patent/EP2565945A1/en not_active Withdrawn

- 2011-02-23 TW TW100105983A patent/TW201228036A/zh unknown

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0856056A (ja) * | 1994-04-06 | 1996-02-27 | At & T Corp | SiO▲x▼層を含む製品及びその製品の作製法 |

| JP2001160650A (ja) * | 1999-09-24 | 2001-06-12 | Sanyo Electric Co Ltd | 半導体発光素子 |

| JP2005310937A (ja) * | 2004-04-20 | 2005-11-04 | Hitachi Cable Ltd | 発光ダイオードアレイ |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113284999A (zh) * | 2021-03-29 | 2021-08-20 | 华灿光电(苏州)有限公司 | 发光二极管芯片及其制备方法 |

| CN113284999B (zh) * | 2021-03-29 | 2022-06-14 | 华灿光电(苏州)有限公司 | 发光二极管芯片及其制备方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2565945A1 (en) | 2013-03-06 |

| TW201228036A (en) | 2012-07-01 |

| US20130049063A1 (en) | 2013-02-28 |

| WO2011135888A1 (ja) | 2011-11-03 |

| KR20120120389A (ko) | 2012-11-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| WO2011135888A1 (ja) | 半導体発光素子、半導体発光素子の保護膜及びその作製方法 | |

| JP5857786B2 (ja) | 半導体発光素子の製造方法 | |

| JP4999696B2 (ja) | GaN系化合物半導体発光素子及びその製造方法 | |

| EP2270881B1 (en) | Light-emitting element and a production method therefor | |

| US9099627B2 (en) | Method for producing group III nitride semiconductor light-emitting device | |

| US8373152B2 (en) | Light-emitting element and a production method therefor | |

| JP5246199B2 (ja) | Iii族窒化物半導体発光素子 | |

| US8673677B2 (en) | Method for producing group III nitride semiconductor light emitting element | |

| JP2006041403A (ja) | 半導体発光素子 | |

| WO2014045883A1 (ja) | Led素子及びその製造方法 | |

| JP2011086910A (ja) | 半導体発光素子 | |

| CN113782655A (zh) | 一种发光二极管及其制备方法 | |

| TW201034252A (en) | Light emitting device | |

| JP2007214569A (ja) | フリップチップ型の発光素子 | |

| JP5327976B2 (ja) | 半導体発光素子の製造方法 | |

| JP5541260B2 (ja) | Iii族窒化物半導体発光素子 | |

| KR101234376B1 (ko) | 반도체 발광 소자, 반도체 발광 소자의 보호막 및 그 제작 방법 | |

| JP2014045094A (ja) | 高透過率保護膜作製方法および半導体発光素子の製造方法 | |

| WO2011135889A1 (ja) | 半導体発光素子、半導体発光素子の保護膜及びその作製方法 | |

| TWI505502B (zh) | 發光二極體及其製造方法 | |

| JP2010109127A (ja) | 発光素子 | |

| JP2024115613A (ja) | 発光素子およびその製造方法 | |

| JP2024101429A (ja) | 発光素子 | |

| KR20130007027A (ko) | 광 추출 효율이 개선된 발광 소자 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130423 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130423 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130924 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140204 |