JP2010528491A - 絶縁された導電性接点を金属パッケージを貫通するように形成するプロセス - Google Patents

絶縁された導電性接点を金属パッケージを貫通するように形成するプロセス Download PDFInfo

- Publication number

- JP2010528491A JP2010528491A JP2010510407A JP2010510407A JP2010528491A JP 2010528491 A JP2010528491 A JP 2010528491A JP 2010510407 A JP2010510407 A JP 2010510407A JP 2010510407 A JP2010510407 A JP 2010510407A JP 2010528491 A JP2010528491 A JP 2010528491A

- Authority

- JP

- Japan

- Prior art keywords

- forming

- substrate

- conductive

- sidewall

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/44—Manufacturing insulated metal core circuits or other insulated electrically conductive core circuits

- H05K3/445—Manufacturing insulated metal core circuits or other insulated electrically conductive core circuits having insulated holes or insulated via connections through the metal core

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/22—Diffusion of impurity materials, e.g. doping materials, electrode materials, into or out of a semiconductor body, or between semiconductor regions; Interactions between two or more impurities; Redistribution of impurities

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K5/00—Casings, cabinets or drawers for electric apparatus

- H05K5/02—Details

- H05K5/0247—Electrical details of casings, e.g. terminals, passages for cables or wiring

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/05—Insulated conductive substrates, e.g. insulated metal substrate

- H05K1/053—Insulated conductive substrates, e.g. insulated metal substrate the metal substrate being covered by an inorganic insulating layer

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/01—Dielectrics

- H05K2201/0137—Materials

- H05K2201/0179—Thin film deposited insulating layer, e.g. inorganic layer for printed capacitor

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09581—Applying an insulating coating on the walls of holes

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/09827—Tapered, e.g. tapered hole, via or groove

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0315—Oxidising metal

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0323—Working metal substrate or core, e.g. by etching, deforming

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/10—Using electric, magnetic and electromagnetic fields; Using laser light

- H05K2203/107—Using laser light

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/4038—Through-connections; Vertical interconnect access [VIA] connections

- H05K3/4053—Through-connections; Vertical interconnect access [VIA] connections by thick-film techniques

- H05K3/4061—Through-connections; Vertical interconnect access [VIA] connections by thick-film techniques for via connections in inorganic insulating substrates

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/49155—Manufacturing circuit on or in base

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/49155—Manufacturing circuit on or in base

- Y10T29/49165—Manufacturing circuit on or in base by forming conductive walled aperture in base

Abstract

Description

電気絶縁層を形成する方法の一つの例が陽極酸化である。別の例が薄膜堆積法である。

一つの例では、ビアは、電気絶縁層を形成する前にクリーニングすることができる。

本発明のこれらの例、及び他の例は、以下に更に詳細に説明される。

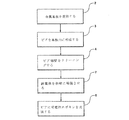

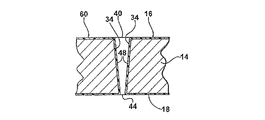

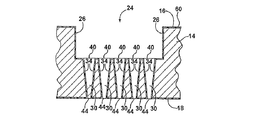

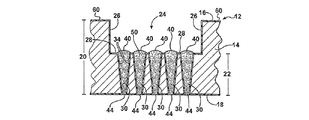

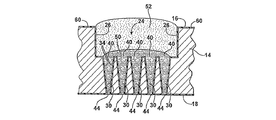

図2を参照すると、絶縁された電気接点を形成する別の例に関連する操作を表わす模式フローチャートが示される。操作2及び3は、図1に関して説明した操作と同じである。ビアを操作3で形成した後、操作4では、ビアの側壁を、従来の薄膜堆積プロセスをビア側壁に対して実行することができるようにクリーニングする。操作7では、ビアを誘電体で被覆する。誘電体をビア側壁に堆積させるために、多くの薄膜堆積技術のいずれの薄膜堆積技術を使用してもよい。例えば、化学気相成長法(CVD)を使用して、二酸化シリコン層をビア側壁に堆積させてもよい。操作6では、ビアに、図1に関して既に説明した導電材料を充填する。

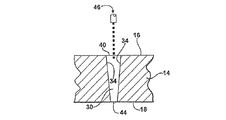

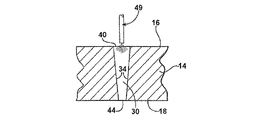

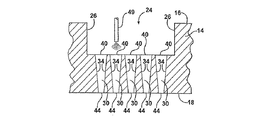

図3Bを参照すると、側壁34が陽極酸化される、又は誘電体材料で被覆される。図3Bでは、要素49は、操作4に関して説明したクリーニングに用いられるアプリケータ、及び操作7による堆積が行なわれるときの操作7の誘電体材料のアプリケータの両方を模式的に表わしている。

Claims (12)

- 電気的に絶縁された接点を金属基板内に形成する方法であって、

ビアを前記金属基板内に形成するステップであって、前記ビアが少なくとも一つの側壁を含む、前記ビアを形成するステップと、

誘電体スリーブを前記ビアの前記少なくとも一つの側壁に形成するステップと、

前記誘電体スリーブを形成した後に、前記ビアに導電材料を充填するステップと、

を含む、方法。 - 前記誘電体スリーブを形成する前に、前記ビアの前記少なくとも一つの側壁をエッチングプロセスでクリーニングするステップを更に含む、

請求項1に記載の方法。 - 前記誘電体スリーブは、陽極酸化又は化学気相成長法により形成される、請求項1又は請求項2に記載の方法。

- 前記基板はアルミニウムにより構成され、そして前記アルミニウムは、前記ビアを形成して前記誘電体スリーブを形成する前に陽極酸化される、請求項1乃至3のいずれかに記載の方法。

- 前記基板は、前記基板内に形成されるポケットを含み、前記ポケットは、少なくとも一つの側壁及び基部を含み、そして前記ビアは、前記ポケットの前記基部に形成される、請求項1乃至4のいずれかに記載の方法。

- 前記ポケットは導電材料で充填される、請求項5に記載の方法。

- 前記導電材料は、導電性インク、又は銀ナノ粒子液体導電性エポキシである、請求項1乃至6のいずれかに記載の方法。

- 前記ビアは、90〜200マイクロメートルの範囲の第1の直径を有する第1端部と、20〜50マイクロメートルの範囲の第2の直径を有する第2端部と、を含む、請求項1乃至7のいずれかに記載の方法。

- 前記ビアは、レーザドリル法により形成される、請求項1乃至8のいずれかに記載の方法。

- 電気的に絶縁された接点を有するハウジング部品であって、前記電気的に絶縁された接点の各接点が、請求項1乃至9のいずれかに記載の方法を使用して形成される、ハウジング部品。

- 前記複数の絶縁された電気接点を使用するアンテナの一部を含む、請求項10に記載のハウジング部品。

- 前記複数の電気的に絶縁された接点のうちの少なくとも一つの接点がオン/オフスイッチとして動作する、請求項10に記載のハウジング部品。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/753,996 US7886437B2 (en) | 2007-05-25 | 2007-05-25 | Process for forming an isolated electrically conductive contact through a metal package |

| PCT/US2008/063609 WO2008147695A1 (en) | 2007-05-25 | 2008-05-14 | Process for forming an isolated electrically conductive contact through a metal package |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014030950A Division JP2014143423A (ja) | 2007-05-25 | 2014-02-20 | コンシュマー電子機器パッケージ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010528491A true JP2010528491A (ja) | 2010-08-19 |

| JP2010528491A5 JP2010528491A5 (ja) | 2011-06-23 |

Family

ID=40071052

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010510407A Pending JP2010528491A (ja) | 2007-05-25 | 2008-05-14 | 絶縁された導電性接点を金属パッケージを貫通するように形成するプロセス |

| JP2014030950A Pending JP2014143423A (ja) | 2007-05-25 | 2014-02-20 | コンシュマー電子機器パッケージ |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014030950A Pending JP2014143423A (ja) | 2007-05-25 | 2014-02-20 | コンシュマー電子機器パッケージ |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US7886437B2 (ja) |

| JP (2) | JP2010528491A (ja) |

| KR (1) | KR20100023804A (ja) |

| CN (1) | CN101681818B (ja) |

| TW (1) | TWI435679B (ja) |

| WO (1) | WO2008147695A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9685414B2 (en) | 2013-06-26 | 2017-06-20 | Intel Corporation | Package assembly for embedded die and associated techniques and configurations |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7886437B2 (en) * | 2007-05-25 | 2011-02-15 | Electro Scientific Industries, Inc. | Process for forming an isolated electrically conductive contact through a metal package |

| US8220142B2 (en) * | 2007-10-03 | 2012-07-17 | Apple Inc. | Method of forming a housing component |

| US8687359B2 (en) * | 2008-10-13 | 2014-04-01 | Apple Inc. | Portable computer unified top case |

| KR20100045857A (ko) * | 2008-10-24 | 2010-05-04 | 삼성전자주식회사 | 반도체 칩, 스택 모듈, 메모리 카드 및 반도체 칩의 제조 방법 |

| CH704884B1 (fr) * | 2011-04-29 | 2015-04-30 | Suisse Electronique Microtech | Substrat destiné à recevoir des contacts électriques. |

| TWI454320B (zh) * | 2011-08-19 | 2014-10-01 | Jieng Tai Internat Electric Corp | 填補穿孔的方法 |

| JP2013045804A (ja) * | 2011-08-22 | 2013-03-04 | Shinko Electric Ind Co Ltd | 基材 |

| US8894868B2 (en) | 2011-10-06 | 2014-11-25 | Electro Scientific Industries, Inc. | Substrate containing aperture and methods of forming the same |

| CN104685456A (zh) | 2012-07-12 | 2015-06-03 | 伊雷克托科学工业股份有限公司 | 交互控制系统、其制造方法以及并入交互控制系统的装置 |

| WO2015076802A1 (en) * | 2013-11-21 | 2015-05-28 | Hewlett Packard Development Company, L.P. | Oxidized layer and light metal layer on substrate |

| KR102134296B1 (ko) | 2014-09-23 | 2020-07-15 | (주)포인트엔지니어링 | 안테나 |

| US10989640B2 (en) | 2015-03-24 | 2021-04-27 | Bell Helicopter Textron Inc. | Method for defining threshold stress curves utilized in fatigue and damage tolerance analysis |

| US10732085B2 (en) | 2015-03-24 | 2020-08-04 | Bell Helicopter Textron Inc. | Notch treatment methods for flaw simulation |

| CN107872936B (zh) | 2016-09-28 | 2020-10-23 | 华为机器有限公司 | 一种移动设备的金属壳及其制备方法、移动设备 |

| EP3428955A1 (en) * | 2017-07-10 | 2019-01-16 | Murata Manufacturing Co., Ltd. | Substrates employing surface-area amplification, for use in fabricating capacitive elements and other devices |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11503565A (ja) * | 1995-03-29 | 1999-03-26 | オリン コーポレイション | 集積回路装置を収容するための部品 |

| JP2003101177A (ja) * | 2001-09-25 | 2003-04-04 | Hitachi Aic Inc | メタルコア配線板とその製造方法、及び、かかるメタルコア配線板を利用した回路部品 |

Family Cites Families (51)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3296099A (en) * | 1966-05-16 | 1967-01-03 | Western Electric Co | Method of making printed circuits |

| US4155972A (en) | 1977-09-06 | 1979-05-22 | Keystone Consolidated Industries, Inc. | Multiple-shot method of molding plastic products |

| JPS59159595A (ja) * | 1983-03-03 | 1984-09-10 | オ−ケ−プリント配線株式会社 | 金属プリント基板の製造方法 |

| US5293025A (en) | 1991-08-01 | 1994-03-08 | E. I. Du Pont De Nemours And Company | Method for forming vias in multilayer circuits |

| JPH07201260A (ja) | 1993-12-29 | 1995-08-04 | Yamatake Honeywell Co Ltd | 電子スイッチの表示窓形成方法 |

| US5518964A (en) | 1994-07-07 | 1996-05-21 | Tessera, Inc. | Microelectronic mounting with multiple lead deformation and bonding |

| US5614114A (en) | 1994-07-18 | 1997-03-25 | Electro Scientific Industries, Inc. | Laser system and method for plating vias |

| US5593606A (en) | 1994-07-18 | 1997-01-14 | Electro Scientific Industries, Inc. | Ultraviolet laser system and method for forming vias in multi-layered targets |

| US5699613A (en) | 1995-09-25 | 1997-12-23 | International Business Machines Corporation | Fine dimension stacked vias for a multiple layer circuit board structure |

| US5757079A (en) | 1995-12-21 | 1998-05-26 | International Business Machines Corporation | Method for repairing defective electrical connections on multi-layer thin film (MLTF) electronic packages and the resulting MLTF structure |

| US6631558B2 (en) | 1996-06-05 | 2003-10-14 | Laservia Corporation | Blind via laser drilling system |

| WO1997046349A1 (en) | 1996-06-05 | 1997-12-11 | Burgess Larry W | Blind via laser drilling system |

| US5787578A (en) | 1996-07-09 | 1998-08-04 | International Business Machines Corporation | Method of selectively depositing a metallic layer on a ceramic substrate |

| US5718326A (en) | 1996-07-22 | 1998-02-17 | Delco Electronics Corporation | Backlit button/switchpad assembly |

| US6541709B1 (en) | 1996-11-01 | 2003-04-01 | International Business Machines Corporation | Inherently robust repair process for thin film circuitry using uv laser |

| WO1998020557A1 (en) | 1996-11-08 | 1998-05-14 | W.L. Gore & Associates, Inc. | Method for reducing via inductance in an electronic assembly and device |

| DE19717636A1 (de) | 1997-04-25 | 1998-11-12 | Trw Fahrzeugelektrik | Verfahren zur Herstellung eines Blendenteils, Betätigungsteils oder dergleichen Teile mit Funktionssymbolen für die Beleuchtung mit Durchlicht |

| JPH11298104A (ja) * | 1998-04-16 | 1999-10-29 | Sumitomo Metal Electronics Devices Inc | 半導体搭載用回路基板 |

| GB9811328D0 (en) | 1998-05-27 | 1998-07-22 | Exitech Ltd | The use of mid-infrared lasers for drilling microvia holes in printed circuit (wiring) boards and other electrical circuit interconnection packages |

| US6400018B2 (en) | 1998-08-27 | 2002-06-04 | 3M Innovative Properties Company | Via plug adapter |

| US6235544B1 (en) | 1999-04-20 | 2001-05-22 | International Business Machines Corporation | Seed metal delete process for thin film repair solutions using direct UV laser |

| JP2003511240A (ja) | 1999-09-30 | 2003-03-25 | シーメンス アクチエンゲゼルシヤフト | 積層体をレーザー穿孔する方法及び装置 |

| JP2001237512A (ja) * | 1999-12-14 | 2001-08-31 | Nitto Denko Corp | 両面回路基板およびこれを用いた多層配線基板ならびに両面回路基板の製造方法 |

| JP3330925B2 (ja) | 2000-04-05 | 2002-10-07 | 株式会社日鉱マテリアルズ | レーザー穴開け用銅箔 |

| DE10125397B4 (de) * | 2001-05-23 | 2005-03-03 | Siemens Ag | Verfahren zum Bohren von Mikrolöchern mit einem Laserstrahl |

| US20030066679A1 (en) | 2001-10-09 | 2003-04-10 | Castro Abram M. | Electrical circuit and method of formation |

| US6627844B2 (en) | 2001-11-30 | 2003-09-30 | Matsushita Electric Industrial Co., Ltd. | Method of laser milling |

| US6541712B1 (en) | 2001-12-04 | 2003-04-01 | Teradyhe, Inc. | High speed multi-layer printed circuit board via |

| US6863926B2 (en) * | 2002-01-15 | 2005-03-08 | David Mark Lynn | Corrosive-resistant coating over aluminum substrates for use in plasma deposition and etch environments |

| TW558823B (en) | 2002-04-10 | 2003-10-21 | Via Tech Inc | Through-hole process of integrated circuit substrate |

| US20040112881A1 (en) | 2002-04-11 | 2004-06-17 | Bloemeke Stephen Roger | Circle laser trepanning |

| TWI271131B (en) | 2002-04-23 | 2007-01-11 | Via Tech Inc | Pattern fabrication process of circuit substrate |

| TW561803B (en) | 2002-10-24 | 2003-11-11 | Advanced Semiconductor Eng | Circuit substrate and manufacturing method thereof |

| TW587322B (en) | 2002-12-31 | 2004-05-11 | Phoenix Prec Technology Corp | Substrate with stacked via and fine circuit thereon, and method for fabricating the same |

| US6867121B2 (en) | 2003-01-16 | 2005-03-15 | International Business Machines Corporation | Method of apparatus for interconnecting a relatively fine pitch circuit layer and adjacent power plane(s) in a laminated construction |

| US20050137942A1 (en) * | 2003-09-17 | 2005-06-23 | Lafleur Bernard B. | Rapid depolyment portable interactive kiosk |

| US7345350B2 (en) * | 2003-09-23 | 2008-03-18 | Micron Technology, Inc. | Process and integration scheme for fabricating conductive components, through-vias and semiconductor components including conductive through-wafer vias |

| US7402758B2 (en) | 2003-10-09 | 2008-07-22 | Qualcomm Incorporated | Telescoping blind via in three-layer core |

| US8084866B2 (en) * | 2003-12-10 | 2011-12-27 | Micron Technology, Inc. | Microelectronic devices and methods for filling vias in microelectronic devices |

| US7018219B2 (en) | 2004-02-25 | 2006-03-28 | Rosenau Steven A | Interconnect structure and method for connecting buried signal lines to electrical devices |

| US20050189656A1 (en) | 2004-02-26 | 2005-09-01 | Chun Yee Tan | Micro-vias for electronic packaging |

| US20060091023A1 (en) | 2004-10-28 | 2006-05-04 | Ahsan Bukhari | Assessing micro-via formation PCB substrate manufacturing process |

| KR100688768B1 (ko) * | 2004-12-30 | 2007-03-02 | 삼성전기주식회사 | 칩 내장형 인쇄회로기판 및 그 제조 방법 |

| US7884315B2 (en) | 2006-07-11 | 2011-02-08 | Apple Inc. | Invisible, light-transmissive display system |

| US7527872B2 (en) * | 2005-10-25 | 2009-05-05 | Goodrich Corporation | Treated aluminum article and method for making same |

| US20070275540A1 (en) * | 2006-05-24 | 2007-11-29 | Hackitt Dale A | Backside via formation prior to die attachment |

| US7968820B2 (en) * | 2006-06-02 | 2011-06-28 | Electro Scientific Industries, Inc. | Method of producing a panel having an area with light transmissivity |

| US8394301B2 (en) * | 2006-06-02 | 2013-03-12 | Electro Scientific Industries, Inc. | Process for forming panel with an optically transmissive portion and products related thereto |

| US7655292B2 (en) * | 2007-04-11 | 2010-02-02 | Kaylu Industrial Corporation | Electrically conductive substrate with high heat conductivity |

| US8134235B2 (en) * | 2007-04-23 | 2012-03-13 | Taiwan Semiconductor Manufacturing Co., Ltd. | Three-dimensional semiconductor device |

| US7886437B2 (en) * | 2007-05-25 | 2011-02-15 | Electro Scientific Industries, Inc. | Process for forming an isolated electrically conductive contact through a metal package |

-

2007

- 2007-05-25 US US11/753,996 patent/US7886437B2/en not_active Expired - Fee Related

-

2008

- 2008-05-14 KR KR1020097023952A patent/KR20100023804A/ko active IP Right Grant

- 2008-05-14 CN CN2008800165914A patent/CN101681818B/zh not_active Expired - Fee Related

- 2008-05-14 WO PCT/US2008/063609 patent/WO2008147695A1/en active Application Filing

- 2008-05-14 JP JP2010510407A patent/JP2010528491A/ja active Pending

- 2008-05-20 TW TW097118537A patent/TWI435679B/zh not_active IP Right Cessation

-

2011

- 2011-02-14 US US13/027,167 patent/US8117744B2/en not_active Expired - Fee Related

-

2014

- 2014-02-20 JP JP2014030950A patent/JP2014143423A/ja active Pending

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11503565A (ja) * | 1995-03-29 | 1999-03-26 | オリン コーポレイション | 集積回路装置を収容するための部品 |

| JP2003101177A (ja) * | 2001-09-25 | 2003-04-04 | Hitachi Aic Inc | メタルコア配線板とその製造方法、及び、かかるメタルコア配線板を利用した回路部品 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9685414B2 (en) | 2013-06-26 | 2017-06-20 | Intel Corporation | Package assembly for embedded die and associated techniques and configurations |

| US10014263B2 (en) | 2013-06-26 | 2018-07-03 | Intel Corporation | Package assembly for embedded die and associated techniques and configurations |

| US10304785B2 (en) | 2013-06-26 | 2019-05-28 | Intel Corporation | Package assembly for embedded die and associated techniques and configurations |

| US10522483B2 (en) | 2013-06-26 | 2019-12-31 | Intel Corporation | Package assembly for embedded die and associated techniques and configurations |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101681818B (zh) | 2011-11-23 |

| TW200913850A (en) | 2009-03-16 |

| KR20100023804A (ko) | 2010-03-04 |

| US20080289178A1 (en) | 2008-11-27 |

| CN101681818A (zh) | 2010-03-24 |

| US20110131807A1 (en) | 2011-06-09 |

| TWI435679B (zh) | 2014-04-21 |

| WO2008147695A1 (en) | 2008-12-04 |

| US8117744B2 (en) | 2012-02-21 |

| US7886437B2 (en) | 2011-02-15 |

| JP2014143423A (ja) | 2014-08-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2010528491A (ja) | 絶縁された導電性接点を金属パッケージを貫通するように形成するプロセス | |

| JP4996096B2 (ja) | 発光装置及びその製造方法 | |

| JP2010528491A5 (ja) | ||

| JP3779745B2 (ja) | プリント回路基板とフィルム回路基板の製造方法 | |

| CN106538079A (zh) | 印刷电路板的通孔 | |

| JP4199206B2 (ja) | 半導体装置の製造方法 | |

| TWI291382B (en) | Method of forming a metal thin film with micro holes by ink-jet printing | |

| JP2011056906A (ja) | 液体吐出ヘッドの製造方法 | |

| TWI292345B (en) | Substrate before insulation, method of manufacturing substrate, method of manufacturing surface acoustic wave transducer, surface acoustic wave device, and electronic equipment | |

| CN113784912B (zh) | 用于在玻璃基底中制造微结构的方法 | |

| JP5219612B2 (ja) | 半導体貫通電極形成方法 | |

| US20140014401A1 (en) | Circuit device and method for making the same | |

| JP2008265164A (ja) | インクジェット記録ヘッド用の基板およびその製造方法 | |

| Anwar et al. | Micropatterning polypyrrole conducting polymer by pulsed electrical discharge | |

| JP2008016507A (ja) | 電気配線の製造方法 | |

| KR20200033956A (ko) | 마이크로기계 장치 및 상응하는 제조 방법 | |

| JP2019059163A (ja) | 液体吐出ヘッド及びその製造方法 | |

| JP2012199404A (ja) | パターン修正方法 | |

| WO2021192502A1 (ja) | 基板処理方法および基板処理装置 | |

| US7033404B2 (en) | Method for producing an anti-wetting barrier, and anode comprising one such anti-wetting barrier | |

| JP2006229036A (ja) | 回路基板及び回路基板製造方法 | |

| JP2013256001A (ja) | マルチノズルプレート及びその製造方法並びに静電吐出型印刷装置 | |

| JP5773633B2 (ja) | 配線基板の製造方法 | |

| JP2010061832A (ja) | 誘電体シート、キャパシタおよび部品搭載基板 | |

| JP2004307924A (ja) | 電子部品のめっき方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110427 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110427 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121009 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20121228 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130110 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130131 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20131022 |