JP2010055730A - センスアンプ回路及び半導体記憶装置 - Google Patents

センスアンプ回路及び半導体記憶装置 Download PDFInfo

- Publication number

- JP2010055730A JP2010055730A JP2008222938A JP2008222938A JP2010055730A JP 2010055730 A JP2010055730 A JP 2010055730A JP 2008222938 A JP2008222938 A JP 2008222938A JP 2008222938 A JP2008222938 A JP 2008222938A JP 2010055730 A JP2010055730 A JP 2010055730A

- Authority

- JP

- Japan

- Prior art keywords

- mos transistor

- sense amplifier

- bit line

- potential

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4091—Sense or sense/refresh amplifiers, or associated sense circuitry, e.g. for coupled bit-line precharging, equalising or isolating

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4097—Bit-line organisation, e.g. bit-line layout, folded bit lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/002—Isolation gates, i.e. gates coupling bit lines to the sense amplifier

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Dram (AREA)

Abstract

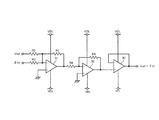

【解決手段】シングルエンド型のセンスアンプ回路は、制御電圧Vgに応じてビット線LBLとセンスノードNsとの接続を制御するMOSトランジスタQ1と、ゲートがセンスノードNsに接続されビット線LBLからMOSトランジスタQ1を介して伝送される信号を増幅するMOSトランジスタQ2と、制御信号PCLに応じてビット線LBLを第1の電位に設定する第1の電位設定回路(Q2)と、制御信号WTに応じてセンスノードNsを第2の電位に設定する第2の電位設定回路(Q5)とを備え、ビット線LBLを前記第1の電位に設定し、かつセンスノードNsを第2の電位に設定した後、MOSトランジスタQ1を介してビット線LBLを電荷分配モードで駆動してMOSトランジスタQ2の増幅動作が行われる。

【選択図】図3

Description

本実施形態のセンスアンプ回路に関し、基本的な動作原理について図1及び図2を参照して説明する。一般に、センスアンプ回路の基本的な動作モードとして、電荷転送モード(チャージトランスファモード)と電荷分配モード(チャージシェアモード)を想定することができる。図1は、電荷転送モード及び電荷分配モードで動作するセンスアンプ回路の入力側の構成を模式的に示す図である。図1においては、N型の選択トランジスタQ0及びキャパシタCsからなるメモリセルMCと、2つのN型のMOSトランジスタQg、Qpからなるセンスアンプ回路が示されている。

(1)MOSトランジスタQgがオフを保持

(2)MOSトランジスタQgを通して上述の電荷転送モードで電荷が移動

(3)MOSトランジスタQgを通して上述の電荷分配モードで電荷が移動

(式1)Vb≦Vs : Va=VDD

(式2)Vs<Vb≦Vc : Va=VDD+(Cs/Ca)Vs

−(Cs/Ca)Vb

(式3)Vc<Vb : Va=(CsVs+CaVDD)/(Cs+Cb+Ca)

+(Cb/(Cs+Cb+Ca))Vb

ただし、電圧Vcは次式で算出される。

Vc=((Cs+Cb)CaVDD)+(Cs+Cb)CsVs)

/(Cs(Cs+Cb+Ca)+CbCa)

Vb=(Cs/(Cs+Cb))Vs

と表される。この時点で、MOSトランジスタQgはオフ状態を保っている。そして、電荷分配モードによる動作が開始し、MOSトランジスタQgのゲートに制御電圧Vgが印加される、ここでMOSトランジスタQgの閾値電圧Vt1を用いて、電圧Vxを次式で定義する。

Vx=Vg−Vt1

この場合、Vb、Vx、VDDの各値の関係に応じて、上述した3つの動作(1)、(2)、(3)に分けることができる。そして、動作(2)と動作(3)の境界となる上記電圧Vcは、

Vc=(CsVs+CaVDD)/(Cs+Cb+Ca)

と表される。これにより、電荷分配モードによる動作を完了した後のセンスノードNsの電位Vaは、動作(1)、(2)、(3)に対応して、それぞれ以下に示す(式1´)、(式2´)、(式3´)のように表現される。

(式1´)Vx≦Vb : Va=VDD

(式2´)Vb<Vx≦Vc : Va=VDD+(Cs/Ca)Vs

−((Cs+Cb)/Ca)Vx

(式3´)Vc<Vx

: Va=(CsVs+CaVDD)/(Cs+Cb+Ca)

以下、本発明の第1実施形態について説明する。第1実施形態では、階層化されたメモリセルアレイが構成され、ビット線とセンスアンプ回路がともに階層化されたDRAMに対し、シングルエンド型の電荷分配制御型センスアンプ回路を適用したものである。図3は、第1実施形態のDRAMのうちセンス系の回路構成の一例を示す図であり、メモリセルMCと、階層化されたビット線としてのローカルビット線LBL(本発明のビット線)及びグローバルビット線GBLと、上述の電荷分配制御型センスアンプ回路としてのローカルセンスアンプ10と、グローバルセンスアンプ11とが示されている。

次に、本発明の第2実施形態について説明する。第2実施形態のDRAMは、第1実施形態と同様、ビット線とセンスアンプ回路が階層化され、概ね第1実施形態と同様に構成されるが、一部の電源系の構成が変更されている。第2実施形態では、MOSトランジスタQ1の閾値電圧Vt1の変動を補償した補償電圧発生回路と、MOSトランジスタQ3の閾値電圧Vt3の変動を補償した補償電圧発生回路を採用している。これらの具体的な構成については後述する。

11…グローバルセンスアンプ

11a…信号電圧判定ラッチ

30…閾値電圧モニタ部

31…レベル補正部

32…補償電圧加算部

40、43…定電流源

41、42、44、48、49、50、51、52、53…オペアンプ

45…セレクタ

46…タップ選択回路

47…ローパスフィルタ

WL…ワード線

BL…ビット線

GBL…グローバルビット線

LBL…ローカルビット線

MC…メモリセル

Q0…選択トランジスタ

Cs…キャパシタ

Q1〜Q20、Q30、Qg、Qp…MOSトランジスタ

Q1r、Q3r…レプリカMOSトランジスタ

PC、PCR、PCL…プリチャージ信号

/PC…反転プリチャージ信号

SET、RT、WT、RES、CTL、CTR、SHL、SHR…制御信号

WE…書き込みイネーブル信号

LTC…ラッチ制御信号

SD…出力信号

YS…センスアンプ選択信号

/RDL…読み出し信号線

/WDL…書き込み信号線

Va…センスノードの電位

Vb…ビット線の電位

Vg…制御電圧

VDD…電源電圧

VSS…グランド電位

VPLT…セルプレート電位

Ns…センスノード

N0、N1、N2、N3、N10、N11、N12…ノード

Claims (10)

- メモリセルから読み出されてビット線を伝送される信号を増幅するシングルエンド型のセンスアンプ回路であって、

ゲートに印加される制御電圧に応じて、前記ビット線に対して所定電位を供給するとともに、前記ビット線とセンスノードとの間の接続を制御する第1のMOSトランジスタと、

ゲートが前記センスノードに接続され、前記ビット線から前記第1のMOSトランジスタを介して伝送される信号を増幅する第2のMOSトランジスタと、

第1の制御信号に応じて、前記ビット線を第1の電位に設定する第1の電位設定回路と、

第2の制御信号に応じて、前記センスノードを第2の電位に設定する第2の電位設定回路と、

を備え、前記ビット線を前記第1の電位に設定し、かつ前記センスノードを前記第2の電位に設定した後、前記第1のMOSトランジスタを介して前記ビット線を電荷分配モードで駆動して前記センスノードの信号電圧を前記第2のMOSトランジスタにより増幅することを特徴とするセンスアンプ回路。 - 前記第1の電位は接地電位であり、前記第2の電位は所定の電源電圧であることを特徴とする請求項1に記載のセンスアンプ回路

- 前記第1の電位設定回路は、ゲートに印加される前記第1の制御信号に応じて、前記ビット線と前記接地電位との間の接続を制御する第3のMOSトランジスタであることを特徴とする請求項2に記載のセンスアンプ回路

- 前記第1のMOSトランジスタの閾値電圧のばらつき許容範囲と、前記第2のMOSトランジスタの閾値電圧のばらつき許容範囲は、前記メモリセルのハイ情報とロー情報をそれぞれ読み出した際の前記センスノードにおける所要の電圧差の範囲内に設定されることを特徴とする請求項1に記載のセンスアンプ回路。

- 前記第1のMOSトランジスタ、前記第2のMOSトランジスタ、前記第1の電位設定回路、前記第2の設定回路をそれぞれ含み、前記ビット線としてのローカルビット線を介して伝送される信号を増幅するローカルセンスアンプと、

前記ローカルセンスアンプを介して所定数の前記ローカルビット線と選択的に接続されるグローバルビット線に接続され、前記グローバルビット線の信号電圧のレベルを判定する信号電圧判定回路を含むグローバルセンスアンプと、

を備えることを特徴とする請求項1に記載のセンスアンプ回路。 - 前記第2の電位は、前記グローバルセンスアンプから前記グローバルビット線を経由して前記第2の電位設定回路に供給されることを特徴とする請求項5に記載のセンスアンプ回路。

- 前記第2の電位設定回路は、ゲートに印加される前記第2の制御信号に応じて、前記センスノードと前記グローバルビット線との間の接続を制御する第4のMOSトランジスタであることを特徴とする請求項6に記載のセンスアンプ回路

- ゲートに印加される第3の制御信号に応じて、前記第2のMOSトランジスタのドレインと前記グローバルビット線との間の接続を制御する第5のMOSトランジスタをさらに備えることを特徴とする請求項6に記載のセンスアンプ回路。

- 入力された基準電圧に対し、前記第1のMOSトランジスタ又は前記第2のMOSトランジスタの閾値電圧の変動が補償された補償電圧を発生し、前記ローカルセンスアンプ又は前記グローバルセンスアンプに供給する補償電圧発生回路をさらに備えることを特徴とする請求項5に記載のセンスアンプ回路。

- 請求項1から9のいずれかに記載のセンスアンプ回路を備えたことを特徴とする半導体記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008222938A JP5518313B2 (ja) | 2008-08-29 | 2008-08-29 | センスアンプ回路及び半導体記憶装置 |

| US12/461,859 US8072828B2 (en) | 2008-08-29 | 2009-08-26 | Sense amplifier circuit and semiconductor memory device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008222938A JP5518313B2 (ja) | 2008-08-29 | 2008-08-29 | センスアンプ回路及び半導体記憶装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014076257A Division JP2014142994A (ja) | 2014-04-02 | 2014-04-02 | センスアンプ回路及び半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010055730A true JP2010055730A (ja) | 2010-03-11 |

| JP5518313B2 JP5518313B2 (ja) | 2014-06-11 |

Family

ID=41799161

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008222938A Expired - Fee Related JP5518313B2 (ja) | 2008-08-29 | 2008-08-29 | センスアンプ回路及び半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8072828B2 (ja) |

| JP (1) | JP5518313B2 (ja) |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010055729A (ja) * | 2008-08-29 | 2010-03-11 | Elpida Memory Inc | センスアンプ回路及び半導体記憶装置 |

| JP2012138160A (ja) * | 2010-10-05 | 2012-07-19 | Semiconductor Energy Lab Co Ltd | 半導体メモリ装置およびその駆動方法 |

| JP2013187223A (ja) * | 2012-03-06 | 2013-09-19 | Elpida Memory Inc | 半導体装置 |

| US8588019B2 (en) | 2010-11-05 | 2013-11-19 | Elpida Memory Inc. | Semiconductor device having current change memory cell |

| US8605532B2 (en) | 2010-11-19 | 2013-12-10 | Elpida Memory, Inc. | Semiconductor device having hierarchical bit line structure |

| US10780684B2 (en) | 2016-04-29 | 2020-09-22 | Shanghai Micro Electronics Equipment (Group) Co., Ltd. | Bonding device |

| JPWO2020201865A1 (ja) * | 2019-03-29 | 2020-10-08 | ||

| WO2023166376A1 (ja) * | 2022-03-04 | 2023-09-07 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| WO2023242668A1 (ja) * | 2022-06-16 | 2023-12-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び記憶装置 |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI399754B (zh) * | 2008-03-17 | 2013-06-21 | Elpida Memory Inc | 具有單端感測放大器之半導體裝置 |

| JP5451281B2 (ja) | 2009-09-16 | 2014-03-26 | ピーエスフォー ルクスコ エスエイアールエル | センスアンプ回路及びそれを備えた半導体装置 |

| JP2011159365A (ja) * | 2010-02-02 | 2011-08-18 | Elpida Memory Inc | 半導体装置及び半導体装置を含む情報処理システム |

| US8179735B2 (en) * | 2010-03-26 | 2012-05-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Using differential signals to read data on a single-end port |

| JP2013157044A (ja) | 2012-01-27 | 2013-08-15 | Elpida Memory Inc | 半導体装置 |

| WO2014045598A1 (en) * | 2012-09-24 | 2014-03-27 | Ps4 Luxco S.A.R.L. | Semiconductor device |

| US11017843B2 (en) * | 2019-06-28 | 2021-05-25 | Intel Corporation | Thin film transistors for memory cell array layer selection |

| TWI764759B (zh) * | 2021-06-11 | 2022-05-11 | 円星科技股份有限公司 | 具備可靠容限設定的電路模組 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63228496A (ja) * | 1987-03-17 | 1988-09-22 | Fujitsu Ltd | メモリ回路 |

| JPH02503606A (ja) * | 1987-05-15 | 1990-10-25 | アナログ・ディバイセス・インコーポレーテッド | センス増幅器 |

| JPH04153977A (ja) * | 1990-10-17 | 1992-05-27 | Hitachi Ltd | 半導体メモリ |

| JPH09297992A (ja) * | 1996-05-01 | 1997-11-18 | Fujitsu Ltd | センスアンプ回路 |

| JPH1050073A (ja) * | 1996-08-01 | 1998-02-20 | Nec Corp | 半導体記憶装置 |

| JPH10312685A (ja) * | 1997-03-11 | 1998-11-24 | Toshiba Corp | 半導体記憶装置 |

| JP2000195268A (ja) * | 1998-10-19 | 2000-07-14 | Toshiba Corp | 半導体記憶装置 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5237533A (en) * | 1991-12-20 | 1993-08-17 | National Semiconductor Corporation | High speed switched sense amplifier |

| JPH1116384A (ja) | 1997-06-26 | 1999-01-22 | Fujitsu Ltd | 半導体集積回路 |

| US6492844B2 (en) * | 2000-02-02 | 2002-12-10 | Broadcom Corporation | Single-ended sense amplifier with sample-and-hold reference |

| JP4138228B2 (ja) * | 2000-11-20 | 2008-08-27 | 株式会社東芝 | 半導体メモリ |

| US6771551B1 (en) * | 2003-02-04 | 2004-08-03 | Broadcom Corporation | Sense amplifier with adaptive reference generation |

| JP2007073121A (ja) | 2005-09-06 | 2007-03-22 | Sony Corp | 半導体メモリ回路 |

-

2008

- 2008-08-29 JP JP2008222938A patent/JP5518313B2/ja not_active Expired - Fee Related

-

2009

- 2009-08-26 US US12/461,859 patent/US8072828B2/en active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63228496A (ja) * | 1987-03-17 | 1988-09-22 | Fujitsu Ltd | メモリ回路 |

| JPH02503606A (ja) * | 1987-05-15 | 1990-10-25 | アナログ・ディバイセス・インコーポレーテッド | センス増幅器 |

| JPH04153977A (ja) * | 1990-10-17 | 1992-05-27 | Hitachi Ltd | 半導体メモリ |

| JPH09297992A (ja) * | 1996-05-01 | 1997-11-18 | Fujitsu Ltd | センスアンプ回路 |

| JPH1050073A (ja) * | 1996-08-01 | 1998-02-20 | Nec Corp | 半導体記憶装置 |

| JPH10312685A (ja) * | 1997-03-11 | 1998-11-24 | Toshiba Corp | 半導体記憶装置 |

| JP2000195268A (ja) * | 1998-10-19 | 2000-07-14 | Toshiba Corp | 半導体記憶装置 |

Non-Patent Citations (1)

| Title |

|---|

| JPN6013055506; 伊藤 清男: アドバンスト エレクトロニクスI-9 超LSIメモリ 初版第6刷, 20000220, p.213-214, 株式会社培風館 * |

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010055729A (ja) * | 2008-08-29 | 2010-03-11 | Elpida Memory Inc | センスアンプ回路及び半導体記憶装置 |

| JP2012138160A (ja) * | 2010-10-05 | 2012-07-19 | Semiconductor Energy Lab Co Ltd | 半導体メモリ装置およびその駆動方法 |

| US8588019B2 (en) | 2010-11-05 | 2013-11-19 | Elpida Memory Inc. | Semiconductor device having current change memory cell |

| US8638630B2 (en) | 2010-11-19 | 2014-01-28 | Elpida Memory, Inc. | Semiconductor device having hierarchical bit line structure |

| US8605532B2 (en) | 2010-11-19 | 2013-12-10 | Elpida Memory, Inc. | Semiconductor device having hierarchical bit line structure |

| US9318159B2 (en) | 2012-03-06 | 2016-04-19 | PS4 Lucxo S.a.r.l. | Semiconductor device |

| JP2013187223A (ja) * | 2012-03-06 | 2013-09-19 | Elpida Memory Inc | 半導体装置 |

| US10780684B2 (en) | 2016-04-29 | 2020-09-22 | Shanghai Micro Electronics Equipment (Group) Co., Ltd. | Bonding device |

| JPWO2020201865A1 (ja) * | 2019-03-29 | 2020-10-08 | ||

| US11948626B2 (en) | 2019-03-29 | 2024-04-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistors with silicon and metal oxide channels |

| JP2025063098A (ja) * | 2019-03-29 | 2025-04-15 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US12531114B2 (en) | 2019-03-29 | 2026-01-20 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| WO2023166376A1 (ja) * | 2022-03-04 | 2023-09-07 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| WO2023242668A1 (ja) * | 2022-06-16 | 2023-12-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び記憶装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8072828B2 (en) | 2011-12-06 |

| US20100061170A1 (en) | 2010-03-11 |

| JP5518313B2 (ja) | 2014-06-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5518313B2 (ja) | センスアンプ回路及び半導体記憶装置 | |

| JP5680819B2 (ja) | センスアンプ回路及び半導体記憶装置 | |

| JP5451281B2 (ja) | センスアンプ回路及びそれを備えた半導体装置 | |

| KR101050699B1 (ko) | 반도체 메모리 디바이스 | |

| US7460416B2 (en) | Voltage supply circuit and semiconductor memory | |

| KR101108906B1 (ko) | 단일-종단 감지 증폭기를 갖는 반도체 디바이스 | |

| US9972371B2 (en) | Memory device including memory cell for generating reference voltage | |

| JP3373534B2 (ja) | 半導体記憶装置 | |

| KR100218759B1 (ko) | 임계값전압의 영향을 받지 않고 안정하게 중간전위를 발생할 수 있는 전압발생회로 | |

| KR101026658B1 (ko) | 단일-종단 감지 증폭기를 갖는 반도체 디바이스 | |

| US20110188325A1 (en) | Semiconductor device and data processing system | |

| US7209399B2 (en) | Circuit and method of driving bitlines of integrated circuit memory using improved precharge scheme and sense-amplification scheme | |

| JP2014142994A (ja) | センスアンプ回路及び半導体記憶装置 | |

| CN116153360B (zh) | 感测放大电路结构及存储器 | |

| US20110248697A1 (en) | Semiconductor device and data processing system |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110609 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20130730 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131023 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131112 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140207 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140304 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140402 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5518313 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |