JP2010051152A - 電流モード制御型スイッチングレギュレータ - Google Patents

電流モード制御型スイッチングレギュレータ Download PDFInfo

- Publication number

- JP2010051152A JP2010051152A JP2008215354A JP2008215354A JP2010051152A JP 2010051152 A JP2010051152 A JP 2010051152A JP 2008215354 A JP2008215354 A JP 2008215354A JP 2008215354 A JP2008215354 A JP 2008215354A JP 2010051152 A JP2010051152 A JP 2010051152A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- circuit

- slope

- transistor

- capacitor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Dc-Dc Converters (AREA)

Abstract

【解決手段】インダクタL1に流れるインダクタ電流iLに応じた傾斜のスロープ電圧Vslpを生成するスロープ電圧生成回路4が、インダクタ電流iLを電圧に変換して検出するスイッチドキャパシタ回路と、該スイッチドキャパシタ回路を所定の定電流で充電又は放電する定電流源と、前記スイッチドキャパシタ回路で変換された電圧を接地電圧基準の電圧に変換してスロープ電圧Vslpを生成する電圧変換回路とで構成されるようにした。

【選択図】図1

Description

図8のスイッチングレギュレータ100は、入力端子INに入力された入力電圧Vinを降圧して、出力端子OUTから出力電圧Voutとして出力するものである。スイッチングレギュレータ100では、スイッチングトランジスタM101と同期整流用トランジスタM102が相補的にオン/オフ動作を行うことにより、インダクタL101とコンデンサC101にエネルギーを蓄え、蓄えたエネルギーを出力端子OUTから出力電圧Voutとして出力し、負荷200に供給している。

スイッチングトランジスタM101がオンしているときにインダクタL101に流れるインダクタ電流iLは、スイッチングトランジスタM101のドレイン電流と等しいため、スイッチングトランジスタM101のオン抵抗が分かっていれば、スイッチングトランジスタM101の電圧降下を検出することによりインダクタ電流iLを検出することができる。

そこで、図9のインダクタ電流検出回路120Aは、スイッチングトランジスタM101がオンしているときの電圧降下を検出している。スイッチングトランジスタM101がオンしている場合は、ゲート信号S101はローレベルであり、このとき、PMOSトランジスタM122がオフすると共に、PMOSトランジスタM123がオンするため、演算増幅回路121の非反転入力端には図8の接続部LXの電圧VLXが入力される。

抵抗R121とR122の各抵抗値が同じであるとすると、PMOSトランジスタM121のドレイン電圧VAは、下記(a)式のようになる。

VA=Vin−VLX………………(a)

ランプ電圧生成回路120BのNMOSトランジスタM124は、ゲート信号S101がハイレベルである間はオンしているため、定電流回路i121から出力される電流はNMOSトランジスタM124でバイパスされ、ランプコンデンサC121の端子電圧VBは0Vになっている。

VC=(VA+VB)/2=(Vin−VLX+VB)/2…………(b)

Vslp=K×VC=K×(Vin−VLX+VB)/2………………(c)

Vslp=VC+(r126×ia)=(Vin−VLX+VB)/2+(r126×ia)………………(d)

前記(d)式から分かるように、スロープ電圧Vslpは、インダクタ電流(Vin−VLX)に、スロープ補償電圧であるランプコンデンサの充電電圧VBとオフセット電圧Vofを加えた電圧である。

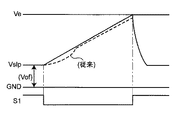

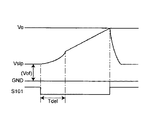

図10は、図8のスロープ電圧生成回路120で生成されたスロープ電圧Vslpの波形例を示した図である。図10から分かるように、スロープ電圧Vslpは、ゲート信号S101がローレベルになった直後は緩やかに立ち上がり、時間の経過に伴って所望の傾斜に近づき、時間Tdel後に該所望の傾斜になっていた。このように、スロープ電圧Vslpの立ち上がりが緩やかになる原因は、電圧VCを演算増幅回路124による電圧−電流変換回路で電流に変換する際の遅延時間と、PMOSトランジスタM127とM128で形成したカレントミラー回路を経由するときの遅延時間によるものである。

制御電極に入力された制御信号に応じてスイッチングを行うスイッチトランジスタと、

該スイッチングトランジスタのスイッチングによって前記入力電圧による充電が行われるインダクタと、

該インダクタの放電を行う整流素子と、

前記インダクタの充電を行う際に該インダクタに流れるインダクタ電流に比例した電圧を生成しスロープ電圧として出力するスロープ電圧生成回路部と、

前記スロープ電圧に応じて前記スイッチングトランジスタのスイッチング制御を行うスイッチング制御回路部と、

を備え、

前記スロープ電圧生成回路部は、

前記スイッチングトランジスタの制御電極に入力される制御信号に応じてスイッチングを行い、前記インダクタ電流を電圧に変換して出力するスイッチドキャパシタ回路と、

該スイッチドキャパシタ回路に対して所定の定電流で充電又は放電を行う第1の定電流源と、

を備えるものである。

前記第1の定電流源からの定電流で充電又は放電が行われるコンデンサと、

該コンデンサの一端と前記インダクタにおける前記スイッチングトランジスタ側の一端との間に接続された第1のスイッチ素子と、

前記コンデンサの前記一端と前記入力電圧との間に接続された第2のスイッチ素子と、

前記コンデンサに並列に接続された第3のスイッチ素子と、

を備え、

前記コンデンサの他端と接地電圧との間に前記第1の定電流源が接続され、前記第1のスイッチ素子は、前記スイッチングトランジスタと同じスイッチング動作を行い、前記第2及び第3の各スイッチ素子は、前記スイッチングトランジスタと相反するスイッチング動作を行うようにした。

前記コンデンサと前記第1の定電流源との接続部の電圧が一方の入力端に入力された演算増幅回路と、

制御電極が該演算増幅回路の出力端に接続されると共に、電流入力端が前記演算増幅回路の他方の入力端に接続された第1のトランジスタと、

前記入力電圧と該第1のトランジスタの電流入力端との間に接続された第1の抵抗と、

前記第1のトランジスタから出力された電流を電圧に変換して前記スロープ電圧を生成する第2の抵抗と、

を備えるようにした。

第1の実施の形態.

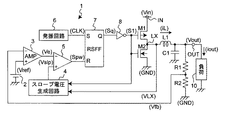

図1は、本発明の第1の実施の形態における電流モード制御型スイッチングレギュレータの回路例を示した図である。

図1において、電流モード制御型スイッチングレギュレータ(以下、スイッチングレギュレータと呼ぶ)1は、入力端子INに入力された入力電圧Vinを所定の定電圧に降圧して出力電圧Voutとして出力端子OUTから負荷10に出力する同期整流方式の降圧型スイッチングレギュレータをなしている。

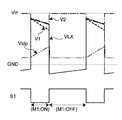

図2は、図1に示したスイッチングレギュレータ1の各信号の波形例を示したタイミングチャートであり、図2を参照しながらスイッチングレギュレータ1の動作について説明する。なお、ioutは出力端子OUTから負荷10に出力される出力電流を示している。

発振回路6からRSフリップフロップ回路7のセット入力端Sには、所定の周期でハイレベルになるクロック信号CLKが入力されており、クロック信号CLKがハイレベルになるとRSフリップフロップ回路7の出力信号Sqはハイレベルになる。

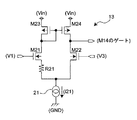

図3において、スロープ電圧生成回路4は、所定の定電流i11を供給する定電流源11、インバータ12、演算増幅回路13、PMOSトランジスタM11〜M14、コンデンサC11及び抵抗R11,R12で構成されている。なお、定電流源11は第1の定電流源を、PMOSトランジスタM11〜M13、コンデンサC11及びインバータ12はスイッチドキャパシタ回路をなし、演算増幅回路13、PMOSトランジスタM14及び抵抗R11,R12は電圧変換回路をなす。また、PMOSトランジスタM11は第1のスイッチ素子を、PMOSトランジスタM12は第2のスイッチ素子を、PMOSトランジスタM13は第3のスイッチ素子をそれぞれなし、PMOSトランジスタM14は第1のトランジスタを、抵抗R11は第1の抵抗を、抵抗R12は第2の抵抗をそれぞれなす。

PMOSトランジスタM11〜M13、コンデンサC11及びインバータ12からなるスイッチドキャパシタ回路と定電流源11はインダクタ電流iLの検出を行っている。

最初に、電流源回路11から定電流i11の供給がない場合の、制御信号S1に応じたPMOSトランジスタM11〜M13及びコンデンサC11の動作について説明する。

制御信号S1がハイレベルのとき、PMOSトランジスタM11はオフして遮断状態になり、PMOSトランジスタM12及びM13がそれぞれオンして導通状態になるため、コンデンサC11の両端は入力電圧Vinで充電される。制御信号S1がローレベルのときは、PMOSトランジスタM11がオンすると共にPMOSトランジスタM12及びM13がそれぞれオフするため、コンデンサC11とPMOSトランジスタM11との接続部は電圧VLXで充電され、電圧V1は電圧VLXになる。

制御信号S1がハイレベルのときは、前記のようにPMOSトランジスタM11はオフすると共に、PMOSトランジスタM12及びM13がそれぞれオンするため、コンデンサC11の両端は入力電圧Vinで充電される。

V1(T)=VLX−T×i11/c11………………(1)

前記(1)式の右辺第1項は、インダクタ電流iLを電圧に変換して検出していることを示し、右辺第2項は一定の傾きを持ったランプ電圧を減算していることを示している。したがって、電圧V1をスロープ電圧として出力することができる。

演算増幅回路13は、電圧V1からオフセット電圧Vofを減算した電圧と電圧V3が等しくなるようにPMOSトランジスタM14のゲート電圧を制御する。抵抗R11に流れる電流をir11とすると、入力電圧Vinから抵抗R11での電圧降下を減算した電圧V3が、電圧V1からオフセット電圧Vofを減算した電圧に等しくなるように、PMOSトランジスタM14によって電流ir11が制御されるため、抵抗R11の抵抗値をr11とすると下記(2)式が成り立つ。

Vin−r11×ir11=V3=V1−Vof

ir11=(Vin−V1+Vof)/r11………………(2)

Vslp=ir11×r12………………(3)

Vslp={Vin−(VLX−T×i11/c11)+Vof}/r11×r12=(Vin−VLX+T×i11/c11)/r11×r12+Vof/r11×r12………………(4)

前記(4)式の右辺第1項は、インダクタ電流を電圧に変換して一定の傾きを持ったランプ電圧を加算していることを表しており、右辺第2項はオフセット電圧を表している。

図5において、演算増幅回路13は、NMOSトランジスタM21,M22、PMOSトランジスタM23,M24、所定の定電流i21を供給する定電流源21及びオフセット電圧Vofを設けるための抵抗R21で構成されている。NMOSトランジスタM21及びM22は差動対をなしており、NMOSトランジスタM21のゲートには電圧V1が、NMOSトランジスタM22のゲートには電圧V3がそれぞれ入力されている。PMOSトランジスタM23及びM24はカレントミラー回路を形成しており、前記差動対の負荷をなしている。PMOSトランジスタM23及びM24において、各ソースはそれぞれ入力電圧Vinに接続され、各ゲートは接続され該接続部はPMOSトランジスタM23のドレインに接続されている。

NMOSトランジスタM21とM22に同一の電流が流れるようにするためには、抵抗R21で発生する電圧降下分だけNMOSトランジスタM21のゲート電圧がNMOSトランジスタM22のゲート電圧よりも大きくならなければならない。すなわち、抵抗R21で発生する前記電圧降下がオフセット電圧Vofになり、演算増幅回路13は、抵抗R21を設けることにより入力端にオフセット電圧Vofが設けられている。

図6から分かるように、従来よりもスロープVslpで発生していた遅延を削減することができるため、制御信号S1がローレベルになった直後からスロープ電圧Vslpの直線性が保たれている。

更に、図9の従来回路から演算増幅回路124、NMOSトランジスタM126、PMOSトランジスタM127,M128、抵抗R123,R124,R125,R126、及び電流源i122に相当する素子を削減することができるため、回路規模を半分以下にすることができる。

2 基準電圧発生回路

3 誤差増幅回路

4 スロープ電圧生成回路

5 PWMコンパレータ

6 発振回路

7 RSフリップフロップ回路

8,12 インバータ

10 負荷

11,14 定電流源

13 演算増幅回路

M1 スイッチングトランジスタ

M2 同期整流用トランジスタ

M11〜M14 PMOSトランジスタ

L1 インダクタ

C1,C11 コンデンサ

R1,R2,R11,R12 抵抗

Claims (7)

- 入力端子に入力された入力電圧を、所定の定電圧に変換して出力端子から出力電圧として出力する電流モード制御型スイッチングレギュレータにおいて、

制御電極に入力された制御信号に応じてスイッチングを行うスイッチトランジスタと、

該スイッチングトランジスタのスイッチングによって前記入力電圧による充電が行われるインダクタと、

該インダクタの放電を行う整流素子と、

前記インダクタの充電を行う際に該インダクタに流れるインダクタ電流に比例した電圧を生成しスロープ電圧として出力するスロープ電圧生成回路部と、

前記スロープ電圧に応じて前記スイッチングトランジスタのスイッチング制御を行うスイッチング制御回路部と、

を備え、

前記スロープ電圧生成回路部は、

前記スイッチングトランジスタの制御電極に入力される制御信号に応じてスイッチングを行い、前記インダクタ電流を電圧に変換して出力するスイッチドキャパシタ回路と、

該スイッチドキャパシタ回路に対して所定の定電流で充電又は放電を行う第1の定電流源と、

を備えることを特徴とする電流モード制御型スイッチングレギュレータ。 - 前記スイッチドキャパシタ回路は、

前記第1の定電流源からの定電流で充電又は放電が行われるコンデンサと、

該コンデンサの一端と前記インダクタにおける前記スイッチングトランジスタ側の一端との間に接続された第1のスイッチ素子と、

前記コンデンサの前記一端と前記入力電圧との間に接続された第2のスイッチ素子と、

前記コンデンサに並列に接続された第3のスイッチ素子と、

を備え、

前記コンデンサの他端と接地電圧との間に前記第1の定電流源が接続され、前記第1のスイッチ素子は、前記スイッチングトランジスタと同じスイッチング動作を行い、前記第2及び第3の各スイッチ素子は、前記スイッチングトランジスタと相反するスイッチング動作を行うことを特徴とする請求項1記載の電流モード制御型スイッチングレギュレータ。 - 前記スロープ電圧生成回路部は、前記コンデンサと前記第1の定電流源との接続部の電圧を前記スロープ電圧として出力することを特徴とする請求項2記載の電流モード制御型スイッチングレギュレータ。

- 前記スロープ電圧生成回路部は、前記コンデンサと前記第1の定電流源との接続部の電圧を接地電圧基準の電圧に変換して前記スロープ電圧として出力する電圧変換回路を備えることを特徴とする請求項2記載の電流モード制御型スイッチングレギュレータ。

- 前記電圧変換回路は、

前記コンデンサと前記第1の定電流源との接続部の電圧が一方の入力端に入力された演算増幅回路と、

制御電極が該演算増幅回路の出力端に接続されると共に、電流入力端が前記演算増幅回路の他方の入力端に接続された第1のトランジスタと、

前記入力電圧と該第1のトランジスタの電流入力端との間に接続された第1の抵抗と、

前記第1のトランジスタから出力された電流を電圧に変換して前記スロープ電圧を生成する第2の抵抗と、

を備えることを特徴とする請求項4記載の電流モード制御型スイッチングレギュレータ。 - 前記演算増幅回路は、少なくとも一方の入力端に所定のオフセット電圧が設けられることを特徴とする請求項5記載の電流モード制御型スイッチングレギュレータ。

- 前記電圧変換回路は、前記第2の抵抗に所定の定電流を供給する第2の定電流源を備えることを特徴とする請求項5記載の電流モード制御型スイッチングレギュレータ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008215354A JP5470772B2 (ja) | 2008-08-25 | 2008-08-25 | 電流モード制御型スイッチングレギュレータ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008215354A JP5470772B2 (ja) | 2008-08-25 | 2008-08-25 | 電流モード制御型スイッチングレギュレータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010051152A true JP2010051152A (ja) | 2010-03-04 |

| JP5470772B2 JP5470772B2 (ja) | 2014-04-16 |

Family

ID=42067753

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008215354A Active JP5470772B2 (ja) | 2008-08-25 | 2008-08-25 | 電流モード制御型スイッチングレギュレータ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5470772B2 (ja) |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8482267B2 (en) | 2008-04-11 | 2013-07-09 | Ricoh Company, Ltd. | Variable voltage DC-DC converter |

| US8502508B2 (en) | 2009-11-11 | 2013-08-06 | Ricoh Company, Ltd. | Switching regulator circuit configured to perform step up and step down operations and operation method therefor |

| JP2014033494A (ja) * | 2012-08-01 | 2014-02-20 | Tottori Cosmo Science Kk | 電源回路 |

| US8860391B2 (en) | 2008-12-26 | 2014-10-14 | Ricoh Company, Ltd. | DC-DC converter, and power supply circuit having DC-DC converter |

| JP2014207741A (ja) * | 2013-04-11 | 2014-10-30 | 株式会社リコー | スイッチングレギュレータ |

| KR101590045B1 (ko) * | 2015-05-27 | 2016-01-29 | (주)비츠로 | 엘이디 등기구 정전류 제어장치 |

| JP2019047692A (ja) * | 2017-09-06 | 2019-03-22 | ローム株式会社 | スイッチング電源装置 |

| JP2019083686A (ja) * | 2019-01-24 | 2019-05-30 | ローム株式会社 | 電流モード制御型スイッチング電源装置 |

| CN117294142A (zh) * | 2023-11-24 | 2023-12-26 | 上海英联电子科技有限公司 | 电压转换电路 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005039925A (ja) * | 2003-07-14 | 2005-02-10 | Shindengen Electric Mfg Co Ltd | スイッチング電源 |

| JP2006246626A (ja) * | 2005-03-03 | 2006-09-14 | Ricoh Co Ltd | スイッチングレギュレータ及びその電圧制御方法 |

| JP2007209103A (ja) * | 2006-02-01 | 2007-08-16 | Ricoh Co Ltd | 電流モード制御dc−dcコンバータ |

| JP2008072833A (ja) * | 2006-09-14 | 2008-03-27 | Ricoh Co Ltd | スロープ補償回路およびスイッチングレギュレータ |

| JP2008161001A (ja) * | 2006-12-26 | 2008-07-10 | Ricoh Co Ltd | 電流モード制御型スイッチングレギュレータ及びその動作制御方法 |

| JP2009219179A (ja) * | 2008-03-07 | 2009-09-24 | Ricoh Co Ltd | 電流モード制御型スイッチングレギュレータ |

-

2008

- 2008-08-25 JP JP2008215354A patent/JP5470772B2/ja active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005039925A (ja) * | 2003-07-14 | 2005-02-10 | Shindengen Electric Mfg Co Ltd | スイッチング電源 |

| JP2006246626A (ja) * | 2005-03-03 | 2006-09-14 | Ricoh Co Ltd | スイッチングレギュレータ及びその電圧制御方法 |

| JP2007209103A (ja) * | 2006-02-01 | 2007-08-16 | Ricoh Co Ltd | 電流モード制御dc−dcコンバータ |

| JP2008072833A (ja) * | 2006-09-14 | 2008-03-27 | Ricoh Co Ltd | スロープ補償回路およびスイッチングレギュレータ |

| JP2008161001A (ja) * | 2006-12-26 | 2008-07-10 | Ricoh Co Ltd | 電流モード制御型スイッチングレギュレータ及びその動作制御方法 |

| JP2009219179A (ja) * | 2008-03-07 | 2009-09-24 | Ricoh Co Ltd | 電流モード制御型スイッチングレギュレータ |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8482267B2 (en) | 2008-04-11 | 2013-07-09 | Ricoh Company, Ltd. | Variable voltage DC-DC converter |

| US8860391B2 (en) | 2008-12-26 | 2014-10-14 | Ricoh Company, Ltd. | DC-DC converter, and power supply circuit having DC-DC converter |

| US8502508B2 (en) | 2009-11-11 | 2013-08-06 | Ricoh Company, Ltd. | Switching regulator circuit configured to perform step up and step down operations and operation method therefor |

| JP2014033494A (ja) * | 2012-08-01 | 2014-02-20 | Tottori Cosmo Science Kk | 電源回路 |

| JP2014207741A (ja) * | 2013-04-11 | 2014-10-30 | 株式会社リコー | スイッチングレギュレータ |

| KR101590045B1 (ko) * | 2015-05-27 | 2016-01-29 | (주)비츠로 | 엘이디 등기구 정전류 제어장치 |

| JP2019047692A (ja) * | 2017-09-06 | 2019-03-22 | ローム株式会社 | スイッチング電源装置 |

| JP2019083686A (ja) * | 2019-01-24 | 2019-05-30 | ローム株式会社 | 電流モード制御型スイッチング電源装置 |

| CN117294142A (zh) * | 2023-11-24 | 2023-12-26 | 上海英联电子科技有限公司 | 电压转换电路 |

| CN117294142B (zh) * | 2023-11-24 | 2024-02-06 | 上海英联电子科技有限公司 | 电压转换电路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5470772B2 (ja) | 2014-04-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5169333B2 (ja) | 電流モード制御型スイッチングレギュレータ | |

| JP5470772B2 (ja) | 電流モード制御型スイッチングレギュレータ | |

| KR101168488B1 (ko) | 충전 제어 회로 | |

| JP5091027B2 (ja) | スイッチングレギュレータ | |

| JP5195182B2 (ja) | 電流モード制御型スイッチングレギュレータ | |

| JP5369555B2 (ja) | 電流モード制御型スイッチングレギュレータ及びその動作制御方法 | |

| JP4473669B2 (ja) | 定電圧回路、その定電圧回路を使用した定電流源、増幅器及び電源回路 | |

| JP4054714B2 (ja) | 昇降圧型dc−dcコンバータ | |

| US20110043175A1 (en) | Current-mode control switching regulator and operations control method thereof | |

| JP6009742B2 (ja) | スイッチング電源装置 | |

| JP5315988B2 (ja) | Dc−dcコンバータ及びそのdc−dcコンバータを備えた電源回路 | |

| JP2009303317A (ja) | 基準電圧発生回路及びその基準電圧発生回路を備えたdc−dcコンバータ | |

| JP2006246626A (ja) | スイッチングレギュレータ及びその電圧制御方法 | |

| JP2009071951A (ja) | 定電流出力制御型スイッチングレギュレータ | |

| JP2007159319A (ja) | Dc−dcコンバータの制御回路および制御方法 | |

| JP4487649B2 (ja) | 昇降圧型dc−dcコンバータの制御装置 | |

| KR20180015592A (ko) | 스위칭 제어 회로, 스위칭 전원 장치, 전자 기기 | |

| CN108475984A (zh) | 在输入电压的宽范围内具有稳定的输出特性且具有应对输入电压变化的器件的dc-dc转换器 | |

| US7423415B2 (en) | DC-DC converter and its control method, and switching regulator and its control method | |

| US20120032659A1 (en) | Power supply device | |

| JP2010063290A (ja) | 電源制御回路 | |

| JP5645466B2 (ja) | 電源の制御回路及び電子機器 | |

| JP5104284B2 (ja) | スイッチング電源の制御回路および該制御回路を用いるスイッチング電源 | |

| WO2024154487A1 (ja) | 電源制御装置、スイッチング電源 | |

| JP2006217720A (ja) | スイッチング電源 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110613 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121019 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121106 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121226 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130618 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130703 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140107 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140120 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5470772 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |