JP2010045238A - 電力用半導体装置 - Google Patents

電力用半導体装置 Download PDFInfo

- Publication number

- JP2010045238A JP2010045238A JP2008208910A JP2008208910A JP2010045238A JP 2010045238 A JP2010045238 A JP 2010045238A JP 2008208910 A JP2008208910 A JP 2008208910A JP 2008208910 A JP2008208910 A JP 2008208910A JP 2010045238 A JP2010045238 A JP 2010045238A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- region

- semiconductor layer

- semiconductor

- difference value

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

- H10D30/665—Vertical DMOS [VDMOS] FETs having edge termination structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/102—Constructional design considerations for preventing surface leakage or controlling electric field concentration

- H10D62/103—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices

- H10D62/105—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices by having particular doping profiles, shapes or arrangements of PN junctions; by having supplementary regions, e.g. junction termination extension [JTE]

- H10D62/109—Reduced surface field [RESURF] PN junction structures

- H10D62/111—Multiple RESURF structures, e.g. double RESURF or 3D-RESURF structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/393—Body regions of DMOS transistors or IGBTs

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

Abstract

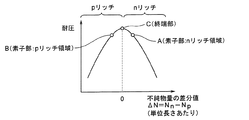

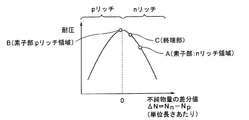

【解決手段】素子部と終端部とを有する電力用半導体装置であって、第1半導体層と;前記第1半導体層上に形成された第2半導体層及び第3半導体層であって、前記素子部には、前記第2及び第3半導体層を有する第1領域と、前記第2及び第3半導体層を有する第2領域とが設けられており、前記第2半導体層の単位長さあたりの不純物量NAから前記第3半導体層の単位長さあたりの不純物量NBを引いた差分値ΔN(=NA−NB)については、前記素子部の前記第1領域の差分値ΔNC1と、前記素子部の前記第2領域の差分値ΔNC2と、前記終端部の差分値ΔNTとの間に、ΔNC1>ΔNT>ΔNC2の関係が成り立つ、第2及び第3半導体層と;第4半導体層と;第5半導体層とを備える電力用半導体装置。

【選択図】図1

Description

図1は、第1実施例の電力用半導体装置101の側方断面図である。図1A及び図1Bには、オン時に電流が流れる素子部111が示されており、図1Cには、素子部111の周辺に位置する終端部112が示されている。図1の電力用半導体装置101は、素子部111と、終端部112とを有している。図1Aの領域と図1Bの領域との関係については、後述する。

図3は、第2実施例の電力用半導体装置101の上面図である。図3において、素子部111は、n+ドレイン層121の表面に垂直な境界面Yにより、nリッチ領域111Aとpリッチ領域111Bとに分割されている。図3の矢印Xは、図1の矢印Xと同様、nピラー層122とpピラー層123とが交互に配置されている方向を表す。

図4は、第3実施例の電力用半導体装置101の上面図である。図4において、素子部111は、n+ドレイン層121の表面に垂直な境界面Yにより、nリッチ領域111Aとpリッチ領域111Bとに分割されている。図4の矢印Xは、図1の矢印Xと同様、nピラー層122とpピラー層123とが交互に配置されている方向を表す。

図5は、第4実施例の電力用半導体装置101の上面図である。図5において、素子部111は、n+ドレイン層121の表面に垂直な境界面Yにより、nリッチ領域111Aとpリッチ領域111Bとに分割されている。図5の矢印Xは、図1の矢印Xと同様、nピラー層122とpピラー層123とが交互に配置されている方向を表す。

111 素子部

112 終端部

121 n+ドレイン層

122 nピラー層

123 pピラー層

124 pベース層

125 nソース層

131 ゲート絶縁膜

132 ゲート電極

133 ソース電極

134 ドレイン電極

201 リサーフ層

211 フィールド絶縁膜

212 フィールドプレート電極

213 フィールドストップ電極

Claims (5)

- 素子部と終端部とを有する電力用半導体装置であって、

第1導電型の第1半導体層と;

前記第1半導体層上に形成され、前記第1半導体層の表面に平行な方向に沿って交互に配置された、第1導電型の第2半導体層及び第2導電型の第3半導体層であって、

前記素子部には、前記第2及び第3半導体層を有する第1領域と、前記第2及び第3半導体層を有する第2領域とが設けられており、前記第1領域と前記第2領域は、前記第1半導体層の表面に平行な方向に隣接しており、

前記第2半導体層の単位長さあたりの不純物量NAから前記第3半導体層の単位長さあたりの不純物量NBを引いた差分値ΔN(=NA−NB)については、前記素子部の前記第1領域の差分値ΔNC1と、前記素子部の前記第2領域の差分値ΔNC2と、前記終端部の差分値ΔNTとの間に、ΔNC1>ΔNT>ΔNC2の関係が成り立つ、

第2及び第3半導体層と;

前記第2及び第3半導体層の表面に選択的に形成された第2導電型の第4半導体層と;

前記第4半導体層の表面に選択的に形成された第1導電型の第5半導体層と;

前記第2、第4、及び第5半導体層上に絶縁膜を介して形成された制御電極と;

前記第4及び第5半導体層に電気的に接続された第1の主電極と;

前記第1半導体層に電気的に接続された第2の主電極とを備えることを特徴とする電力用半導体装置。 - 前記素子部の前記第1領域の差分値ΔNC1は、0よりも大きく、

前記素子部の前記第2領域の差分値ΔNC2は、0よりも小さいことを特徴とする請求項1に記載の電力用半導体装置。 - 前記終端部では、前記第2半導体層の単位長さあたりの不純物量と、前記第3半導体層の単位長さあたりの不純物量とが等しいことを特徴とする請求項1又は2に記載の電力用半導体装置。

- 前記第1領域と前記第2領域は、前記第2半導体層と前記第3半導体層とが交互に配置された方向の平行方向又は垂直方向に隣接していることを特徴とする請求項1から3のいずれか1項に記載の電力用半導体装置。

- 前記素子部には、前記第2及び第3半導体層を有する1つ以上の前記第1領域と、前記第2及び第3半導体層を有する1つ以上の前記第2領域とが設けられていることを特徴とする請求項1から4のいずれか1項に記載の電力用半導体装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008208910A JP4686580B2 (ja) | 2008-08-14 | 2008-08-14 | 電力用半導体装置 |

| US12/540,192 US8030706B2 (en) | 2008-08-14 | 2009-08-12 | Power semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008208910A JP4686580B2 (ja) | 2008-08-14 | 2008-08-14 | 電力用半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010045238A true JP2010045238A (ja) | 2010-02-25 |

| JP4686580B2 JP4686580B2 (ja) | 2011-05-25 |

Family

ID=41680705

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008208910A Expired - Fee Related JP4686580B2 (ja) | 2008-08-14 | 2008-08-14 | 電力用半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8030706B2 (ja) |

| JP (1) | JP4686580B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011054884A (ja) * | 2009-09-04 | 2011-03-17 | Sony Corp | 半導体装置及び半導体装置の製造方法 |

| WO2017094144A1 (ja) * | 2015-12-02 | 2017-06-08 | サンケン電気株式会社 | 半導体装置 |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8829640B2 (en) * | 2011-03-29 | 2014-09-09 | Alpha And Omega Semiconductor Incorporated | Configuration and method to generate saddle junction electric field in edge termination |

| CN104638004B (zh) * | 2013-11-15 | 2018-04-17 | 上海华虹宏力半导体制造有限公司 | 超级结mosfet器件的结构 |

| CN108181564A (zh) * | 2016-12-07 | 2018-06-19 | 无锡同方微电子有限公司 | 一种uis测试电路及其测试方法 |

| CN114402443A (zh) * | 2020-03-17 | 2022-04-26 | 华为技术有限公司 | 一种绝缘栅双极型晶体管、电机控制器及汽车 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001298191A (ja) * | 2000-02-09 | 2001-10-26 | Fuji Electric Co Ltd | 半導体装置 |

| JP2007235095A (ja) * | 2006-01-31 | 2007-09-13 | Denso Corp | 半導体装置および半導体基板の製造方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4524539B2 (ja) | 2002-08-13 | 2010-08-18 | 富士電機システムズ株式会社 | 半導体素子 |

| JP4997715B2 (ja) | 2005-05-18 | 2012-08-08 | 富士電機株式会社 | 半導体装置およびその製造方法 |

| JP2008182054A (ja) * | 2007-01-25 | 2008-08-07 | Toshiba Corp | 半導体装置 |

| JP4564509B2 (ja) * | 2007-04-05 | 2010-10-20 | 株式会社東芝 | 電力用半導体素子 |

-

2008

- 2008-08-14 JP JP2008208910A patent/JP4686580B2/ja not_active Expired - Fee Related

-

2009

- 2009-08-12 US US12/540,192 patent/US8030706B2/en not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001298191A (ja) * | 2000-02-09 | 2001-10-26 | Fuji Electric Co Ltd | 半導体装置 |

| JP2007235095A (ja) * | 2006-01-31 | 2007-09-13 | Denso Corp | 半導体装置および半導体基板の製造方法 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011054884A (ja) * | 2009-09-04 | 2011-03-17 | Sony Corp | 半導体装置及び半導体装置の製造方法 |

| WO2017094144A1 (ja) * | 2015-12-02 | 2017-06-08 | サンケン電気株式会社 | 半導体装置 |

| KR20180037057A (ko) * | 2015-12-02 | 2018-04-10 | 산켄덴키 가부시키가이샤 | 반도체 장치 |

| JPWO2017094144A1 (ja) * | 2015-12-02 | 2018-07-19 | サンケン電気株式会社 | 半導体装置 |

| KR102015962B1 (ko) * | 2015-12-02 | 2019-08-29 | 산켄덴키 가부시키가이샤 | 반도체 장치 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8030706B2 (en) | 2011-10-04 |

| US20100038712A1 (en) | 2010-02-18 |

| JP4686580B2 (ja) | 2011-05-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5580150B2 (ja) | 半導体装置 | |

| JP6061181B2 (ja) | 半導体装置 | |

| US8227854B2 (en) | Semiconductor device having first and second resurf layers | |

| CN106165101B (zh) | 半导体装置 | |

| JP5687582B2 (ja) | 半導体素子およびその製造方法 | |

| JP2010251571A (ja) | 半導体装置 | |

| US9318590B2 (en) | IGBT using trench gate electrode | |

| JP2016062981A (ja) | 半導体装置及びその製造方法 | |

| JP4686580B2 (ja) | 電力用半導体装置 | |

| CN101847656B (zh) | 绝缘栅双极性晶体管 | |

| CN103681668A (zh) | 半导体装置 | |

| JP2008294028A (ja) | 半導体装置 | |

| CN105448994A (zh) | 半导体装置及其制造方法 | |

| KR101121574B1 (ko) | 전하 균형 전력 디바이스 및 그 제조 방법 | |

| KR101127501B1 (ko) | 트렌치 게이트 구조를 가지는 전력 반도체 소자 | |

| JP5738653B2 (ja) | 絶縁ゲート型半導体装置 | |

| JP2010045307A (ja) | 電力用半導体装置 | |

| JP5446404B2 (ja) | 半導体装置 | |

| US8072027B2 (en) | 3D channel architecture for semiconductor devices | |

| KR101279199B1 (ko) | 반도체 소자 및 이의 제조 방법 | |

| JP2013051434A (ja) | 半導体装置 | |

| JP5753114B2 (ja) | ダイオード | |

| JP2009277956A (ja) | 半導体装置 | |

| JP2007115943A (ja) | 半導体装置 | |

| JP2024025440A (ja) | 炭化珪素半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100803 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110107 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110118 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110214 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140218 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140218 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |