JP2010034776A - 非可逆回路素子 - Google Patents

非可逆回路素子 Download PDFInfo

- Publication number

- JP2010034776A JP2010034776A JP2008193685A JP2008193685A JP2010034776A JP 2010034776 A JP2010034776 A JP 2010034776A JP 2008193685 A JP2008193685 A JP 2008193685A JP 2008193685 A JP2008193685 A JP 2008193685A JP 2010034776 A JP2010034776 A JP 2010034776A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- ferrite

- circuit board

- soldered

- terminal electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Abstract

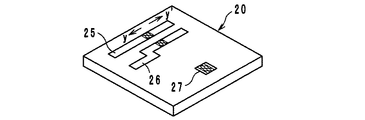

【解決手段】永久磁石41と該永久磁石41により直流磁界が印加されるフェライト32とを一体化したフェライト・磁石素子30を回路基板20上にはんだ付け実装した非可逆回路素子。フェライト32は第1中心電極及び第2中心電極を備えている。回路基板20の表面には、第1中心電極の一端部電極がはんだ付けされる入力端子電極25と、第1中心電極の他端部と第2中心電極の一端部の電極がはんだ付けされる出力端子電極26と、第2中心電極の他端部電極がはんだ付けされるグランド端子電極27とが設けられ、入力端子電極25はy方向のみならず、それと反対のy’方向にも延在されている。

【選択図】図1

Description

永久磁石と、

前記永久磁石により直流磁界が印加される直方体形状のフェライトと、

前記フェライトの互いに平行に位置する二つの主面に、互いに電気的に絶縁状態で交差して配置された導体膜からなる第1中心電極及び第2中心電極と、

表面に端子電極が形成された回路基板と、

を備え、

前記フェライトの主面に前記永久磁石を固定してフェライト・磁石素子が形成され、該フェライト・磁石素子は前記回路基板上にフェライトの主面が垂直方向に位置するように配置され、

前記回路基板の表面には、第1及び第2中心電極のそれぞれの端部がはんだ付けされる第1、第2及び第3端子電極が形成されており、第1及び第2端子電極は前記フェライトの長辺方向の一端部分に対向して配置され、第3端子電極は前記フェライトの長辺方向の他端部分に対向して配置されており、

第1及び第2端子電極の少なくともいずれかは前記フェライトの長辺方向とほぼ直交する第1の方向に延在され、第1及び第2端子電極の少なくともいずれかは前記第1の方向とはほぼ反対の第2の方向に延在されていること、

を特徴とする。

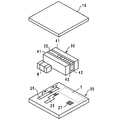

本発明に係る非可逆回路素子の第1実施例である2ポート型アイソレータの分解斜視図を図1に示す。この2ポート型アイソレータは、集中定数型アイソレータであり、概略、回路基板20と、フェライト32と一対の永久磁石41とからなるフェライト・磁石素子30と、平板状ヨーク10とで構成されている。

図4に第2実施例であるアイソレータの要部を示す。回路基板20の表面に形成した入力端子電極25及び出力端子電極26のそれぞれがy方向に加えてy’方向にも延在されている。他の構成は前記第1実施例と同様である。

図5に第3実施例であるアイソレータの要部を示す。回路基板20の表面に形成した入力端子電極25及び出力端子電極26のy方向に延在した部分25a,26aにはんだ流れ防止処理が施されている。具体的には、はんだ濡れ性の悪い材料、樹脂材料を含むオーバーコート材やガラス材料を含むオーバーグレーズ材などで端子電極25,26の一部を被覆している。レーザで端子電極25,26の表面を酸化させてもよい。他の構成は前記第1実施例と同様である。

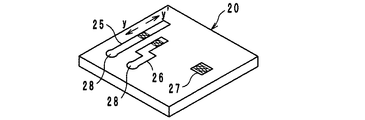

図6に第4実施例であるアイソレータの要部を示す。回路基板20の表面に形成した入力端子電極25及び出力端子電極26のy方向に延在した部分が回路基板20に内蔵された電極(図示せず)に接続したビアホール導体28に接続されている。本第4実施例では前記第1実施例で示した終端抵抗Rは回路基板20に内蔵されている。他の構成は第1実施例と同様である。

図7に第5実施例であるアイソレータを示す。このアイソレータでは、終端抵抗RとコンデンサC1とがチップ型の電子部品として回路基板20の表面に実装されている。それゆえ、出力端子電極26のy方向への延在部分は端部26b,26cに分岐され、回路基板20上には別途端子電極29が形成されている。コンデンサC1は入力端子電極25と出力端子電極26の端部26bとにはんだ付けされる。終端抵抗Rは出力端子電極26の端部26cと端子電極29とにはんだ付けされる。

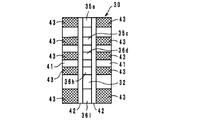

図8に示すように、永久磁石41の回路基板20との対向面に電極43(車線を付して示す)を形成し、該電極43を回路基板20上に設けた電極とリフローによってはんだ付けしてもよい。電極43が接合される回路基板20上の電極は、入力端子電極25や出力端子電極26であってもよく、あるいは、専用に形成された接続用の電極である。また、前記電極43は接着剤42上にも形成するようにしてもよい。

なお、本発明に係る非可逆回路素子は前記実施例に限定するものではなく、その要旨の範囲内で種々に変更することができる。

25…入力端子電極

26…出力端子電極

27…グランド端子電極

28…ビアホール導体

30…フェライト・磁石素子

32…フェライト

35…第1中心電極

36…第2中心電極

41…永久磁石

43…電極

A…入力ポート

B…出力ポート

C…グランドポート

R…終端抵抗

C1…コンデンサ

Claims (6)

- 永久磁石と、

前記永久磁石により直流磁界が印加される直方体形状のフェライトと、

前記フェライトの互いに平行に位置する二つの主面に、互いに電気的に絶縁状態で交差して配置された導体膜からなる第1中心電極及び第2中心電極と、

表面に端子電極が形成された回路基板と、

を備え、

前記フェライトの主面に前記永久磁石を固定してフェライト・磁石素子が形成され、該フェライト・磁石素子は前記回路基板上にフェライトの主面が垂直方向に位置するように配置され、

前記回路基板の表面には、第1及び第2中心電極のそれぞれの端部がはんだ付けされる第1、第2及び第3端子電極が形成されており、第1及び第2端子電極は前記フェライトの長辺方向の一端部分に対向して配置され、第3端子電極は前記フェライトの長辺方向の他端部分に対向して配置されており、

第1及び第2端子電極の少なくともいずれかは前記フェライトの長辺方向とほぼ直交する第1の方向に延在され、第1及び第2端子電極の少なくともいずれかは前記第1の方向とはほぼ反対の第2の方向に延在されていること、

を特徴とする非可逆回路素子。 - 第1端子電極は第1中心電極の一端がはんだ付けされる入力端子電極であり、第2端子電極は第1中心電極の他端と第2中心電極の一端がはんだ付けされる出力端子電極であり、第3端子電極は第2中心電極の他端がはんだ付けされるグランド端子電極であることを特徴とする請求項1に記載の非可逆回路素子。

- 第1及び第2端子電極の第1の方向への延在部分にはチップ型電子部品がはんだ付けされていることを特徴とする請求項1又は請求項2に記載の非可逆回路素子。

- 第1及び第2端子電極の少なくともいずれかの第1の方向への延在部分には前記回路基板に内蔵された電極に接続したビアホール導体が接続されていることを特徴とする請求項1又は請求項2に記載の非可逆回路素子。

- 前記第1及び第2端子電極の少なくともいずれかの第1の方向への延在部分にははんだ流れ防止処理が施されていることを特徴とする請求項1ないし請求項4のいずれかに記載の非可逆回路素子。

- 前記永久磁石の前記回路基板との対向面に形成された電極が該回路基板上に設けた電極とはんだ付けされていることを特徴とする請求項1ないし請求項5のいずれかに記載の非可逆回路素子。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008193685A JP5168011B2 (ja) | 2008-07-28 | 2008-07-28 | 非可逆回路素子 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008193685A JP5168011B2 (ja) | 2008-07-28 | 2008-07-28 | 非可逆回路素子 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010034776A true JP2010034776A (ja) | 2010-02-12 |

| JP5168011B2 JP5168011B2 (ja) | 2013-03-21 |

Family

ID=41738777

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008193685A Expired - Fee Related JP5168011B2 (ja) | 2008-07-28 | 2008-07-28 | 非可逆回路素子 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5168011B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012222775A (ja) * | 2011-04-14 | 2012-11-12 | Murata Mfg Co Ltd | 非可逆回路素子及びフェライト・磁石素子 |

| DE112011100603T5 (de) | 2010-02-19 | 2013-01-31 | Ihi Corp. | Abgaswärmerückgewinnungssystem, Energieversorgungssystem und Abgaswärmerückgewinnungsverfahren |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003017906A (ja) * | 2001-06-28 | 2003-01-17 | Murata Mfg Co Ltd | 非可逆回路素子及び通信装置 |

| JP2006020052A (ja) * | 2004-07-01 | 2006-01-19 | Hitachi Metals Ltd | 2ポートアイソレータ |

| JP2006211373A (ja) * | 2005-01-28 | 2006-08-10 | Murata Mfg Co Ltd | 2ポート型非可逆回路素子及び通信装置 |

| JP2006311455A (ja) * | 2005-05-02 | 2006-11-09 | Murata Mfg Co Ltd | 非可逆回路素子、その製造方法及び通信装置 |

-

2008

- 2008-07-28 JP JP2008193685A patent/JP5168011B2/ja not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003017906A (ja) * | 2001-06-28 | 2003-01-17 | Murata Mfg Co Ltd | 非可逆回路素子及び通信装置 |

| JP2006020052A (ja) * | 2004-07-01 | 2006-01-19 | Hitachi Metals Ltd | 2ポートアイソレータ |

| JP2006211373A (ja) * | 2005-01-28 | 2006-08-10 | Murata Mfg Co Ltd | 2ポート型非可逆回路素子及び通信装置 |

| JP2006311455A (ja) * | 2005-05-02 | 2006-11-09 | Murata Mfg Co Ltd | 非可逆回路素子、その製造方法及び通信装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE112011100603T5 (de) | 2010-02-19 | 2013-01-31 | Ihi Corp. | Abgaswärmerückgewinnungssystem, Energieversorgungssystem und Abgaswärmerückgewinnungsverfahren |

| JP2012222775A (ja) * | 2011-04-14 | 2012-11-12 | Murata Mfg Co Ltd | 非可逆回路素子及びフェライト・磁石素子 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5168011B2 (ja) | 2013-03-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4380769B2 (ja) | 非可逆回路素子、その製造方法及び通信装置 | |

| JP4656186B2 (ja) | 非可逆回路素子及び複合電子部品の製造方法 | |

| JP4692679B2 (ja) | 非可逆回路素子 | |

| JP4640455B2 (ja) | フェライト・磁石素子、非可逆回路素子及び複合電子部品 | |

| JP5423814B2 (ja) | 回路モジュール | |

| JP4155342B1 (ja) | 非可逆回路素子 | |

| JP2007208943A (ja) | 非可逆回路素子及び通信装置 | |

| JP4858542B2 (ja) | 非可逆回路素子 | |

| JP5168011B2 (ja) | 非可逆回路素子 | |

| JP5056878B2 (ja) | 回路モジュール | |

| JP5573178B2 (ja) | 非可逆回路素子 | |

| JP5532945B2 (ja) | 回路モジュール | |

| JP2011055222A (ja) | 非可逆回路素子 | |

| JP5098813B2 (ja) | 非可逆回路素子及び複合電子部品 | |

| JP4760981B2 (ja) | 非可逆回路素子 | |

| JP5120101B2 (ja) | フェライト・磁石素子の製造方法 | |

| JP5083113B2 (ja) | 非可逆回路素子 | |

| JP2009296051A (ja) | フェライト・磁石素子、非可逆回路素子及び複合電子部品 | |

| JP4929488B2 (ja) | 非可逆回路素子 | |

| JP5527331B2 (ja) | 回路モジュール | |

| JP2009290422A (ja) | 非可逆回路素子 | |

| JP4192883B2 (ja) | 2ポート型非可逆回路素子および通信装置 | |

| JP4692676B2 (ja) | 非可逆回路素子 | |

| JP2010157844A (ja) | 非可逆回路素子 | |

| JP5799794B2 (ja) | 非可逆回路素子 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110615 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120606 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120612 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120727 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20120727 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121127 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121210 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5168011 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |