JP2010020801A - マイクロコンピュータ - Google Patents

マイクロコンピュータ Download PDFInfo

- Publication number

- JP2010020801A JP2010020801A JP2009245314A JP2009245314A JP2010020801A JP 2010020801 A JP2010020801 A JP 2010020801A JP 2009245314 A JP2009245314 A JP 2009245314A JP 2009245314 A JP2009245314 A JP 2009245314A JP 2010020801 A JP2010020801 A JP 2010020801A

- Authority

- JP

- Japan

- Prior art keywords

- memory

- clock

- data

- microcomputer

- ddr

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 230000015654 memory Effects 0.000 claims abstract description 135

- 230000001360 synchronised effect Effects 0.000 claims abstract description 16

- 230000000630 rising effect Effects 0.000 claims abstract description 12

- 239000004065 semiconductor Substances 0.000 claims description 9

- 230000004044 response Effects 0.000 abstract 1

- 239000000758 substrate Substances 0.000 description 8

- 238000010586 diagram Methods 0.000 description 6

- 230000008859 change Effects 0.000 description 5

- 230000010363 phase shift Effects 0.000 description 5

- 238000000034 method Methods 0.000 description 3

- 230000003111 delayed effect Effects 0.000 description 2

- 230000008901 benefit Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

Images

Landscapes

- Microcomputers (AREA)

Abstract

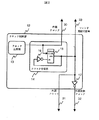

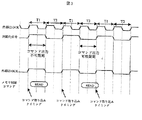

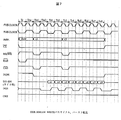

【解決手段】中央処理ユニット、メモリ制御手段、及びクロック制御部を有するマイクロコンピュータは、クロック制御部から供給されたクロックを外部クロックとしてマイクロコンピュータの外部に出力し、外部クロックを反転したクロックをマイクロコンピュータの外部に出力する。メモリ制御手段は、前記クロックに対応し、第1の電位状態と第2の電位状態とに遷移するデータストローブ信号を生成する。メモリ制御手段によって制御されるメモリは、データストローブ信号の立ち上がりエッジと立ち下がりエッジに同期してデータの入出力を行うDDR方式の同期型メモリである。メモリ制御手段は、同期型メモリにデータを書き込むとき、前記データストローブ信号の立ち上がりエッジと立ち下がりエッジに同期してデータを外部に出力する。

【選択図】図1

Description

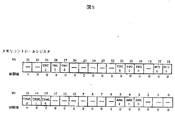

メモリインタフェースモジュールには、クロック制御部12から出力される、プロセッサの内部クロックと、前記内部クロックの1/2の周波数のコマンド同期化信号33とが供給されている。コマンド同期化信号は、プロセッサ外部のDDR−SDRAMに供給される外部クロックと同じ周波数で、同じ位相をもったクロックである。メモリインタフェースモジュールは、メモリが外部クロック31の立ち上がりで各種コマンドを受け取れるよう制御する。メモリは、外部クロックがLOWの期間(T2)にメモリに対して出力されたコマンドについては、外部クロックの次の立ち上がりの時点で受け取ることが可能であるが、外部クロックがHIGHの期間にメモリに対して与えられたコマンドについては受け取ることが出来ない。そのためコマンド出力可能期間、つまり外部クロックがLOWのときにのみ制御信号を出力し、コマンド出力不可期間には制御信号の出力はしないようにする必要がある。

メモリ動作の基準となる外部クロックと、外部クロックの2倍の周波数の内部クロックを共にプロセッサ内部で生成するため、外部クロックと内部クロックの位相差の制御が可能となる。また、外部クロックの2倍の周波数の内部クロックを使用することで、外部クロックに対して90度の位相シフトを容易に行うことが出来る。

2 CPU/Cacheモジュール

3 DMAC

4 リクエスト制御部

5 レジスタR/W制御部

6 レジスタ

7 外部バス制御部

8 アドレス制御部

9 制御信号

10 データ制御部

11 データバッファ

12 クロック制御部

13 クロック生成部

14 クロック分周器

15 ラッチ

16 分周器用インバータ

17 外部クロック用インバータ

20 マイクロプロセッサ

21 ダブルデータレートシンクロナスDRAM(DDR−SDRAM)

30 内部クロック

31 外部クロック

32 反転クロック

33 出力コマンド同期化信号

34 アドレス

35 メモリ制御信号

36 データ

101 レジスタアクセスリクエスト

102 レジスタ書き込み信号

103 データ

104 メモリアクセスリクエスト

105 メモリタイミング情報

106 メモリアドレス情報

107 リクエストアドレス

Claims (1)

- 中央処理ユニットと、

前記中央処理ユニットに接続されたメモリ制御手段と、

前記中央処理ユニットと前記メモリ制御手段とにクロックを供給するためのクロック制御部と、を有し、一つの半導体チップ上に形成されたマイクロコンピュータであって、

前記マイクロコンピュータは、前記クロック制御部から供給されたクロックを外部クロックとしてマイクロコンピュータの外部に出力し、前記外部クロックを反転した外部反転クロックをマイクロコンピュータの外部に出力し、

前記メモリ制御手段は、前記クロックに対応し、第1の電位状態と第2の電位状態とに遷移するデータストローブ信号を生成可能であり、

前記メモリ制御手段によって制御されるメモリは、前記データストローブ信号の立ち上がりエッジと立ち下がりエッジに同期してデータの入出力を行うことが可能なダブルデータレート方式の同期型メモリであり、

前記メモリ制御手段は、前記同期型メモリにデータを書き込むとき、前記データストローブ信号の立ち上がりエッジと立ち下がりエッジに同期してデータを外部に出力し、

前記中央処理ユニットは、前記同期型メモリにアクセスするためのメモリアドレスを生成し、

前記メモリ制御手段は、前記外部クロックに同期して前記メモリアドレスを出力することが可能であることを特徴とするマイクロコンピュータ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009245314A JP4785153B2 (ja) | 2009-10-26 | 2009-10-26 | マイクロコンピュータ及びマイコンシステム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009245314A JP4785153B2 (ja) | 2009-10-26 | 2009-10-26 | マイクロコンピュータ及びマイコンシステム |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006155841A Division JP2006244528A (ja) | 2006-06-05 | 2006-06-05 | マイクロコンピュータ |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011048604A Division JP2011118932A (ja) | 2011-03-07 | 2011-03-07 | マイクロコンピュータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010020801A true JP2010020801A (ja) | 2010-01-28 |

| JP4785153B2 JP4785153B2 (ja) | 2011-10-05 |

Family

ID=41705546

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009245314A Expired - Fee Related JP4785153B2 (ja) | 2009-10-26 | 2009-10-26 | マイクロコンピュータ及びマイコンシステム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4785153B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101113188B1 (ko) | 2010-09-30 | 2012-02-16 | 주식회사 하이닉스반도체 | 동작 속도가 가변되는 비휘발성 메모리 장치 및 이를 위한 상보신호 제어 방법 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05120114A (ja) * | 1991-04-23 | 1993-05-18 | Texas Instr Inc <Ti> | マイクロプロセツサと同期して動作するランダムアクセスメモリ |

| JPH07105173A (ja) * | 1993-09-30 | 1995-04-21 | Hitachi Ltd | データ処理装置 |

| JPH07160249A (ja) * | 1993-10-15 | 1995-06-23 | Hitachi Ltd | データプロセッサ及びデータ処理システム |

| JPH07282000A (ja) * | 1994-04-04 | 1995-10-27 | Hitachi Ltd | バスインタフェース回路及びデータ転送システム |

| JPH09106671A (ja) * | 1995-09-11 | 1997-04-22 | Samsung Electron Co Ltd | 半導体メモリ装置とその読出及び書込方法 |

| JPH10199239A (ja) * | 1996-12-27 | 1998-07-31 | Fujitsu Ltd | 半導体記憶装置システム及び半導体記憶装置 |

| JPH11505047A (ja) * | 1995-05-05 | 1999-05-11 | シリコン、グラフィクス、インコーポレイテッド | ソース同期クロック型データリンク |

-

2009

- 2009-10-26 JP JP2009245314A patent/JP4785153B2/ja not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05120114A (ja) * | 1991-04-23 | 1993-05-18 | Texas Instr Inc <Ti> | マイクロプロセツサと同期して動作するランダムアクセスメモリ |

| JPH07105173A (ja) * | 1993-09-30 | 1995-04-21 | Hitachi Ltd | データ処理装置 |

| JPH07160249A (ja) * | 1993-10-15 | 1995-06-23 | Hitachi Ltd | データプロセッサ及びデータ処理システム |

| JPH07282000A (ja) * | 1994-04-04 | 1995-10-27 | Hitachi Ltd | バスインタフェース回路及びデータ転送システム |

| JPH11505047A (ja) * | 1995-05-05 | 1999-05-11 | シリコン、グラフィクス、インコーポレイテッド | ソース同期クロック型データリンク |

| JPH09106671A (ja) * | 1995-09-11 | 1997-04-22 | Samsung Electron Co Ltd | 半導体メモリ装置とその読出及び書込方法 |

| JPH10199239A (ja) * | 1996-12-27 | 1998-07-31 | Fujitsu Ltd | 半導体記憶装置システム及び半導体記憶装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101113188B1 (ko) | 2010-09-30 | 2012-02-16 | 주식회사 하이닉스반도체 | 동작 속도가 가변되는 비휘발성 메모리 장치 및 이를 위한 상보신호 제어 방법 |

| US8482996B2 (en) | 2010-09-30 | 2013-07-09 | SK Hynix Inc. | Nonvolatile memory apparatus with changeable operation speed and related signal control method |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4785153B2 (ja) | 2011-10-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2002007200A (ja) | メモリ制御装置及び動作切替方法並びにインターフェース装置、半導体集積チップ、記録媒体 | |

| USRE44230E1 (en) | Clock signal generation apparatus for use in semiconductor memory device and its method | |

| JP4723679B2 (ja) | 半導体記憶装置、メモリシステム、及び半導体記憶装置のリフレッシュ制御方法 | |

| US7716443B2 (en) | Apparatus and method for controlling memory interface | |

| JP2002358231A (ja) | メモリ制御システム | |

| JPH1116349A (ja) | 同期型半導体記憶装置 | |

| JP3272914B2 (ja) | 同期型半導体装置 | |

| JP2010192031A (ja) | 半導体記憶装置及びこれを備えるメモリモジュール、並びに、データ処理システム | |

| JP5733126B2 (ja) | メモリインタフェース回路及びタイミング調整方法 | |

| JP2010165422A (ja) | 半導体記憶装置及びそのリード待ち時間調整方法、メモリシステム、並びに半導体装置 | |

| JP2008112434A (ja) | メモリクロック信号を送信するための、方法および回路 | |

| JP2002074952A (ja) | 同期型半導体記憶装置及びその入力回路の制御方法 | |

| CN112041925A (zh) | 用于在读取操作期间控制数据选通信号的系统及方法 | |

| JP2000030456A (ja) | メモリデバイス | |

| JP4079507B2 (ja) | メモリ制御システムおよびメモリ制御方法 | |

| JP2002304885A (ja) | 半導体集積回路 | |

| JP2011118932A (ja) | マイクロコンピュータ | |

| JP3865972B2 (ja) | マイクロコンピュータおよびマイクロコンピュータを用いたシステム | |

| JP2009282721A (ja) | メモリコントローラ、メモリコントロールシステム及びメモリ遅延量制御方法 | |

| JP4785153B2 (ja) | マイクロコンピュータ及びマイコンシステム | |

| JP2003173290A (ja) | メモリ制御装置 | |

| CN101609439A (zh) | 具有分时总线的电子系统与共用电子系统的总线的方法 | |

| JP2006244528A (ja) | マイクロコンピュータ | |

| JP2008192264A (ja) | 半導体記憶装置 | |

| US7103707B2 (en) | Access control unit and method for use with synchronous dynamic random access memory device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091125 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100527 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101220 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110105 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110307 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110421 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110615 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110707 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110708 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140722 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |