JP2010010371A - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP2010010371A JP2010010371A JP2008167620A JP2008167620A JP2010010371A JP 2010010371 A JP2010010371 A JP 2010010371A JP 2008167620 A JP2008167620 A JP 2008167620A JP 2008167620 A JP2008167620 A JP 2008167620A JP 2010010371 A JP2010010371 A JP 2010010371A

- Authority

- JP

- Japan

- Prior art keywords

- pmosfet

- active region

- film

- nmosfet

- compressive stress

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 42

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 16

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims abstract description 53

- 229910052814 silicon oxide Inorganic materials 0.000 claims abstract description 53

- 238000002955 isolation Methods 0.000 claims abstract description 37

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 44

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 44

- 239000000758 substrate Substances 0.000 claims description 25

- 238000005530 etching Methods 0.000 claims description 9

- 238000000034 method Methods 0.000 claims description 6

- 238000005268 plasma chemical vapour deposition Methods 0.000 claims description 3

- 238000002230 thermal chemical vapour deposition Methods 0.000 claims description 2

- 239000010408 film Substances 0.000 claims 25

- 239000013039 cover film Substances 0.000 claims 3

- 230000007423 decrease Effects 0.000 abstract description 3

- 230000002708 enhancing effect Effects 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 16

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 15

- 229910052710 silicon Inorganic materials 0.000 description 15

- 239000010703 silicon Substances 0.000 description 15

- 239000012535 impurity Substances 0.000 description 8

- 229910021332 silicide Inorganic materials 0.000 description 7

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical group [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 7

- 238000009792 diffusion process Methods 0.000 description 6

- 239000007789 gas Substances 0.000 description 5

- 150000004767 nitrides Chemical class 0.000 description 5

- 238000001020 plasma etching Methods 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- 230000001133 acceleration Effects 0.000 description 4

- 230000000052 comparative effect Effects 0.000 description 4

- 238000000151 deposition Methods 0.000 description 4

- 239000011229 interlayer Substances 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 230000008021 deposition Effects 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 239000012159 carrier gas Substances 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 229910000077 silane Inorganic materials 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000002800 charge carrier Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- MROCJMGDEKINLD-UHFFFAOYSA-N dichlorosilane Chemical compound Cl[SiH2]Cl MROCJMGDEKINLD-UHFFFAOYSA-N 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- VEDJZFSRVVQBIL-UHFFFAOYSA-N trisilane Chemical compound [SiH3][SiH2][SiH3] VEDJZFSRVVQBIL-UHFFFAOYSA-N 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823878—Complementary field-effect transistors, e.g. CMOS isolation region manufacturing related aspects, e.g. to avoid interaction of isolation region with adjacent structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/0217—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon nitride not containing oxygen, e.g. SixNy or SixByNz

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/314—Inorganic layers

- H01L21/318—Inorganic layers composed of nitrides

- H01L21/3185—Inorganic layers composed of nitrides of siliconnitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76832—Multiple layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823807—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the channel structures, e.g. channel implants, halo or pocket implants, or channel materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3157—Partial encapsulation or coating

- H01L23/3192—Multilayer coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7842—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate

- H01L29/7843—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate the means being an applied insulating layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7842—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate

- H01L29/7846—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate the means being located in the lateral device isolation region, e.g. STI

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

- H10B10/12—Static random access memory [SRAM] devices comprising a MOSFET load element

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/665—Unipolar field-effect transistors with an insulated gate, i.e. MISFET using self aligned silicidation, i.e. salicide

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66575—Lateral single gate silicon transistors where the source and drain or source and drain extensions are self-aligned to the sides of the gate

- H01L29/6659—Lateral single gate silicon transistors where the source and drain or source and drain extensions are self-aligned to the sides of the gate with both lightly doped source and drain extensions and source and drain self-aligned to the sides of the gate, e.g. lightly doped drain [LDD] MOSFET, double diffused drain [DDD] MOSFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Ceramic Engineering (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Chemical Vapour Deposition (AREA)

- Element Separation (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Formation Of Insulating Films (AREA)

- Semiconductor Memories (AREA)

Abstract

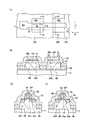

【解決手段】半導体装置は、NMOSFET用活性領域AR1、PMOSFET用活性領域AR2を画定する素子分離溝STと、素子分離溝の下部のみを埋め、その上に凹部を画定する酸化シリコン膜OXと、NMOSFET領域AR1に形成されたNMOSFETと、PMOSFET領域AR2に形成されたPMOSFETと、NMOSFET構造を覆い、NMOSFET用活性領域AR1の周囲における凹部上及びPMOSFET用活性領域AR2のゲート幅方向外側における凹部上に延在して形成された引張応力膜TSFと、PMOSFET構造を覆い、PMOSFET用活性領域AR2のチャネル長方向外側における凹部上に延在して形成された圧縮応力膜CSFとを有する。

【選択図】図1

Description

半導体基板と、

前記半導体基板表面部に形成され、NMOSFET用活性領域、PMOSFET用活性領域を画定する素子分離溝と、

前記素子分離溝の下部のみを埋め、その上に凹部を画定する酸化シリコン膜と、

前記NMOSFET用活性領域に形成され、絶縁ゲート電極構造、n型ソース/ドレイン領域を有するNMOSFET構造と、

前記PMOSFET用活性領域に形成され、絶縁ゲート電極構造、p型ソース/ドレイン領域を有するPMOSFET構造と、

前記NMOSFET構造を覆い、前記NMOSFET用活性領域周囲の前記凹部上及び前記PMOSFET用活性領域のゲート幅方向外側における前記凹部上に延在して形成された引張応力膜と、

前記PMOSFET構造を覆い、前記PMOSFET用活性領域のチャネル長方向外側における前記凹部上に延在して形成された圧縮応力膜と、

を有する半導体装置

が提供される。

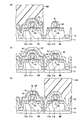

(a)半導体基板表面部に、NMOSFET用活性領域、PMOSFET用活性領域を画定する素子分離溝を形成する工程と;

(b)前記素子分離溝に圧縮応力を有する酸化シリコン膜を埋め込む工程と、

(c)NMOSFET用活性領域に絶縁ゲート電極構造、n型ソース/ドレイン領域を有するNMOSFET構造、前記PMOSFET用活性領域に絶縁ゲート電極構造、p型ソース/ドレイン領域を有するPMOSFET構造を形成する工程と;

(d)前記素子分離溝に埋め込まれた酸化シリコン膜の上部を除去し、凹部を形成する工程と、

(e)前記NMOSFET用活性領域を覆い、前記NMOSFET用活性領域周囲の前記凹部上及び前記PMOSFET用活性領域のチャネル幅方向外側における前記凹部上に延在する引張応力絶縁膜を形成する工程と、

(f)前記PMOSFET用活性領域を覆い、前記PMOSFET用活性領域のチャネル長方向外側における前記凹部上に延在する圧縮応力絶縁膜を形成する工程と、

を含む半導体装置の製造方法

が提供される。

12 酸化シリコン膜、

13 窒化シリコン膜、

14 酸化シリコン膜、

AR 活性領域、

ST 素子分離溝、

TSF 引張応力膜、

CSF 圧縮応力膜、

EX エクステンション領域、

SD ソース/ドレイン領域、

PW p型ウェル、

NW n型ウェル、

15 ゲート絶縁膜、

16 ゲート電極(多結晶シリコン膜)、

18 引張応力窒化シリコン膜、

19 酸化シリコン膜、

20 圧縮応力窒化シリコン膜、

21 エクステンション領域、

22 ソース/ドレイン拡散層、

SW サイドウォール、

SL シリサイド領域、

Claims (10)

- 半導体基板と、

前記半導体基板表面部に形成され、NMOSFET用活性領域、PMOSFET用活性領域を画定する素子分離溝と、

前記素子分離溝の下部のみを埋め、その上に凹部を画定する酸化シリコン膜と、

前記NMOSFET用活性領域に形成され、絶縁ゲート電極構造、n型ソース/ドレイン領域を有するNMOSFET構造と、

前記PMOSFET用活性領域に形成され、絶縁ゲート電極構造、p型ソース/ドレイン領域を有するPMOSFET構造と、

前記NMOSFET構造を覆い、前記NMOSFET用活性領域周囲の前記凹部上及び前記PMOSFET用活性領域のゲート幅方向外側における前記凹部上に延在して形成された引張応力膜と、

前記PMOSFET構造を覆い、前記PMOSFET用活性領域のチャネル長方向外側における前記凹部上に延在して形成された圧縮応力膜と、

を有する半導体装置。 - 前記NMOSFET構造と前記PMOSFET構造とが平行なチャネル長方向を有し、前記引張応力膜、前記圧縮応力膜が前記チャネル長方向に沿ったストライプ状に形成されている請求項1記載の半導体装置。

- 前記凹部の深さは、前記ソース/ドレイン領域より深く、前記素子分離溝の深さの半分以下である請求項1または2記載の半導体装置。

- 前記引張応力膜、前記圧縮応力膜が接している請求項1〜3のいずれか1項記載の半導体装置。

- 前記引張応力膜、圧縮応力膜が窒化シリコン膜である請求項1〜4のいずれか1項記載の半導体装置。

- (a)半導体基板表面部に、NMOSFET用活性領域、PMOSFET用活性領域を画定する素子分離溝を形成する工程と;

(b)前記素子分離溝に圧縮応力を有する酸化シリコン膜を埋め込む工程と、

(c)NMOSFET用活性領域に絶縁ゲート電極構造、n型ソース/ドレイン領域を有するNMOSFET構造、前記PMOSFET用活性領域に絶縁ゲート電極構造、p型ソース/ドレイン領域を有するPMOSFET構造を形成する工程と;

(d)前記素子分離溝に埋め込まれた酸化シリコン膜の上部を除去し、凹部を形成する工程と、

(e)前記NMOSFET用活性領域を覆い、前記NMOSFET用活性領域周囲の前記凹部上及び前記PMOSFET用活性領域のチャネル幅方向外側における前記凹部上に延在する引張応力絶縁膜を形成する工程と、

(f)前記PMOSFET用活性領域を覆い、前記PMOSFET用活性領域のチャネル長方向外側における前記凹部上に延在する圧縮応力絶縁膜を形成する工程と、

を含む半導体装置の製造方法。 - 前記工程(e)が、前記半導体基板上に引張応力絶縁膜を堆積し、前記PMOSFET用活性領域、および前記PMOSFET用活性領域のチャネル長方向外側における前記凹部の上から前記引張応力絶縁膜を除去し、

前記工程(f)が、前記半導体基板上に圧縮応力絶縁膜を堆積し、前記NMOSFET用活性領域、前記NMOSFET用活性領域周囲の前記凹部及び前記PMOSFET用活性領域のチャネル幅方向外側における前記凹部の上から前記圧縮応力絶縁膜を除去する、

請求項6記載の半導体装置の製造方法。 - 前記工程(e)における引張応力膜、前記工程(f)における圧縮応力膜が、窒化シリコン膜である請求項7記載の半導体装置の製造方法。

- 前記工程(e)が、前記引張応力膜を熱CVDで形成し、前記工程(f)が前記圧縮応力膜をプラズマCVDで形成する請求項8記載の半導体装置の製造方法。

- 前記工程(e)、(f)の内、先に行われる工程が前記窒化シリコン膜の上に酸化シリコンカバー膜を堆積し、前記酸化シリコンカバー膜を前記窒化シリコン膜と同一パターンにエッチングし、前記工程(e)、(f)の内、後に行われる工程が前記酸化シリコンカバー膜をエッチングストッパとして使用する請求項8又は9記載の半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008167620A JP5163311B2 (ja) | 2008-06-26 | 2008-06-26 | 半導体装置及びその製造方法 |

| US12/411,602 US8030710B2 (en) | 2008-06-26 | 2009-03-26 | Strained semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008167620A JP5163311B2 (ja) | 2008-06-26 | 2008-06-26 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010010371A true JP2010010371A (ja) | 2010-01-14 |

| JP5163311B2 JP5163311B2 (ja) | 2013-03-13 |

Family

ID=41446347

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008167620A Expired - Fee Related JP5163311B2 (ja) | 2008-06-26 | 2008-06-26 | 半導体装置及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8030710B2 (ja) |

| JP (1) | JP5163311B2 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8218353B1 (en) * | 2009-09-16 | 2012-07-10 | Altera Corporation | Memory element circuitry with stressed transistors |

| DE102010038746B4 (de) | 2010-07-30 | 2013-11-14 | GLOBALFOUNDRIES Dresden Module One Ltd. Liability Company & Co. KG | Verfahren zum Reduzieren der Topographie in Isolationsgebieten eines Halbleiterbauelements durch Anwenden einer Abscheide/Ätzsequenz vor der Herstellung des Zwischenschichtdielektrikums |

| US8453100B2 (en) * | 2010-09-01 | 2013-05-28 | International Business Machines Corporation | Circuit analysis using transverse buckets |

| US8378428B2 (en) * | 2010-09-29 | 2013-02-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Metal gate structure of a semiconductor device |

| CN102881694A (zh) | 2011-07-14 | 2013-01-16 | 中国科学院微电子研究所 | 半导体器件及其制造方法 |

| US10043903B2 (en) * | 2015-12-21 | 2018-08-07 | Samsung Electronics Co., Ltd. | Semiconductor devices with source/drain stress liner |

| CN106910739B (zh) * | 2015-12-21 | 2022-01-11 | 三星电子株式会社 | 半导体器件 |

| KR102375583B1 (ko) * | 2015-12-21 | 2022-03-16 | 삼성전자주식회사 | 반도체 장치 및 이의 제조 방법 |

| US10736557B2 (en) | 2016-03-30 | 2020-08-11 | Brain F.I.T. Imaging, LLC | Methods and magnetic imaging devices to inventory human brain cortical function |

| KR102524806B1 (ko) * | 2016-08-11 | 2023-04-25 | 삼성전자주식회사 | 콘택 구조체를 포함하는 반도체 소자 |

| CA3077705A1 (en) | 2017-10-03 | 2019-04-11 | Braint F.I.T. Imaging, Llc | Methods and magnetic imaging devices to inventory human brain cortical function |

| EP3946034A4 (en) | 2019-04-03 | 2023-01-11 | Brain F.I.T. Imaging, LLC | METHODS AND MAGNETIC TOMOGRAPHY DEVICES FOR THE INVENTORY OF CORCOAL FUNCTION OF THE HUMAN BRAIN |

| FR3100084B1 (fr) * | 2019-08-23 | 2021-10-01 | Commissariat Energie Atomique | procédé de fabrication de composants micro-électroniques |

| US11450573B2 (en) * | 2020-06-17 | 2022-09-20 | Globalfoundries U.S. Inc. | Structure with different stress-inducing isolation dielectrics for different polarity FETs |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003158241A (ja) * | 2001-11-26 | 2003-05-30 | Hitachi Ltd | 半導体装置及び製造方法 |

| JP2006229071A (ja) * | 2005-02-18 | 2006-08-31 | Fujitsu Ltd | 半導体装置 |

| JP2006278754A (ja) * | 2005-03-29 | 2006-10-12 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2006286889A (ja) * | 2005-03-31 | 2006-10-19 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2008053518A (ja) * | 2006-08-25 | 2008-03-06 | Sony Corp | 半導体装置 |

| JP2008066484A (ja) * | 2006-09-06 | 2008-03-21 | Fujitsu Ltd | Cmos半導体装置とその製造方法 |

| JP2009527928A (ja) * | 2006-02-24 | 2009-07-30 | フリースケール セミコンダクター インコーポレイテッド | ソース/ドレインストレッサ、及び中間誘電体層ストレッサを統合する半導体の製造方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003086708A (ja) | 2000-12-08 | 2003-03-20 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP4994581B2 (ja) | 2004-06-29 | 2012-08-08 | 富士通セミコンダクター株式会社 | 半導体装置 |

| US7600207B2 (en) * | 2006-02-27 | 2009-10-06 | Synopsys, Inc. | Stress-managed revision of integrated circuit layouts |

| US20080237733A1 (en) * | 2007-03-27 | 2008-10-02 | International Business Machines Corporation | Structure and method to enhance channel stress by using optimized sti stress and nitride capping layer stress |

-

2008

- 2008-06-26 JP JP2008167620A patent/JP5163311B2/ja not_active Expired - Fee Related

-

2009

- 2009-03-26 US US12/411,602 patent/US8030710B2/en not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003158241A (ja) * | 2001-11-26 | 2003-05-30 | Hitachi Ltd | 半導体装置及び製造方法 |

| JP2006229071A (ja) * | 2005-02-18 | 2006-08-31 | Fujitsu Ltd | 半導体装置 |

| JP2006278754A (ja) * | 2005-03-29 | 2006-10-12 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2006286889A (ja) * | 2005-03-31 | 2006-10-19 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2009527928A (ja) * | 2006-02-24 | 2009-07-30 | フリースケール セミコンダクター インコーポレイテッド | ソース/ドレインストレッサ、及び中間誘電体層ストレッサを統合する半導体の製造方法 |

| JP2008053518A (ja) * | 2006-08-25 | 2008-03-06 | Sony Corp | 半導体装置 |

| JP2008066484A (ja) * | 2006-09-06 | 2008-03-21 | Fujitsu Ltd | Cmos半導体装置とその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20090321840A1 (en) | 2009-12-31 |

| JP5163311B2 (ja) | 2013-03-13 |

| US8030710B2 (en) | 2011-10-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5163311B2 (ja) | 半導体装置及びその製造方法 | |

| US8680576B2 (en) | CMOS device and method of forming the same | |

| US7737495B2 (en) | Semiconductor device having inter-layers with stress levels corresponding to the transistor type | |

| JP5132928B2 (ja) | 半導体装置 | |

| JP2009111200A (ja) | 半導体装置及びその製造方法 | |

| US20080054366A1 (en) | CMOS semiconductor device having tensile and compressive stress films | |

| JP5268859B2 (ja) | 半導体装置 | |

| WO2015125205A1 (ja) | 半導体装置の製造方法、及び、半導体装置 | |

| JP2012160637A (ja) | 半導体装置及びその製造方法、並びにsoi基板及びその製造方法 | |

| JP5137378B2 (ja) | 半導体装置及びその製造方法 | |

| JP2007324391A (ja) | 半導体装置及びその製造方法 | |

| JP2006351975A (ja) | 半導体装置およびその製造方法 | |

| JP2004063591A (ja) | 半導体装置とその製造方法 | |

| JP2004193166A (ja) | 半導体装置 | |

| JP2010098157A (ja) | 半導体装置の製造方法 | |

| JP2007173356A (ja) | 半導体装置およびその製造方法 | |

| JP5132943B2 (ja) | 半導体装置 | |

| US7956390B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP2008182118A (ja) | 半導体装置及びその製造方法。 | |

| JP4630235B2 (ja) | 半導体装置及びその製造方法 | |

| JP2010183065A (ja) | 半導体およびその製造方法 | |

| JP2009170523A (ja) | 半導体装置およびその製造方法 | |

| JP2005311000A (ja) | 半導体装置及びその製造方法 | |

| JP2006060175A (ja) | 半導体装置及びその製造方法 | |

| JP6033938B2 (ja) | 半導体装置の製造方法、及び、半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110125 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121112 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121120 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121203 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151228 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5163311 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |