JP2006261681A - ポリシリコン薄膜トランジスタ基板の製造方法及び液晶表示装置 - Google Patents

ポリシリコン薄膜トランジスタ基板の製造方法及び液晶表示装置 Download PDFInfo

- Publication number

- JP2006261681A JP2006261681A JP2006075342A JP2006075342A JP2006261681A JP 2006261681 A JP2006261681 A JP 2006261681A JP 2006075342 A JP2006075342 A JP 2006075342A JP 2006075342 A JP2006075342 A JP 2006075342A JP 2006261681 A JP2006261681 A JP 2006261681A

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- polysilicon

- thin film

- film transistor

- liquid crystal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000000758 substrate Substances 0.000 title claims abstract description 157

- 229910021420 polycrystalline silicon Inorganic materials 0.000 title claims abstract description 101

- 229920005591 polysilicon Polymers 0.000 title claims abstract description 101

- 239000010409 thin film Substances 0.000 title claims abstract description 57

- 239000004973 liquid crystal related substance Substances 0.000 title claims abstract description 46

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 28

- 238000000034 method Methods 0.000 title claims description 40

- 239000013078 crystal Substances 0.000 claims abstract description 71

- 238000005498 polishing Methods 0.000 claims abstract description 61

- 238000004140 cleaning Methods 0.000 claims abstract description 23

- 239000004065 semiconductor Substances 0.000 claims abstract description 21

- 239000000126 substance Substances 0.000 claims abstract description 21

- 229910021417 amorphous silicon Inorganic materials 0.000 claims description 33

- 239000002002 slurry Substances 0.000 claims description 17

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 claims description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 5

- 238000000059 patterning Methods 0.000 claims description 5

- 229910021642 ultra pure water Inorganic materials 0.000 claims description 5

- 239000012498 ultrapure water Substances 0.000 claims description 5

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 claims description 3

- CETPSERCERDGAM-UHFFFAOYSA-N ceric oxide Chemical compound O=[Ce]=O CETPSERCERDGAM-UHFFFAOYSA-N 0.000 claims description 3

- 229910000422 cerium(IV) oxide Inorganic materials 0.000 claims description 3

- 239000002245 particle Substances 0.000 claims description 2

- 239000000377 silicon dioxide Substances 0.000 claims description 2

- 238000004506 ultrasonic cleaning Methods 0.000 claims description 2

- 239000003990 capacitor Substances 0.000 description 12

- 238000002425 crystallisation Methods 0.000 description 11

- 238000010586 diagram Methods 0.000 description 8

- 230000008569 process Effects 0.000 description 7

- 238000003860 storage Methods 0.000 description 7

- 239000010408 film Substances 0.000 description 5

- 238000010438 heat treatment Methods 0.000 description 5

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 230000008025 crystallization Effects 0.000 description 4

- 229910052710 silicon Inorganic materials 0.000 description 4

- 239000010703 silicon Substances 0.000 description 4

- 239000003082 abrasive agent Substances 0.000 description 3

- 238000005224 laser annealing Methods 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- MCMNRKCIXSYSNV-UHFFFAOYSA-N Zirconium dioxide Chemical compound O=[Zr]=O MCMNRKCIXSYSNV-UHFFFAOYSA-N 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 238000001816 cooling Methods 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 239000010419 fine particle Substances 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- AMWRITDGCCNYAT-UHFFFAOYSA-L hydroxy(oxo)manganese;manganese Chemical compound [Mn].O[Mn]=O.O[Mn]=O AMWRITDGCCNYAT-UHFFFAOYSA-L 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000000737 periodic effect Effects 0.000 description 2

- 230000010287 polarization Effects 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 229910006404 SnO 2 Inorganic materials 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000007517 polishing process Methods 0.000 description 1

- 239000011148 porous material Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000007711 solidification Methods 0.000 description 1

- 230000008023 solidification Effects 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

- H10D86/021—Manufacture or treatment of multiple TFTs

- H10D86/0221—Manufacture or treatment of multiple TFTs comprising manufacture, treatment or patterning of TFT semiconductor bodies

- H10D86/0223—Manufacture or treatment of multiple TFTs comprising manufacture, treatment or patterning of TFT semiconductor bodies comprising crystallisation of amorphous, microcrystalline or polycrystalline semiconductor materials

- H10D86/0229—Manufacture or treatment of multiple TFTs comprising manufacture, treatment or patterning of TFT semiconductor bodies comprising crystallisation of amorphous, microcrystalline or polycrystalline semiconductor materials characterised by control of the annealing or irradiation parameters

-

- E—FIXED CONSTRUCTIONS

- E21—EARTH OR ROCK DRILLING; MINING

- E21B—EARTH OR ROCK DRILLING; OBTAINING OIL, GAS, WATER, SOLUBLE OR MELTABLE MATERIALS OR A SLURRY OF MINERALS FROM WELLS

- E21B17/00—Drilling rods or pipes; Flexible drill strings; Kellies; Drill collars; Sucker rods; Cables; Casings; Tubings

- E21B17/10—Wear protectors; Centralising devices, e.g. stabilisers

- E21B17/1035—Wear protectors; Centralising devices, e.g. stabilisers for plural rods, pipes or lines, e.g. for control lines

-

- E—FIXED CONSTRUCTIONS

- E02—HYDRAULIC ENGINEERING; FOUNDATIONS; SOIL SHIFTING

- E02F—DREDGING; SOIL-SHIFTING

- E02F5/00—Dredgers or soil-shifting machines for special purposes

- E02F5/16—Machines for digging other holes in the soil

- E02F5/20—Machines for digging other holes in the soil for vertical holes

-

- E—FIXED CONSTRUCTIONS

- E21—EARTH OR ROCK DRILLING; MINING

- E21B—EARTH OR ROCK DRILLING; OBTAINING OIL, GAS, WATER, SOLUBLE OR MELTABLE MATERIALS OR A SLURRY OF MINERALS FROM WELLS

- E21B17/00—Drilling rods or pipes; Flexible drill strings; Kellies; Drill collars; Sucker rods; Cables; Casings; Tubings

- E21B17/10—Wear protectors; Centralising devices, e.g. stabilisers

- E21B17/1085—Wear protectors; Blast joints; Hard facing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6741—Group IV materials, e.g. germanium or silicon carbide

- H10D30/6743—Silicon

- H10D30/6745—Polycrystalline or microcrystalline silicon

Landscapes

- Engineering & Computer Science (AREA)

- Mining & Mineral Resources (AREA)

- Geology (AREA)

- Life Sciences & Earth Sciences (AREA)

- Mechanical Engineering (AREA)

- General Life Sciences & Earth Sciences (AREA)

- Fluid Mechanics (AREA)

- Environmental & Geological Engineering (AREA)

- Physics & Mathematics (AREA)

- Geochemistry & Mineralogy (AREA)

- Civil Engineering (AREA)

- General Engineering & Computer Science (AREA)

- Structural Engineering (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Mechanical Treatment Of Semiconductor (AREA)

- Recrystallisation Techniques (AREA)

Abstract

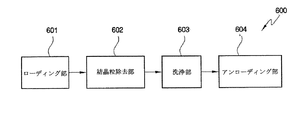

【解決手段】ポリシリコン結晶粒が形成された基板をローディングする段階と、ポリシリコン結晶粒の間の結晶粒界で突出している結晶粒を化学的機械的研磨によって除去して研磨された基板を形成する段階と、研磨された基板を洗浄して洗浄された基板を形成する段階と、洗浄された基板をアンローディングする段階とを有する。

【選択図】 図6

Description

110 下部基板

401 バッファ層

402 非晶質シリコン層

402’ ポリシリコン層

600 結晶粒除去装置

601 ローディング部

602 結晶粒除去部

603 洗浄部

604 アンローディング部

700 化学的機械的研磨装置

701 研磨テーブル

702 研磨パッド

703 スラリー供給部

704 パッドコンディショナー

705 ヘッド

Claims (20)

- ポリシリコン結晶粒が形成された基板をローディングする段階と、

前記ポリシリコン結晶粒の間の結晶粒界から突出している結晶粒を化学的機械的研磨によって除去して研磨された基板を形成する段階と、

前記研磨された基板を洗浄して洗浄された基板を形成する段階と、

前記洗浄された基板をアンローディングする段階とを有することを特徴とするポリシリコン薄膜トランジスタ基板の製造方法。 - 前記ポリシリコン結晶粒を除去して研磨された基板を形成する段階は、前記基板を研磨パッドの表面に密着させた状態で前記研磨パッドを回転させる同時に前記基板と前記研磨パッドとの間にスラリーを供給する段階を含むことを特徴とする請求項1に記載のポリシリコン薄膜トランジスタ基板の製造方法。

- パッドコンディショナーで前記研磨パッドの表面状態を向上させる段階をさらに有することを特徴とする請求項2に記載のポリシリコン薄膜トランジスタ基板の製造方法。

- 前記基板が前記研磨パッドに接触している間、前記研磨パッドの回転とは独立的に前記基板を回転させる段階をさらに有することを特徴とする請求項2に記載のポリシリコン薄膜トランジスタ基板の製造方法。

- 前記スラリーの研磨材は、アルミナ、シリカ、又はセリア(CeO2)であることを特徴とする請求項2に記載のポリシリコン薄膜トランジスタ基板の製造方法。

- 前記研磨材の粒度範囲は、50nm〜200nmであることを特徴とする請求項5に記載のポリシリコン薄膜トランジスタ基板の製造方法。

- 前記基板をローディングする段階前に前洗浄する段階をさらに有することを特徴とする請求項1に記載のポリシリコン薄膜トランジスタ基板の製造方法。

- 前記研磨された基板を形成する段階と洗浄された基板を形成する段階は、連続的に実行されることを特徴とする請求項1に記載のポリシリコン薄膜トランジスタ基板の製造方法。

- 前記洗浄された基板を形成する段階は、ブラシ洗浄、超音波洗浄、イソプロピルアルコール洗浄又は超純水洗浄の少なくともいずれか一つで実施されることを特徴とする請求項1に記載のポリシリコン薄膜トランジスタ基板の製造方法。

- 前記基板をローディングする段階は、前記ポリシリコン結晶粒が下側に向くように前記基板を反転し、前記基板を化学的機械的研磨装置に移動させる段階を有することを特徴とする請求項1に記載のポリシリコン薄膜トランジスタ基板の製造方法。

- 前記洗浄された基板をアンローディングする段階は、前記ポリシリコン結晶粒が上側に向くように前記基板を反転させる段階を有することを特徴とする請求項10に記載のポリシリコン薄膜トランジスタ基板の製造方法。

- 前記ポリシリコン結晶粒は、前記基板上にポリシリコン層で形成され、

前記洗浄された基板をアンローディングする段階後に、前記ポリシリコン層をパターニングして前記ポリシリコン薄膜トランジスタ基板の半導体層を形成する段階をさらに有することを特徴とする請求項1に記載のポリシリコン薄膜トランジスタ基板の製造方法。 - 前記基板をローディングする段階前に、前記基板にバッファ層及び該バッファ層上の非晶質シリコン層を提供し、前記非晶質シリコン層をレーザーアニーリングして前記ポリシリコン結晶粒を有するポリシリコン層を形成する段階をさらに有することを特徴とする請求項1に記載のポリシリコン薄膜トランジスタ基板の製造方法。

- ポリシリコン結晶粒が形成された基板をローディングする段階と、

前記ポリシリコン結晶粒の間の結晶粒界から突出している結晶粒を化学的機械的研磨によって除去して研磨された基板を形成する段階と、

前記研磨された基板を洗浄して洗浄された基板を形成する段階と、

前記洗浄された基板をアンローディングする段階とを有する方法によって製造されたポリシリコン薄膜トランジスタ基板より成ることを特徴とする液晶表示装置。 - 前記ポリシリコン結晶粒を除去して研磨された基板を形成する段階は、前記基板を研磨パッドの表面に密着させた状態で前記研磨パッドを回転させる同時に前記基板と前記研磨パッドとの間にスラリーを供給する段階を含むことを特徴とする請求項14に記載の液晶表示装置。

- 前記ポリシリコン結晶粒は、前記基板上にポリシリコン層で形成され、

前記洗浄された基板をアンローディングする段階後に、前記ポリシリコン層をパターニングして前記ポリシリコン薄膜トランジスタ基板の半導体層を形成する段階をさらに有することを特徴とする請求項14に記載の液晶表示装置。 - 前記液晶表示装置の作動中に前記半導体層で電流濃度の局所的集中が実質的に防止されることを特徴とする請求項16に記載の液晶表示装置。

- 前記ポリシリコン結晶粒は、前記基板上にポリシリコン層で形成され、前記ポリシリコン層は、前記突出している結晶粒を除去する間に実質的に平坦化されることを特徴とする請求項14に記載の液晶表示装置。

- 基板と、

前記基板上に形成されるポリシリコン層よりパターニングされて前記基板上に形成される半導体層とを有し、

前記ポリシリコン層は、突出しているポリシリコン結晶粒が除去されるように化学的機械的研磨によって平坦化されることを特徴とする液晶表示装置。 - 前記半導体層のソース領域及びドレイン領域を含む薄膜トランジスタをさらに含むことを特徴とする請求項19に記載の液晶表示装置。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020050022276A KR20060100602A (ko) | 2005-03-17 | 2005-03-17 | 폴리실리콘 박막 트랜지스터의 제조 방법 및 그에 의해제조된 폴리실리콘 박막 트랜지스터를 포함하는 액정 표시장치 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006261681A true JP2006261681A (ja) | 2006-09-28 |

| JP2006261681A5 JP2006261681A5 (ja) | 2009-04-30 |

Family

ID=37010903

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006075342A Pending JP2006261681A (ja) | 2005-03-17 | 2006-03-17 | ポリシリコン薄膜トランジスタ基板の製造方法及び液晶表示装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20060211181A1 (ja) |

| JP (1) | JP2006261681A (ja) |

| KR (1) | KR20060100602A (ja) |

| TW (1) | TW200703658A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012077797A1 (ja) | 2010-12-10 | 2012-06-14 | 帝人株式会社 | 半導体積層体、半導体デバイス、及びそれらの製造方法 |

| WO2013147202A1 (ja) | 2012-03-30 | 2013-10-03 | 帝人株式会社 | 半導体積層体及びその製造方法、半導体デバイスの製造方法、半導体デバイス、ドーパント組成物、ドーパント注入層、並びにドープ層の形成方法 |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102800574A (zh) * | 2011-05-26 | 2012-11-28 | 中国科学院微电子研究所 | 多晶硅栅极的制造方法 |

| KR102313563B1 (ko) * | 2014-12-22 | 2021-10-18 | 주식회사 케이씨텍 | 다양한 웨이퍼 연마 공정을 처리할 수 있는 웨이퍼 처리 시스템 |

| KR102333209B1 (ko) | 2015-04-28 | 2021-12-01 | 삼성디스플레이 주식회사 | 기판 연마 장치 |

| KR102509260B1 (ko) * | 2015-11-20 | 2023-03-14 | 삼성디스플레이 주식회사 | 실리콘 연마 슬러리, 다결정 실리콘의 연마방법 및 박막 트랜지스터 기판의 제조방법 |

| KR102647695B1 (ko) | 2016-08-12 | 2024-03-14 | 삼성디스플레이 주식회사 | 트랜지스터 표시판 및 그 제조 방법 |

| KR102559647B1 (ko) | 2016-08-12 | 2023-07-25 | 삼성디스플레이 주식회사 | 기판 연마 시스템 및 기판 연마 방법 |

| KR102322767B1 (ko) | 2017-03-10 | 2021-11-08 | 삼성디스플레이 주식회사 | 기판과 스테이지 간의 분리 기구가 개선된 기판 처리 장치 및 그것을 이용한 기판 처리 방법 |

| KR102420327B1 (ko) | 2017-06-13 | 2022-07-14 | 삼성디스플레이 주식회사 | 박막 트랜지스터 어레이 기판, 이를 구비한 표시 장치 및 이의 제조 방법 |

| KR102426624B1 (ko) | 2017-11-23 | 2022-07-28 | 삼성디스플레이 주식회사 | 표시 장치 및 그 제조 방법 |

| JP7106209B2 (ja) * | 2018-04-05 | 2022-07-26 | 株式会社ディスコ | SiC基板の研磨方法 |

| KR20210116775A (ko) | 2020-03-13 | 2021-09-28 | 삼성디스플레이 주식회사 | 표시 장치 및 그 제조 방법 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10200120A (ja) * | 1997-01-10 | 1998-07-31 | Sharp Corp | 半導体装置の製造方法 |

| JP2000040828A (ja) * | 1998-07-24 | 2000-02-08 | Toshiba Corp | 薄膜トランジスタの製造方法 |

| JP2000218512A (ja) * | 1999-01-28 | 2000-08-08 | Osaka Diamond Ind Co Ltd | Cmp用パッドコンディショナーおよびその製造方法 |

| JP2000246650A (ja) * | 1999-02-25 | 2000-09-12 | Mitsubishi Materials Corp | 耐食性砥石 |

| JP2001345293A (ja) * | 2000-05-31 | 2001-12-14 | Ebara Corp | 化学機械研磨方法及び化学機械研磨装置 |

| JP2003109918A (ja) * | 2001-09-28 | 2003-04-11 | Internatl Business Mach Corp <Ibm> | 化学機械研磨(cmp)を用いてボンディングのためにウェハを平滑化する装置およびその方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6431959B1 (en) * | 1999-12-20 | 2002-08-13 | Lam Research Corporation | System and method of defect optimization for chemical mechanical planarization of polysilicon |

| JP2002151410A (ja) * | 2000-08-22 | 2002-05-24 | Sony Corp | 結晶質半導体材料の製造方法および半導体装置の製造方法 |

| US6686978B2 (en) * | 2001-02-28 | 2004-02-03 | Sharp Laboratories Of America, Inc. | Method of forming an LCD with predominantly <100> polycrystalline silicon regions |

| KR100753568B1 (ko) * | 2003-06-30 | 2007-08-30 | 엘지.필립스 엘시디 주식회사 | 비정질 반도체층의 결정화방법 및 이를 이용한 액정표시소자의 제조방법 |

| US7189649B2 (en) * | 2004-08-20 | 2007-03-13 | United Microelectronics Corp. | Method of forming a material film |

-

2005

- 2005-03-17 KR KR1020050022276A patent/KR20060100602A/ko not_active Application Discontinuation

-

2006

- 2006-03-16 TW TW095108970A patent/TW200703658A/zh unknown

- 2006-03-17 JP JP2006075342A patent/JP2006261681A/ja active Pending

- 2006-03-17 US US11/378,861 patent/US20060211181A1/en not_active Abandoned

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10200120A (ja) * | 1997-01-10 | 1998-07-31 | Sharp Corp | 半導体装置の製造方法 |

| JP2000040828A (ja) * | 1998-07-24 | 2000-02-08 | Toshiba Corp | 薄膜トランジスタの製造方法 |

| JP2000218512A (ja) * | 1999-01-28 | 2000-08-08 | Osaka Diamond Ind Co Ltd | Cmp用パッドコンディショナーおよびその製造方法 |

| JP2000246650A (ja) * | 1999-02-25 | 2000-09-12 | Mitsubishi Materials Corp | 耐食性砥石 |

| JP2001345293A (ja) * | 2000-05-31 | 2001-12-14 | Ebara Corp | 化学機械研磨方法及び化学機械研磨装置 |

| JP2003109918A (ja) * | 2001-09-28 | 2003-04-11 | Internatl Business Mach Corp <Ibm> | 化学機械研磨(cmp)を用いてボンディングのためにウェハを平滑化する装置およびその方法 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012077797A1 (ja) | 2010-12-10 | 2012-06-14 | 帝人株式会社 | 半導体積層体、半導体デバイス、及びそれらの製造方法 |

| EP2701182A2 (en) | 2010-12-10 | 2014-02-26 | Teijin Limited | Semiconductor laminate, semiconductor device, method for producing semiconductor laminate, and method for manufacturing semiconductor device |

| EP3046136A1 (en) | 2010-12-10 | 2016-07-20 | Teijin Limited | Dispersion containing semiconductor particles |

| US9577050B2 (en) | 2010-12-10 | 2017-02-21 | Teijin Limited | Semiconductor laminate, semiconductor device, and production method thereof |

| WO2013147202A1 (ja) | 2012-03-30 | 2013-10-03 | 帝人株式会社 | 半導体積層体及びその製造方法、半導体デバイスの製造方法、半導体デバイス、ドーパント組成物、ドーパント注入層、並びにドープ層の形成方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20060211181A1 (en) | 2006-09-21 |

| KR20060100602A (ko) | 2006-09-21 |

| TW200703658A (en) | 2007-01-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2006261681A (ja) | ポリシリコン薄膜トランジスタ基板の製造方法及び液晶表示装置 | |

| JP6840810B2 (ja) | 半導体装置 | |

| CN101378082B (zh) | 显示装置以及显示装置的制造方法 | |

| KR100817879B1 (ko) | 반도체장치 제작방법 | |

| JP4854866B2 (ja) | 半導体装置の作製方法 | |

| CN100431149C (zh) | 半导体器件及其制造方法 | |

| CN109690734B (zh) | 玻璃衬底的清洗方法、半导体装置的制造方法及玻璃衬底 | |

| JPH11354445A (ja) | 半導体装置 | |

| CN1680992A (zh) | 具有驱动电路的液晶显示器件及其制造方法 | |

| JP2009134274A (ja) | 液晶表示装置の作製方法 | |

| JP2008042044A (ja) | 薄膜トランジスタアレイ基板、その製造方法、及び表示装置 | |

| JP2001217424A (ja) | 薄膜トランジスタおよびそれを用いた液晶表示装置 | |

| JP4159633B2 (ja) | 半導体装置およびその作製方法並びに電子機器 | |

| CN104658891B (zh) | 低温多晶硅薄膜的制备方法、薄膜晶体管及显示装置 | |

| JP2004088103A (ja) | 液晶ディスプレイの製造方法 | |

| JPH0642494B2 (ja) | 薄膜トランジスタの製造方法 | |

| JP5042133B2 (ja) | 半導体装置の作製方法 | |

| JP4256087B2 (ja) | 半導体装置の作製方法 | |

| JP5185512B2 (ja) | 画像表示装置 | |

| JP2010034463A (ja) | レーザアニール装置 | |

| KR20020032196A (ko) | 다결정실리콘 박막트랜지스터 소자 및 그 제조방법 | |

| JP2011187609A (ja) | 半導体装置の製造方法、電気光学装置、電子機器 | |

| JP4120700B2 (ja) | 半導体基板 | |

| JP2002237453A (ja) | 結晶質半導体膜の作製方法 | |

| JP2010040674A (ja) | レーザアニール装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090317 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090317 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120525 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120529 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120829 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121211 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20121213 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130611 |