JP2006054017A5 - - Google Patents

Download PDFInfo

- Publication number

- JP2006054017A5 JP2006054017A5 JP2004236245A JP2004236245A JP2006054017A5 JP 2006054017 A5 JP2006054017 A5 JP 2006054017A5 JP 2004236245 A JP2004236245 A JP 2004236245A JP 2004236245 A JP2004236245 A JP 2004236245A JP 2006054017 A5 JP2006054017 A5 JP 2006054017A5

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- terminal

- capacitor

- voltage source

- constant voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000003990 capacitor Substances 0.000 claims 26

- 238000000034 method Methods 0.000 claims 19

- 239000004020 conductor Substances 0.000 claims 1

- 230000004044 response Effects 0.000 claims 1

Images

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004236245A JP2006054017A (ja) | 2004-08-13 | 2004-08-13 | メモリディジット線のキャパシタ支持によるプレチャージ |

| US10/958,936 US7177213B2 (en) | 2004-08-13 | 2004-10-05 | Capacitor supported precharging of memory digit lines |

| US11/642,810 US7423923B2 (en) | 2004-08-13 | 2006-12-19 | Capacitor supported precharging of memory digit lines |

| US12/228,459 US7663952B2 (en) | 2004-08-13 | 2008-08-12 | Capacitor supported precharging of memory digit lines |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004236245A JP2006054017A (ja) | 2004-08-13 | 2004-08-13 | メモリディジット線のキャパシタ支持によるプレチャージ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006054017A JP2006054017A (ja) | 2006-02-23 |

| JP2006054017A5 true JP2006054017A5 (enExample) | 2007-09-27 |

Family

ID=35799774

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004236245A Pending JP2006054017A (ja) | 2004-08-13 | 2004-08-13 | メモリディジット線のキャパシタ支持によるプレチャージ |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US7177213B2 (enExample) |

| JP (1) | JP2006054017A (enExample) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006054017A (ja) * | 2004-08-13 | 2006-02-23 | Micron Technology Inc | メモリディジット線のキャパシタ支持によるプレチャージ |

| US8282667B2 (en) * | 2009-06-05 | 2012-10-09 | Entellus Medical, Inc. | Sinus dilation catheter |

| US8872247B2 (en) * | 2009-11-04 | 2014-10-28 | Micron Technology, Inc. | Memory cells having a folded digit line architecture |

| US9224464B2 (en) * | 2014-02-10 | 2015-12-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory circuit and related method |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US107932A (en) * | 1870-10-04 | Improvement in meat and vegetable slicers | ||

| KR890004762B1 (ko) * | 1986-11-21 | 1989-11-25 | 삼성전자 주식회사 | 고성능 디램을 위한 센스 증폭기 |

| JPH0634355B2 (ja) * | 1987-01-26 | 1994-05-02 | 日本電気株式会社 | デイジツト線バランスレベル補正方法 |

| JPS63308792A (ja) * | 1987-06-10 | 1988-12-16 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JPH01171194A (ja) * | 1987-12-25 | 1989-07-06 | Nec Ic Microcomput Syst Ltd | 半導体記憶装置 |

| JP2641904B2 (ja) * | 1988-06-15 | 1997-08-20 | 日本電気アイシーマイコンシステム株式会社 | 半導体記憶装置 |

| JPH02128395A (ja) * | 1988-11-08 | 1990-05-16 | Nec Ic Microcomput Syst Ltd | 半導体記憶装置 |

| KR100203142B1 (ko) | 1996-06-29 | 1999-06-15 | 김영환 | 디램 |

| US5754486A (en) * | 1997-02-28 | 1998-05-19 | Micron Technology, Inc. | Self-test circuit for memory integrated circuits |

| US5856949A (en) * | 1997-03-07 | 1999-01-05 | Advanced Micro Devices, Inc. | Current sense amplifier for RAMs |

| US6094734A (en) * | 1997-08-22 | 2000-07-25 | Micron Technology, Inc. | Test arrangement for memory devices using a dynamic row for creating test data |

| JP2000195268A (ja) * | 1998-10-19 | 2000-07-14 | Toshiba Corp | 半導体記憶装置 |

| KR100355222B1 (ko) * | 1998-12-28 | 2003-02-19 | 삼성전자 주식회사 | 빠른감지속도와높은전원전압마진을갖는전류감지증폭기 |

| KR100299522B1 (ko) * | 1999-06-28 | 2001-11-01 | 박종섭 | 고속 센스 증폭기 |

| JP2001319472A (ja) * | 2000-05-10 | 2001-11-16 | Toshiba Corp | 半導体記憶装置 |

| US6304505B1 (en) * | 2000-05-22 | 2001-10-16 | Micron Technology Inc. | Differential correlated double sampling DRAM sense amplifier |

| JP3874655B2 (ja) | 2001-12-06 | 2007-01-31 | 富士通株式会社 | 半導体記憶装置、及び半導体記憶装置のデータアクセス方法 |

| US6587367B1 (en) * | 2002-03-19 | 2003-07-01 | Texas Instruments Incorporated | Dummy cell structure for 1T1C FeRAM cell array |

| JP2006054017A (ja) * | 2004-08-13 | 2006-02-23 | Micron Technology Inc | メモリディジット線のキャパシタ支持によるプレチャージ |

-

2004

- 2004-08-13 JP JP2004236245A patent/JP2006054017A/ja active Pending

- 2004-10-05 US US10/958,936 patent/US7177213B2/en not_active Expired - Lifetime

-

2006

- 2006-12-19 US US11/642,810 patent/US7423923B2/en not_active Expired - Lifetime

-

2008

- 2008-08-12 US US12/228,459 patent/US7663952B2/en not_active Expired - Lifetime

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR940018984A (ko) | 다이나믹형 램(ram)과 그것을 이용한 정보처리 시스템 | |

| JP2005536827A5 (enExample) | ||

| JPH0518198B2 (enExample) | ||

| KR20020036562A (ko) | 반도체 메모리의 데이타 감지 장치 | |

| US5822262A (en) | Apparatus and method for a dynamic random access memory data sensing architecture | |

| CN115039176A (zh) | 读/写数据的方法、存储器、存储装置和终端 | |

| US8279692B2 (en) | Semiconductor device having hierarchical data line structure and control method thereof | |

| JP2006054017A5 (enExample) | ||

| KR20070043177A (ko) | 센스앰프 회로 | |

| US5768202A (en) | Fast sense amplifier for small voltage differences | |

| JP6287043B2 (ja) | 半導体記憶装置 | |

| US7539064B2 (en) | Precharge circuit of semiconductor memory apparatus | |

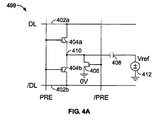

| US7663952B2 (en) | Capacitor supported precharging of memory digit lines | |

| KR19990041459A (ko) | 반도체 메모리장치의 셀 어레이 제어장치 | |

| US20110310687A1 (en) | Current sense amplifiers, memory devices and methods | |

| US6272059B1 (en) | Bit line sense-amplifier for a semiconductor memory device and a method for driving the same | |

| US20040257895A1 (en) | Bit line precharge signal generator for memory device | |

| JPH07211071A (ja) | 半導体記憶回路 | |

| JPS5813519Y2 (ja) | 半導体記憶装置 | |

| JP2000243081A (ja) | ダイナミックランダムアクセスメモリ(dram)等の集積回路用の基準電圧発生器 | |

| US20080062790A1 (en) | Bit-line equalizer, semiconductor memory device including the same, and method for manufacturing bit-line equalizer | |

| TW200537524A (en) | Semiconductor memory device | |

| US7038958B2 (en) | Dual stage DRAM memory equalization | |

| KR100320440B1 (ko) | 반도체 메모리 장치의 비트 라인 프리차지 회로 | |

| JP2672529B2 (ja) | 半導体記憶装置 |