JP2006054017A - メモリディジット線のキャパシタ支持によるプレチャージ - Google Patents

メモリディジット線のキャパシタ支持によるプレチャージ Download PDFInfo

- Publication number

- JP2006054017A JP2006054017A JP2004236245A JP2004236245A JP2006054017A JP 2006054017 A JP2006054017 A JP 2006054017A JP 2004236245 A JP2004236245 A JP 2004236245A JP 2004236245 A JP2004236245 A JP 2004236245A JP 2006054017 A JP2006054017 A JP 2006054017A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- circuit

- capacitor

- node

- conductive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000003990 capacitor Substances 0.000 title claims abstract description 74

- 230000015654 memory Effects 0.000 title claims abstract description 31

- 238000000034 method Methods 0.000 claims abstract description 36

- 230000004044 response Effects 0.000 claims description 4

- 238000012546 transfer Methods 0.000 claims description 2

- 238000010586 diagram Methods 0.000 description 11

- 238000004088 simulation Methods 0.000 description 4

- 238000013459 approach Methods 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000004513 sizing Methods 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4094—Bit-line management or control circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/12—Bit line control circuits, e.g. drivers, boosters, pull-up circuits, pull-down circuits, precharging circuits, equalising circuits, for bit lines

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Dram (AREA)

- Electronic Switches (AREA)

- Logic Circuits (AREA)

Abstract

【解決手段】 メモリディジット線の対をプレチャージする回路および方法が提供される。ディジット線の最終的なプレチャージ電圧は、プレチャージ前のディジット線電圧の平均とは異なる。その最終的なプレチャージ電圧は、プレチャージ回路のキャパシタのサイズを適切に選択することによって設定され得る。

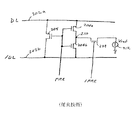

【選択図】 図4A

Description

(要旨)

メモリディジット線の対をプレチャージする回路および方法が提供される。ディジット線の最終的なプレチャージ電圧は、プレチャージ前のディジット線電圧の平均とは異なる。その最終的なプレチャージ電圧は、プレチャージ回路のキャパシタのサイズを適切に選択することによって設定され得る。

502 複数のDRAMチップ

504 プロセッサ

506 メモリコントローラ

508 入力デバイス

510 出力デバイス

512 選択的ストレージデバイス

514 バス

516 バス

Claims (33)

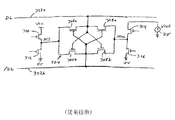

- 複数の導電線の各々に対して同じ電圧を設定する回路であって、該回路は、

第1の端子および第2の端子を有するキャパシタであって、該第1の端子がノードに接続され、該第2の端子が第1の一定電圧源に接続されている、キャパシタと、

該ノードと第2の一定電圧源との間に直列に接続された第1のスイッチングデバイスと、

該導電線と該ノードとの間に接続された少なくとも1つの第2のスイッチングデバイスと

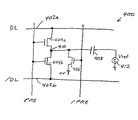

を備える、回路。 - 前記第1のスイッチングデバイスは、第1の制御信号を受信することに応答して、前記ノードを前記第2の一定電圧源に接続するように動作し、

前記第2のスイッチングデバイスは、第2の制御信号を受信することに応答して、前記複数の導電線を該ノードに接続するように動作する、請求項1に記載の回路。 - 前記第1の制御信号および前記第2の制御信号は、実質的に反対の論理値を有する、請求項2に記載の回路。

- 前記第2のスイッチングデバイスは、2つのトランジスタを含み、

前記第2の制御信号は、該2つのトランジスタのゲートに接続される、請求項2に記載の回路。 - 前記同じ電圧は、該同じ電圧が設定される前は、該導電線に対する電圧の平均に等しくない、請求項1に記載の回路。

- 前記第1のスイッチングデバイスは、トランジスタを含む、請求項1に記載の回路。

- 前記第2の一定電圧源は、前記第1の一定電圧源の電圧よりも低い電圧を有する、請求項1に記載の回路。

- 複数の導電線の各々に対して同じ電圧を設定する方法であって、該方法は、

該キャパシタを所望の電圧値へと充電可能にするために、第1のスイッチを介して、キャパシタを一定電圧源に接続するステップと、

該第1のスイッチを介して、該キャパシタを該一定電圧源から切断するステップと、

少なくとも1つの他のスイッチを介して、該複数の導電線を該キャパシタに接続するステップと

を包含する、方法。 - 前記同じ電圧は、前記複数の導電線を前記キャパシタに接続する前は、該導電線に対する電圧の平均に等しくない、請求項8に記載の方法。

- 前記キャパシタを一定電圧源から切断するステップと、前記複数の導電線をキャパシタに接続するステップは、実質的に同時に起こる、前記請求項8に記載の方法。

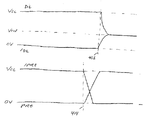

- 導電線の対の各々に対して同じ電圧を設定する方法であって、該方法は、

第1の導電線に対して第1の電圧を設定するステップと、

第2の導電線に対して該第1の電圧に等しくない第2の電圧を設定するステップと、

該第1の導電線および該第2の導電線を互いに接続するステップと、

該第1の電圧および該第2の電圧を所定の値へと引っ張るステップであって、該所定の値が該第1の電圧および該第2の電圧の平均に等しくない、ステップと

を包含する、方法。 - 前記所定の値は、前記第1の電圧および前記第2の電圧の平均よりも小さい、請求項11に記載の方法。

- 前記第1の電圧および前記第2の電圧は、実質的に反対の論理値を有する、請求項11に記載の方法。

- 前記第1の電圧を設定するステップと、前記第2の電圧を設定するステップは、センスアンプを稼動するステップを含む、請求項11に記載の方法。

- 前記接続するステップは、少なくとも1つのスイッチングデバイスを介してなされる、請求項11に記載の方法。

- 前記接続するステップは、前記第1の導電線と前記第2の導電線との間に直列に接続された2つのトランジスタを稼動するステップを含む、請求項11に記載の方法。

- 前記接続するステップは、前記第1の導電線および前記第2の導電線を前記同じノードに接続するステップを含む、請求項11に記載の方法。

- 前記ノードの電圧を固定値に設定するステップをさらに包含する、請求項17に記載の方法。

- 前記固定値は、前記所定の値よりも低い、請求項18に記載の方法。

- 前記所定の値を提供するために、キャパシタのサイズを決定するステップをさらに包含する、請求項11に記載の方法。

- 前記接続するステップは、前記第1の導電線および前記第2の導電線を前記キャパシタの端子に接続するステップを含む、請求項20に記載の方法。

- 複数のセルを含むダイナミックランダムアクセスメモリ(DRAM)であって、

該複数のセルの各々は、プレチャージ回路を含み、

該プレチャージ回路は、

第1の端子および第2の端子を有するキャパシタであって、該第1の端子がノードに接続され、該第2の端子が第1の一定電圧源に接続される、キャパシタと、

該ノードと該第2の一定電圧源との間に直列に接続された第1のスイッチングデバイスと、

導電線の対と該ノードとの間に接続された少なくとも1つの他のスイッチングデバイスと

を含む、DRAM。 - 前記複数のセルにそれぞれ接続された複数のセンスアンプをさらに含む、請求項22に記載のDRAM。

- 前記少なくとも1つのスイッチングデバイスは、2つのトランジスタを含み、

前記トランジスタのゲートは、互いに接続され、

該ゲートは、第1の制御信号線に接続されている、請求項22に記載のDRAM。 - 前記第1のスイッチングデバイスは、トランジスタであり、該トランジスタのゲートは、第2の制御信号線に接続され、

前記第1の制御信号線および該第2の制御信号線の電圧は、実質的に反対の論理値を有する、請求項24に記載のDRAM。 - プロセッサと、

該プロセッサに接続されたメモリコントローラと、

複数の導電線を介して、該メモリコントローラに接続されたメモリと

を含み、

該メモリは、各々がプレチャージ回路を含む複数のセルを含み、

該プレチャージ回路は、

第1の端子および第2の端子を有するキャパシタであって、該第1の端子がノードに接続され、該第2の端子が第1の一定電圧源に接続される、キャパシタと、

該ノードと第2の一定電圧源との間に直列に接続されている第1のスイッチングデバイスと、

該導電線の対と該ノードとの間に接続されている少なくとも1つの他のスイッチングデバイスと

を含む、システム。 - 前記導電線は、前記メモリコントローラと前記メモリとの間でデータを転送する、請求項26に記載のシステム。

- 前記メモリは、ダイナミックランダムアクセスメモリを含む、請求項26に記載のシステム。

- 複数の導電線の各々に対して同じ電圧を設定する回路であって、該回路は、

第1の導電線とノードとの間に接続された第1のトランジスタと、

第2の導電線と該ノードとの間に接続された第2のトランジスタと、

該ノードと第1の一定電圧源との間に接続されたキャパシタと、

該ノードと第2の一定電圧源との間に接続された第3のトランジスタと

を含む、回路。 - 前記第1のトランジスタおよび前記第2のトランジスタのゲートに接続されている第1の制御信号線と、

前記第3のトランジスタのゲートに接続されている第2の制御信号線と

をさらに含む、請求項29に記載の回路。 - 前記第1の一定電圧源および前記第2の一定電圧源は、異なる電圧値を生成する、請求項29に記載の回路。

- 複数の導電線の各々に対して同じ電圧を設定する回路であって、該回路は、

該キャパシタを所望の電圧値へと充電可能にするために、キャパシタを一定電圧源に接続する手段と、

該キャパシタを該一定電圧源から切断する手段と、

該複数の導電線を該キャパシタに接続する手段と

を含む、回路。 - 複数の導電線の各々に対して同じ電圧を設定する回路であって、該回路は、

第1の導電線に対して第1の電圧を設定する手段と、

第2の導電線に対して該第1の電圧に等しくない第2の電圧を設定する手段と、

該第1の導電線および該第2の導電線を互いに接続する手段と、

該第1の電圧および該第2の電圧を所定の値へと引っ張る手段であって、該所定の値が該第1の電圧および該第2の電圧の平均に等しくない、手段と

を含む、回路。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004236245A JP2006054017A (ja) | 2004-08-13 | 2004-08-13 | メモリディジット線のキャパシタ支持によるプレチャージ |

| US10/958,936 US7177213B2 (en) | 2004-08-13 | 2004-10-05 | Capacitor supported precharging of memory digit lines |

| US11/642,810 US7423923B2 (en) | 2004-08-13 | 2006-12-19 | Capacitor supported precharging of memory digit lines |

| US12/228,459 US7663952B2 (en) | 2004-08-13 | 2008-08-12 | Capacitor supported precharging of memory digit lines |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004236245A JP2006054017A (ja) | 2004-08-13 | 2004-08-13 | メモリディジット線のキャパシタ支持によるプレチャージ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006054017A true JP2006054017A (ja) | 2006-02-23 |

| JP2006054017A5 JP2006054017A5 (ja) | 2007-09-27 |

Family

ID=35799774

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004236245A Pending JP2006054017A (ja) | 2004-08-13 | 2004-08-13 | メモリディジット線のキャパシタ支持によるプレチャージ |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US7177213B2 (ja) |

| JP (1) | JP2006054017A (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006054017A (ja) * | 2004-08-13 | 2006-02-23 | Micron Technology Inc | メモリディジット線のキャパシタ支持によるプレチャージ |

| US8282667B2 (en) * | 2009-06-05 | 2012-10-09 | Entellus Medical, Inc. | Sinus dilation catheter |

| US8872247B2 (en) * | 2009-11-04 | 2014-10-28 | Micron Technology, Inc. | Memory cells having a folded digit line architecture |

| US9224464B2 (en) * | 2014-02-10 | 2015-12-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory circuit and related method |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63183686A (ja) * | 1987-01-26 | 1988-07-29 | Nec Corp | デイジツト線バランスレベル補正方法 |

| JPS63308792A (ja) * | 1987-06-10 | 1988-12-16 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JPH023162A (ja) * | 1988-06-15 | 1990-01-08 | Nec Ic Microcomput Syst Ltd | 半導体記憶装置 |

| JPH02128395A (ja) * | 1988-11-08 | 1990-05-16 | Nec Ic Microcomput Syst Ltd | 半導体記憶装置 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US107932A (en) * | 1870-10-04 | Improvement in meat and vegetable slicers | ||

| KR890004762B1 (ko) * | 1986-11-21 | 1989-11-25 | 삼성전자 주식회사 | 고성능 디램을 위한 센스 증폭기 |

| JPH01171194A (ja) * | 1987-12-25 | 1989-07-06 | Nec Ic Microcomput Syst Ltd | 半導体記憶装置 |

| KR100203142B1 (ko) | 1996-06-29 | 1999-06-15 | 김영환 | 디램 |

| US5754486A (en) * | 1997-02-28 | 1998-05-19 | Micron Technology, Inc. | Self-test circuit for memory integrated circuits |

| US5856949A (en) * | 1997-03-07 | 1999-01-05 | Advanced Micro Devices, Inc. | Current sense amplifier for RAMs |

| US6094734A (en) * | 1997-08-22 | 2000-07-25 | Micron Technology, Inc. | Test arrangement for memory devices using a dynamic row for creating test data |

| JP2000195268A (ja) * | 1998-10-19 | 2000-07-14 | Toshiba Corp | 半導体記憶装置 |

| KR100355222B1 (ko) * | 1998-12-28 | 2003-02-19 | 삼성전자 주식회사 | 빠른감지속도와높은전원전압마진을갖는전류감지증폭기 |

| KR100299522B1 (ko) * | 1999-06-28 | 2001-11-01 | 박종섭 | 고속 센스 증폭기 |

| JP2001319472A (ja) * | 2000-05-10 | 2001-11-16 | Toshiba Corp | 半導体記憶装置 |

| US6304505B1 (en) * | 2000-05-22 | 2001-10-16 | Micron Technology Inc. | Differential correlated double sampling DRAM sense amplifier |

| JP3874655B2 (ja) | 2001-12-06 | 2007-01-31 | 富士通株式会社 | 半導体記憶装置、及び半導体記憶装置のデータアクセス方法 |

| US6587367B1 (en) * | 2002-03-19 | 2003-07-01 | Texas Instruments Incorporated | Dummy cell structure for 1T1C FeRAM cell array |

| JP2006054017A (ja) * | 2004-08-13 | 2006-02-23 | Micron Technology Inc | メモリディジット線のキャパシタ支持によるプレチャージ |

-

2004

- 2004-08-13 JP JP2004236245A patent/JP2006054017A/ja active Pending

- 2004-10-05 US US10/958,936 patent/US7177213B2/en not_active Expired - Lifetime

-

2006

- 2006-12-19 US US11/642,810 patent/US7423923B2/en not_active Expired - Lifetime

-

2008

- 2008-08-12 US US12/228,459 patent/US7663952B2/en not_active Expired - Lifetime

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63183686A (ja) * | 1987-01-26 | 1988-07-29 | Nec Corp | デイジツト線バランスレベル補正方法 |

| JPS63308792A (ja) * | 1987-06-10 | 1988-12-16 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JPH023162A (ja) * | 1988-06-15 | 1990-01-08 | Nec Ic Microcomput Syst Ltd | 半導体記憶装置 |

| JPH02128395A (ja) * | 1988-11-08 | 1990-05-16 | Nec Ic Microcomput Syst Ltd | 半導体記憶装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20070097764A1 (en) | 2007-05-03 |

| US7177213B2 (en) | 2007-02-13 |

| US7423923B2 (en) | 2008-09-09 |

| US20090003038A1 (en) | 2009-01-01 |

| US7663952B2 (en) | 2010-02-16 |

| US20060034113A1 (en) | 2006-02-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN102693753B (zh) | 读放大器 | |

| US7738306B2 (en) | Method to improve the write speed for memory products | |

| US11087805B2 (en) | Apparatus with a biasing mechanism and methods for operating the same | |

| JPH0713857B2 (ja) | 半導体記憶装置 | |

| JP2001195885A (ja) | データ伝送回路 | |

| JP6697015B2 (ja) | 1t1d dramセル並びにdramのためのアクセス方法及び関連する装置 | |

| KR102326332B1 (ko) | 독출 컬럼 선택 네거티브 부스트 드라이버 회로 및 시스템 | |

| US8279692B2 (en) | Semiconductor device having hierarchical data line structure and control method thereof | |

| US7663952B2 (en) | Capacitor supported precharging of memory digit lines | |

| US9013914B2 (en) | Semiconductor memory device and method for controlling semiconductor memory device | |

| US5777934A (en) | Semiconductor memory device with variable plate voltage generator | |

| JP2006228261A (ja) | デジット線絶縁ゲートの負電圧駆動 | |

| US6469952B1 (en) | Semiconductor memory device capable of reducing power supply voltage in a DRAM's word driver | |

| US8379469B2 (en) | Integrated circuit memory operation apparatus and methods | |

| US6115308A (en) | Sense amplifier and method of using the same with pipelined read, restore and write operations | |

| US6434069B1 (en) | Two-phase charge-sharing data latch for memory circuit | |

| EP0318094B1 (en) | Integrated memory circuit with on-chip supply voltage control | |

| JP2001229671A (ja) | 半導体記憶装置 | |

| US20090046503A1 (en) | Enhanced Gated Diode Memory Cells | |

| KR100502661B1 (ko) | 반도체메모리장치의 비트라인센싱회로 | |

| US9070425B2 (en) | Data line control for sense amplifiers | |

| JP3129235B2 (ja) | 半導体記憶装置 | |

| JPH0935478A (ja) | 半導体記憶装置 | |

| JPH10162579A (ja) | ビット線プリチャージ方法、半導体メモリ回路およびプリチャージ回路 | |

| KR20030083230A (ko) | 데이터 전송 회로의 제어를 통한 비트라인쌍 상의 초기독출 데이터 증폭 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070813 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070813 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100629 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100706 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20100916 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100916 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20100927 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20101004 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20101004 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20101008 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20101108 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110830 |