JP2005294581A - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP2005294581A JP2005294581A JP2004108433A JP2004108433A JP2005294581A JP 2005294581 A JP2005294581 A JP 2005294581A JP 2004108433 A JP2004108433 A JP 2004108433A JP 2004108433 A JP2004108433 A JP 2004108433A JP 2005294581 A JP2005294581 A JP 2005294581A

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- semiconductor device

- mosfet

- plug

- protective

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D89/00—Aspects of integrated devices not covered by groups H10D84/00 - H10D88/00

- H10D89/60—Integrated devices comprising arrangements for electrical or thermal protection, e.g. protection circuits against electrostatic discharge [ESD]

- H10D89/601—Integrated devices comprising arrangements for electrical or thermal protection, e.g. protection circuits against electrostatic discharge [ESD] for devices having insulated gate electrodes, e.g. for IGFETs or IGBTs

- H10D89/611—Integrated devices comprising arrangements for electrical or thermal protection, e.g. protection circuits against electrostatic discharge [ESD] for devices having insulated gate electrodes, e.g. for IGFETs or IGBTs using diodes as protective elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/811—Combinations of field-effect devices and one or more diodes, capacitors or resistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1203—Rectifying Diode

- H01L2924/12036—PN diode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

Abstract

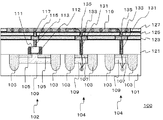

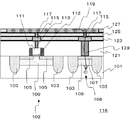

【解決手段】 シリコン基板101、コンタクト層間膜121、第一配線層間膜123、第一ビア層間膜125、および第二配線層間膜127がこの順に積層した構成の半導体装置100において、MOSFET102に第二配線119を介して接続する複数の保護ダイオード104を設ける。

【選択図】 図1

Description

ここで、アンテナ比が10000以上の前記MOSFETのすべてについて複数の前記保護プラグを設けてもよい。

Rmax=5.0×105[1/μm2]SCT+5000 (1)

Rmax=5.0×105[1/μm2]SCT+5000 (1)

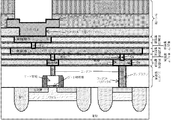

図1は、本実施形態に係る半導体装置100の構成を模式的に示す断面図である。半導体装置100は、シリコン基板101、コンタクト層間膜121、第一配線層間膜123、第一ビア層間膜125、および第二配線層間膜127がこの順に積層した構成であり、MOSFET102および二つの保護ダイオード104を有する。

半導体装置100においては、一つのMOSFET102に二つの保護ダイオード104が接続されている。これにより、保護プラグ131と拡散層107との接触面積(保護プラグ131の底面積)の総和を好適に増加させることができる。このため、半導体装置100の作製にプラズマ処理を用いる場合にも、第二配線119に蓄積した電荷を複数の保護ダイオード104に分散させて、MOSFET102を通らずにシリコン基板101に逃がすようにすることができる。電流経路が複数の保護ダイオード104に分散するため、MOSFET102におけるアンテナ効果を確実に抑制することができる。このため、ゲート絶縁膜112の損傷やそれに伴うリーク電流の発生を確実に抑制することができる。このため、MOSFET102に接続する配線の配線規模を大きくすることができる。

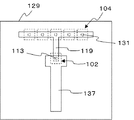

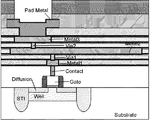

図4は、本実施形態に係る半導体装置の構成を模式的に示す断面図である。図4に示した半導体装置114は、MOSFET102に接続する第二配線119に保護ダイオード106が接続している。

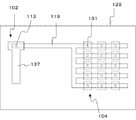

図5は、本実施形態に係る半導体装置の構成を模式的に示す断面図である。図5に示した半導体装置116は、MOSFET102に接続する第二配線119に、保護ダイオード108が接続している。

本実施形態では、以上の実施形態に記載の半導体装置中の一つのMOSFET102に係るアンテナ比の設定方法について説明する。トランジスタはゲート電極の底面積が大きいほど破壊電圧に対する耐圧が大きくなる。そのためプラズマダメージの観点からデバイスの規模を表現するときは、ゲート電極の底面積とデバイス規模の比である「アンテナ比(antenna Ratio)」Rを用いる。プラズマダメージはデバイスごとに発生するので、アンテナ比はデバイス毎に計算する。ここで、デバイスとは、各層配線(Metal1、2、3等)、各層ビア(Via1、2、3等)を指し、デバイスの規模を変化させる因子として、配線長、配線の高さもしくは厚さ、ビア個数、ビア径などが挙げられる。MOSFETのゲート電極に接続する配線およびビアについて、アンテナ比Rはたとえば以下のようにして求められる。

R=Sms/Sg (i)

R=Smb/Sg (ii)

本実施形態では、配線の底面積からアンテナ比Rを求める式(ii)(図7(b))の場合を例に以下説明する。

R=Svb×n/Sg (iii)

(a)MOSFETに接続される保護ダイオードを複数個設ける、

(b)MOSFETに接続される一つの保護ダイオードが、複数の保護プラグを有する構成とする、または

(c)MOSFETのゲート電極に接続されるコンタクトプラグの底面積よりも保護ダイオードの拡散層に接続される保護プラグの底面積を大きくする、

のいずれかを満たすようにゲート電極に接続する保護ダイオードを設ける。このようにすれば、MOSFETのアンテナ比が10000以上の場合にも、ゲート絶縁膜の損傷を抑制することができる。このため、ゲート電極からシリコン基板へのリーク電流の増加を抑制することができる。よって、MOSFETの動作不良を抑制することができる。

以上の実施形態に記載の半導体装置において、一つのMOSFET102に係るアンテナ比を以下のように設定することもできる。

Rmax=5.0×105[1/μm2]SCT+5000 (1)

Rmax=α×SCT+A0 (2)

α=β/S0

と表される。S0は、MOSFETのゲート電極に接続するコンタクトプラグの底面積であり、設計値から算出することができる。βは係数であり、保護プラグの底面積がS0分増加したときに増えるアンテナ比を表す。βの値は実験的に求めることができる。S0の性質から、αはCMOS世代によって変化する値となり、上述のように実験により求めることができる。αは、たとえば5.0×105[1/μm2]とすることができる。

Rmax/2>A0の場合、Rmin=Rmax/2、

Rmax/2≦A0の場合、Rmin=A0、

とすることができる。こうすることにより、アンテナ比を充分に高めつつ、ゲート絶縁膜112の損傷が抑制された構成とすることができる。

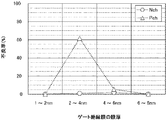

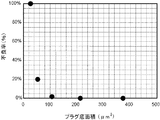

本実施例では、MOSFETのアンテナ比と不良率の関係について検討を行った。まず、図14に示した半導体装置を作製した。この半導体装置について、ゲート絶縁膜を変化させてゲート電極におけるリーク電流を測定し、ある一定値以上の電流が流れたチップを不良と判定した。保護プラグのホール径を、0.10〜0.15μmとした。

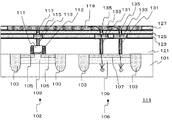

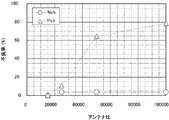

本実施例では、第一の実施形態(図1)に記載の構成を用いて、複数の保護ダイオード104を有する半導体装置を作製した。一つのゲート電極111に接続する保護ダイオード104の個数を変化させることにより、ゲート電極111に接続する保護プラグ131の合計面積を変化させ、ゲート電極111の不良率との関係を調べた。図11は、保護ダイオード104に接続する保護プラグ131の底面積と不良率との関係を示す図である。図11より、接続する保護ダイオード104の個数を2個以上にすることにより、1個の場合より不良率低減の効果が得られることがわかる。また、接続する保護ダイオード104の数が多いほど電荷を逃がしやすくなることがわかる。

本実施例では、第二の実施形態(図4)に記載の構成を用いて、保護ダイオード106の拡散層107に複数の保護プラグ131が接続された半導体装置を作製した。具体的には、図12の右上図および右下図に例示したように、保護ダイオード106の拡散層107に接続する円柱形の保護プラグ131の本数を変化させることにより、アンテナ比を変化させた。そして、そのときの不良率を評価した。

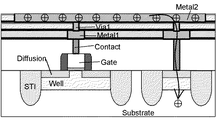

本実施例では、第五の実施形態に記載の上記式(1)を満たす半導体装置を作製した。図13は、本実施例に係る半導体装置の構成を模式的に示す断面図である。図13に示したように、保護ダイオードに接続するコンタクトプラグの径を、トランジスタに接続するコンタクトプラグの径よりも太くした。図13に示した半導体装置において、各層および各部材の構成は以下のようにした。

・ゲート絶縁膜

膜厚:0.1〜10nm

ホール形成後にバリアメタルを成膜し、その上にタングステンを成膜した。

ホール径:100〜200nm

バリアメタル材質:チタンと窒化チタンの積層膜とした。チタン膜厚:5〜15nm、窒化チタン膜厚:10〜20nmとした。

層間膜:シリコン酸化膜、膜厚:500〜800nm

溝形成後にバリアメタルを成膜し、その上にCuを主成分とする金属を成膜した。

バリアメタル材質:タンタルと窒化タンタルの積層膜とした。タンタル膜厚:50〜200nm、窒化タンタル膜厚:50〜200nmとした。

配線幅:100〜20000nm

配線厚:100〜300nm

層間膜:シリコン窒化膜上にシリコン酸化膜を成膜した。シリコン窒化膜の膜厚:20〜100nm、シリコン酸化膜の膜厚:100〜400nmとした。

溝形成後にバリアメタルを成膜し、その上にCuを主成分とする金属を成膜した。

バリアメタル材質:タンタルと窒化タンタルの積層膜とした。タンタル膜厚:5〜20nm、窒化タンタル膜厚:5〜20nmとした。

配線幅:100〜20000nm

配線厚:100〜300nm

層間膜:シリコン窒化膜上に低誘電率膜を成膜、その上にシリコン酸化膜を成膜した。シリコン窒化膜の膜厚:20〜100nm、低誘電率膜の膜厚:100〜300nm、シリコン酸化膜の膜厚:10〜40nmとした。

溝形成後にバリアメタルを成膜し、その上にCuを主成分とする金属を成膜した。

ホール径:100〜200nm

バリアメタル材質:タンタルと窒化タンタルの積層膜とした。タンタル膜厚:5〜20nm、窒化タンタル膜厚:5〜20nmとした。

層間膜:シリコン窒化膜上に低誘電率膜を成膜、その上にシリコン酸化膜を成膜した。シリコン窒化膜の膜厚:20〜100nm、低誘電率膜の膜厚:100〜300nm、シリコン酸化膜の膜厚:10〜40nmとした。

下部のバリアメタルを成膜後、アルミニウムを主成分とする金属を成膜し、その上に上部のバリアメタルを成膜した。

アルミニウムを主成分とする金属の膜厚:1000〜3000nm

下部のバリアメタル材質:チタンと窒化チタンの積層膜とした。チタン膜厚:30〜100nm、窒化チタン膜厚:50〜300nmとした。

上部のバリアメタル材質:窒化チタンの単層膜とした。窒化チタン膜厚:10〜50nmとした。

シリコン酸化膜上にシリコン酸窒化膜を成膜し、その上にポリイミドを成膜してパッシベイション膜(吸湿防止膜)とした。それぞれ、シリコン酸化膜厚:500〜2000nm、シリコン酸窒化膜厚:500〜2000nm、ポリイミド膜厚:1000〜5000nmとした。

P型トランジスタの場合、トランジスタ:P+拡散層、Nウェル、

ダイオード:P+拡散層、Nウェル。

または、

N型トランジスタの場合、トランジスタ:N+拡散層、Pウェル、

ダイオード:N+拡散層、Pウェル。

とした。

101 シリコン基板

103 素子分離領域

104 保護ダイオード

105 拡散層

106 保護ダイオード

107 拡散層

108 保護ダイオード

109 ウェル

111 ゲート電極

112 ゲート絶縁膜

113 コンタクトプラグ

114 半導体装置

115 第一配線

116 半導体装置

117 第一ビア

119 第二配線

121 コンタクト層間膜

123 第一配線層間膜

125 第一ビア層間膜

127 第二配線層間膜

129 内部回路

131 保護プラグ

133 第一配線

135 第一ビア

137 上部配線

139 大径プラグ

Claims (12)

- 半導体基板と、

前記半導体基板の素子形成面に設けられたMOSFETと、

前記MOSFETのゲート電極に配線を介して接続される複数の保護ダイオードと、

を有することを特徴とする半導体装置。 - 半導体基板と、

前記半導体基板の素子形成面に設けられたMOSFETと、

前記MOSFETのゲート電極に配線を介して接続され、前記半導体基板に設けられた拡散層を構成要素とする保護ダイオードと、

前記拡散層に接するとともに前記配線に接続される複数の保護プラグと、

を有することを特徴とする半導体装置。 - 半導体基板と、

前記半導体基板の素子形成面に設けられたMOSFETと、

前記MOSFETのゲート電極に配線を介して接続され、前記半導体基板に設けられた拡散層を構成要素とする保護ダイオードと、

底面において前記ゲート電極に接するとともに前記配線と接続するトランジスタ接続プラグと、

底面において前記拡散層に接するとともに前記配線と接続する保護プラグと、

を有し、

前記保護プラグの底面積が、前記トランジスタ接続プラグの底面積よりも大きいことを特徴とする半導体装置。 - 半導体基板と、

前記半導体基板の素子形成面に設けられたアンテナ比10000以上のMOSFETと、

を有し、

前記MOSFETの少なくとも一つに対し、複数の保護ダイオードが接続されていることを特徴とする半導体装置。 - 半導体基板と、

前記半導体基板の素子形成面に設けられたアンテナ比10000以上のMOSFETと、

を有し、

前記MOSFETの少なくとも一つに対し、

当該MOSFETのゲート電極に配線を介して接続され、前記半導体基板に設けられた拡散層を構成要素とする保護ダイオードと、

前記拡散層に接するとともに前記配線に接続する複数の保護プラグと、

が設けられたことを特徴とする半導体装置。 - 半導体基板と、

前記半導体基板の素子形成面に設けられたアンテナ比10000以上のMOSFETと、

を有し、

前記MOSFETの少なくとも一つに対し、

当該MOSFETのゲート電極に配線を介して接続され、前記半導体基板に設けられた拡散層を構成要素とする保護ダイオードと、

底面において前記ゲート電極に接するとともに前記配線と接続するトランジスタ接続プラグと、

底面において前記拡散層に接するとともに前記配線と接続する保護プラグと、

が設けられ、

前記保護プラグの底面積が、前記トランジスタ接続プラグの底面積よりも大きいことを特徴とする半導体装置。 - 請求項1乃至6いずれかに記載の半導体装置において、

複数の前記保護ダイオードが所定の間隔で配設されたことを特徴とする半導体装置。 - 請求項1乃至7いずれかに記載の半導体装置において、

複数の前記保護ダイオードがアレイ状に配置されたことを特徴とする半導体装置。 - 請求項1乃至8いずれかに記載の半導体装置において、

前記保護ダイオードが内部回路中に設けられたことを特徴とする半導体装置。 - 請求項1乃至9いずれかに記載の半導体装置において、

前記保護ダイオードが、素子分離領域を介して前記MOSFETに隣接していることを特徴とする半導体装置。 - 請求項1乃至10いずれかに記載の半導体装置において、

前記配線と、前記保護ダイオードとが保護プラグによって接続されており、

前記MOSFETのアンテナ比Rの最大許容値Rmaxが、前記保護プラグの底面積SCTに応じて定められており、前記最大許容値Rmaxが下記式(1)で表されることを特徴とする半導体装置。

Rmax=5.0×105[1/μm2]SCT+5000 (1) - シリコン基板の素子形成面にMOSFETおよび保護ダイオードを形成する工程と、

前記MOSFETのゲート電極に接続するトランジスタ接続プラグおよび前記保護ダイオードの拡散層に接続する保護プラグを絶縁膜中に埋設する工程と、

前記トランジスタ接続プラグおよび前記保護プラグに接続する配線を前記絶縁膜中に形成する配線形成工程と、

前記トランジスタ接続プラグに接続された前記配線のアンテナ比の上限を、前記保護プラグが前記保護ダイオードの前記拡散層と接触する面積によって決定する工程と、

を含み、

前記配線形成工程において、アンテナ比の上限を決定する前記工程にて決定された前記上限以下の前記アンテナ比となるように、前記配線を形成することを特徴とする半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108433A JP4609982B2 (ja) | 2004-03-31 | 2004-03-31 | 半導体装置およびその製造方法 |

| US11/078,477 US7190011B2 (en) | 2004-03-31 | 2005-03-14 | Semiconductor device and method for manufacturing same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108433A JP4609982B2 (ja) | 2004-03-31 | 2004-03-31 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005294581A true JP2005294581A (ja) | 2005-10-20 |

| JP4609982B2 JP4609982B2 (ja) | 2011-01-12 |

Family

ID=35096793

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004108433A Expired - Fee Related JP4609982B2 (ja) | 2004-03-31 | 2004-03-31 | 半導体装置およびその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7190011B2 (ja) |

| JP (1) | JP4609982B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009231585A (ja) * | 2008-03-24 | 2009-10-08 | Seiko Epson Corp | 半導体装置及びその製造方法 |

| JP2009239019A (ja) * | 2008-03-27 | 2009-10-15 | Seiko Epson Corp | 半導体装置及びその製造方法 |

| WO2018110304A1 (ja) * | 2016-12-14 | 2018-06-21 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置、および保護素子 |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4205732B2 (ja) * | 2006-05-12 | 2009-01-07 | エルピーダメモリ株式会社 | 半導体集積回路装置 |

| JP2010171345A (ja) * | 2009-01-26 | 2010-08-05 | Renesas Electronics Corp | 半導体装置 |

| JP5657116B2 (ja) * | 2010-08-02 | 2015-01-21 | マニトワック・フードサービス・カンパニーズ・エルエルシー | 水体が氷結している間に水体中を伝搬する音波の解析 |

| KR101865840B1 (ko) * | 2011-08-10 | 2018-06-08 | 삼성전자주식회사 | 반도체 소자 |

| CN110366781B (zh) * | 2017-01-19 | 2023-07-21 | 德克萨斯仪器股份有限公司 | 具有深源接触的功率mosfet |

| US10480843B2 (en) | 2018-01-19 | 2019-11-19 | Manitowoc Foodservice Companies, Llc | Ice-making machine that utilizes closed-loop harvest control with vibrational feedback |

| CN111508954A (zh) * | 2020-04-28 | 2020-08-07 | 上海华力集成电路制造有限公司 | 一种基于fdsoi工艺平台的保护二极管结构及其制作方法 |

| US20230171963A1 (en) * | 2021-11-26 | 2023-06-01 | Samsung Electronics Co., Ltd. | Semiconductor device |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63314860A (ja) * | 1987-06-17 | 1988-12-22 | Mitsubishi Electric Corp | 入力保護回路 |

| JPS6446973A (en) * | 1988-07-22 | 1989-02-21 | Hitachi Ltd | Semiconductor device |

| JPH05175426A (ja) * | 1991-12-26 | 1993-07-13 | Kawasaki Steel Corp | 半導体静電保護回路 |

| JPH0611361U (ja) * | 1992-07-15 | 1994-02-10 | 三菱電機株式会社 | Mic用入力端子構造 |

| JPH08274267A (ja) * | 1995-04-03 | 1996-10-18 | Nec Corp | 半導体装置 |

| JPH11186394A (ja) * | 1997-12-19 | 1999-07-09 | Matsushita Electric Ind Co Ltd | 半導体集積回路の製造方法 |

| JP2000106419A (ja) * | 1998-09-29 | 2000-04-11 | Oki Electric Ind Co Ltd | Ic設計用ライブラリ及びレイアウトパターン設計方法 |

| US6091114A (en) * | 1998-03-31 | 2000-07-18 | Texas Instruments Incorporated | Method and apparatus for protecting gate oxide from process-induced charging effects |

| JP2002100739A (ja) * | 2000-09-25 | 2002-04-05 | Hitachi Ltd | 半導体装置 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3413876B2 (ja) * | 1992-07-08 | 2003-06-09 | セイコーエプソン株式会社 | 半導体装置 |

| JP2000323582A (ja) | 1999-05-14 | 2000-11-24 | Hitachi Ltd | 半導体装置およびその製造方法 |

| US6344368B1 (en) * | 2000-06-26 | 2002-02-05 | United Microelectronics Corp. | Method for forming CMOS sensor |

-

2004

- 2004-03-31 JP JP2004108433A patent/JP4609982B2/ja not_active Expired - Fee Related

-

2005

- 2005-03-14 US US11/078,477 patent/US7190011B2/en not_active Expired - Lifetime

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63314860A (ja) * | 1987-06-17 | 1988-12-22 | Mitsubishi Electric Corp | 入力保護回路 |

| JPS6446973A (en) * | 1988-07-22 | 1989-02-21 | Hitachi Ltd | Semiconductor device |

| JPH05175426A (ja) * | 1991-12-26 | 1993-07-13 | Kawasaki Steel Corp | 半導体静電保護回路 |

| JPH0611361U (ja) * | 1992-07-15 | 1994-02-10 | 三菱電機株式会社 | Mic用入力端子構造 |

| JPH08274267A (ja) * | 1995-04-03 | 1996-10-18 | Nec Corp | 半導体装置 |

| JPH11186394A (ja) * | 1997-12-19 | 1999-07-09 | Matsushita Electric Ind Co Ltd | 半導体集積回路の製造方法 |

| US6091114A (en) * | 1998-03-31 | 2000-07-18 | Texas Instruments Incorporated | Method and apparatus for protecting gate oxide from process-induced charging effects |

| JP2000106419A (ja) * | 1998-09-29 | 2000-04-11 | Oki Electric Ind Co Ltd | Ic設計用ライブラリ及びレイアウトパターン設計方法 |

| JP2002100739A (ja) * | 2000-09-25 | 2002-04-05 | Hitachi Ltd | 半導体装置 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009231585A (ja) * | 2008-03-24 | 2009-10-08 | Seiko Epson Corp | 半導体装置及びその製造方法 |

| JP2009239019A (ja) * | 2008-03-27 | 2009-10-15 | Seiko Epson Corp | 半導体装置及びその製造方法 |

| WO2018110304A1 (ja) * | 2016-12-14 | 2018-06-21 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置、および保護素子 |

| US10861847B2 (en) | 2016-12-14 | 2020-12-08 | Sony Semiconductor Solutions Corporation | Semiconductor device and protection element |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050233517A1 (en) | 2005-10-20 |

| US7190011B2 (en) | 2007-03-13 |

| JP4609982B2 (ja) | 2011-01-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4502173B2 (ja) | 半導体装置及びその製造方法 | |

| JP5329068B2 (ja) | 半導体装置 | |

| US8810001B2 (en) | Seal ring structure with capacitor | |

| JP5799235B2 (ja) | 半導体装置 | |

| TWI466236B (zh) | 裂縫停止結構及其形成方法 | |

| US20060145347A1 (en) | Semiconductor device and method for fabricating the same | |

| JP5090696B2 (ja) | 半導体装置 | |

| TWI540725B (zh) | 半導體裝置及半導體裝置之製造方法 | |

| JP2006005288A (ja) | 半導体装置 | |

| JPWO2005083767A1 (ja) | 半導体装置 | |

| JP4609982B2 (ja) | 半導体装置およびその製造方法 | |

| CN112838070A (zh) | 内连线结构、内连线布局结构及其制作方法 | |

| US11830870B2 (en) | ESD protection device and manufacturing method thereof | |

| JP7039557B2 (ja) | 半導体装置、及び、製造方法 | |

| CN105826293A (zh) | 半导体器件及其制造方法 | |

| JP2006344773A (ja) | 半導体装置及びその製造方法 | |

| JP5553923B2 (ja) | 半導体装置 | |

| US12451444B2 (en) | Semiconductor wafer including chip guard | |

| JP4205732B2 (ja) | 半導体集積回路装置 | |

| JP2013016721A (ja) | 半導体装置 | |

| JP2006005213A (ja) | 半導体装置の製造方法及び半導体装置 | |

| JP5722651B2 (ja) | 半導体装置およびその製造方法 | |

| JP2005150396A (ja) | 半導体装置の製造方法及び半導体装置 | |

| JP5801329B2 (ja) | 半導体装置 | |

| JP2009032730A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060222 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080108 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080310 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080729 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080929 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091201 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101005 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101008 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131022 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4609982 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |