JP2005294430A - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2005294430A JP2005294430A JP2004105529A JP2004105529A JP2005294430A JP 2005294430 A JP2005294430 A JP 2005294430A JP 2004105529 A JP2004105529 A JP 2004105529A JP 2004105529 A JP2004105529 A JP 2004105529A JP 2005294430 A JP2005294430 A JP 2005294430A

- Authority

- JP

- Japan

- Prior art keywords

- temperature

- electrode

- insulating film

- cutting

- base

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H10W72/013—

-

- H10W72/20—

-

- H10W74/012—

-

- H10W74/131—

-

- H10W74/15—

-

- H10W72/01225—

-

- H10W72/01251—

-

- H10W72/01255—

-

- H10W72/01351—

-

- H10W72/07236—

-

- H10W72/073—

-

- H10W72/07338—

-

- H10W72/251—

-

- H10W72/252—

-

- H10W72/352—

-

- H10W72/354—

-

- H10W72/856—

-

- H10W72/923—

-

- H10W72/9415—

-

- H10W72/952—

-

- H10W80/301—

-

- H10W90/724—

-

- H10W90/734—

Landscapes

- Wire Bonding (AREA)

Abstract

【解決手段】 バイトを用いた切削加工で発生する摩擦熱により上昇する絶縁膜6の温度を80℃より低温に制御しつつ、切削加工工程の全体を通して80℃よりも低温という温度範囲を保持しながら平坦化処理した後、80℃以上で絶縁膜6の硬化温度よりも低い温度で、電極5と電極19とを対応させて接触させ、絶縁膜6を液化させて電極5及び電極19間を絶縁膜6の絶縁樹脂で充填させた後、硬化温度以上で絶縁樹脂を硬化させる。

【選択図】 図2

Description

本発明では、CMP法に替わり、基体上に形成された多数の電極の表面を安価に高速で一斉に平坦化する手法として、ダイヤモンド等からなる硬質バイトを用いた切削加工を適用する。この切削加工によれば、基体表面上で絶縁膜内に電極が埋め込み形成されているような場合でも、CMP法のように金属と絶縁物の研磨速度等に依存することなく、基板上で一斉に金属と絶縁膜とを連続して切削し、ディッシング等を発生せしめることなく全体的に両者を均一に平坦化することができる。上述の平坦化処理は、例えば金バンプを電解メッキで形成する場合に、使用したフォトレジストと電極とを一括してバイトで切削加工した後、フォトレジストを除去することで行うことができる。

以下、本発明を適用した具体的な諸実施形態について、図面を参照しながら詳細に説明する。

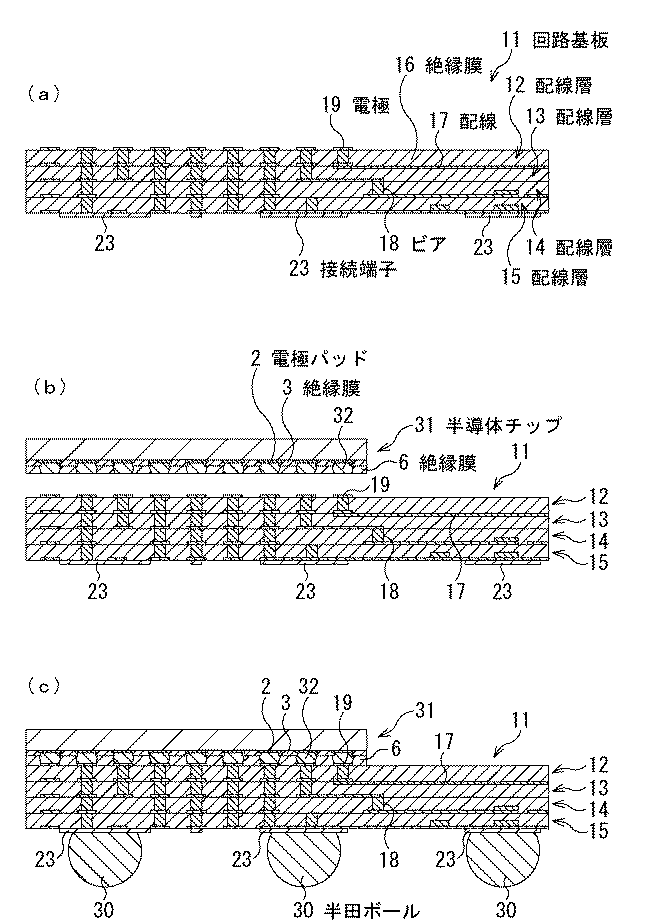

図1及び図2は、第1の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

ここでは、一対の基体として、第1の基体が半導体基板から個片化された半導体チップであり、第2の基体が回路基板である場合を挙げ、回路基板上に半導体チップを搭載する場合について例示する。本実施形態では、半導体チップの表面を切削平坦化し、電極同士を対向させて接続する。

具体的には、電極5の材料としては、低温で固相拡散可能なものを選択する。例えば、Au、Sn、銅(Cu)、銀(Ag)、Snを主材料とした半田等が好適であり、ここではAuを用い、例えば電解メッキ法により金属膜を成膜し、これと下地膜4をパターニングすることにより、電極5を形成する。このとき、各電極5はその形成状態等に起因して、図示の如く各々不均一な高さに形成されることがある。一般的に、各電極5の高さは半導体チップ1内で数μm程度のバラツキを示す。

図4は、切削加工時に絶縁樹脂が若干量液化し、電極の表面に薄く絶縁樹脂の汚れ(ムラ)が形成された様子を示す顕微鏡写真である。この場合、電極間の固相拡散反応を阻害する程度の状態とは評価されないが、本実施形態の切削加工では、かかる状態も発生しないようにすることが必要である。

表1に、切削加工時に絶縁材料をその絶縁材料の第1の温度よりも低温に抑えるための効果的な切削加工のパラメータとその傾向を記述する。

以下、第1の実施形態の諸変形例について説明する。本変形例では、半導体チップの電極構成が本実施形態と異なる。なお、本実施形態で示したものと同様の構成要素等については同符号を記す。

ここでは、半導体チップの回路基板との接続用電極として、半田バンプを形成する場合について説明する。

図5及び図6は、変形例1による半導体装置の製造方法を工程順に示す概略断面図である。

具体的に、電極32の材料としては、低温で固相拡散可能なものとして半田を用い、電極32として半田バンプを形成する。このとき、各電極32はその形成状態等に起因して、図示の如く各々不均一な高さに形成されることがある。一般的に、各電極32の高さは半導体チップ31内で数10μm程度のバラツキを示す。

ここでは、半導体チップの回路基板との接続用電極として、半田バンプを形成する場合について説明する。

図8及び図9は、変形例2による半導体装置の製造方法を工程順に示す概略断面図である。

具体的に、電極42の材料としては、低温で固相拡散可能なものとしてAuを用い、スタッドバンプ法により電極42としてAuスタッドバンプを形成する。このとき、各電極42はその形成状態等に起因して、図示の如く各々不均一な高さに形成されることがある。一般的に、各電極42の高さは半導体チップ41内で±10μm程度のバラツキを示す。

以下、本発明の第2の実施形態について説明する。本実施形態では、回路基板の電極状態が第1の実施形態と異なる。なお、第1の実施形態で示したものと同様の構成要素等については同符号を記す。

図11は、第2の実施形態による半導体装置の製造方法の主要工程を示す概略断面図である。

以下、本発明に関して行った諸実験について説明する。

ここでは、第1の実施形態の変形例1で説明した半田バンプの電極32を有する半導体チップ31を用いて半導体装置を作製するに際して、上述した本発明の切削加工による平坦化処理を実行した場合について、当該切削加工を実行しない比較例との比較において、半導体チップと回路基板との接続状態について調べた。

1.加重:一の電極当たり10gf

2.超音波発信時間:5秒

3.回路基板の温度:140℃

4.半導体チップの温度:室温

5.絶縁樹脂の最終固化条件:150℃で30分間

図12により、本発明では、両電極間に固層拡散が生じ、均一な合金層が明確に生成されているのに対し、比較例では、十分な合金が生成されず、電極間に隙間が形成されているのが判る。種々の条件を調査した結果、比較例では、何れの条件においても十分な合金を生成することができず、実用化は不可能と判断するのが妥当である。

ここでは、バイトを用いた切削加工の研磨加工に対する優位性について調べた。

図13は実験例2による作製結果を示す顕微鏡写真であり、(a)が研削加工によるもの、(b)が切削加工によるものを示しており、(a),(b)共に上図が平坦化直後の電極表面の様子を、中図が電極の接続直後の様子を、下図が150℃で96時間経過後の接続の様子をそれぞれ示している。

前記絶縁膜の温度を前記第1の温度よりも低い温度に保持しながら、バイトを用いた切削加工により、前記第1の電極の表面及び前記絶縁膜の表面が連続して平坦となるように平坦化処理する工程と、

表面に複数の第2の電極が形成されてなる第2の基体に前記第1の基体を前記第1の電極と前記第2の電極とが接触するように対向させ、前記第1の基体と前記第2の基体とを前記絶縁膜により接続するとともに、前記第1の電極と前記第2の電極との間に金属の固相拡散層を生成せしめる工程と

を含むことを特徴とする半導体装置の製造方法。

前記第1の温度以上で、前記絶縁膜による接続と同時に、前記第1の電極と前記第2の電極との接続を同時に行うことを特徴とする付記1又は2に記載の半導体装置の製造方法。

前記第1の基体の温度を前記第1の温度よりも低い温度に設定し、前記第2の基体の温度を前記第1の温度よりも高い温度に設定する工程と、

前記設定された温度において、前記第1の電極と前記第2の電極とを対向接触させ、前記絶縁膜の温度を前記第1の温度以上にして前記第1の基体と前記第2の基体とを接続する工程と

を含むことを特徴とする付記1又は2に記載の半導体装置の製造方法。

前記第1の基体と前記第2の基体とを対向させて接続する工程において、

前記第1の温度以上で、前記第1の電極と前記第2の電極とを所定の圧力で対向接触させて塑性変形させるとともに、液化した前記絶縁材料により前記電極間を充填させ、前記第1の基体と前記第2の基体とを接続することを特徴とする付記5に記載の半導体装置の製造方法。

前記切削加工の後、前記第1の温度以上で前記第2の温度よりも低い温度で、前記第1の電極と前記第2の電極とを対向接触させ、前記第1の基体と前記第2の基体とを前記絶縁膜により接続する工程と、

前記第2の温度以上で、前記絶縁膜を固化させるとともに、前記固相拡散層の生成を助長する工程と

を含むことを特徴とする付記7に記載の半導体装置の製造方法。

2 電極パッド

3,6,16 絶縁膜

4 下地膜

5,19,32,42,52 電極

10 バイト

11,51 回路基板

12〜15 配線層

17 配線

18 ビア

20 半導体基板

21 基板支持台(回転テーブル)

22 切削部

23 接続端子

Claims (10)

- 表面に複数の第1の電極が形成されてなる第1の基体について、第1の温度以上で接着性を発現する絶縁材料を用いて前記第1の電極を埋め込んで封止する絶縁膜を形成する工程と、

前記絶縁膜の温度を前記第1の温度よりも低い温度に保持しながら、バイトを用いた切削加工により、前記第1の電極の表面及び前記絶縁膜の表面が連続して平坦となるように平坦化処理する工程と、

表面に複数の第2の電極が形成されてなる第2の基体に前記第1の基体を前記第1の電極と前記第2の電極とが接触するように対向させ、前記第1の基体と前記第2の基体とを前記絶縁膜により接続するとともに、前記第1の電極と前記第2の電極との間に金属の固相拡散層を生成せしめる工程と

を含むことを特徴とする半導体装置の製造方法。 - 前記切削加工の工程において、当該切削加工で発生する摩擦熱により上昇する前記絶縁膜の温度を前記第1の温度よりも低い温度に保持しながら行うことを特徴とする請求項1に記載の半導体装置の製造方法。

- 前記第1の基体と前記第2の基体とを対向させて接続する工程において、

前記第1の温度以上で、前記絶縁膜による接続と同時に、前記第1の電極と前記第2の電極との接続を同時に行うことを特徴とする請求項1又は2に記載の半導体装置の製造方法。 - 前記第1の基体と前記第2の基体とを対向させて接続する工程は、

前記第1の基体の温度を前記第1の温度よりも低い温度に設定し、前記第2の基体の温度を前記第1の温度よりも高い温度に設定する工程と、

前記設定された温度において、前記第1の電極と前記第2の電極とを対向接触させ、前記絶縁膜の温度を前記第1の温度以上にして前記第1の基体と前記第2の基体とを接続する工程と

を含むことを特徴とする請求項1又は2に記載の半導体装置の製造方法。 - 前記絶縁材料は、常温では固体で接着性を示さず、前記第1の温度に達すると液化して接着性を発現するものであることを特徴とする請求項1〜4のいずれか1項に記載の半導体装置の製造方法。

- 前記第2の基体の前記第2の電極がそれぞれ所定の高さとされており、

前記第1の基体と前記第2の基体とを対向させて接続する工程において、

前記第1の温度以上で、前記第1の電極と前記第2の電極とを所定の圧力で対向接触させて塑性変形させるとともに、液化した前記絶縁材料により前記電極間を充填させ、前記第1の基体と前記第2の基体とを接続することを特徴とする請求項5に記載の半導体装置の製造方法。 - 前記絶縁材料は、前記第1の温度よりも高い第2の温度以上で接着性を消失するものであることを特徴とする請求項1〜6のいずれか1項に記載の半導体装置の製造方法。

- 前記第1の基体と前記第2の基体とを対向させて接続する工程は、

前記切削加工の後、前記第1の温度以上で前記第2の温度よりも低い温度で、前記第1の電極と前記第2の電極とを対向接触させ、前記第1の基体と前記第2の基体とを前記絶縁膜により接続する工程と、

前記第2の温度以上で、前記絶縁膜を固化させるとともに、前記固相拡散層の生成を助長する工程と

を含むことを特徴とする請求項7に記載の半導体装置の製造方法。 - 前記第1の基体が半導体基板に形成された状態で前記第1の基体に前記切削加工を施すことを特徴とする請求項1〜8のいずれか1項に記載の半導体装置の製造方法。

- 個片化された半導体チップである前記第1の基体に前記切削加工を施すことを特徴とする請求項1〜8のいずれか1項に記載の半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004105529A JP4353845B2 (ja) | 2004-03-31 | 2004-03-31 | 半導体装置の製造方法 |

| US11/019,157 US7402461B2 (en) | 2004-03-31 | 2004-12-23 | Method of connecting base materials |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004105529A JP4353845B2 (ja) | 2004-03-31 | 2004-03-31 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005294430A true JP2005294430A (ja) | 2005-10-20 |

| JP4353845B2 JP4353845B2 (ja) | 2009-10-28 |

Family

ID=35061114

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004105529A Expired - Fee Related JP4353845B2 (ja) | 2004-03-31 | 2004-03-31 | 半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7402461B2 (ja) |

| JP (1) | JP4353845B2 (ja) |

Cited By (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008235527A (ja) * | 2007-03-20 | 2008-10-02 | Fujitsu Ltd | 部品内蔵基板の製造方法 |

| JP2009253055A (ja) * | 2008-04-07 | 2009-10-29 | Nikon Corp | 半導体装置および半導体装置の製造方法 |

| JP2011071427A (ja) * | 2009-09-28 | 2011-04-07 | Sekisui Chem Co Ltd | 接着剤層付き半導体チップの製造方法 |

| JP4932040B1 (ja) * | 2011-02-28 | 2012-05-16 | アキム株式会社 | 電子部品組み立て方法、電子部品組み立て装置 |

| JP2012204523A (ja) * | 2011-03-24 | 2012-10-22 | Fujitsu Ltd | 半導体装置の製造方法 |

| JP2012204588A (ja) * | 2011-03-25 | 2012-10-22 | Disco Abrasive Syst Ltd | 半導体デバイスチップの実装方法 |

| JP2013008977A (ja) * | 2012-07-31 | 2013-01-10 | Nikon Corp | 半導体装置および半導体装置の製造方法 |

| JP2013214558A (ja) * | 2012-03-30 | 2013-10-17 | Olympus Corp | 配線基板およびその製造方法、並びに半導体装置およびその製造方法 |

| US8610269B2 (en) | 2009-06-24 | 2013-12-17 | Nec Corporation | Semiconductor device, method for manufacturing semiconductor device, and circuit device using semiconductor device |

| JP2014146703A (ja) * | 2013-01-29 | 2014-08-14 | Ren Solation Co Ltd | 光電変換素子 |

| JP2014528644A (ja) * | 2011-09-30 | 2014-10-27 | インテル・コーポレーション | 非常に薄いデバイスウェハを扱う方法 |

| JP2022166091A (ja) * | 2015-08-28 | 2022-11-01 | 昭和電工マテリアルズ株式会社 | 半導体装置及びその製造方法 |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4130668B2 (ja) * | 2004-08-05 | 2008-08-06 | 富士通株式会社 | 基体の加工方法 |

| JP4667094B2 (ja) * | 2005-03-18 | 2011-04-06 | 富士通株式会社 | 電子装置の製造方法 |

| US9111950B2 (en) * | 2006-09-28 | 2015-08-18 | Philips Lumileds Lighting Company, Llc | Process for preparing a semiconductor structure for mounting |

| US7928582B2 (en) | 2007-03-09 | 2011-04-19 | Micron Technology, Inc. | Microelectronic workpieces and methods for manufacturing microelectronic devices using such workpieces |

| US20090241329A1 (en) * | 2008-03-28 | 2009-10-01 | Utac Thai Limited | Side rail remover |

| WO2010013728A1 (ja) * | 2008-07-31 | 2010-02-04 | 日本電気株式会社 | 半導体装置及びその製造方法 |

| DE102008054415A1 (de) * | 2008-12-09 | 2010-06-10 | Robert Bosch Gmbh | Anordnung zweier Substrate mit einer SLID-Bondverbindung und Verfahren zur Herstellung einer solchen Anordnung |

| JP5508802B2 (ja) * | 2009-09-30 | 2014-06-04 | 株式会社東芝 | 半導体装置の製造方法 |

| JP5548060B2 (ja) * | 2010-07-28 | 2014-07-16 | 株式会社東芝 | 半導体装置 |

| KR20140067524A (ko) * | 2012-11-26 | 2014-06-05 | 삼성전자주식회사 | 파워소자의 웨이퍼 레벨 패키징 방법 |

| CN105308732B (zh) * | 2013-06-24 | 2018-11-27 | 亮锐控股有限公司 | 包括通过平面化减少焊接垫拓扑差异的制造电子结构的方法和对应的电子结构 |

| KR20150004005A (ko) * | 2013-07-02 | 2015-01-12 | 에스케이하이닉스 주식회사 | 스택 패키지 및 이의 제조방법 |

| US9548273B2 (en) * | 2014-12-04 | 2017-01-17 | Invensas Corporation | Integrated circuit assemblies with rigid layers used for protection against mechanical thinning and for other purposes, and methods of fabricating such assemblies |

| KR102906195B1 (ko) * | 2021-04-28 | 2026-01-05 | 후지필름 가부시키가이샤 | 접합체의 제조 방법, 반도체 디바이스의 제조 방법, 및, 수지 조성물 |

| EP4135027A1 (en) * | 2021-08-11 | 2023-02-15 | Murata Manufacturing Co., Ltd. | Surface-mount components, methods of manufacture thereof, and mounting methods employing the components |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3526788B2 (ja) * | 1999-07-01 | 2004-05-17 | 沖電気工業株式会社 | 半導体装置の製造方法 |

| WO2001015223A1 (en) * | 1999-08-23 | 2001-03-01 | Rohm Co., Ltd. | Semiconductor device and method of manufacture thereof |

| EP1151962B1 (en) * | 2000-04-28 | 2007-06-13 | STMicroelectronics S.r.l. | Structure for electrically connecting a first body of semiconductor material overlaid by a second body of semiconductor material, composite structure using the electric connection structure, and manufacturing process thereof |

| JP3822043B2 (ja) * | 2000-09-25 | 2006-09-13 | 太陽誘電株式会社 | チップ部品組立体の製造方法 |

| TW544901B (en) * | 2001-06-13 | 2003-08-01 | Matsushita Electric Industrial Co Ltd | Semiconductor device and manufacture thereof |

| JP3717899B2 (ja) * | 2002-04-01 | 2005-11-16 | Necエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| US6936913B2 (en) * | 2002-12-11 | 2005-08-30 | Northrop Grumman Corporation | High performance vias for vertical IC packaging |

| JP3680839B2 (ja) * | 2003-03-18 | 2005-08-10 | セイコーエプソン株式会社 | 半導体装置および半導体装置の製造方法 |

-

2004

- 2004-03-31 JP JP2004105529A patent/JP4353845B2/ja not_active Expired - Fee Related

- 2004-12-23 US US11/019,157 patent/US7402461B2/en not_active Expired - Lifetime

Cited By (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008235527A (ja) * | 2007-03-20 | 2008-10-02 | Fujitsu Ltd | 部品内蔵基板の製造方法 |

| JP2009253055A (ja) * | 2008-04-07 | 2009-10-29 | Nikon Corp | 半導体装置および半導体装置の製造方法 |

| US8610269B2 (en) | 2009-06-24 | 2013-12-17 | Nec Corporation | Semiconductor device, method for manufacturing semiconductor device, and circuit device using semiconductor device |

| JP2011071427A (ja) * | 2009-09-28 | 2011-04-07 | Sekisui Chem Co Ltd | 接着剤層付き半導体チップの製造方法 |

| JP4932040B1 (ja) * | 2011-02-28 | 2012-05-16 | アキム株式会社 | 電子部品組み立て方法、電子部品組み立て装置 |

| JP2012204523A (ja) * | 2011-03-24 | 2012-10-22 | Fujitsu Ltd | 半導体装置の製造方法 |

| JP2012204588A (ja) * | 2011-03-25 | 2012-10-22 | Disco Abrasive Syst Ltd | 半導体デバイスチップの実装方法 |

| JP2014528644A (ja) * | 2011-09-30 | 2014-10-27 | インテル・コーポレーション | 非常に薄いデバイスウェハを扱う方法 |

| JP2013214558A (ja) * | 2012-03-30 | 2013-10-17 | Olympus Corp | 配線基板およびその製造方法、並びに半導体装置およびその製造方法 |

| JP2013008977A (ja) * | 2012-07-31 | 2013-01-10 | Nikon Corp | 半導体装置および半導体装置の製造方法 |

| JP2014146703A (ja) * | 2013-01-29 | 2014-08-14 | Ren Solation Co Ltd | 光電変換素子 |

| JP2022166091A (ja) * | 2015-08-28 | 2022-11-01 | 昭和電工マテリアルズ株式会社 | 半導体装置及びその製造方法 |

| JP7327601B2 (ja) | 2015-08-28 | 2023-08-16 | 株式会社レゾナック | 半導体装置及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7402461B2 (en) | 2008-07-22 |

| JP4353845B2 (ja) | 2009-10-28 |

| US20050227474A1 (en) | 2005-10-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4353845B2 (ja) | 半導体装置の製造方法 | |

| JP4918088B2 (ja) | エレクトロマイグレーション耐性を有し柔軟性のあるワイヤ相互接続、ナノサイズのはんだ組成、それらを形成するシステム、およびはんだ付けされたパッケージの組み立て方法 | |

| JP4130668B2 (ja) | 基体の加工方法 | |

| US10849240B2 (en) | Contact structures with porous networks for solder connections, and methods of fabricating same | |

| JP3866591B2 (ja) | 電極間接続構造体の形成方法および電極間接続構造体 | |

| TWI313502B (en) | Nano-sized metals and alloys, and methods of assembling packages containing same | |

| US7910403B2 (en) | Metal particles-dispersed composition and flip chip mounting process and bump-forming process using the same | |

| JP5878362B2 (ja) | 半導体装置、半導体パッケージ及び半導体装置の製造方法 | |

| CN101304014B (zh) | 半导体芯片及其制造方法 | |

| JP4684311B2 (ja) | 基体の加工方法 | |

| KR100315158B1 (ko) | 비솔더 플립 칩 본딩용 고신뢰성 비전도성 접착제 및 이를이용한 플립 칩 본딩 방법 | |

| JP6572673B2 (ja) | 電子装置及び電子装置の製造方法 | |

| US20130037943A1 (en) | Semiconductor device, semiconductor package, method for manufacturing semiconductor device, and method for manufacturing semiconductor package | |

| TW201438245A (zh) | 半導體裝置及其製造方法 | |

| WO2006030674A1 (ja) | フリップチップ実装方法及びフリップチップ実装体 | |

| JP2008078682A (ja) | フリップチップ実装装置 | |

| JP2002170921A (ja) | 半導体装置およびその製造方法 | |

| JP4131681B2 (ja) | 半導体装置の製造方法 | |

| JP4846633B2 (ja) | 部品内蔵基板の製造方法 | |

| JP2006294650A (ja) | 電子部品の実装方法 | |

| JP2004247668A (ja) | 積層用中間配線部材、配線板及びそれらの製造方法 | |

| JP5385471B2 (ja) | 半導体装置の製造方法 | |

| JP4667094B2 (ja) | 電子装置の製造方法 | |

| JP2005116612A (ja) | フリップチップ実装方法およびこの方法を用いた電子回路装置 | |

| KR20180073767A (ko) | 고온용 접합 페이스트 및 인 시츄 미세 은 범프 형성을 이용한 접합 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070315 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090317 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090407 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090608 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090707 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090728 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4353845 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120807 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120807 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130807 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |