JP2005236003A - 抵抗変化型不揮発性メモリ、抵抗変化型不揮発性メモリの製造方法、記録方法、再生方法、消去方法、抵抗変化材料微細構造体および抵抗変化材料微細構造体の製造方法 - Google Patents

抵抗変化型不揮発性メモリ、抵抗変化型不揮発性メモリの製造方法、記録方法、再生方法、消去方法、抵抗変化材料微細構造体および抵抗変化材料微細構造体の製造方法 Download PDFInfo

- Publication number

- JP2005236003A JP2005236003A JP2004042849A JP2004042849A JP2005236003A JP 2005236003 A JP2005236003 A JP 2005236003A JP 2004042849 A JP2004042849 A JP 2004042849A JP 2004042849 A JP2004042849 A JP 2004042849A JP 2005236003 A JP2005236003 A JP 2005236003A

- Authority

- JP

- Japan

- Prior art keywords

- variable resistance

- nonvolatile memory

- thin film

- electrode

- block copolymer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 230000015654 memory Effects 0.000 title claims abstract description 135

- 239000000463 material Substances 0.000 title claims abstract description 126

- 238000000034 method Methods 0.000 title claims description 95

- 238000004519 manufacturing process Methods 0.000 title claims description 31

- 229920001400 block copolymer Polymers 0.000 claims abstract description 74

- 239000000758 substrate Substances 0.000 claims abstract description 71

- 229910002367 SrTiO Inorganic materials 0.000 claims abstract description 43

- 239000010410 layer Substances 0.000 claims description 85

- 239000010409 thin film Substances 0.000 claims description 75

- 230000008859 change Effects 0.000 claims description 73

- 239000010408 film Substances 0.000 claims description 63

- 229910052751 metal Inorganic materials 0.000 claims description 55

- 239000002184 metal Substances 0.000 claims description 55

- 239000011148 porous material Substances 0.000 claims description 35

- 239000000523 sample Substances 0.000 claims description 30

- 238000005530 etching Methods 0.000 claims description 24

- 238000000926 separation method Methods 0.000 claims description 24

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 claims description 14

- 238000007743 anodising Methods 0.000 claims description 14

- 229910052782 aluminium Inorganic materials 0.000 claims description 12

- 229910001029 Hf alloy Inorganic materials 0.000 claims description 11

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 10

- 239000000126 substance Substances 0.000 claims description 10

- RVYOQIHOUTVEKU-UHFFFAOYSA-N aluminum hafnium Chemical compound [Al].[Hf] RVYOQIHOUTVEKU-UHFFFAOYSA-N 0.000 claims description 9

- 229910052804 chromium Inorganic materials 0.000 claims description 9

- 238000011049 filling Methods 0.000 claims description 8

- 229910052712 strontium Inorganic materials 0.000 claims description 8

- 229910052735 hafnium Inorganic materials 0.000 claims description 7

- 229910052723 transition metal Inorganic materials 0.000 claims description 6

- 150000003624 transition metals Chemical class 0.000 claims description 6

- 229910052802 copper Inorganic materials 0.000 claims description 5

- 229910052746 lanthanum Inorganic materials 0.000 claims description 5

- 229910052759 nickel Inorganic materials 0.000 claims description 5

- 229910052719 titanium Inorganic materials 0.000 claims description 5

- 239000002356 single layer Substances 0.000 claims description 4

- 229910052737 gold Inorganic materials 0.000 claims description 3

- 229910052741 iridium Inorganic materials 0.000 claims description 3

- 229910052763 palladium Inorganic materials 0.000 claims description 3

- 229910052697 platinum Inorganic materials 0.000 claims description 3

- 229910052703 rhodium Inorganic materials 0.000 claims description 3

- 229910052707 ruthenium Inorganic materials 0.000 claims description 3

- 229910052684 Cerium Inorganic materials 0.000 claims description 2

- 229910052779 Neodymium Inorganic materials 0.000 claims description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 2

- 229910004121 SrRuO Inorganic materials 0.000 claims description 2

- 229910052788 barium Inorganic materials 0.000 claims description 2

- 229910052791 calcium Inorganic materials 0.000 claims description 2

- 239000012212 insulator Substances 0.000 claims description 2

- 229910052742 iron Inorganic materials 0.000 claims description 2

- 229910052749 magnesium Inorganic materials 0.000 claims description 2

- 229910052748 manganese Inorganic materials 0.000 claims description 2

- 229910052710 silicon Inorganic materials 0.000 claims description 2

- 239000010703 silicon Substances 0.000 claims description 2

- 229910052720 vanadium Inorganic materials 0.000 claims description 2

- 229910052726 zirconium Inorganic materials 0.000 claims description 2

- 238000010894 electron beam technology Methods 0.000 abstract description 8

- 238000000609 electron-beam lithography Methods 0.000 abstract description 8

- 239000002105 nanoparticle Substances 0.000 abstract description 6

- 238000012856 packing Methods 0.000 abstract 1

- 239000002096 quantum dot Substances 0.000 description 30

- 229910004298 SiO 2 Inorganic materials 0.000 description 17

- 230000015572 biosynthetic process Effects 0.000 description 17

- 239000011651 chromium Substances 0.000 description 15

- 239000000243 solution Substances 0.000 description 14

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 12

- 230000008569 process Effects 0.000 description 11

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 10

- 229920001195 polyisoprene Polymers 0.000 description 10

- 239000004926 polymethyl methacrylate Substances 0.000 description 10

- -1 titanium alkoxide Chemical class 0.000 description 10

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 9

- 239000004793 Polystyrene Substances 0.000 description 9

- 239000002086 nanomaterial Substances 0.000 description 9

- 239000012071 phase Substances 0.000 description 9

- 238000003860 storage Methods 0.000 description 9

- 239000010936 titanium Substances 0.000 description 9

- 238000010438 heat treatment Methods 0.000 description 8

- 239000000203 mixture Substances 0.000 description 8

- 230000003647 oxidation Effects 0.000 description 8

- 238000007254 oxidation reaction Methods 0.000 description 8

- 238000005516 engineering process Methods 0.000 description 7

- 229920000642 polymer Polymers 0.000 description 7

- 229920002223 polystyrene Polymers 0.000 description 7

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 6

- 239000002253 acid Substances 0.000 description 6

- 150000001732 carboxylic acid derivatives Chemical class 0.000 description 6

- 239000013078 crystal Substances 0.000 description 6

- MLFHJEHSLIIPHL-UHFFFAOYSA-N isoamyl acetate Chemical compound CC(C)CCOC(C)=O MLFHJEHSLIIPHL-UHFFFAOYSA-N 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- 239000002994 raw material Substances 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- 230000008901 benefit Effects 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 238000001312 dry etching Methods 0.000 description 4

- 239000007789 gas Substances 0.000 description 4

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 4

- FUZZWVXGSFPDMH-UHFFFAOYSA-N hexanoic acid Chemical compound CCCCCC(O)=O FUZZWVXGSFPDMH-UHFFFAOYSA-N 0.000 description 4

- 239000003960 organic solvent Substances 0.000 description 4

- 229910000487 osmium oxide Inorganic materials 0.000 description 4

- JIWAALDUIFCBLV-UHFFFAOYSA-N oxoosmium Chemical compound [Os]=O JIWAALDUIFCBLV-UHFFFAOYSA-N 0.000 description 4

- 238000004528 spin coating Methods 0.000 description 4

- XEKOWRVHYACXOJ-UHFFFAOYSA-N Ethyl acetate Chemical compound CCOC(C)=O XEKOWRVHYACXOJ-UHFFFAOYSA-N 0.000 description 3

- LRHPLDYGYMQRHN-UHFFFAOYSA-N N-Butanol Chemical compound CCCCO LRHPLDYGYMQRHN-UHFFFAOYSA-N 0.000 description 3

- MUBZPKHOEPUJKR-UHFFFAOYSA-N Oxalic acid Chemical compound OC(=O)C(O)=O MUBZPKHOEPUJKR-UHFFFAOYSA-N 0.000 description 3

- 229910010413 TiO 2 Inorganic materials 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 238000002048 anodisation reaction Methods 0.000 description 3

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 3

- BTANRVKWQNVYAZ-UHFFFAOYSA-N butan-2-ol Chemical compound CCC(C)O BTANRVKWQNVYAZ-UHFFFAOYSA-N 0.000 description 3

- 150000001735 carboxylic acids Chemical class 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 230000010354 integration Effects 0.000 description 3

- 229940117955 isoamyl acetate Drugs 0.000 description 3

- 238000000608 laser ablation Methods 0.000 description 3

- 229910052760 oxygen Inorganic materials 0.000 description 3

- 239000001301 oxygen Substances 0.000 description 3

- 238000005191 phase separation Methods 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- BDERNNFJNOPAEC-UHFFFAOYSA-N propan-1-ol Chemical compound CCCO BDERNNFJNOPAEC-UHFFFAOYSA-N 0.000 description 3

- 150000003839 salts Chemical class 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 3

- NQPDZGIKBAWPEJ-UHFFFAOYSA-N valeric acid Chemical compound CCCCC(O)=O NQPDZGIKBAWPEJ-UHFFFAOYSA-N 0.000 description 3

- 239000012808 vapor phase Substances 0.000 description 3

- HNRMPXKDFBEGFZ-UHFFFAOYSA-N 2,2-dimethylbutane Chemical compound CCC(C)(C)C HNRMPXKDFBEGFZ-UHFFFAOYSA-N 0.000 description 2

- WFRBDWRZVBPBDO-UHFFFAOYSA-N 2-methyl-2-pentanol Chemical compound CCCC(C)(C)O WFRBDWRZVBPBDO-UHFFFAOYSA-N 0.000 description 2

- OVBFMEVBMNZIBR-UHFFFAOYSA-N 2-methylvaleric acid Chemical compound CCCC(C)C(O)=O OVBFMEVBMNZIBR-UHFFFAOYSA-N 0.000 description 2

- IGIDLTISMCAULB-UHFFFAOYSA-N 3-methylvaleric acid Chemical compound CCC(C)CC(O)=O IGIDLTISMCAULB-UHFFFAOYSA-N 0.000 description 2

- FERIUCNNQQJTOY-UHFFFAOYSA-N Butyric acid Chemical compound CCCC(O)=O FERIUCNNQQJTOY-UHFFFAOYSA-N 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- AMQJEAYHLZJPGS-UHFFFAOYSA-N N-Pentanol Chemical compound CCCCCO AMQJEAYHLZJPGS-UHFFFAOYSA-N 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 150000004703 alkoxides Chemical class 0.000 description 2

- DKPFZGUDAPQIHT-UHFFFAOYSA-N butyl acetate Chemical compound CCCCOC(C)=O DKPFZGUDAPQIHT-UHFFFAOYSA-N 0.000 description 2

- 238000002425 crystallisation Methods 0.000 description 2

- 230000008025 crystallization Effects 0.000 description 2

- GHVNFZFCNZKVNT-UHFFFAOYSA-N decanoic acid Chemical compound CCCCCCCCCC(O)=O GHVNFZFCNZKVNT-UHFFFAOYSA-N 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- POULHZVOKOAJMA-UHFFFAOYSA-N dodecanoic acid Chemical compound CCCCCCCCCCCC(O)=O POULHZVOKOAJMA-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000003792 electrolyte Substances 0.000 description 2

- 150000002148 esters Chemical class 0.000 description 2

- 238000010574 gas phase reaction Methods 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 150000002367 halogens Chemical class 0.000 description 2

- PHTQWCKDNZKARW-UHFFFAOYSA-N isoamylol Chemical compound CC(C)CCO PHTQWCKDNZKARW-UHFFFAOYSA-N 0.000 description 2

- ZXEKIIBDNHEJCQ-UHFFFAOYSA-N isobutanol Chemical compound CC(C)CO ZXEKIIBDNHEJCQ-UHFFFAOYSA-N 0.000 description 2

- FGKJLKRYENPLQH-UHFFFAOYSA-N isocaproic acid Chemical compound CC(C)CCC(O)=O FGKJLKRYENPLQH-UHFFFAOYSA-N 0.000 description 2

- QWTDNUCVQCZILF-UHFFFAOYSA-N isopentane Chemical compound CCC(C)C QWTDNUCVQCZILF-UHFFFAOYSA-N 0.000 description 2

- JVTAAEKCZFNVCJ-UHFFFAOYSA-N lactic acid Chemical compound CC(O)C(O)=O JVTAAEKCZFNVCJ-UHFFFAOYSA-N 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- 238000001451 molecular beam epitaxy Methods 0.000 description 2

- FBUKVWPVBMHYJY-UHFFFAOYSA-N nonanoic acid Chemical compound CCCCCCCCC(O)=O FBUKVWPVBMHYJY-UHFFFAOYSA-N 0.000 description 2

- WWZKQHOCKIZLMA-UHFFFAOYSA-N octanoic acid Chemical compound CCCCCCCC(O)=O WWZKQHOCKIZLMA-UHFFFAOYSA-N 0.000 description 2

- JYVLIDXNZAXMDK-UHFFFAOYSA-N pentan-2-ol Chemical compound CCCC(C)O JYVLIDXNZAXMDK-UHFFFAOYSA-N 0.000 description 2

- PGMYKACGEOXYJE-UHFFFAOYSA-N pentyl acetate Chemical compound CCCCCOC(C)=O PGMYKACGEOXYJE-UHFFFAOYSA-N 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 229920000193 polymethacrylate Polymers 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000007261 regionalization Effects 0.000 description 2

- 238000012827 research and development Methods 0.000 description 2

- 238000001338 self-assembly Methods 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- 238000009210 therapy by ultrasound Methods 0.000 description 2

- VXUYXOFXAQZZMF-UHFFFAOYSA-N titanium(IV) isopropoxide Chemical compound CC(C)O[Ti](OC(C)C)(OC(C)C)OC(C)C VXUYXOFXAQZZMF-UHFFFAOYSA-N 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 230000005641 tunneling Effects 0.000 description 2

- POILWHVDKZOXJZ-ARJAWSKDSA-M (z)-4-oxopent-2-en-2-olate Chemical compound C\C([O-])=C\C(C)=O POILWHVDKZOXJZ-ARJAWSKDSA-M 0.000 description 1

- XYHKNCXZYYTLRG-UHFFFAOYSA-N 1h-imidazole-2-carbaldehyde Chemical compound O=CC1=NC=CN1 XYHKNCXZYYTLRG-UHFFFAOYSA-N 0.000 description 1

- XFOASZQZPWEJAA-UHFFFAOYSA-N 2,3-dimethylbutyric acid Chemical compound CC(C)C(C)C(O)=O XFOASZQZPWEJAA-UHFFFAOYSA-N 0.000 description 1

- SDGKUVSVPIIUCF-UHFFFAOYSA-N 2,6-dimethylpiperidine Chemical compound CC1CCCC(C)N1 SDGKUVSVPIIUCF-UHFFFAOYSA-N 0.000 description 1

- OXQGTIUCKGYOAA-UHFFFAOYSA-N 2-Ethylbutanoic acid Chemical compound CCC(CC)C(O)=O OXQGTIUCKGYOAA-UHFFFAOYSA-N 0.000 description 1

- JCCIFDCPHCKATH-UHFFFAOYSA-N 2-methylbutan-2-yl acetate Chemical compound CCC(C)(C)OC(C)=O JCCIFDCPHCKATH-UHFFFAOYSA-N 0.000 description 1

- MLMQPDHYNJCQAO-UHFFFAOYSA-N 3,3-dimethylbutyric acid Chemical compound CC(C)(C)CC(O)=O MLMQPDHYNJCQAO-UHFFFAOYSA-N 0.000 description 1

- GWYFCOCPABKNJV-UHFFFAOYSA-M 3-Methylbutanoic acid Natural products CC(C)CC([O-])=O GWYFCOCPABKNJV-UHFFFAOYSA-M 0.000 description 1

- SVOZMXFQYZNNOY-UHFFFAOYSA-N CCCCC(OCCCC)(OCC(C)C)OC(CCCC)(OCCCC)OCC(C)C Chemical compound CCCCC(OCCCC)(OCC(C)C)OC(CCCC)(OCCCC)OCC(C)C SVOZMXFQYZNNOY-UHFFFAOYSA-N 0.000 description 1

- 239000005632 Capric acid (CAS 334-48-5) Substances 0.000 description 1

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 1

- 229910003410 La0.7Ca0.3MnO3 Inorganic materials 0.000 description 1

- 229910002182 La0.7Sr0.3MnO3 Inorganic materials 0.000 description 1

- 239000005639 Lauric acid Substances 0.000 description 1

- 239000005643 Pelargonic acid Substances 0.000 description 1

- 229910010037 TiAlN Inorganic materials 0.000 description 1

- 238000004220 aggregation Methods 0.000 description 1

- 230000002776 aggregation Effects 0.000 description 1

- 230000032683 aging Effects 0.000 description 1

- 150000001298 alcohols Chemical class 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- GWYFCOCPABKNJV-UHFFFAOYSA-N beta-methyl-butyric acid Natural products CC(C)CC(O)=O GWYFCOCPABKNJV-UHFFFAOYSA-N 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 238000001354 calcination Methods 0.000 description 1

- 150000007942 carboxylates Chemical class 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 150000004696 coordination complex Chemical class 0.000 description 1

- RKTYLMNFRDHKIL-UHFFFAOYSA-N copper;5,10,15,20-tetraphenylporphyrin-22,24-diide Chemical compound [Cu+2].C1=CC(C(=C2C=CC([N-]2)=C(C=2C=CC=CC=2)C=2C=CC(N=2)=C(C=2C=CC=CC=2)C2=CC=C3[N-]2)C=2C=CC=CC=2)=NC1=C3C1=CC=CC=C1 RKTYLMNFRDHKIL-UHFFFAOYSA-N 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 229940093499 ethyl acetate Drugs 0.000 description 1

- 239000010419 fine particle Substances 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 229940035429 isobutyl alcohol Drugs 0.000 description 1

- 239000004310 lactic acid Substances 0.000 description 1

- 235000014655 lactic acid Nutrition 0.000 description 1

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 1

- 239000007791 liquid phase Substances 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- YKYONYBAUNKHLG-UHFFFAOYSA-N n-Propyl acetate Natural products CCCOC(C)=O YKYONYBAUNKHLG-UHFFFAOYSA-N 0.000 description 1

- 238000011017 operating method Methods 0.000 description 1

- 235000006408 oxalic acid Nutrition 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 229940090181 propyl acetate Drugs 0.000 description 1

- DCKVNWZUADLDEH-UHFFFAOYSA-N sec-butyl acetate Chemical compound CCC(C)OC(C)=O DCKVNWZUADLDEH-UHFFFAOYSA-N 0.000 description 1

- WMOVHXAZOJBABW-UHFFFAOYSA-N tert-butyl acetate Chemical compound CC(=O)OC(C)(C)C WMOVHXAZOJBABW-UHFFFAOYSA-N 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0007—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising metal oxide memory material, e.g. perovskites

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0009—RRAM elements whose operation depends upon chemical change

- G11C13/0014—RRAM elements whose operation depends upon chemical change comprising cells based on organic memory material

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0009—RRAM elements whose operation depends upon chemical change

- G11C13/0014—RRAM elements whose operation depends upon chemical change comprising cells based on organic memory material

- G11C13/0016—RRAM elements whose operation depends upon chemical change comprising cells based on organic memory material comprising polymers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/30—Resistive cell, memory material aspects

- G11C2213/31—Material having complex metal oxide, e.g. perovskite structure

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/77—Array wherein the memory element being directly connected to the bit lines and word lines without any access device being used

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Materials Engineering (AREA)

- Semiconductor Memories (AREA)

Abstract

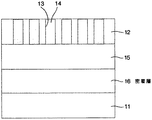

【解決手段】 Si基板等の基板11上に形成したPt等の電極15上にナノホール13を有するナノテンプレート層12を形成した後、ナノホール13の内部にCrドープSrTiO3 等の抵抗変化材料を充填してナノドット14を形成する。ナノテンプレート層12は、Al薄膜を陽極酸化したり、ドット状凝集部と他の凝集部とからなるブロックコポリマーを形成した後、そのドット状凝集部を除去することにより形成する。

【選択図】 図2

Description

最近、これらの従来の不揮発性メモリと異なる抵抗変化型不揮発性メモリ(RRAM;resistance RAM)が提案されている(非特許文献1)。この抵抗変化型不揮発性メモリは、電圧パルスの印加によってメモリセルの抵抗変化層の抵抗値を設定することにより情報を書き込むことができ、かつ情報の非破壊読み出しを行うことができる不揮発性メモリであり、セル面積が小さく、かつ多値化が可能なことから、既存の不揮発性メモリを凌ぐ可能性を有する。抵抗変化型不揮発性メモリについては他の提案もなされている(非特許文献2、特許文献1)。

W.W.Zhuang et.al., 2002 IEDM, 論文番号7.5, Dec2002 A.Beck et.al., Applied Physics Letters, vol.77, 2000, 139

既存技術の中では、500円硬貨サイズで500MB程度の容量を有するハードディスクが既に開発されており、前記のようなデジタル携帯端末用途に適用できる見込みがあるものの、ハードディスクには、消費電力が大きいというデメリットがある。すなわち、現状では、消費電力が1W以上であるために、バッテリ駆動時間に大きな負担となる。

近い将来に、数百Gb/inch2 〜1Tb/inch2 の高密度メモリを実現するためには、1ビット当たり数nm〜数十nmの大きさの記憶ビットを規則正しく高密度に形成する技術が必要不可欠である。従来の半導体微細加工に用いられる光リソグラフィーでは、加工寸法100nm程度まで技術が進展しているものの、数nm〜数十nmの寸法の加工は困難である。数nm〜数十nmの寸法のパターン形成の方法は、現状では電子線リソグラフィーあるいは電子線による直接描画が唯一の方法であるが、コストが非常に高くなるという欠点がある。

Masuda et.al., Applied Physics Letters, vol.71, 1997, 2770

P.Mansky et.al., Applied Physics Letters, vol.68, No.18, 2586

M.Park et.al., Science, vol.276, 1404

Jpn.J.Appl.Phys.,Vol.41(2002),p.6112

この発明が解決しようとする他の課題は、上記の抵抗変化型不揮発性メモリに好適な記録方法、再生方法および消去方法を提供することにある。

すなわち、最近進展が著しいナノテクノロジーに着目すると、自然に生成される規則的な微細構造、いわゆる分子・原子の自己組織化によってナノオーダーの微細構造を実現しようという試みがなされている。これらの試みのいくつかは、記録媒体の大容量化に適したナノ構造を作り出している。

また、第二の方法として、二種類のポリマー鎖が連結したブロックコポリマーを用いる手法がある。ブロックコポリマーは、数十nm程度の周期を持つミクロ相分離構造と呼ばれる規則的な相分離構造を有する。例えば、ブロックコポリマーがAというポリマー鎖とBというポリマー鎖とからできている場合、このブロックコポリマーを適切な基板上に展開して乾燥すると、Aポリマーが凝集したA相とBポリマーが凝集したB相とが空間的に互いに分離したミクロ相分離構造を形成する。この単位セルは、分子鎖の大きさより大きくならず、その大きさは数nm〜数十nmのオーダーである。

そして、電極となる金属上、もしくは導電性酸化物上に、上述のような陽極酸化アルミナ、あるいはブロックコポリマーを形成し、そこに生じるナノサイズの細孔内にメモリ材料である抵抗変化材料を充填し、ひとつひとつの独立したナノドットを形成することができる。

こうして形成される抵抗変化材料からなるナノドットは、一般に、直径が200nm以下、配列間隔が200nm以下の2次元ナノ構造を有し、各ナノドットが抵抗変化材料に特有のI(電流)−V(電圧)ヒステリシスあるいはパルス電圧による抵抗変化特性を示す。

この発明は、以上のような本発明者らによる検討に基づいて案出されたものである。

電極上に抵抗変化材料からなる微細なドットを有する

ことを特徴とする抵抗変化型不揮発性メモリである。

電極上に細孔を有する薄膜を形成する工程と、

上記細孔の内部に抵抗変化材料を充填して抵抗変化材料からなる微細なドットを形成する工程とを有する

ことを特徴とする抵抗変化型不揮発性メモリの製造方法である。

この第2の発明においては、上記以外のことについては、その性質に反しない限り、第1の発明に関連して述べたことが成立する。

電極上に抵抗変化材料薄膜を形成する工程と、

上記抵抗変化材料薄膜上に、ドット状凝集部と他の凝集部とからなるミクロ相分離構造を有するブロックコポリマーを形成し、このブロックコポリマーの上記他の凝集部を除去する工程と、

上記他の凝集部を除去した上記ブロックコポリマーをマスクとして上記抵抗変化材料薄膜をエッチングすることにより微細なドットを形成する工程とを有する

ことを特徴とする抵抗変化型不揮発性メモリの製造方法である。

この第3の発明においては、上記以外のことについては、その性質に反しない限り、第1および第2の発明に関連して述べたことが成立する。

電極上の抵抗変化材料からなる微細なドットに対し、探針と電極とを用いて電圧を印加することにより抵抗変化材料の抵抗値を変化させ、これを記録ビットとするようにした

ことを特徴とする記録方法である。

電極上の抵抗変化材料からなる微細なドットに探針を接触または接近させることにより記録ビットの内容を読み出すようにした

ことを特徴とする再生方法である。

電極上の抵抗変化材料からなる微細なドットに対し、探針と電極とを用いて電圧を印加することにより記録ビットの内容を消去するようにした

ことを特徴とする消去方法である。

第4〜第6の発明においては、上記以外のことについては、その性質に反しない限り、第1の発明に関連して述べたことが成立する。

電極上に抵抗変化材料からなる微細なドットを有する

ことを特徴とする抵抗変化材料微細構造体である。

電極上に細孔を有する薄膜を形成する工程と、

上記細孔の内部に抵抗変化材料を充填して抵抗変化材料からなる微細なドットを形成する工程とを有する

ことを特徴とする抵抗変化材料微細構造体の製造方法である。

電極上に抵抗変化材料薄膜を形成する工程と、

上記抵抗変化材料薄膜上に、ドット状凝集部と他の凝集部とからなるミクロ相分離構造を有するブロックコポリマーを形成し、このブロックコポリマーの上記他の凝集部を除去する工程と、

上記他の凝集部を除去した上記ブロックコポリマーをマスクとして上記抵抗変化材料薄膜をエッチングすることにより微細なドットを形成する工程とを有する

ことを特徴とする抵抗変化材料微細構造体の製造方法である。

第7〜第9の発明においては、上記以外のことについては、その性質に反しない限り、第1〜第3の発明に関連して述べたことが成立する。

図1はこの発明の第1の実施形態による抵抗変化型不揮発性メモリを示す。

図1に示すように、この抵抗変化型不揮発性メモリにおいては、基板11上にナノテンプレート層12が設けられている。このナノテンプレート層12にはナノホール13が二次元アレイ状の配列、例えば六方格子や正方格子状の配列で設けられている。そして、ナノホール13の内部に抵抗変化材料からなるナノドット14が埋め込まれている。ナノテンプレート層12は、Al薄膜を陽極酸化することにより形成されるポーラスアルミナ、Al−Hf合金薄膜を陽極酸化することにより形成されるポーラス酸化物、ブロックコポリマーのミクロ層分離構造、SiO2 膜等からなる。ナノドット14を構成する抵抗変化材料は、例えば、既に挙げたものの中から必要に応じて選ぶことができる。ナノホール13の直径あるいはナノドット14の直径は例えば5〜200nm、高さは例えば10〜250nm、好適には50〜120nm、配列間隔は例えば200nm程度以下である。

まず、基板11上にCVD法、スパッタリング法等により密着層16を形成した後、その上にスパッタリング法、真空蒸着法等により金属電極15を形成する。

MOD法では、金属カルボン酸塩、金属アルコキシド、金属アセチルアセトナート等の金属錯体を適当な溶媒と組み合わせて使用する例が多い。例えば、CrをドープしたSrTiO3 やLaをドープしたSrTiO3 を成膜する場合、Sr成分の原料としてはカルボン酸ストロンチウム、Ti成分の原料としてはチタンアルコキシド、Cr成分の原料としてはカルボン酸クロム、La成分の原料としてはカルボン酸ランタンをそれぞれ用いることができる。カルボン酸ストロンチウム、カルボン酸クロム、カルボン酸ランタンの一般式はそれぞれSr(Cn H2n-1COO)2 、Cr(Cn H2n-1COO)3 、La(Cn H2n-1COO)3 で表され、具体的には下記のカルボン酸のSr塩、Cr塩、La塩が挙げられる。すなわち、これらのカルボン酸は、2−エチルへキシル酸、酢酸、n−酪酸、n−カプロン酸、2−メチルブタン、2−エチル酪酸、2,2−ジメチルブタン、イソ吉草酸、3,3−ジメチル酪酸、2,3−ジメチル酪酸、4−メチルペンタン酸、n−吉草酸、2−メチル吉草酸、3−メチル吉草酸、n−ヘキサン酸、n−カプリル酸、2−エチルヘキシル酸、5−メチルカプロン酸、イソカプリル酸、乳酸、α−オキシ酪酸、β−オキシ酪酸、α−オキソイソ酪酸、ペラルゴン酸、カプリン酸、ラウリン酸等である。

MOD法では、このMOD溶液をナノテンプレート層12上に塗布し、乾燥、仮焼、本焼成を行うことにより所望の組成を有する抵抗変化材料を形成する。

以上のようにして、目的とする抵抗変化型不揮発性メモリが製造される。

なお、図4に示すように金属電極15とナノテンプレート層12との間に導電性酸化物層17を設ける場合には、金属電極15上に導電性酸化物層17を形成した後、その上にナノテンプレート層12を形成する。この導電性酸化物層17の形成方法としては、抵抗変化材料の成膜方法と同様な方法を用いることができる。

図5に示すように、この記録再生システムにおいては、走査型プローブ顕微鏡の探針21と抵抗変化型不揮発性メモリの金属電極15との間に電圧を印加することにより、各ナノドット14に対する情報の書き込み(記録)、読み出し(再生)および消去を行う。この走査型プローブ顕微鏡は、探針21と抵抗変化型不揮発性メモリの金属電極15との間に電圧を印加することができればよく、原子間力を検出する原子間力顕微鏡(AFM:Atomic Force Microscope)、トンネル電流を検出する走査型トンネル顕微鏡(AFM:Scanning Tunneling Microscope)等、どのような原理のものを利用してもよい。図2に示す例では、AFMを利用して、導電性カンチレバー探針としての探針21の先端を抵抗変化型不揮発性メモリの抵抗変化材料からなるナノドット14の上部に接触させて適切な電圧を印加することができる構造になっている。ナノドット14への情報の書き込みは、具体的には、探針21と金属電極15との間に所定の電圧パルスを印加してナノドット14の抵抗値を所定の値に設定することにより行う。ナノドット14からの情報の読み出しは、具体的には、探針21と金属電極15との間に所定の電圧を印加した時に流れる電流を検出することにより行う。また、ナノドット14の情報の消去は、具体的には、探針21と金属電極15との間に所定の電圧パルスを印加してナノドット14の抵抗値を所定の初期値に設定することにより行う。

図6に示すように、この抵抗変化型不揮発性メモリにおいては、基板11上に抵抗変化材料からなるナノドット14が立設して設けられており、ナノテンプレート層12は設けられていない。これらのナノドット14の間の部分には、必要に応じてSiO2 膜等の絶縁体が埋め込まれる。

上記以外の構成は第1の実施形態と同様であるので、説明を省略する。

まず、第1の実施形態と同様にして、基板11上に密着層16を形成した後、その上に金属電極15を形成する。

次に、図10に示すように、金属電極15上に抵抗変化材料薄膜31を成膜する。

この後、ナノテンプレート層33をエッチングにより除去する。

以上のようにして、目的とする抵抗変化型不揮発性メモリが製造される。

この第2の実施形態によれば、第1の実施形態と同様な利点を得ることができる。

抵抗変化材料は、一つのコンデンサ状構造を一つのメモリ素子として使用することが可能であり、クロスポイント型と称されるメモリセル構造を適用することができる。一つのメモリ素子中にトランジスタを必要とするフラッシュメモリやFeRAM等の従来の不揮発性メモリと比べて、回路およびプロセスを簡素化できるので、集積度の向上とコスト低減とが見込まれる。

実施例1に基づいて製造した抵抗変化型不揮発性メモリの構造を図15に示す。

この抵抗変化型不揮発性メモリの製造方法は次のとおりである。

基板11としてSi(001)基板を用い、その上にSiO2 膜16aおよびTiO2 膜16bを順次形成して密着層16を形成し、さらにその上に厚さ約100nmのPt膜を形成して金属電極15を形成した。TiO2 膜16bの代わりにTi膜を用いることもできる。

次に、このAl薄膜の陽極酸化を以下のようにして行う。上記のSi基板11上のAl薄膜を陽極にし、対向電極となるPt板を陰極にして、0.3〜0.5Mのシュウ酸水溶液中、5〜15℃において、50Vの直流電圧を5分印加して、ポーラスアルミナからなるナノテンプレート層12のナノホール13がPt膜からなる金属電極15の表面に達するまで陽極酸化を行った。金属電極15へのナノホール13の到達はモニターしている電流値により確認した。陽極酸化後、純水およびイソプロピルアルコールによる洗浄を行った。

以上の陽極酸化工程により、直径約100nm以下、深さ約200nmのナノホール13を有するポーラスアルミナからなるナノテンプレート層12を形成することができる。

図16に、二次元アレイ状に配列したナノホール13にナノドット14が充填されたナノテンプレート層12の一例を示す。

まず、SPMのカンチレバー探針を電源ソースの出力端子の一方に接続し、CrドープSrTiO3 からなるナノドット14の下の金属電極15をもう一方の端子に接続する。そして、所望のナノドット14の位置にSPMのカンチレバー探針をコンタクトさせ、DC電圧+5Vまたは−5Vを1秒間印加する。この作業を所望のナノドット14に対して行うことにより各ナノドット14に所望の抵抗値を書き込み、保持させることができる。このようにして、抵抗変化を利用した記録ビットの書き込みが完了する。

実施例2に基づいて製造した抵抗変化型不揮発性メモリの構造は図15に示すものと同じである。

この抵抗変化型不揮発性メモリの製造方法は次のとおりである。

ナノホール13を有するポーラスアルミナからなるナノテンプレート層12の形成までは実施例1と同様にして行う。

実施例1と同様の方法により、CrドープSrTiO3 からなるナノドット14を記録ビットとした書き込み、読み出しが可能である。

実施例3に基づいて製造した抵抗変化型不揮発性メモリの構造は図15に示すものと同じである。

この抵抗変化型不揮発性メモリの製造方法は次のとおりである。

金属電極15の形成までは実施例1と同様にして行う。

平均分子量が約65000のポリスチレン(PS)とポリメタクリレート(PMMA)とからなり、PMMAの体積分率が約20体積%であるブロックコポリマーを1〜10重量%のトルエン溶液として調製し、上記の基板11上にスピンコート法により形成した。このとき、得られるブロックコポリマー薄膜51の膜厚はブロックコポリマー溶液の濃度やスピンコートの回転数に依存する。典型的には、溶液濃度2重量%、回転数3000rpmにて成膜すると約200nmの膜厚のブロックコポリマー薄膜51が形成される。

次に、基板11をトルエン溶液中に30分間浸漬することにより、ブロックコポリマー薄膜51を溶解除去する。その結果、直径30nm、ドット間隔30〜40nm、高さ70nmの円柱状のCrドープSrTiO3 からなるナノドット14が形成される。

続いて、電気炉にて、酸素雰囲気下、700℃において1時間熱処理して、ナノドット14を構成するCrドープSrTiO3 の結晶化を促した。

この実施例3では、実施例1と同様の方法によりCrドープSrTiO3 からなるナノドット14を記録ビットとした書き込み、読み出しが可能である。

実施例4に基づいて製造した抵抗変化型不揮発性メモリの構造は図15に示すものと同じである。

この抵抗変化型不揮発性メモリの製造方法は次のとおりである。

金属電極15の形成までは実施例1と同様にして行う。

次に、実施例3と同様に、SiO2 膜61上にブロックコポリマーを利用してナノホール62を有するナノテンプレート層63を形成する。

次に、実施例2と同様にして、PLD法により、SiO2 膜61のナノホール64に抵抗変化材料としてCrドープSrTiO3 膜を室温で堆積し、ナノドット14を形成した。CrドープSrTiO3 膜の膜厚は、SiO2 膜61の膜厚100nmを越えない膜厚として70nmとした。

続いて、電気炉にて、酸素雰囲気下、700℃において1時間熱処理して、ナノドット14を構成するCrドープSrTiO3 の結晶化を促した。

この実施例4では、実施例1と同様の方法によりCrドープSrTiO3 からなるナノドット14を記録ビットとした書き込み、読み出しが可能である。

実施例5に基づいて製造した抵抗変化型不揮発性メモリの構造は図8に示すものと同じである。

この抵抗変化型不揮発性メモリの製造方法は次のとおりである。

金属電極15の形成までは実施例1と同様にして行う。

次に、このCrドープSrTiO3 膜の上に、ブロックコポリマーによるナノテンプレート層33を形成する(図11参照)。実施例3および4で用いたブロックコポリマーによるナノテンプレート層は、ポリスチレンが構成する海にPMMAの島が存在し、そのPMMAを除去した結果形成されるナノテンプレート層であったが、この実施例5では、その二つがネガ・ポジ反転したブロックコポリマーによるナノテンプレート層を用いる。

平均分子量が約65000のポリスチレン(PS)とポリメタクリレート(PMMA)とからなり、PMMAの体積分率が約80体積%であるブロックコポリマーを1〜10重量%のトルエン溶液として調製し、上記の基板11上にスピンコート法により形成した。このとき、得られるブロックコポリマー薄膜の膜厚はブロックコポリマー溶液の濃度やスピンコートの回転数に依存する。典型的には、溶液濃度2重量%、回転数3000rpmにて成膜すると約200nmの膜厚のブロックコポリマー薄膜が形成される。

次に、上記のミクロ相分離構造を有するブロックコポリマー薄膜にハロゲンランプにより紫外線照射を行い、続いて酢酸中(1N)超音波処理を10分間行うことにより、PMMA部をエッチングする。その結果、PSからなるドット状凝集部が残り、ナノドットテンプレート層が形成される。

この実施例5では、実施例1と同様の方法によりCrドープSrTiO3 からなるナノドット14を記録ビットとした書き込み、読み出しが可能である。

例えば、上述の実施形態および実施例において挙げた数値、構造、材料、プロセスなどはあくまでも例に過ぎず、必要に応じてこれらと異なる数値、構造、材料、プロセスなどを用いてもよい。

Claims (32)

- 電極上に抵抗変化材料からなる微細なドットを有する

ことを特徴とする抵抗変化型不揮発性メモリ。 - 上記電極上に細孔を有する薄膜を有し、上記細孔の内部に上記抵抗変化材料が存在して上記ドットが形成されていることを特徴とする請求項1記載の抵抗変化型不揮発性メモリ。

- 上記薄膜がアルミナからなることを特徴とする請求項2記載の抵抗変化型不揮発性メモリ。

- 上記薄膜がアルミニウムを陽極酸化することにより形成されたポーラスアルミナからなることを特徴とする請求項2記載の抵抗変化型不揮発性メモリ。

- 上記薄膜がアルミニウム−ハフニウム合金を陽極酸化することにより形成されたポーラス材料からなることを特徴とする請求項2記載の抵抗変化型不揮発性メモリ。

- 上記薄膜が、ドット状凝集部と他の凝集部とからなるミクロ相分離構造を有するブロックコポリマーの上記ドット状凝集部を除去したものからなることを特徴とする請求項2記載の抵抗変化型不揮発性メモリ。

- 上記薄膜が絶縁体からなることを特徴とする請求項2記載の抵抗変化型不揮発性メモリ。

- 上記ドットの直径が5〜200nmであることを特徴とする請求項1記載の抵抗変化型不揮発性メモリ。

- 上記細孔の直径が5〜200nmであることを特徴とする請求項2記載の抵抗変化型不揮発性メモリ。

- 上記ドットの高さが10〜250nmであることを特徴とする請求項1記載の抵抗変化型不揮発性メモリ。

- 上記ドットが周期的に配列していることを特徴とする請求項1記載の抵抗変化型不揮発性メモリ。

- 上記抵抗変化材料が、遷移金属を0.01〜10モル%ドープした化学式ABO3 またはBO2 で表される物質であって、AがMg、Ca、SrおよびBaからなる群より選ばれた少なくとも一種からなり、BがTi、ZrおよびHfからなる群より選ばれた少なくとも一種からなるものからなることを特徴とする請求項1記載の抵抗変化型不揮発性メモリ。

- 上記遷移金属が、Cr、Mn、V、Fe、Co、NiおよびCuからなる群より選ばれた少なくとも一種からなることを特徴とする請求項12記載の抵抗変化型不揮発性メモリ。

- 上記電極が金属電極であることを特徴とする請求項1記載の抵抗変化型不揮発性メモリ。

- 上記電極が、Ir、Pt、Ru、Rh、Pd、Au、Cr、Ni、CuおよびAlからなる群より選ばれた少なくとも一種からなる単層構造または多層構造を有することを特徴とする請求項1記載の抵抗変化型不揮発性メモリ。

- 上記電極と上記ドットとの間に導電性酸化物層を有することを特徴とする請求項1記載の抵抗変化型不揮発性メモリ。

- 上記導電性酸化物層が、LaドープSrTiO3 、NbドープSrTiO3 、SrRuO3 、Sr2 RuO4 、SrCrO3 、LaTiO3 、(La,Sr)Cu2 O4 、(Nd,Ce)Cu2 O4 およびYBa2 Cu3 O7-x からなる群より選ばれた少なくとも一種からなることを特徴とする請求項16記載の抵抗変化型不揮発性メモリ。

- 上記抵抗変化材料が、Crを0.01〜10モル%ドープしたSrTiO3 またはSrZrO3 からなり、上記導電性酸化物層がLaドープSrTiO3 からなることを特徴とする請求項16記載の抵抗変化型不揮発性メモリ。

- 上記電極がシリコン基板上に形成されていることを特徴とする請求項1記載の抵抗変化型不揮発性メモリ。

- 電極上に細孔を有する薄膜を形成する工程と、

上記細孔の内部に抵抗変化材料を充填して抵抗変化材料からなる微細なドットを形成する工程とを有する

ことを特徴とする抵抗変化型不揮発性メモリの製造方法。 - 上記電極上にアルミニウム薄膜を形成した後、このアルミニウム薄膜を陽極酸化することにより上記薄膜を形成することを特徴とする請求項20記載の抵抗変化型不揮発性メモリの製造方法。

- 上記電極上にアルミニウム−ハフニウム合金薄膜を形成した後、このアルミニウム−ハフニウム合金薄膜を陽極酸化することにより上記薄膜を形成することを特徴とする請求項20記載の抵抗変化型不揮発性メモリの製造方法。

- 上記電極上に、ドット状凝集部と他の凝集部とからなるミクロ相分離構造を有するブロックコポリマーを形成した後、このブロックコポリマーの上記ドット状凝集部を除去することにより上記薄膜を形成することを特徴とする請求項20記載の抵抗変化型不揮発性メモリの製造方法。

- 上記電極上に絶縁膜を形成し、次いでこの絶縁膜上にドット状凝集部と他の凝集部とからなるミクロ相分離構造を有するブロックコポリマーを形成し、次いでこのブロックコポリマーの上記ドット状凝集部を除去した後、このブロックコポリマーをマスクとして上記絶縁膜をエッチングすることにより上記薄膜を形成することを特徴とする請求項20記載の抵抗変化型不揮発性メモリの製造方法。

- 電極上に抵抗変化材料薄膜を形成する工程と、

上記抵抗変化材料薄膜上に、ドット状凝集部と他の凝集部とからなるミクロ相分離構造を有するブロックコポリマーを形成し、このブロックコポリマーの上記他の凝集部を除去する工程と、

上記他の凝集部を除去した上記ブロックコポリマーをマスクとして上記抵抗変化材料薄膜をエッチングすることにより微細なドットを形成する工程とを有する

ことを特徴とする抵抗変化型不揮発性メモリの製造方法。 - 電極上の抵抗変化材料からなる微細なドットに対し、探針と上記電極とを用いて電圧を印加することにより上記抵抗変化材料の抵抗値を変化させ、これを記録ビットとするようにした

ことを特徴とする記録方法。 - 上記探針が走査型プローブ顕微鏡の探針であることを特徴とする請求項26記載の記録方法。

- 電極上の抵抗変化材料からなる微細なドットに探針を接触または接近させることにより記録ビットの内容を読み出すようにした

ことを特徴とする再生方法。 - 電極上の抵抗変化材料からなる微細なドットに対し、探針と上記電極とを用いて電圧を印加することにより記録ビットの内容を消去するようにした

ことを特徴とする消去方法。 - 電極上に抵抗変化材料からなる微細なドットを有する

ことを特徴とする抵抗変化材料微細構造体。 - 電極上に細孔を有する薄膜を形成する工程と、

上記細孔の内部に抵抗変化材料を充填して抵抗変化材料からなる微細なドットを形成する工程とを有する

ことを特徴とする抵抗変化材料微細構造体の製造方法。 - 電極上に抵抗変化材料薄膜を形成する工程と、

上記抵抗変化材料薄膜上に、ドット状凝集部と他の凝集部とからなるミクロ相分離構造を有するブロックコポリマーを形成し、このブロックコポリマーの上記他の凝集部を除去する工程と、

上記他の凝集部を除去した上記ブロックコポリマーをマスクとして上記抵抗変化材料薄膜をエッチングすることにより微細なドットを形成する工程とを有する

ことを特徴とする抵抗変化材料微細構造体の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004042849A JP2005236003A (ja) | 2004-02-19 | 2004-02-19 | 抵抗変化型不揮発性メモリ、抵抗変化型不揮発性メモリの製造方法、記録方法、再生方法、消去方法、抵抗変化材料微細構造体および抵抗変化材料微細構造体の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004042849A JP2005236003A (ja) | 2004-02-19 | 2004-02-19 | 抵抗変化型不揮発性メモリ、抵抗変化型不揮発性メモリの製造方法、記録方法、再生方法、消去方法、抵抗変化材料微細構造体および抵抗変化材料微細構造体の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005236003A true JP2005236003A (ja) | 2005-09-02 |

| JP2005236003A5 JP2005236003A5 (ja) | 2006-10-05 |

Family

ID=35018642

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004042849A Pending JP2005236003A (ja) | 2004-02-19 | 2004-02-19 | 抵抗変化型不揮発性メモリ、抵抗変化型不揮発性メモリの製造方法、記録方法、再生方法、消去方法、抵抗変化材料微細構造体および抵抗変化材料微細構造体の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005236003A (ja) |

Cited By (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2007052426A1 (ja) * | 2005-11-02 | 2007-05-10 | Sharp Kabushiki Kaisha | クロスポイント構造の半導体記憶装置 |

| JP2008141193A (ja) * | 2006-11-21 | 2008-06-19 | Samsung Electronics Co Ltd | 不揮発性メモリ素子及びその製造方法 |

| WO2008132899A1 (ja) * | 2007-04-17 | 2008-11-06 | Nec Corporation | 抵抗変化素子及び該抵抗変化素子を含む半導体装置 |

| JP2009295944A (ja) * | 2008-06-09 | 2009-12-17 | Sharp Corp | 可変抵抗素子及びその製造方法 |

| WO2010039568A1 (en) * | 2008-09-30 | 2010-04-08 | Sandisk 3D Llc | Self-assembly process for memory array |

| WO2011000316A1 (zh) * | 2009-07-02 | 2011-01-06 | 黑龙江大学 | 纳米结构快速开关忆阻器及其制造方法 |

| CN102522418A (zh) * | 2011-12-29 | 2012-06-27 | 北京大学 | 具有交叉阵列结构的自整流阻变存储器及制备方法 |

| JP2012209410A (ja) * | 2011-03-29 | 2012-10-25 | Seiko Epson Corp | 半導体装置の製造方法、強誘電体素子の製造方法および電子機器の製造方法 |

| US8462539B2 (en) | 2009-02-20 | 2013-06-11 | Murata Manufacturing Co., Ltd. | Resistive memory element and use thereof |

| US8542520B2 (en) | 2009-02-20 | 2013-09-24 | Murata Manufacturing Co., Ltd. | Resistive memory element and use thereof |

| JP2015015425A (ja) * | 2013-07-08 | 2015-01-22 | 株式会社東芝 | パターン形成方法 |

| US8946672B2 (en) | 2009-11-11 | 2015-02-03 | Nec Corporation | Resistance changing element capable of operating at low voltage, semiconductor device, and method for forming resistance change element |

| JP2015176895A (ja) * | 2014-03-13 | 2015-10-05 | 株式会社東芝 | 不揮発性メモリ |

| CN108389964A (zh) * | 2018-04-03 | 2018-08-10 | 集美大学 | 以纳米遮蔽层进行离子定位注入的阻变存储器制备方法 |

| WO2019175673A1 (en) * | 2018-03-16 | 2019-09-19 | 4D-S, Ltd. | Resistive memory device having a template layer |

| CN110600499A (zh) * | 2015-04-16 | 2019-12-20 | 意法半导体公司 | 高密度电阻性随机存取存储器(rram) |

| CN111701588A (zh) * | 2020-05-08 | 2020-09-25 | 昆明理工大学 | 一种贵金属纳米多孔材料及其制备方法和应用 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001278700A (ja) * | 2000-03-29 | 2001-10-10 | Canon Inc | ナノ構造体、その製造方法および磁気デバイス |

| JP2002537627A (ja) * | 1999-02-17 | 2002-11-05 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 情報を保存するマイクロ電子デバイスとその方法 |

| JP2004502554A (ja) * | 2000-03-22 | 2004-01-29 | ユニバーシティー オブ マサチューセッツ | ナノシリンダー・アレイ |

-

2004

- 2004-02-19 JP JP2004042849A patent/JP2005236003A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002537627A (ja) * | 1999-02-17 | 2002-11-05 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 情報を保存するマイクロ電子デバイスとその方法 |

| JP2004502554A (ja) * | 2000-03-22 | 2004-01-29 | ユニバーシティー オブ マサチューセッツ | ナノシリンダー・アレイ |

| JP2001278700A (ja) * | 2000-03-29 | 2001-10-10 | Canon Inc | ナノ構造体、その製造方法および磁気デバイス |

Cited By (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2007052426A1 (ja) * | 2005-11-02 | 2007-05-10 | Sharp Kabushiki Kaisha | クロスポイント構造の半導体記憶装置 |

| JP2008141193A (ja) * | 2006-11-21 | 2008-06-19 | Samsung Electronics Co Ltd | 不揮発性メモリ素子及びその製造方法 |

| US8362456B2 (en) | 2007-04-17 | 2013-01-29 | Nec Corporation | Resistance change element and semiconductor device including the same |

| WO2008132899A1 (ja) * | 2007-04-17 | 2008-11-06 | Nec Corporation | 抵抗変化素子及び該抵抗変化素子を含む半導体装置 |

| JP5526776B2 (ja) * | 2007-04-17 | 2014-06-18 | 日本電気株式会社 | 抵抗変化素子及び該抵抗変化素子を含む半導体装置 |

| JP2009295944A (ja) * | 2008-06-09 | 2009-12-17 | Sharp Corp | 可変抵抗素子及びその製造方法 |

| WO2010039568A1 (en) * | 2008-09-30 | 2010-04-08 | Sandisk 3D Llc | Self-assembly process for memory array |

| US8008213B2 (en) | 2008-09-30 | 2011-08-30 | Sandisk 3D Llc | Self-assembly process for memory array |

| JP5459516B2 (ja) * | 2009-02-20 | 2014-04-02 | 株式会社村田製作所 | 抵抗記憶素子およびその使用方法 |

| US8462539B2 (en) | 2009-02-20 | 2013-06-11 | Murata Manufacturing Co., Ltd. | Resistive memory element and use thereof |

| US8542520B2 (en) | 2009-02-20 | 2013-09-24 | Murata Manufacturing Co., Ltd. | Resistive memory element and use thereof |

| WO2011000316A1 (zh) * | 2009-07-02 | 2011-01-06 | 黑龙江大学 | 纳米结构快速开关忆阻器及其制造方法 |

| US9231207B2 (en) | 2009-11-11 | 2016-01-05 | Nec Corporation | Method for forming resistance changing element capable of operating at low voltage |

| US8946672B2 (en) | 2009-11-11 | 2015-02-03 | Nec Corporation | Resistance changing element capable of operating at low voltage, semiconductor device, and method for forming resistance change element |

| JP2012209410A (ja) * | 2011-03-29 | 2012-10-25 | Seiko Epson Corp | 半導体装置の製造方法、強誘電体素子の製造方法および電子機器の製造方法 |

| CN102522418A (zh) * | 2011-12-29 | 2012-06-27 | 北京大学 | 具有交叉阵列结构的自整流阻变存储器及制备方法 |

| JP2015015425A (ja) * | 2013-07-08 | 2015-01-22 | 株式会社東芝 | パターン形成方法 |

| JP2015176895A (ja) * | 2014-03-13 | 2015-10-05 | 株式会社東芝 | 不揮発性メモリ |

| CN110600499A (zh) * | 2015-04-16 | 2019-12-20 | 意法半导体公司 | 高密度电阻性随机存取存储器(rram) |

| WO2019175673A1 (en) * | 2018-03-16 | 2019-09-19 | 4D-S, Ltd. | Resistive memory device having a template layer |

| US10622559B2 (en) | 2018-03-16 | 2020-04-14 | 4DS Memory, Limited | Resistive memory device having a template layer |

| US10734577B2 (en) | 2018-03-16 | 2020-08-04 | 4DS Memory, Limited | Resistive memory device having a template layer |

| TWI711198B (zh) * | 2018-03-16 | 2020-11-21 | 澳大利亞商4D S有限公司 | 具有一模板層之電阻式記憶體裝置 |

| US10847717B2 (en) | 2018-03-16 | 2020-11-24 | 4DS Memory, Limited | Resistive memory device having a template layer |

| US10862028B2 (en) | 2018-03-16 | 2020-12-08 | 4DS Memory, Limited | Resistive memory device having a template layer |

| US11043633B2 (en) | 2018-03-16 | 2021-06-22 | 4DS Memory, Limited | Resistive memory device having a template layer |

| CN108389964A (zh) * | 2018-04-03 | 2018-08-10 | 集美大学 | 以纳米遮蔽层进行离子定位注入的阻变存储器制备方法 |

| CN111701588A (zh) * | 2020-05-08 | 2020-09-25 | 昆明理工大学 | 一种贵金属纳米多孔材料及其制备方法和应用 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2005236003A (ja) | 抵抗変化型不揮発性メモリ、抵抗変化型不揮発性メモリの製造方法、記録方法、再生方法、消去方法、抵抗変化材料微細構造体および抵抗変化材料微細構造体の製造方法 | |

| JP4221660B2 (ja) | 細孔構造体及びその製造方法、メモリ装置及びその製造方法、吸着量分析装置、並びに磁気記録媒体 | |

| JP5204969B2 (ja) | 強誘電体酸化物人工格子および強誘電体酸化物人工格子の製造方法 | |

| Han et al. | Nanostructured ferroelectrics: fabrication and structure–property relations | |

| CN1925184B (zh) | 非易失存储器件及其制造方法 | |

| TWI316752B (en) | Vertical side wall active pin structures in a phase change memory and manufacturing methods | |

| KR101078125B1 (ko) | 다공성 물질을 이용한 비휘발성 나노 채널 메모리 소자 | |

| JPWO2005041303A1 (ja) | 抵抗変化素子、その製造方法、その素子を含むメモリ、およびそのメモリの駆動方法 | |

| JP2018520522A (ja) | 抵抗変化型メモリデバイスに用いるメモリ構造及びデータ記憶デバイスの製造に用いる方法 | |

| JP2016541109A (ja) | SiOxスイッチング素子の性能を改善するための多孔質SiOx材料 | |

| JP2005123361A (ja) | 抵抗変化型不揮発性メモリおよびその製造方法ならびに抵抗変化層の形成方法 | |

| CN111799369A (zh) | 拓扑磁结构及其制备方法、拓扑磁结构调控方法及存储器 | |

| CN102157686B (zh) | 一种表面阻态随电畴变化的存储器及其制备方法 | |

| CN109509753B (zh) | 一种高密度无损读取的铁电畴壁存储器 | |

| TWI493549B (zh) | 電阻式隨機存取記憶體 | |

| JP4383796B2 (ja) | ナノ構造体、及びその製造方法 | |

| Guo et al. | Self‐Rolling‐Up Enabled Ultrahigh‐Density Information Storage in Freestanding Single‐Crystalline Ferroic Oxide Films | |

| CN101533669A (zh) | 电阻式随机存储器用多层薄膜结构的电阻转变方式的调控 | |

| WO2006013826A1 (ja) | Bi層状化合物ナノプレート及びその配列体並びにそれらの製造方法とそれを用いた装置 | |

| JP2010199348A (ja) | 半導体メモリとその製造方法 | |

| CN112490359A (zh) | 一种基于AAO模板的Sb单元素纳米颗粒相变储存器及其制备方法 | |

| JP2008258616A (ja) | 不揮発性記憶装置のストレージ及びその形成方法 | |

| US8581222B2 (en) | Phase change memory device comprising bismuth-tellurium nanowires | |

| CN111146338B (zh) | 一种铁电二极管储存器及其制备方法 | |

| CN101673803A (zh) | 基于氧化铌薄膜的电阻随机存储器及其制备方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060823 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060823 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20081226 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100727 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100906 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101228 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110419 |