JP2005142319A - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2005142319A JP2005142319A JP2003376639A JP2003376639A JP2005142319A JP 2005142319 A JP2005142319 A JP 2005142319A JP 2003376639 A JP2003376639 A JP 2003376639A JP 2003376639 A JP2003376639 A JP 2003376639A JP 2005142319 A JP2005142319 A JP 2005142319A

- Authority

- JP

- Japan

- Prior art keywords

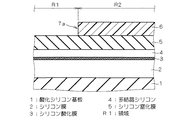

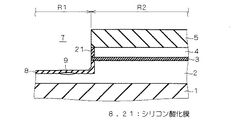

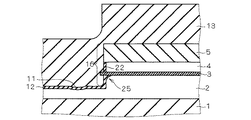

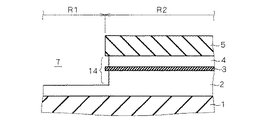

- silicon

- film

- trench

- silicon oxide

- oxide film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

- H10D30/0321—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] comprising silicon, e.g. amorphous silicon or polysilicon

- H10D30/0323—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] comprising silicon, e.g. amorphous silicon or polysilicon comprising monocrystalline silicon

-

- H10P36/07—

-

- H10W10/00—

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/322—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to modify their internal properties, e.g. to produce internal imperfections

- H01L21/3221—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to modify their internal properties, e.g. to produce internal imperfections of silicon bodies, e.g. for gettering

- H01L21/3226—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to modify their internal properties, e.g. to produce internal imperfections of silicon bodies, e.g. for gettering of silicon on insulator

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76264—SOI together with lateral isolation, e.g. using local oxidation of silicon, or dielectric or polycristalline material refilled trench or air gap isolation regions, e.g. completely isolated semiconductor islands

- H01L21/76283—Lateral isolation by refilling of trenches with dielectric material

-

- H10P90/1906—

-

- H10W10/01—

-

- H10W10/014—

-

- H10W10/061—

-

- H10W10/17—

-

- H10W10/181—

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Element Separation (AREA)

- Semiconductor Memories (AREA)

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003376639A JP2005142319A (ja) | 2003-11-06 | 2003-11-06 | 半導体装置の製造方法 |

| KR1020040082084A KR100654871B1 (ko) | 2003-11-06 | 2004-10-14 | 반도체 장치의 제조 방법 |

| TW093132342A TWI250607B (en) | 2003-11-06 | 2004-10-26 | Manufacturing method of semiconductor device |

| US10/978,796 US20050101070A1 (en) | 2003-11-06 | 2004-11-02 | Method of manufacturing semiconductor device |

| CNB2004100905397A CN1311539C (zh) | 2003-11-06 | 2004-11-05 | 半导体装置的制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003376639A JP2005142319A (ja) | 2003-11-06 | 2003-11-06 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005142319A true JP2005142319A (ja) | 2005-06-02 |

| JP2005142319A5 JP2005142319A5 (enExample) | 2006-12-14 |

Family

ID=34544369

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003376639A Withdrawn JP2005142319A (ja) | 2003-11-06 | 2003-11-06 | 半導体装置の製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20050101070A1 (enExample) |

| JP (1) | JP2005142319A (enExample) |

| KR (1) | KR100654871B1 (enExample) |

| CN (1) | CN1311539C (enExample) |

| TW (1) | TWI250607B (enExample) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20150139787A (ko) | 2014-06-04 | 2015-12-14 | 르네사스 일렉트로닉스 가부시키가이샤 | 반도체 장치의 제조 방법 |

| JP2016134614A (ja) * | 2015-01-22 | 2016-07-25 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5455530B2 (ja) | 2009-09-30 | 2014-03-26 | 株式会社トクヤマ | ポリシリコン金属汚染防止方法 |

| CN103887223A (zh) * | 2014-03-12 | 2014-06-25 | 上海华力微电子有限公司 | 降低炉管工艺金属污染的方法 |

| JP2021129042A (ja) * | 2020-02-14 | 2021-09-02 | キオクシア株式会社 | 半導体装置およびその製造方法 |

| CN113257734B (zh) * | 2021-04-30 | 2023-06-23 | 北海惠科半导体科技有限公司 | 半导体器件及其制作方法和芯片 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2955459B2 (ja) * | 1993-12-20 | 1999-10-04 | 株式会社東芝 | 半導体装置の製造方法 |

| JPH08340044A (ja) * | 1995-06-09 | 1996-12-24 | Rohm Co Ltd | 半導体装置及びその製造方法 |

| US5719085A (en) * | 1995-09-29 | 1998-02-17 | Intel Corporation | Shallow trench isolation technique |

| JP3296229B2 (ja) * | 1997-01-21 | 2002-06-24 | 株式会社デンソー | 半導体装置の製造方法 |

| US5817566A (en) * | 1997-03-03 | 1998-10-06 | Taiwan Semiconductor Manufacturing Company, Ltd. | Trench filling method employing oxygen densified gap filling silicon oxide layer formed with low ozone concentration |

| JPH113936A (ja) * | 1997-06-13 | 1999-01-06 | Nec Corp | 半導体装置の製造方法 |

| US5783476A (en) * | 1997-06-26 | 1998-07-21 | Siemens Aktiengesellschaft | Integrated circuit devices including shallow trench isolation |

| KR100268453B1 (ko) * | 1998-03-30 | 2000-11-01 | 윤종용 | 반도체 장치 및 그것의 제조 방법 |

| TW426874B (en) * | 1998-10-14 | 2001-03-21 | United Microelectronics Corp | Method for cleaning a semiconductor wafer |

| JP2000164569A (ja) * | 1998-11-25 | 2000-06-16 | Nec Corp | 半導体装置の製造方法 |

| TW461025B (en) * | 2000-06-09 | 2001-10-21 | Nanya Technology Corp | Method for rounding corner of shallow trench isolation |

| US6627484B1 (en) * | 2000-11-13 | 2003-09-30 | Advanced Micro Devices, Inc. | Method of forming a buried interconnect on a semiconductor on insulator wafer and a device including a buried interconnect |

| US6879000B2 (en) * | 2003-03-08 | 2005-04-12 | Taiwan Semiconductor Manufacturing Co., Ltd. | Isolation for SOI chip with multiple silicon film thicknesses |

| US6864152B1 (en) * | 2003-05-20 | 2005-03-08 | Lsi Logic Corporation | Fabrication of trenches with multiple depths on the same substrate |

-

2003

- 2003-11-06 JP JP2003376639A patent/JP2005142319A/ja not_active Withdrawn

-

2004

- 2004-10-14 KR KR1020040082084A patent/KR100654871B1/ko not_active Expired - Fee Related

- 2004-10-26 TW TW093132342A patent/TWI250607B/zh not_active IP Right Cessation

- 2004-11-02 US US10/978,796 patent/US20050101070A1/en not_active Abandoned

- 2004-11-05 CN CNB2004100905397A patent/CN1311539C/zh not_active Expired - Fee Related

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20150139787A (ko) | 2014-06-04 | 2015-12-14 | 르네사스 일렉트로닉스 가부시키가이샤 | 반도체 장치의 제조 방법 |

| US9947715B2 (en) | 2014-06-04 | 2018-04-17 | Renesas Electronics Corporation | Manufacturing method of semiconductor device |

| JP2016134614A (ja) * | 2015-01-22 | 2016-07-25 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| US9842871B2 (en) | 2015-01-22 | 2017-12-12 | Renesas Electronics Corporation | Method of manufacturing semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| KR100654871B1 (ko) | 2006-12-11 |

| CN1614762A (zh) | 2005-05-11 |

| US20050101070A1 (en) | 2005-05-12 |

| CN1311539C (zh) | 2007-04-18 |

| TWI250607B (en) | 2006-03-01 |

| TW200527587A (en) | 2005-08-16 |

| KR20050043622A (ko) | 2005-05-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6242323B1 (en) | Semiconductor device and process for producing the same | |

| CN101425521B (zh) | Soi衬底及其制造方法 | |

| US5223450A (en) | Method of producing semiconductor substrate having dielectric separation region | |

| JP2003017506A (ja) | L字型スペーサを利用する半導体トランジスタ及びその製造方法 | |

| JPH09321132A (ja) | 半導体装置のトレンチ素子分離方法 | |

| JP5121102B2 (ja) | 半導体装置の製造方法 | |

| JP3604072B2 (ja) | 半導体装置の製造方法 | |

| JP3063705B2 (ja) | 半導体装置の製造方法 | |

| JP2005142319A (ja) | 半導体装置の製造方法 | |

| JP2004006660A (ja) | 半導体装置の製造方法 | |

| JP2001007196A (ja) | 半導体装置の製造方法 | |

| KR100470573B1 (ko) | 반도체 장치의 제조 방법 | |

| KR20020018168A (ko) | 반도체장치의 제조방법 | |

| JPH0964319A (ja) | Soi基板およびその製造方法 | |

| JP4577680B2 (ja) | 半導体装置の製造方法 | |

| JP2005353892A (ja) | 半導体基板、半導体装置及びその製造方法 | |

| JP2001118919A (ja) | 半導体装置およびその製造方法 | |

| US11488837B2 (en) | Method for fabricating high-voltage (HV) transistor | |

| US6500729B1 (en) | Method for reducing dishing related issues during the formation of shallow trench isolation structures | |

| JP2004363121A (ja) | 半導体装置の製造方法 | |

| JPH10172922A (ja) | 半導体装置の製造方法 | |

| JP2005079215A (ja) | 半導体装置の製造方法 | |

| JP2007173694A (ja) | 半導体基板の作製方法 | |

| US6887767B2 (en) | Method for manufacturing semiconductor device | |

| JP3277957B2 (ja) | Soi半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061031 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061031 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20090204 |