JP2005116709A - 半導体集積回路装置およびその製造方法 - Google Patents

半導体集積回路装置およびその製造方法 Download PDFInfo

- Publication number

- JP2005116709A JP2005116709A JP2003347449A JP2003347449A JP2005116709A JP 2005116709 A JP2005116709 A JP 2005116709A JP 2003347449 A JP2003347449 A JP 2003347449A JP 2003347449 A JP2003347449 A JP 2003347449A JP 2005116709 A JP2005116709 A JP 2005116709A

- Authority

- JP

- Japan

- Prior art keywords

- integrated circuit

- semiconductor integrated

- light emitting

- circuit device

- emitting element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Led Device Packages (AREA)

- Electrodes Of Semiconductors (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Led Devices (AREA)

- Photo Coupler, Interrupter, Optical-To-Optical Conversion Devices (AREA)

Abstract

【課題】 簡易な構造でありながら高機能な信号処理機能や演算処理機能と光信号通信機能とを備えた、半導体集積回路装置およびその製造方法を提供する。

【解決手段】 入力される光信号を電気信号に変換する光電変換素子1と、その光電変換素子1から出力される電気信号に対して信号処理または演算処理を施す半導体集積回路2と、その半導体集積回路2で処理された電気信号を受けて、その電気信号を光信号に変換して出力する発光素子3とが、一つの半導体基板4に作り込まれている。このような主要部の構成により、本発明の半導体集積回路装置では、高速の光信号入力11および電気信号変換ならびに光信号出力14が、一つの半導体基板4内でダイレクトにかつ連続的に行われる。

【選択図】 図1

【解決手段】 入力される光信号を電気信号に変換する光電変換素子1と、その光電変換素子1から出力される電気信号に対して信号処理または演算処理を施す半導体集積回路2と、その半導体集積回路2で処理された電気信号を受けて、その電気信号を光信号に変換して出力する発光素子3とが、一つの半導体基板4に作り込まれている。このような主要部の構成により、本発明の半導体集積回路装置では、高速の光信号入力11および電気信号変換ならびに光信号出力14が、一つの半導体基板4内でダイレクトにかつ連続的に行われる。

【選択図】 図1

Description

本発明は、光通信システムなどに好適な半導体集積回路装置およびその製造方法に関する。

従来の、いわゆる光インターコネクト装置あるいは光半導体装置等では、外部から送られて来た光信号を、情報処理装置で処理可能な電気信号に変換することが行われていた。

あるいは、図21に一例を示したように、外部から送られて来た光信号11を、フォトダイオード1001により電気信号12に変換して、LSIのような半導体集積回路からなる論理回路チップ1002あるいは汎用コンピュータのような情報処理装置(図示省略)に入力する。論理回路チップ1002または情報処理装置では、フォトダイオード1001から送られて来た電気信号12に対して、例えば所定の増幅率で増幅したりA/D変換するなどの信号処理や、さらに複雑な情報処理あるいは演算処理等を施す。そしてその論理回路チップ1002等から出力された電気信号13を、レーザダイオード1003などによって光信号14に変換して、例えば外部の情報処理装置等(図示省略)へと出力する。

このようにして、従来の技術では、外部から送信されて来た光信号に対して信号処理や演算処理等を施して外部へと送出していた(特許文献1〜特許文献6)。

また、装置全体のさらなる小型化を企図して、半導体集積回路上にGaAs系の化合物半導体からなる面発光レーザ素子を、例えばバンプ接続等を介して実装し、半導体集積回路と受発光素子とを一つのモジュールとして装置化する試みなども試行されている(非特許文献1)。

特開平10−214995号公報

特開2001−135893号公報

特開平11−46014号公報

特開平9−293893号公報

特開平11−274315号公報

特開平7−64140号公報

Ext.Abst.Of2001 Int.Conf.SSDM p594〜595

しかしながら、上記のような従来の構成では、発光素子として化合物系の半導体素子を、例えば半導体集積回路や配線基板などの上に実装する必要があり、装置全体のさらなる小型化や構造の簡易化、あるいは装置としてのさらなる高機能化・信号処理や演算処理の高速化等が困難であるという問題があった。

本発明はかかる問題点に鑑みてなされたもので、その目的は、受光素子および発光素子ならびに半導体集積回路を一つの半導体基板に作り込んでいわゆるワンチップ化するなどして、簡易な構造でありながら高機能な信号処理機能や演算処理機能と光信号通信機能とを備えた、半導体集積回路装置およびその製造方法を提供することにある。

本発明による半導体集積回路装置は、入力される光信号を電気信号に変換する光電変換素子と、その光電変換素子から出力される電気信号に対して信号処理または演算処理を施す半導体集積回路と、その半導体集積回路で処理された電気信号を受けて、その電気信号を光信号に変換して出力する発光素子とが、一つの半導体基板に作り込まれている。

本発明による半導体集積回路装置の製造方法は、入力される光信号を電気信号に変換する光電変換素子と、その光電変換素子から出力される電気信号に対して信号処理または演算処理を施す半導体集積回路と、その半導体集積回路で処理された電気信号を受けてその電気信号を光信号に変換して出力する発光素子とを、一つの半導体基板に作り込む、というものである。

本発明による半導体集積回路装置またはその製造方法では、光電変換素子と、半導体集積回路と、発光素子とを、一つの半導体基板に作り込んで、例えばワンチップ化している。簡易な構造でありながら高機能な信号処理機能や演算処理機能と光信号通信機能とを備えたものとなっている。

なお、上記のように光電変換素子と半導体集積回路と発光素子とを一つの半導体基板に作り込むためには、発光素子を、発光部位がポーラスシリコン、またはSiGeからなるものであるようにすることが望ましい。あるいは、発光素子を、少なくとも発光部位に微結晶シリコンを用いてなるものであるようにすることが望ましい。

本発明の半導体集積回路装置またはその製造方法によれば、光電変換素子と、半導体集積回路と、発光素子とを、一つの半導体基板に作り込んで、例えばワンチップ化するようにしたので、簡易な構造でありながら高機能な信号処理機能や演算処理機能と光信号通信機能とを備えたものとなっており、これにより、装置全体のさらなる小型化や構造の簡易化あるいは装置としてのさらなる高機能化等が達成可能となる。

以下、本発明の実施の形態について図面を参照して詳細に説明する。

図1は、本発明の一実施の形態に係る半導体集積回路装置の主要部の構成を表した概念図である。

この半導体集積回路装置は、外部から入力される光信号(光信号入力11)を電気信号に変換して出力するPD(Photo Diode ;フォトダイオード,以下、PDと略称)のような光電変換素子1と、その光電変換素子1から出力される電気信号(電気信号入力12)に対して信号処理および演算処理を施す半導体集積回路2と、その半導体集積回路2で処理されて出力される電気信号(電気信号出力13)を受けて、その電気信号を光信号(光信号出力14)に変換して出力することで外部とのインターコネクトをとるLD(Laser Diode;レーザダイオード)のような発光素子3とを備えており、これら光電変換素子1,半導体集積回路2および発光素子3を一つの半導体基板4に作り込んで、その主要部が構成されている。

この半導体集積回路装置では、1チップ内で、外部から送信されて来た光信号入力11を電気信号入力12して信号処理および演算処理し、その処理してなる電気信号出力13を光信号出力14に変換して、外部へと送出する。

なお、半導体集積回路2をはじめとして、この半導体集積回路装置の全体を作動させるための電源電力は、外部から供給することが必要であるため、この半導体集積回路装置の表面には、GND端子5およびVcc端子6が設けられている。そして、これらのGND端子5およびVcc端子6の接続位置、ならびに光電変換素子1,発光素子3の各々の光軸位置などのアライメント(位置合せ)等を行って、図2に一例を示したように、この半導体集積回路装置(半導体基板4)を、配線基板または板体状の光インターフェイス(導光部材等)などのような基板15の表面に、フリップチップ状態で実装することなども可能である。

一般的な半導体基板の形成材料であるシリコンは、間接半導体であるので発光しないとされていたが、ポーラスシリコンやシリコン微結晶により発光する。また、シリコンとゲルマニウムとの混晶によりシリコンが発光する。

本実施の形態では、そのようなポーラスシリコンやシリコン微結晶あるいはシリコンとゲルマニウムとの混晶を用いて、発光素子3や光電変換素子1を、半導体集積回路2と共に同じシリコンからなる一つの半導体基板4に作り込む。

このように、光電変換素子1と、半導体集積回路2と、発光素子3とを、一つの半導体基板4に作り込んで、ワンチップ化することにより、本実施の形態に係る半導体集積回路装置は、簡易な構造でありながら高機能な信号処理機能や演算処理機能と光信号通信機能とを備えたものとなっている。その結果、装置全体のさらなる小型化や構造の簡易化あるいは装置としての高機能化等が達成される。

さらに詳細には、光電変換素子1と半導体集積回路2と発光素子3とが一つの半導体基板に作り込まれているので、光信号〜電気信号〜光信号という信号の変換経路の途中で、従来のような別体の素子どうしの間での電気的接続等を介在することなく、高速の光信号入力および電気信号変換ならびに光信号出力を一つの半導体基板内でダイレクトにかつ連続的に行うことができるので、信号処理の遅延がなく、また余分な素子が必要なくなり、装置の小型化・高機能化を達成することができる。

ここで、下記の各実施例でもさらに詳細に説明するが、発光素子3の発光部位をポーラスシリコンで構成する場合には、そのポーラスシリコンの上には、例えばCu(銅)やAl(アルミニウム)のような金属からなる配線層のような、光信号出力14の送出を遮る材質からなる種々の構造物を除去して、光出力窓を設けるようにすることが望ましい。また、さらには、光出力窓の側壁を金属膜で覆うようにしてもよい。あるいは、発光素子3は、例えば配線層が作り込まれた深さよりも半導体基板の表面に近い深さに形成することが望ましい。これらは、光信号出力14を有効に利用することができるようにするためである。

また、ポーラスシリコンからなる発光素子3は、ポーラス度の異なるポーラスシリコン多層膜を、反射層として発光部位のポーラスシリコンの下に備えるようにしてもよい。これは、発光素子3から出力される光信号出力14が正規の出射方向とは反対方向(正規の出射方向を上側とすると、下側)などに漏洩して光信号出力14の有効利用効率が低下することを、反射層の付設によって防ぐためである。

また、シリコン系材料としてSiGe(シリコンゲルマニウム)を用いると共に、そのシリコン系材料にエルビウム(Er)またはそれと置換可能な希土類元素をドープするようにしてもよい。この場合、受光素子3は、光電変換部位にSiGeを用いて構成することが望ましい。

あるいは、発光素子3は、少なくともその発光部位に微結晶シリコンを用いたものとすることなども可能である。

また、発光素子3または光電変換素子1のうち少なくともいずれか一種類の上に、光信号入力11や光信号出力14を集光または導光するためのレンズ系または導光部材などを付設するようにしてもよい。

また、上記のように発光素子3の発光部位に微結晶シリコンを用いる場合、シリコンをスパッタまたはCVD(Chemical Vapor Deposition)法で成膜した後、フォトリソグラフィ法によりナノレベルの微結晶を一括形成することで、発光素子3の発光部位を微結晶シリコンで構成するようにし、その微結晶シリコンを形成した後、水素ガスまたは水素プラズマによって、シリコンダングリングボンドを終端するようにすることなども可能である。

なお、光電変換素子1や発光素子3は、それぞれ1個ずつでもよいが、複数個をアレイ状に列設するようにしてもよい。

あるいは、複数個の光電変換素子1や発光素子3を一つの半導体基板4内に設ける場合には、複数個の光電変換素子1のそれぞれが、互いに波長の異なる光信号入力11を受け付けるようにしたり、複数個の発光素子3のそれぞれが、互いに波長の異なる光信号出力14を出力するようにしてもよい。このようにすることにより、一度に多チャンネルの光通信が可能となるので望ましい。

図3は本発明の第1の実施例に係るCMOS(Complementary Metal Oxide Semiconductor)集積回路装置の断面構成を表したものである。なお、この図3では、便宜上、光電変換素子1と半導体集積回路2と発光素子3との、全ての素子が一つずつ半導体基板4内に作り込まれている。なお、これらの素子は互いに隣接しているようにも見えるが、実際には、半導体基板4内での光電変換素子1と半導体集積回路2と発光素子3との位置関係は、もっと離れたものであってもよく、また光電変換素子1、半導体集積回路2、発光素子3はそれぞれ、複数個の素子が列設されているものであってもよいことは言うまでもない。特に、半導体集積回路2は、実際には、この図3に示したような1個のトランジスタ素子を極めて多数個に亘って集積して回路系を構成してなるものである。また、この図3では、図示および説明の簡潔化を図るため、フリップチップ等の電気的インターフェイスの部位などについては図示を省略してある。

このCMOS集積回路は、p型のシリコン基板を半導体基板4として用いて、その半導体基板4内に、光電変換素子1および発光素子3を、論理回路を主体とするCMOSトランジスタを含む半導体集積回路2と共に一体的に形成してなるものである。図3に示したように、光電変換素子1、半導体集積回路2、発光素子3の実質的な構造の主要部である素子部300と配線層400とは、互いに分離された層に形成されている。素子部300よりも上層に、例えばCuダマシンプロセスによって配線層400が形成される。光電変換素子1、半導体集積回路2、発光素子3のそれぞれと配線層400とは、コンタクトプラグ410によって電気的に接続されている。

光電変換素子1としては、本実施例ではシリコンpn接合フォトダイオード101の素子構造を採用した。この光電変換素子1では、シリコンpn接合フォトダイオード101で光電変換された電子は、ポテンシャル井戸102に蓄積されるが、読み出しの方式の一例として、ここではトランスファゲート103を備えて電子を読み出す構造とした。

発光素子3としては、ポーラスシリコン層301を用いたものとした。このポーラスシリコン層301は、電子を注入することによって発光する。この発光素子3のさらに詳細な構造の製造プロセスについては後述する。

半導体集積回路2は、CMOSトランジスタからなる、論理回路系を構成している半導体集積回路であるが、ここではnチャンネルトランジスタ201のみを示している。この半導体集積回路2を構成している各トランジスタ素子や発光素子3などの各素子は、STI(Shallow Trench Isolation)素子分離部202によって互いに分離されている。なお、この半導体集積回路2のnチャンネルトランジスタ201それ自体の素子構造は、一般的なもので構わないので、その詳細な説明についてはここでは省略する。

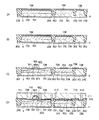

次に、図4,図5,図6を参照して、発光素子3の製造プロセスについて説明する。

まず、図4(A)に示したように、p型のシリコン基板である半導体基板4にSTI素子分離部202を形成する。このSTI素子分離部202の形成に当たっては、周知のリソグラフィ法およびエッチング技術によって、半導体基板4にトレンチ(溝)を形成し、このトレンチ部にHDP酸化膜のような酸化膜を埋没させる。そしてその酸化膜をCMP(Chemical and Mechanical Polishing : 化学的機械研磨)技術によって研磨加工して、トレンチ部以外のシリコン酸化膜を除去することで、STI素子分離部202が形成される。

続いて、図4(B)に示したように、発光部を形成すべき場所に、リンや砒素のような不純物を注入して、n型領域401を形成する。

さらに、図4(C)に示したように、n型領域401中のポーラスシリコン化すべき部分にボロンを注入して、深さ0.3〜3[μm]のp型領域402を形成する。

なお、3[μm]よりも厚い(深い)p型領域402を形成することが必要な場合には、あらかじめ、このような分布を持ったエピタキシャル基板を半導体基板4として使用するようにしてもよい。

次に、図4(D)に示したように、例えば表面技術Vol.46,No.5,p8−p13「多孔質シリコンの陽極化成」にて提案されているような陽極化成法により、発光部分となるポーラスシリコン層301を形成する。ポーラスシリコン化する部分以外はフォトレジスト等でマスキングしておき、p型領域402の表面からHF(フッ化水素)を浸漬させて、そのp型領域402をポーラス化する。このとき、深さ方向へのポーラス度は、時間と電流密度とによって制御することができる。なお、ポーラスシリコン層301上には、後述するようにエピタキシャル法でシリコン層を形成する必要があるため、陽極化成の初期は電流密度を小さく設定して表面近傍のポーラス度は小さめに形成し、その後は電流密度を上げて所望のポーラス度となるようにして多層構造とする。

ポーラスシリコン層301を形成した後、フォトレジスト等のマスキングを除去する。

引き続いて、図5(A)に示したように、エピタキシャル成長によりシリコン層403を形成する。このとき、シリコン層403を欠陥の少ない膜とするために、エピタキシャル成長の前に、例えば1000℃以上の高温で水素アニールして、表面付近のポーラス層のみを再配列させて平坦化する。そして、図5(B)に示したように、全面に熱酸化膜404を形成する。

続いて、シリサイド接合による電気接合部を形成する。すなわち、電極を形成する予定の部分406の熱酸化膜404を、例えば周知のフォトエッチング法などによるパターニング技術によって除去し、その後、図5(C)に示したように、周知のシリサイド技術等によって、Ni(ニッケル),Co(コバルト),Ti(チタン),W(タングステン)などの材料によるシリサイド層405を形成する。

そして、図5(D)に示したように、後述のコンタクトホールエッチングの際にストッパとするべく、例えばSiN(窒化シリコン)からなるエッチングストッパ膜407を成膜し、さらに酸化シリコン(SiO2 )膜,PSG(Phospho Silicate Glass) 、BPSG(Boron Phospho Silicate Glass)などからなる層間絶縁膜408を形成する。

引き続いて、図6(A)に示したように、コンタクトホール409を開口し、図6(B)に示したように、このコンタクトホール409に、例えばタングステンのような金属からなるコンタクトプラグ410を形成する。このコンタクトプラグ410は、TiN等のバリアメタルをスパッタやCVD法で成膜した後、CVD法によってタングステンを成長させ、次いでCMPによってホール部以外のタングステンを除去して形成することができる。その後、周知のCuダマシン技術等によって多層配線の配線層400を形成する。この配線層400以降のプロセスについては、半導体集積回路2のトランジスタ素子201や光電変換素子1の配線や電極と同じプロセスで形成するようにしてもよい。

図7(A)は発光素子3の構成の主要部を表した平面図、図7(B)はその断面図である。発光素子4は、上記のようにして形成されたポーラスシリコン層301を有している。拡散領域(ポーラスシリコン層301やSTI素子分離部202以外の、n型領域401を含むn型シリコンの領域)は、STI素子分離部202の下まで拡がっており、これによってポーラスシリコン層301に電流が流入できるようになっている。

この発光素子3の実質的な発光部はシリサイド化されていない部分であり、シリサイド層405の内側が該当する。例えば順方向に電圧を掛けることにより、この発光素子3のポーラスシリコン層301を中心とした発光部が発光する。なお、本実施例では、拡散領域がn型(n+ )で形成されている場合の一例について説明したが、拡散領域をp型(p+ )することも可能であることは言うまでもない。

さらに、図8に示したように、表面側への発光効率をさらに向上するために、ポーラスシリコン層301の直下に超格子構造の反射層411を形成するようにしてもよい。この反射層411は、ポーラス度の異なる2つの膜を複数層に亘って積層することによって形成することができる。また、その層の全体的なポーラス度および厚さは、陽極化成の電位および継続時間を調整することによって、所望のポーラス度および層厚とすることが可能である。

なお、光電変換素子1および半導体集積回路2については、周知の技術によって形成することができるので、その製造プロセスについての詳細な説明は省略するが、ここではその主な構造について、図9,図10の断面図を参照して説明する。

半導体集積回路2のnチャンネルトランジスタ201は、図9に示したように、nチャンネルCMOS型のトランジスタで、サイドウォール501に挟まれたゲート電極502、ゲート絶縁膜503、n型チャンネル領域504、シリサイド層505等を有する一般的なものである。

このnチャンネルトランジスタ201のゲート絶縁膜503は、発光素子3のシリコン酸化膜の膜厚とは異なり、より薄膜化されたものである。さらに、high−k材料であるハフニウム酸化膜等を使用するようにしてもよい。

ゲート電極502は、例えばポリシリコンやシリコンゲルマニウム(SiGe)により形成されており、さらに低抵抗化のためにNiやCoなどでシリサイド層505が形成されている。このシリサイド層505は発光素子3におけるシリサイド層405と同一工程において形成することができる。

光電変換素子1は、図10に示したように、pn接合型のフォトダイオード101の構造を有するもので、n拡散層601,603、p拡散層602、トランスファゲート103等を備えている。この光電変換素子1は通常のイオン注入法等を用いて作製することができる。

本実施例では、発光素子3(および光電変換素子1も可能)にSiGe材料を用いた場合の一例について、図11,図12,図13を参照して説明する。

まず、図11(A)に示したように、n型シリコン基板である半導体基板4における、発光素子3を形成すべき領域に、ボロンのような不純物を注入して、p型領域701を形成する。

続いて、図11(B)に示したように、SiGeの混晶あるいはSiGeとSiとからなる層を、交互に4〜20層程度に亘って積層して、SiGe層702を形成する。そしてこのSiGe層702の上に、Si層703を成長させる。このとき、SiGe層702には、発光効率を向上させるために、エルビウム(Er)のような希土類元素をドーピングするようにしてもよい。

続いて、図11(C)に示したように、発光領域(発光部)704以外のSiGe層702を、フォトリソグラフィ法およびエッチング法等を用いて、選択的に除去した後、全面にSiをエピタキシャル成長させてSi層を形成する。そして、図11(D)に示したように、Si層703の、発光領域704上の部分のみを、フォトリソグラフィ法およびエッチング法により、選択的に除去する。

引き続いて、図12(A)に示したように、全面を軽くエッチングした後、再度Siを全面に均一に成膜して、n型ドープのSi層706を形成する。

続いて、図12(B)に示したように、STI素子分離部202を実施例1の場合と同様のプロセスで形成する。このSTI素子分離部202によって発光層であるSiGe層702の表裏に電位が掛かるように分離を行う。すなわち、図12(A)のp型領域701がこのSTI素子分離部202の下まで広がるように深い注入を行う必要がある。

続いて、裏面の電極を形成すべき部分にボロン等の不純物を注入してp型領域707を形成する(図12(C))。

その後、図13(A)に示したように、表面酸化膜708を形成する。そして、実施例1と同様の方法で、Ni,Co,Ti,W等のシリサイド層709を形成する(図13(B))。

そして、例えばSiNからなるエッチングストッパ膜710を成膜し、さらに層間絶縁膜711を成膜した後、コンタクトホールを開口してそこにバリアメタルTiNを形成した後、例えはタングステン(W)からなるコンタクトプラグ410を形成する(図13(C))。この図13(C)に示した発光素子3の上面側から見た平面的な構成については、実施例1の発光素子3と同様のパターンとすることが可能である。

図14は、上記のような発光素子3に用いたSiGe系の材料を用いて形成されて光電変換素子1として用いられるフォトダイオードの構造の一例を表した断面図である。なお、発光素子3と同様の構造の部位には、発光素子3に付したものと同一の符号を付している。

基本的な構造は、発光素子3のものとほぼ同様であるが、発光素子3ではSiGe層702が光を出力するのに対して、この光電変換素子1ではSiGe層702は入力される光を電気的出力に変換する。また、この光電変換素子1では、光の受光率をさらに向上するために、Si層は除去してSiGe層702の上に直接的に表面酸化膜708を積層している。なお、詳細な説明および図示は省略するが、Strain−Siによるトランジスタを作製するために、SiGe層を用いるようにしてもよい。

この実施例3では、発光素子3の発光部の材料として微結晶シリコンを用いた場合の一例について説明する。

すなわち、この実施例3の半導体集積回路装置は、上記の実施例1のポーラスシリコン層301の代りに、微結晶シリコンを発光部として用いたものである。微結晶シリコンは、粒径が数[nm](ナノメートル)ないし数10[nm]の結晶粒であり、40℃レベルの低温のCVD成長法によって形成することができる。微結晶シリコンはこのように低温の成長が可能であるため、配線を形成した後に形成することが可能である。

図15は、実施例3の半導体集積回路装置の主要部の構成を表した断面図である。なお、図15では、実施例1または実施例2と同様の部位については同じ符号を付して示している。Cuのような導電体材料からなる配線層400よりも上層(換言すれば、半導体基板4の深さ方向で、配線層400よりも半導体基板4の表面(図15では上側の表面)に近い位置)に、TaN等からなるバリアメタル層801を形成し、CVD法によって微結晶シリコン層802を成長する。発光素子3以外の部位の微結晶シリコン膜については周知のフォトリソグラフィ法およびエッチング法によって除去し、電極803をシリサイド化によって形成する。半導体基板4の上側の表面ほぼ全面を覆うように窒化膜804を成膜する。そしてさらに半導体基板4の上面ほぼ全面を透明カバー805で覆う。この発光素子3では、配線層400および電極803のシリサイド膜を介して微結晶シリコン層802に電流を注入すると、微結晶シリコン層802が発光するように設定されている。

この実施例3の発光素子3の上面側から見た平面的な構成については、実施例1の発光素子3と同様のパターンとすることが可能である。

なお、光電変換素子1および半導体集積回路2については、実施例1の場合と同様に、一般的な周知の構成で構わないので、その詳細な説明については省略する。

なお、光電変換素子1および半導体集積回路2については、実施例1の場合と同様に、一般的な周知の構成で構わないので、その詳細な説明については省略する。

ここで、微結晶シリコン層802の成膜およびパターニング方法としては、図16(A)に示したように、スパッタ法またはCVD法などによってSi層812を成膜し、図16(B)に示したように、電子ビームまたはEUV等を用いた超解像描画技術によってフォトレジスト811をパターニングし、それを用いたドライエッチングを行った後、フォトレジストを剥離することによって、図16(C)の断面図および図17の平面図に示したように、数[nm]〜10[nm]程度の厚さの発光部を有する結晶シリコン層802を形成することも可能である。また、エッチングによるパターニングを行った後に、ダングリングボンドの終端として水素ガスによるアニール処理や水素プラズマ処理を実施することなども望ましい。ここで、図17では、斜線を付して示した部分が、それぞれナノメータ・スケールの発光素子3となる部分となっている。

図18は、光電変換素子1の受光領域および発光素子3の発光領域の上の層間絶縁膜および配線層を除去して、その部分に光窓を設けた場合の一例を表したものである。

すなわち、例えば配線が複雑化することなどに伴って、配線層400の層厚が増大して、配線層400や層間絶縁膜408の厚さが増大した場合には、外部から光電変換素子1へと入射される光信号や、発光素子3から外部へと出射される光信号が、配線層400や層間絶縁膜408を透過する際に、大幅に減衰する虞がある。

そこで、光電変換素子1の受光領域および発光素子3の発光領域の上の、層間絶縁膜408および配線層400を除去して光窓900を設けることで、その光窓900を通して光信号を減衰することなく通過させることができるようにすることにより、光信号の減衰を防止する。

なお、図18では図示を省略したが、光信号の拡散等を防止するために、上記のように層間絶縁膜408および配線層400を除去して設けられた光窓900の壁面(側壁)に、光を反射させる材質の金属材料等からなる反射膜を付設するようにしてもよい。その形成(着膜)方法としては、金属材料をCVD法などで成膜した後、エッチバックして、光窓900の壁面のみに反射膜を付設することなどが可能である。

図19は、例えば実施例1で説明した光電変換素子1の受光領域および発光素子3の発光領域の上に、それぞれレンズを設けた場合の、一例を表したものである。なお、図19では、実施例1と同様の部位については実施例の説明で用いたものと同じ符号を付して示している。

このように、光電変換素子1の受光領域および発光素子3の発光領域の上に、それぞれレンズ910を設けることにより、光の拡散に起因した光信号の利用効率の低下を防止することができる。なお、レンズ910は、例えばSiN膜や有機系材料からなる膜などを用いて構成することが可能である。

図20は、一つの半導体基板内に発光素子と半導体集積回路とを並行して製造するプロセスの主要な流れを表したものである。ここで、図20では、半導体集積回路2と発光素子3との、製造プロセスの流れを判りやすく対比するために、図のほぼ左半分に半導体集積回路2のプロセスを、右半分に発光素子3のプロセスを、それぞれ示している。また、既述の各実施例と同様の部位についてはそれらと同一の符号を付して示している。なお、一般的な半導体集積素子等の構造と同様の部位であって本発明の実施例としての主要部とは関係性の薄い部分の詳細な説明については省略する。

例えば図11から図12(B)までに示したようなプロセスを経て、図20(A)に示したようなSi層706を半導体基板4の表面に形成し、さらにその表面に、図20(B)に示したような表面酸化膜708を、例えば表面酸化法(酸化成長法)により形成する。そして半導体集積回路2には、不純物としてP(燐)を、例えばイオン注入法などによって、表面から注入する。それと並行して、発光素子3には、裏面の電極を形成すべき部分に不純物を注入してp型領域707を形成する。

その後、図20(C)に示したように、半導体集積回路2には、ゲート電極502、サイドウォール501等を形成して、いわゆるトランジスタ構造を構成した後、実施例1と同様の方法で、Ni,Co,Ti,W等を用いてオーミックコンタクト用のシリサイド層709を形成する。それと並行して、発光素子3にも、オーミックコンタクト用のシリサイド層709を形成する。

そして、図20(D)に示したように、発光素子3には、例えばSiNからなるエッチングストッパ膜710を成膜し、さらに層間絶縁膜711を成膜した後、コンタクトホールを開口してそこにバリアメタルTiNを形成した後、例えはタングステン(W)からなるコンタクトプラグ410を形成する。また、それと平行して、半導体集積回路2でも、エッチングストッパ膜710を成膜し、さらに層間絶縁膜711を成膜した後、コンタクトホールを開口してそこにバリアメタルTiNを形成した後、例えはタングステン(W)からなるコンタクトプラグ410を形成する。

このように、一つの半導体基板4内に発光素子3と半導体集積回路2とを、製造方法を煩雑化させる虞のある別個のプロセスで作るのではなくて、一つのプロセスで並行して製造することにより、高速動作可能な半導体集積回路2と出力効率の良好な発光素子3とを簡易なプロセスで製造することが可能となる。

なお、上記のような本発明の一実施の形態および各実施例では、ポーラスシリコン、SiGe、微結晶シリコンなどによって発光素子3や光電変換素子1を構成する場合について説明したが、発光素子3の発光部と光電変換素子1の光電変換部とを、互いに異なった材料で形成するようにしてもよいことは言うまでもない。

本発明の半導体集積回路装置は、例えば光通信システムにおいて、外部から送信されて来た光信号を、一旦、電気信号に変換して、半導体集積回路で信号処理または演算処理を行い、その処済みの電気信号を再び光信号に変換して外部へと出力する、といった機能を果たす半導体集積回路装置として好適に利用可能である。そしてまた、本発明の半導体集積回路装置の製造方法は、そのような半導体集積回路装置を一つの半導体基板内に簡易に作り込むことが可能な製造方法として利用される。

1…光電変換素子、2…半導体集積回路、3…発光素子、4…半導体基板、300…素子部、301…ポーラスシリコン層、400…配線部、702…SiGe層、802…微結晶シリコン層、900…光窓

Claims (16)

- 入力される光信号を電気信号に変換する光電変換素子と、前記光電変換素子から出力される電気信号に対して信号処理または演算処理を施す半導体集積回路と、前記半導体集積回路で処理された電気信号を受けて、当該電気信号を光信号に変換して出力する発光素子とが、一つの半導体基板に作り込まれた

ことを特徴とする半導体集積回路装置。 - 前記半導体基板が、シリコン系材料からなるものである

ことを特徴とする請求項1記載の半導体集積回路装置。 - 前記発光素子は、発光部位がポーラスシリコンからなるものである

ことを特徴とする請求項2記載の半導体集積回路装置。 - 前記発光素子の発光部位の上には、前記光信号の出力を遮る材質の構造物を除去することにより光出力窓が設けられている

ことを特徴とする請求項1記載の半導体集積回路装置。 - 前記ポーラスシリコンからなる発光素子は、ポーラス度の異なるポーラスシリコン多層膜を、反射層として前記発光部位のポーラスシリコンの下に備えている

ことを特徴とする請求項3記載の半導体集積回路装置。 - 前記シリコン系材料として、SiGeを用いた

ことを特徴とする請求項2記載の半導体集積回路装置。 - 前記シリコン系材料が、エルビウムまたはそれと置換可能な希土類元素をドープしてなるものである

ことを特徴とする請求項6記載の半導体集積回路装置。 - 前記光電変換素子が、少なくとも光電変換部位にSiGeを用いてなるものである

ことを特徴とする請求項2記載の半導体集積回路装置。 - 前記発光素子が、少なくとも発光部位に微結晶シリコンを用いてなるものである

ことを特徴とする請求項1記載の半導体集積回路装置。 - 前記半導体基板には配線層が作り込まれており、

前記発光素子は、前記配線層が作り込まれた深さよりも前記半導体基板の表面に近い深さに形成されている

ことを特徴とする請求項1記載の半導体集積回路装置。 - 前記光出力窓の側壁が、金属膜で覆われている

ことを特徴とする請求項4記載の半導体集積回路装置。 - 発光素子または受光素子のうち少なくともいずれか一種類の上に、レンズが形成されている

ことを特徴とする請求項1記載の半導体集積回路装置。 - 前記半導体集積回路が、前記光電変換素子から出力される電気信号に対して信号処理または演算処理を施す機能を有する回路を含んだ論理回路であり、

前記一つの半導体基板が、前記半導体集積回路および前記光電変換素子ならびに前記発光素子を作り込まれた一つの半導体チップである

ことを特徴とする請求項1記載の半導体集積回路装置。 - 入力される光信号を電気信号に変換する光電変換素子と、前記光電変換素子から出力される電気信号に対して信号処理または演算処理を施す半導体集積回路と、前記半導体集積回路で処理された電気信号を受けて当該電気信号を光信号に変換して出力する発光素子とを、一つの半導体基板に作り込む

ことを特徴とする半導体集積回路装置の製造方法。 - シリコンをスパッタまたはCVD法で成膜した後、フォトリソグラフィ法によりナノレベルの微結晶を一括形成することで、前記発光素子の発光部位を微結晶シリコンで構成する

ことを特徴とする請求項14記載の半導体集積回路装置の製造方法。 - 前記微結晶シリコンを形成した後、水素ガスまたは水素プラズマによりシリコンダングリングボンドを終端する

ことを特徴とする請求項15記載の半導体集積回路装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003347449A JP2005116709A (ja) | 2003-10-06 | 2003-10-06 | 半導体集積回路装置およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003347449A JP2005116709A (ja) | 2003-10-06 | 2003-10-06 | 半導体集積回路装置およびその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005116709A true JP2005116709A (ja) | 2005-04-28 |

Family

ID=34540019

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003347449A Pending JP2005116709A (ja) | 2003-10-06 | 2003-10-06 | 半導体集積回路装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005116709A (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006332490A (ja) * | 2005-05-30 | 2006-12-07 | Sony Corp | 発光素子及び発光装置 |

| JP2011077072A (ja) * | 2009-09-29 | 2011-04-14 | Panasonic Corp | 固体撮像素子及びその製造方法 |

| WO2014125945A1 (ja) * | 2013-02-13 | 2014-08-21 | ソニー株式会社 | 受発光装置 |

| CN105006468A (zh) * | 2015-06-29 | 2015-10-28 | 上海集成电路研发中心有限公司 | 一种多层硅片封装结构中的信息传输装置 |

| JP6391890B1 (ja) * | 2017-11-27 | 2018-09-19 | 三菱電機株式会社 | 光半導体装置 |

| JP2020109799A (ja) * | 2019-01-07 | 2020-07-16 | 富士通株式会社 | 電子装置、電子装置の製造方法及び電子機器 |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05175592A (ja) * | 1991-06-06 | 1993-07-13 | American Teleph & Telegr Co <Att> | 光増幅装置 |

| JPH05327017A (ja) * | 1992-05-22 | 1993-12-10 | Toshiba Corp | 半導体発光素子 |

| JPH06268254A (ja) * | 1993-03-15 | 1994-09-22 | Toshiba Corp | 半導体装置 |

| JPH07237995A (ja) * | 1994-02-28 | 1995-09-12 | Rikagaku Kenkyusho | 超微結晶シリコン発光材料、その製造方法、超微結晶シリコン発光材料を用いた素子およびその製造方法 |

| JPH07247199A (ja) * | 1994-03-09 | 1995-09-26 | Rikagaku Kenkyusho | 可視発光するシリコンの製造方法およびそれを用いた素子の製造方法 |

| JPH08148280A (ja) * | 1994-04-14 | 1996-06-07 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2000298218A (ja) * | 1999-04-13 | 2000-10-24 | Hitachi Ltd | 光インターコネクト装置およびその製造方法 |

| JP2003273397A (ja) * | 2002-03-19 | 2003-09-26 | Fuji Xerox Co Ltd | 半導体発光素子、半導体複合素子、及び半導体発光素子の製造方法 |

| JP2003273394A (ja) * | 2002-03-13 | 2003-09-26 | Matsushita Electric Ind Co Ltd | 発光表示素子及びその製造方法 |

-

2003

- 2003-10-06 JP JP2003347449A patent/JP2005116709A/ja active Pending

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05175592A (ja) * | 1991-06-06 | 1993-07-13 | American Teleph & Telegr Co <Att> | 光増幅装置 |

| JPH05327017A (ja) * | 1992-05-22 | 1993-12-10 | Toshiba Corp | 半導体発光素子 |

| JPH06268254A (ja) * | 1993-03-15 | 1994-09-22 | Toshiba Corp | 半導体装置 |

| JPH07237995A (ja) * | 1994-02-28 | 1995-09-12 | Rikagaku Kenkyusho | 超微結晶シリコン発光材料、その製造方法、超微結晶シリコン発光材料を用いた素子およびその製造方法 |

| JPH07247199A (ja) * | 1994-03-09 | 1995-09-26 | Rikagaku Kenkyusho | 可視発光するシリコンの製造方法およびそれを用いた素子の製造方法 |

| JPH08148280A (ja) * | 1994-04-14 | 1996-06-07 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2000298218A (ja) * | 1999-04-13 | 2000-10-24 | Hitachi Ltd | 光インターコネクト装置およびその製造方法 |

| JP2003273394A (ja) * | 2002-03-13 | 2003-09-26 | Matsushita Electric Ind Co Ltd | 発光表示素子及びその製造方法 |

| JP2003273397A (ja) * | 2002-03-19 | 2003-09-26 | Fuji Xerox Co Ltd | 半導体発光素子、半導体複合素子、及び半導体発光素子の製造方法 |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006332490A (ja) * | 2005-05-30 | 2006-12-07 | Sony Corp | 発光素子及び発光装置 |

| JP2011077072A (ja) * | 2009-09-29 | 2011-04-14 | Panasonic Corp | 固体撮像素子及びその製造方法 |

| WO2014125945A1 (ja) * | 2013-02-13 | 2014-08-21 | ソニー株式会社 | 受発光装置 |

| US10284758B2 (en) | 2013-02-13 | 2019-05-07 | Sony Semiconductor Solutions Corporation | Light receiving and emitting device |

| CN105006468A (zh) * | 2015-06-29 | 2015-10-28 | 上海集成电路研发中心有限公司 | 一种多层硅片封装结构中的信息传输装置 |

| JP6391890B1 (ja) * | 2017-11-27 | 2018-09-19 | 三菱電機株式会社 | 光半導体装置 |

| WO2019102605A1 (ja) * | 2017-11-27 | 2019-05-31 | 三菱電機株式会社 | 光半導体装置 |

| CN111418074A (zh) * | 2017-11-27 | 2020-07-14 | 三菱电机株式会社 | 光半导体装置 |

| US11081602B2 (en) | 2017-11-27 | 2021-08-03 | Mitsubishi Electric Corporation | Optical semiconductor device |

| JP2020109799A (ja) * | 2019-01-07 | 2020-07-16 | 富士通株式会社 | 電子装置、電子装置の製造方法及び電子機器 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10158036B2 (en) | Semiconductor device and its manufacturing method | |

| KR101448284B1 (ko) | 후면 조명된 이미지 센서들 | |

| KR20190054881A (ko) | 흡수 강화 반도체 층을 가진 이미지 센서 | |

| JP5917978B2 (ja) | 半導体装置及びその製造方法 | |

| TW201344893A (zh) | 半導體裝置及其製造方法 | |

| US20100032659A1 (en) | Semiconductor device and method of fabricating the same | |

| JP5523477B2 (ja) | シリコンベースの光電気回路 | |

| JP2003264311A (ja) | ホトダイオードを有する集積回路の製造方法 | |

| KR20150139787A (ko) | 반도체 장치의 제조 방법 | |

| TW202135171A (zh) | 用於光電元件信噪比的增強的結構和材料工程方法 | |

| US7101725B2 (en) | Solution to thermal budget | |

| TWI817161B (zh) | 影像感測器、半導體裝置及其製造方法 | |

| JP2003264243A (ja) | 2つのタイプのホトダイオードを包含する集積回路装置 | |

| US20190280023A1 (en) | Imaging device, method of manufacturing the same, and apparatus | |

| JP4517144B2 (ja) | Mos電界効果トランジスタ型量子ドット発光素子の製造方法 | |

| WO2022004160A1 (ja) | 半導体装置及び撮像装置 | |

| JP2005116709A (ja) | 半導体集積回路装置およびその製造方法 | |

| JP4315020B2 (ja) | 半導体集積回路装置およびその製造方法 | |

| JP2023097349A (ja) | デバイスおよび半導体デバイスを製造するための方法(密度スケーリングのための背面電源レールおよび配電網) | |

| TW202229937A (zh) | 半導體影像感測器 | |

| JP2003031790A (ja) | 半導体装置およびその製造方法 | |

| CN107425027B (zh) | 半导体装置以及半导体装置的制造方法 | |

| JP2019046867A (ja) | 半導体装置及び半導体装置の製造方法 | |

| US20230402477A1 (en) | Image sensor | |

| US20070262380A1 (en) | Semiconductor device and method for manufacturing semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060809 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090317 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091202 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100325 |