JP2004508717A - 薄いゲート酸化物MOSFETsでのゲート誘起ドレイン漏洩(GIDL)電流を減らす方法およびデバイス - Google Patents

薄いゲート酸化物MOSFETsでのゲート誘起ドレイン漏洩(GIDL)電流を減らす方法およびデバイス Download PDFInfo

- Publication number

- JP2004508717A JP2004508717A JP2002524227A JP2002524227A JP2004508717A JP 2004508717 A JP2004508717 A JP 2004508717A JP 2002524227 A JP2002524227 A JP 2002524227A JP 2002524227 A JP2002524227 A JP 2002524227A JP 2004508717 A JP2004508717 A JP 2004508717A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- gate

- region

- semiconductor layer

- oxide layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims abstract description 89

- 239000004065 semiconductor Substances 0.000 claims abstract description 52

- 238000004519 manufacturing process Methods 0.000 claims abstract description 17

- 239000007943 implant Substances 0.000 claims abstract description 9

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 34

- 229920005591 polysilicon Polymers 0.000 claims description 34

- 238000005468 ion implantation Methods 0.000 claims description 29

- 150000002500 ions Chemical class 0.000 claims description 28

- 239000002019 doping agent Substances 0.000 claims description 18

- 229910052731 fluorine Inorganic materials 0.000 claims description 14

- 239000011737 fluorine Substances 0.000 claims description 14

- 230000005684 electric field Effects 0.000 claims description 10

- 125000006850 spacer group Chemical group 0.000 claims description 9

- 230000000295 complement effect Effects 0.000 claims description 8

- 230000005669 field effect Effects 0.000 claims description 8

- 229910052751 metal Inorganic materials 0.000 claims description 7

- 239000002184 metal Substances 0.000 claims description 7

- 238000000137 annealing Methods 0.000 claims description 6

- -1 boron difluoride ions Chemical class 0.000 claims description 6

- 229910052801 chlorine Inorganic materials 0.000 claims description 6

- 239000000460 chlorine Substances 0.000 claims description 6

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 claims description 5

- 229910052721 tungsten Inorganic materials 0.000 claims description 5

- 239000010937 tungsten Substances 0.000 claims description 5

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 4

- 229910001092 metal group alloy Inorganic materials 0.000 claims description 4

- 150000002739 metals Chemical class 0.000 claims description 4

- 238000000059 patterning Methods 0.000 claims description 4

- 229910021332 silicide Inorganic materials 0.000 claims description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 claims description 3

- 229910052785 arsenic Inorganic materials 0.000 claims description 3

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 claims description 3

- 238000004518 low pressure chemical vapour deposition Methods 0.000 claims description 3

- 229910052698 phosphorus Inorganic materials 0.000 claims description 3

- 239000011574 phosphorus Substances 0.000 claims description 3

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 claims 9

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims 2

- 238000001802 infusion Methods 0.000 claims 2

- 239000010936 titanium Substances 0.000 claims 2

- 229910052719 titanium Inorganic materials 0.000 claims 2

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims 1

- 239000000758 substrate Substances 0.000 abstract description 36

- 238000002955 isolation Methods 0.000 abstract description 8

- 238000010586 diagram Methods 0.000 abstract description 5

- 239000000463 material Substances 0.000 description 13

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 238000007254 oxidation reaction Methods 0.000 description 5

- 230000008569 process Effects 0.000 description 5

- 238000012545 processing Methods 0.000 description 5

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical group [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 4

- 239000000969 carrier Substances 0.000 description 4

- 238000007796 conventional method Methods 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 4

- 238000002513 implantation Methods 0.000 description 4

- 230000003647 oxidation Effects 0.000 description 4

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 3

- 230000004888 barrier function Effects 0.000 description 3

- 238000005452 bending Methods 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 239000012535 impurity Substances 0.000 description 3

- 238000001259 photo etching Methods 0.000 description 3

- 238000005240 physical vapour deposition Methods 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-M Fluoride anion Chemical compound [F-] KRHYYFGTRYWZRS-UHFFFAOYSA-M 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 229920002120 photoresistant polymer Polymers 0.000 description 2

- 230000003244 pro-oxidative effect Effects 0.000 description 2

- 238000010405 reoxidation reaction Methods 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 208000022010 Lhermitte-Duclos disease Diseases 0.000 description 1

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- OKZIUSOJQLYFSE-UHFFFAOYSA-N difluoroboron Chemical compound F[B]F OKZIUSOJQLYFSE-UHFFFAOYSA-N 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000011065 in-situ storage Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000005289 physical deposition Methods 0.000 description 1

- 230000036417 physical growth Effects 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 239000010421 standard material Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 238000002207 thermal evaporation Methods 0.000 description 1

- 150000003657 tungsten Chemical class 0.000 description 1

- 230000005641 tunneling Effects 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

- H01L21/26513—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors of electrically active species

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26586—Bombardment with radiation with high-energy radiation producing ion implantation characterised by the angle between the ion beam and the crystal planes or the main crystal surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28158—Making the insulator

- H01L21/28167—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation

- H01L21/28176—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation with a treatment, e.g. annealing, after the formation of the definitive gate conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28158—Making the insulator

- H01L21/28167—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation

- H01L21/28185—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation with a treatment, e.g. annealing, after the formation of the gate insulator and before the formation of the definitive gate conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28158—Making the insulator

- H01L21/28167—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation

- H01L21/28194—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation by deposition, e.g. evaporation, ALD, CVD, sputtering, laser deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/511—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures

- H01L29/512—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures the variation being parallel to the channel plane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/518—Insulating materials associated therewith the insulating material containing nitrogen, e.g. nitride, oxynitride, nitrogen-doped material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66659—Lateral single gate silicon transistors with asymmetry in the channel direction, e.g. lateral high-voltage MISFETs with drain offset region, extended drain MISFETs

Abstract

低減されたGIDL電流を有するFETを提供する集積回路の作製方法が記載される。半導体基板が用意され、そこには、活性領域が隔離領域によって分離され、ゲート酸化物層が活性領域上に形成される。ゲート電極は、活性領域におけるゲート酸化物層上に形成される。傾斜した高ドーズのイオン注入が行われて、ゲート−ドレインオーバーラップ領域における各ゲート電極のエッジの下のゲート酸化物層を選択的にドープし、集積回路の作製が完了する。

【選択図】

【選択図】

Description

【0001】

本発明は、集積回路デバイスの作製に関し、さらに特定すれば、集積回路の作製中に、そのゲート/ドレイン・オーバーラップ領域中だけで、電気的ゲート酸化物厚さ(electrical gate oxide thickness)を選択的に増加させることによりゲート誘起ドレイン漏洩(GIDL)電流を減らす方法に関する。

【0002】

集積回路の作製において、現状先端技術の金属酸化物半導体電界効果トランジスタ[MOSFETs(Metal Oxide Semiconductor Field Effect Transistors]などの半導体デバイスのサイズが小型化しているので、これらデバイスの電流駆動性能(current driving capability)に関連する実用性能上の問題が存在する。この電流駆動性能は、ソース抵抗(source resistance)とゲート酸化物の厚さの両方の関数であるから、これらデバイスでのより良好な実用性能は、ゲート酸化物とスペーサ層の厚さをより薄くすることにより達成される。しかしゲート酸化物をより薄くすると、ゲート誘起ドレイン漏洩(GIDL)電流が、閾値以下の総漏洩電流の大きいパーセントを占めるようになって、このGIDL電流が、これらデバイスの実用性能を損なうことが観測されている。このGIDL電流は、ゲート/ドレイン・オーバーラップ領域での過剰なバンド・ベンディング(band bending)の結果、価電子帯(valence band)から伝導帯(conduction band)にトンネル効果で抜けてきた電子に起因する。これら半導体デバイスの小型化につれて、その閾値以下の領域に亘って適切なゲート制御を提供するためには、そのゲート酸化物の層の厚さが減り続けなければならない。またパンチ・スルー特性を改善するために、そしてドライブ(drives)を増大するために、そのチャネルおよびソース/ドレイン領域のドーピング密度も増加しなければならない。不都合なことに、そのチャネルおよびソース/ドレイン領域のドーピング密度が増加すると、その表面電場も強くなり、その結果、バンド・ベンディングが大きくなり、従ってGIDL電流も増える。かくして、高い電流駆動性能と少ないGIDL電流との間で適切なバランスを有する小型半導体デバイスを提供するには困難が存在する。

【0003】

GIDL電流を減らす一つの方法は、ゲート−ソースおよびゲート−ドレイン・オーバーラップ領域だけで、厚いゲート酸化物を提供するための対称的酸化を含んでいる。このゲート−ドレイン領域での厚いゲート酸化物は、GIDL電流を減らす。しかし、このゲート−ソース領域に厚いゲート酸化物があると、ソース抵抗が増加し、そのため、そのデバイスの電流駆動性能が低下する。

【0004】

もう一つの方法が、米国特許第5,684,317号明細書[発明者:Hwang]に開示されており、その発明者は、ソース抵抗を増加させないで、GIDL電流を減らすために、ゲート−ドレイン領域だけに厚い酸化物層を形成させることを教示している。このゲート−ドレイン領域での酸化物層の材料の厚さは、その領域においてより厚いゲート酸化物層を物理的に成長させるために塩素またはフッ素のような酸化促進物質をその領域に注入することにより増大される。この酸化促進物質が存在することにより、そのゲート−ドレイン領域の酸化物層は、その基材上の残りの部分より速く成長する。しかし、ゲート−ドレイン領域の酸化物層の材料の厚みが増大すると、そのトランジスタの電流駆動が阻害され、そしてまた、体積膨張により、そのオーバーラップ領域近くの活性領域での応力増大の原因にもなる。

【0005】

従って、改善された電気的実用性能を有し、従来技術の欠点を克服できる薄いゲート酸化物を有する寸法の小さい半導体デバイスに対する需要が存在する。この半導体デバイスとその作製法は、コスト効率が良くそして大量生産が可能でなければならず、現存のプロセス・フローに容易に適合されねばならず、そして、そのプロセス・フローのサイクルタイムを有意に長くしてはならない。

【0006】

本発明は、普通に知られている方法で作られるゲート酸化物層の厚さが同程度の電界効果トランジスタ(FET)デバイスより、ゲート誘起ドレイン漏洩(GIDLs)がより少ないFETデバイスを製造する方法を提供する。以下に説明される本発明の方法は、N−チャネル、P−チャネルおよびCMOS FETデバイス全ての製作に用いられてもよい。

【0007】

本発明の方法は、非−直交イオン注入法を用い、それによってFETデバイスのゲート−ドレイン・オーバーラップ領域中のゲート酸化物層が選択的にフッ素または塩素イオンでドープされる。そのイオン注入の処方量は、そのイオン濃度が、そのゲート−ソース/ドレイン・コーナー近くの“電気的”ゲート酸化物厚さを増加し、その際、そのイオンドープされたゲート酸化物層の実際の厚さは厚くならないで、そのゲート−ドレイン・オーバーラップ領域中のゲート酸化物層の誘電率が低下するような量である。GIDLは表面電場の大きさに指数関数的に依存するから、その電場が僅かに小さくなっても、GIDLは劇的に減少する。従って、現存のFET製作工程に本発明の方法を追加すれば、そのオーバーラップ領域中の有効表面電場が低下し、それにより、本発明が実施されたFETデバイスでのGIDLは最小化される。

【0008】

本発明の方法は、ゲート酸化物層が“薄い”ことに因りGIDLが増大し易い任意のFETデバイスで用いられてもよい。本発明の方法は、動的ランダム・アクセス・メモリー(DRAM)集積回路、静的ランダム・アクセス・メモリー(SRAM)集積回路、消去可能なプログラム可能読取り専用メモリー(EPROM)、およびアプリケーション専用集積回路(ASICs)を含む集積回路内のN−MOSFETデバイスで実施されてもよいが、これらに限定はされない。また本発明の方法は、広範囲の適用性を有しており、そして、この方法は、これらデバイスの製作に適用可能であるから、集積回路内のP−MOSFETおよびCMOSデバイスでも実施され得る。

【0009】

本発明の一つの態様に従って、半導体層、その半導体層上に形成された酸化物層、その酸化物層上に形成されたポリシリコン層、そのポリシリコン層から形成されるゲート構造を含む回路構造であって、そのゲート構造は、規定されたリーディング・エッジを有しており、そしてそのゲート構造の下で、そのリーディング・エッジに隣接するオーバーラップ領域は、そのオーバーラップ領域中での電気的ゲート酸化物厚さを増加させるのに十分である所定のイオン注入濃度を有している、回路構造が提供される。

【0010】

本発明のもう一つの態様に従って、半導体層上に酸化物層を形成させる工程;その酸化物層上にポリシリコン層を形成させる工程;そのポリシリコン層を、規定されたリーディング・エッジを有するゲート構造にパターン化し、そしてその酸化物層を露出させる工程;および、ゲート構造の下で、規定されたリーディング・エッジに隣接するオーバーラップ領域で、その酸化物層の厚さを増加させずに、オーバーラップ領域中だけで、その電気的ゲート酸化物厚さを増加させるのに十分な所定のイオン注入濃度までその酸化物層にイオンを注入する工程であって、そのイオンは半導体層の面に直交しない傾斜角度で注入される工程;を含む半導体層上に構造を作製するための方法が提供される。

【0011】

本発明のさらにもう一つの態様に従って、半導体基板上に、ゲート酸化物層、そのゲート酸化物層上のゲート電極およびその半導体基板内に形成された二つのソース/ドレイン領域を含む電界効果トランジスタ構造を形成させる工程;その半導体基板をアニーリングする工程;オーバーラップ領域を規定する、ゲート電極の下でドレイン領域に隣接しているゲート酸化物層に、そのオーバーラップ領域中だけで電気的ゲート酸化物厚さを増加させるのに十分な所定のイオン注入濃度までイオンを注入する工程であって、そのイオンは半導体基板の面に直交しない傾斜角度で注入される工程;およびその半導体基板の作製を完成する工程;を含む、電界効果トランジスタ(FETs)内のゲート誘起ドレイン漏洩(GIDL)電流を減らす方法が提供される。

【0012】

本発明の一つの目的は、集積回路の作製中に、そのゲート/ドレイン・オーバーラップ領域だけで、その電気的ゲート酸化物厚さを選択的に増加させることによりゲート誘起ドレイン漏洩電流を減らす方法を提供することである。

【0013】

本発明のもう一つの目的は、ゲート誘起ドレイン漏洩を減少させる結果になる集積回路を作製するための、量産可能な方法を提供することである。

他の目的、特徴および利点が、以下の考察の過程において、より十分に明らかにされるであろう。

【0014】

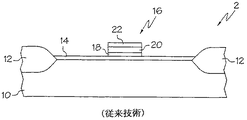

図1は、従来技術の常法により半導体基板上に形成された一部完成FET回路デバイスの横断面を例示した概略図であり;

図2A〜2Cは、本発明の一つの態様に従うゲート構造を作製する加工工程を例示しており;そして、

図3A〜3Dは、本発明の方法に従ってFETデバイスの作製を完成する逐次段階を例示する一連の横断面を例示した概略図である。

【0015】

同じ参照番号は、各態様図を通して同じ部分に対応する。

図1は、任意の既知の常用法により作製できる一部完成FETデバイス2の一部分を例示したものである。一例として、そして一般的に言って、このFETデバイス2は既知の局部シリコン酸化(LOCOS)法によって製造される:この方法では、半導体層または基板10の一部が、リソグラフ・マスクを通して、酸化され、電場分離領域(field isolation regions)12が形成される。電場分離領域12は、活性デバイス領域を規定し、そして基板10の表面内および表面上の同じマスクにより形成される隣接デバイスの間の横分離(lateral isolation)をも提供する。分かり易くするために、デバイス間の電場分離領域12は一部だけが示されている。さらにこのリソグラフ・マスクは常用のリソグラフ法とエッチング法により作製される。基板10は、様々なドーパント濃度、どちらか一方のドーパント極性そして様々な結晶学的配向を有する活性で操作可能な部分を含んでいる一つまたはそれ以上の半導体層または構造であってもよいが、望ましくは本発明は、100−結晶学的配向を有するシリコン構造上で実施されることに留意すべきである。さらに、本発明は、N−およびP−表面チャネル・デバイスの両方に、同等に上手く適用できるから、簡単のために、本発明者達は、N−MOSFETデバイスの場合だけを提示する。この方法はP−MOSFETの場合に類似している。従って、この基板10がP−ドープされているのは、その基板10の一次キャリアーが“正”孔であることを意味する。P−MOSFETデバイスでは、その第1導電率タイプは、そのn−ドープされた基板が一次キャリアーとして電子を有するので、“負”である。

【0016】

分離領域12が形成された後、この技術分野で常用されているような熱的酸化により、基板10のクリーンな活性デバイス領域の上に、誘電性層またはゲート酸化物層14が形成される。次いで、そのゲート酸化物層14の上に、その場で(in−situ)ドープされたポリシリコン層18を含むゲート電極16が、低圧化学気相堆積法(LPCVD)、プラズマ・エンハンスド化学気相堆積法(PECVD)または物理的気相堆積法(PVD)のような既知の方法により堆積される。このポリシリコン層18は、この技術分野での常用法でエッチングされ、基板10の活性領域内のゲート電極16に望ましいパターンが提供される。このゲート酸化物層14の厚さは約20〜約80オングストロームであるのが望ましいが、ゲート酸化物の厚さ(tox)はそのテクノロジー・ノード(technology node)に依存するから、本発明の方法は、より薄いゲート酸化物層が要求される任意のテクノロジー・ノードで有用であると信じられる。さらに、そしてまたテクノロジー・ノードに依存する場合でも、本発明の望ましい態様では、そのポリシリコン層18と、その高ドープされた(highly doped)ポリシリコン層からパターン化されたゲート電極16の総厚さは、約200〜約1000オングストロームであるのが望ましい。

【0017】

本発明の実施にとって必須ではないが、一般に、ゲート電極16のポリシリコン層18の上に追加の材料の層を形成させるために、さらなる材料が堆積されてもよい。これら層用の標準的材料に含まれるのは、このデバイスの電気的特性を改善する目的で用いられる、金属類、金属合金類、高ドープされたポリシリコン、ケイ化物類およびポリサイド類(ポリシリコン/金属ケイ化物−スタック)である。推奨される一つの態様では、窒化チタニウム(TiN)の比較的薄い層が、バリアー層20を形成するためにポリシリコン層18の上に堆積される。次いで、このバリアー層20はタングステン(W)層22で覆われて、ゲート電極16の形成が完了する。

【0018】

本発明の一つの態様に従う、ゲート構造を作製するプロセス工程を一般的に例示している図2A〜2Cに見られるように、ゲート酸化物層14は、望ましくはシリコン基板である半導体基板10上に熱酸化により成長させられる。酸化物層14の上にポリシリコン層が堆積され、そして光エッチング法を用いてパターン化されて、ゲート構造15が形成される。ゲート酸化物層14に接しているゲート構造15の表面はリーディング・エッジ17を有している。次いで、図2Bに示したように、その基板10の表面を覆ってフォトレジスト層23を取付け、そしてパターン化して酸化物層14とゲート構造15の両方の一部を露出させる。この酸化物層14のオーバーラップ領域26を、選択的にイオンでドープするために、常用の装置を用いて、傾斜角度をつけて、高注入量、低エネルギーで注入することで、イオンインプラント24が行われる。

【0019】

図2Cに示したように、オーバーラップ領域26は、ゲート構造15の下で、そのリーディング・エッジ17に隣接している。このイオンインプラント24は、望ましくはフッ素であり、そして代替として、塩素または酸化物層14の誘電率を低下させる任意の他のイオンでもよい。推奨される態様で、このフッ素イオンは:(1)その基板10の面に直交する軸から約5から約15度の傾斜角で、(2)平方センチメートル当たり約1E13から約1E14原子のイオン注入量で、そして(3)約10KeVから約20KeVのイオン注入エネルギーで、注入される。イオン注入に推奨される角度範囲は約5から約15度であるが、イオン注入角は、ゲート構造15のスタックの高さに依存することに留意すべきである。フッ素イオンインプラント24の注入は、オーバーラップ領域26で、ゲート構造15の下で、推奨されるイオン濃度:約1E18原子/cm3に達するように調整することが重要である。この推奨される濃度まで、オーバーラップ領域26を選択的にドーピングすると、そのオーバーラップ領域の近くのゲート酸化物層14の誘電率が変化する(低下する)。

【0020】

フォトレジスト層23を除去した図2Cに示したように、この推奨されるイオン濃度までドーピングすると、従来技術の方法におけるように、その酸化物層14のtoxが物理的に成長または増加することなく、オーバーラップ領域26における“電気的ゲート酸化物”厚さは増加する。そこで、本発明により形成されたこのゲート構造で、その半導体基板10の作製がさらに継続され、回路デバイスが完成されてもよい。

【0021】

本発明の方法により形成され得るこのようなデバイスの一つは、電界効果トランジスタである。このFETデバイスの製造が、一連の横断面図でその逐次段階を模式的に例示した図3A〜3Dにより示されている。最初の図3Aは、図1を参照して考察された従来技術の方法(しかし必須ではない)に従って作製された一部完成のFETデバイス2である。図2A〜2Cを参照して上に説明したように、オーバーラップ領域26でのイオン注入(イオンインプラント24)を行う前に、基板10で短い再酸化が行われる。半導体基板10の再酸化またはアニーリングのために、数種の方法が用いられてもよく、これら方法には、熱的方法、迅速熱処理(Rapid Thermal Processing:RTP)法およびレーザー支援処理法が含まれるが、これらに限定はされない。本発明の推奨される態様で、基板10は、熱的方法で、約800〜約900℃の温度で約10〜約15分間アニーリングされる。

【0022】

上の短い再酸化期間の後、ゲート酸化物層14のオーバーラップ領域26とゲート電極16のポリシリコン層18に、イオンで選択的にドープするためのイオン注入工程(イオンインプラント24)が、常用の装置で行われる。前述のように、このイオンインプラント24は、望ましくはフッ素であり、そして代替として、塩素またはゲート酸化物層14の誘電率を低下させる任意の他のイオンでもよい。さらに、重要なことは、標準的なFETデバイス2にとって、フッ素イオンインプラント24の望ましい注入工程は、ドレイン領域30bに隣接するゲート電極16の下のゲート−ポリ/ゲート酸化物界面で、約1E18原子/cm3のイオン濃度に達するように調整されることである。ゲート−ドレイン・オーバーラップ領域26を、この推奨されるイオン濃度まで選択的にドーピングすると、オーバーラップ領域26近くのゲート酸化物14の誘電率が変化し(低下し)、かくして、オーバーラップ領域26における“電気的ゲート酸化物”厚さは増すが、従来技術の方法におけるように、物理的に成長してより厚いゲート酸化物層24になることはない。

【0023】

図3B〜3Dに例示されているように、FETデバイス2を完成するために、上述の図3Aのイオン注入工程の後に、任意の常用の方法で、残りの製作工程が継続される。図3Bで示したように、FETデバイス2の上に、さらに、ゲート電極16の両側に隣接し、そしてその電場分離領域12にまで延びているソース領域28aおよびドレイン領域28bから成る不純物拡散領域が形成される。そのゲート電極16に隣接するソース/ドレイン領域28aおよび領域28bのエッジが、基板10の表面でチャネル領域29を規定する。ソース/ドレイン領域28aおよび領域28bは、普通、低ドープされたドレイン(lightly doped drain:LDD)を、そして次いで高ドープされたドレイン(heavily doped drain:HDD)を形成させるために、不純物ドーパント材料による二段階注入法で作製される。ソース/ドレイン領域28aおよび領域28bの作製に用いられた不純物ドーパント材料が、そのソース/ドレイン領域で一次キャリアーとして電子を用いるn−タイプであると、その場合得られるMOSFETは、N−MOSFET(“n−チャネル”)トランジスタ・デバイスである。例えば、ひ素またはリンが、cm2当たり約2E15〜約5E15原子の量で、そして約5KeV〜約15KeVのエネルギーで、このn−チャネル・ドープされたドレイン28aおよび28bを生成させるために用いられてもよい。逆に、ソース/ドレインドーパント用材料が、そのソース/ドレイン領域で一次キャリヤーとしてホール(空孔)を用いるp−タイプであると、その場合得られるMOSFETは、P−MOSFET(“p−チャネル”)トランジスタ・デバイスである。例えば、ジフッ化ホウ素が、cm2当たり約2E15〜約5E15原子の量で、そして約10KeV〜約25KeVのエネルギーで、そのp−チャネル・ドープされたドレイン28aおよび28bを生成させるために用いられてもよい。FETデバイス2が、同じ基板10の上にn−チャネルおよびp−チャネル・トランジスタの組合せで形成されていると、その時得られるMOSFETは相補型FET(CMOS)であり、そして同じ基板10上の、複数のN−MOSFETと複数の相補型P−MOSFETから構成されてもよい。

【0024】

このソース/ドレイン領域28aおよび28bを作る場合、第1イオン注入はLDDソース/ドレイン領域30aおよび30bのより低くドープされた部分を形成させるために、その基板をマスクするためのゲート電極16および電界分離領域12を用いて行われる。一般に、本発明の実施に必須ではないが、図3Cに示されるように、そのゲート電極16の両側に、電極スペーサ32が準備される。この電極スペーサ32は、酸化ケイ素、窒化ケイ素およびオキシ窒化ケイ素(silicon oxynitrides)のような絶縁性材料を含む材料(これらに限定はされない)から作られてもよい。電極スペーサ32を作るためには、様々な方法が用いられる。このような方法に含まれるのは、反応性イオンエッチング(Reactive Ion Etch:RIE)、および上述の材料堆積法である。普通、電極スペーサ32は、テトラエトキシシラン(TEOS)オキシドのような酸化物フィルムを、約600〜約720℃で、約300〜約700オングストロームの厚さに堆積させることにより作られる。第2イオン注入は、HDDソース/ドレイン領域34aおよび34bを有するソース/ドレイン領域28aおよび28bを完成するために行われる。例示したFETデバイス2で、このソース/ドレイン領域20は、n−タイプまたはp−タイプ・ドーパントでドープされてもよく、あるいは、異なる拡散特性を達成するために、異なるn−タイプドーパントまたはp−タイプ・ドーパントの組合せが用いられることもある。さらに、本発明の傾斜イオン注入工程は、希望によってLDD、スペーサあるいはまたHDDのどれか一つの生成の前または後にこの工程を行っても外見上の利点または欠点が無いので、FETデバイス2の製作のこの段階でも行われ得ることに留意すべきである。

【0025】

基板10へのソース/ドレイン領域28aおよび28bの取付けに次いで基板10は、ソース/ドレイン領域24aおよび24bを再結晶化させるために、もう一度アニーリングされる。前と同様にソース/ドレイン領域28aおよび28bのアニーリングも、熱的方法、急速熱処理(RTP)法およびレーザー支援法で行われてもよい。本発明の推奨される態様では、この半導体基板は、再結晶化されたソース/ドレイン領域28aおよび28bを生成させるために、約800〜約1000℃の温度で約10〜約20秒の間、RTP−法でアニーリングされる。

【0026】

さて図3Dを参照すると、本発明の推奨される態様に従ってFETを作製する最終の一連の加工工程が、横断面模式図として例示されている。図3Dに、パターン化されたインターレベル誘電体層36a、36bおよび36cが示されている。パターン化されたインターレベル誘電体層36a、36bおよび36cは、基板10上に作られたブランケットインターレベル誘電性層を、この分野で知られているような光リソグラフ法および光エッチング法でパターン化することにより作製される。ブランケット・インターレベル誘電性層は、酸化ケイ素、窒化ケイ素およびオキシ窒化ケイ素を含む絶縁性材料から作られてもよいが、それら材料に限定はされない。これらの絶縁性層は、化学気相堆積(CVD)法、プラズマ・エンハンスド化学気相堆積(PECVD)法または物理的堆積(PVD)法を含む方法により半導体基板の上に形成されてもよいが、これら方法に限定はされない。

【0027】

本発明の推奨される態様では、このパターン化されたインターレベル誘電体層36a、36bおよび36cは、この分野で知られているような光リソグラフ法および光エッチング法を用い、ソース材料としてテトラエチル・オルトシリケート(TEOS)を使用する化学気相堆積(CVD)法によって基板10上に堆積された酸化ケイ素材料から形成されているブランケット・インターレベル誘電性層をパターン化することにより作製される。他の方法と材料により作られた絶縁層も用いられてもよいが、この推奨される方法および材料は、簡単で、そしてこの技術分野で良く知られている方法である。パターン化されたインターレベル誘電体層36aおよび36bと、パターン化されたインターレベル誘電体層36bおよび36cの間の開口部の底部は、ゲート酸化物層14を通してエッチングされ、ソース/ドレイン領域28aと28bの表面がそれぞれ露出される。このパターン化されたインターレベル誘電体層36aおよび36bと、パターン化されたインターレベル誘電体層36bおよび36cの間の開口部にそれぞれ形成されている導電性コンタクトスタッド(conductive contact studs)38aと38bは、それぞれ、そのソース/ドレイン領域28aと28bの露出された表面と接している。この導電性コンタクトスタッド38aと38bは、この技術分野で常用されている物で、熱気相堆積法(thermal evaporation method)、電子ビーム支援気相堆積法およびCVD法を含む方法(これら方法に限定はされない)により半導体基材上に堆積された金属類、金属合金類およびポリシリコンを含む導電性材料(これら材料に限定はされない)から作られてもよい。本発明の推奨される態様では、この導電性コンタクトスタッド38aおよび38bは、厚さ約200〜約1000オングストロームの薄い窒化チタニウム・バリヤー層から作られるのが望ましく、その上に、より厚い導電性タングステン層が形成される。このタングステン層は、インターレベル誘電体層36a、36bおよび36c内の開口部を完全に充填するのに十分な厚さである。

【0028】

このパターン化されたインターレベル誘電体層36a、36bおよび36c内に導電性コンタクトスタッド38aと38bを形成させると、集積回路内に本発明の推奨される態様のFETデバイス2が作製され、このFETデバイスは、類似設計の従来のFETデバイスよりGIDLが少ない。本発明の方法は、sub−vtおよびドライブ(drives)のような他のデバイス特性を犠牲にすることなしに、GIDL電流が低下するという、従来技術より優れた利点を有していることが評価されるべきである。従って、本発明の方法を適用することにより作られた新しい電気的フロー(electrical flow)は、スケーリング則(scaling rules)によって、ディープ・サブミクロン(deep submicron)の幾何学的形状物で、ゲート酸化物の厚さを薄くすることが可能である。従って、本発明の方法は、DRAM、SRAM、EPROM、ASICなどのような集積回路デバイスを作るための任意の二重(またはそれ以上の多重の)ポリシリコン法で利用することができる。

【0029】

本発明は、詳細に、そしてその推奨される実施態様を引用することにより説明されたが、添付された特許請求の範囲に詳細に記載された本発明の範囲から逸脱することなしに、修正法および変法が可能であることは明らかであろう。

【図面の簡単な説明】

【図1】図1は、従来技術の常法により半導体基板上に形成された一部完成FET回路デバイスの横断面を例示した概略図である。

【図2】図2A〜2Cは、本発明の一つの態様に従うゲート構造を作製する加工工程を例示している。

【図3】図3A〜3Dは、本発明の方法に従ってFETデバイスの作製を完成する逐次段階を例示する一連の横断面を例示した概略図である。

同じ参照番号は、各態様図を通して同じ部分に対応する。

本発明は、集積回路デバイスの作製に関し、さらに特定すれば、集積回路の作製中に、そのゲート/ドレイン・オーバーラップ領域中だけで、電気的ゲート酸化物厚さ(electrical gate oxide thickness)を選択的に増加させることによりゲート誘起ドレイン漏洩(GIDL)電流を減らす方法に関する。

【0002】

集積回路の作製において、現状先端技術の金属酸化物半導体電界効果トランジスタ[MOSFETs(Metal Oxide Semiconductor Field Effect Transistors]などの半導体デバイスのサイズが小型化しているので、これらデバイスの電流駆動性能(current driving capability)に関連する実用性能上の問題が存在する。この電流駆動性能は、ソース抵抗(source resistance)とゲート酸化物の厚さの両方の関数であるから、これらデバイスでのより良好な実用性能は、ゲート酸化物とスペーサ層の厚さをより薄くすることにより達成される。しかしゲート酸化物をより薄くすると、ゲート誘起ドレイン漏洩(GIDL)電流が、閾値以下の総漏洩電流の大きいパーセントを占めるようになって、このGIDL電流が、これらデバイスの実用性能を損なうことが観測されている。このGIDL電流は、ゲート/ドレイン・オーバーラップ領域での過剰なバンド・ベンディング(band bending)の結果、価電子帯(valence band)から伝導帯(conduction band)にトンネル効果で抜けてきた電子に起因する。これら半導体デバイスの小型化につれて、その閾値以下の領域に亘って適切なゲート制御を提供するためには、そのゲート酸化物の層の厚さが減り続けなければならない。またパンチ・スルー特性を改善するために、そしてドライブ(drives)を増大するために、そのチャネルおよびソース/ドレイン領域のドーピング密度も増加しなければならない。不都合なことに、そのチャネルおよびソース/ドレイン領域のドーピング密度が増加すると、その表面電場も強くなり、その結果、バンド・ベンディングが大きくなり、従ってGIDL電流も増える。かくして、高い電流駆動性能と少ないGIDL電流との間で適切なバランスを有する小型半導体デバイスを提供するには困難が存在する。

【0003】

GIDL電流を減らす一つの方法は、ゲート−ソースおよびゲート−ドレイン・オーバーラップ領域だけで、厚いゲート酸化物を提供するための対称的酸化を含んでいる。このゲート−ドレイン領域での厚いゲート酸化物は、GIDL電流を減らす。しかし、このゲート−ソース領域に厚いゲート酸化物があると、ソース抵抗が増加し、そのため、そのデバイスの電流駆動性能が低下する。

【0004】

もう一つの方法が、米国特許第5,684,317号明細書[発明者:Hwang]に開示されており、その発明者は、ソース抵抗を増加させないで、GIDL電流を減らすために、ゲート−ドレイン領域だけに厚い酸化物層を形成させることを教示している。このゲート−ドレイン領域での酸化物層の材料の厚さは、その領域においてより厚いゲート酸化物層を物理的に成長させるために塩素またはフッ素のような酸化促進物質をその領域に注入することにより増大される。この酸化促進物質が存在することにより、そのゲート−ドレイン領域の酸化物層は、その基材上の残りの部分より速く成長する。しかし、ゲート−ドレイン領域の酸化物層の材料の厚みが増大すると、そのトランジスタの電流駆動が阻害され、そしてまた、体積膨張により、そのオーバーラップ領域近くの活性領域での応力増大の原因にもなる。

【0005】

従って、改善された電気的実用性能を有し、従来技術の欠点を克服できる薄いゲート酸化物を有する寸法の小さい半導体デバイスに対する需要が存在する。この半導体デバイスとその作製法は、コスト効率が良くそして大量生産が可能でなければならず、現存のプロセス・フローに容易に適合されねばならず、そして、そのプロセス・フローのサイクルタイムを有意に長くしてはならない。

【0006】

本発明は、普通に知られている方法で作られるゲート酸化物層の厚さが同程度の電界効果トランジスタ(FET)デバイスより、ゲート誘起ドレイン漏洩(GIDLs)がより少ないFETデバイスを製造する方法を提供する。以下に説明される本発明の方法は、N−チャネル、P−チャネルおよびCMOS FETデバイス全ての製作に用いられてもよい。

【0007】

本発明の方法は、非−直交イオン注入法を用い、それによってFETデバイスのゲート−ドレイン・オーバーラップ領域中のゲート酸化物層が選択的にフッ素または塩素イオンでドープされる。そのイオン注入の処方量は、そのイオン濃度が、そのゲート−ソース/ドレイン・コーナー近くの“電気的”ゲート酸化物厚さを増加し、その際、そのイオンドープされたゲート酸化物層の実際の厚さは厚くならないで、そのゲート−ドレイン・オーバーラップ領域中のゲート酸化物層の誘電率が低下するような量である。GIDLは表面電場の大きさに指数関数的に依存するから、その電場が僅かに小さくなっても、GIDLは劇的に減少する。従って、現存のFET製作工程に本発明の方法を追加すれば、そのオーバーラップ領域中の有効表面電場が低下し、それにより、本発明が実施されたFETデバイスでのGIDLは最小化される。

【0008】

本発明の方法は、ゲート酸化物層が“薄い”ことに因りGIDLが増大し易い任意のFETデバイスで用いられてもよい。本発明の方法は、動的ランダム・アクセス・メモリー(DRAM)集積回路、静的ランダム・アクセス・メモリー(SRAM)集積回路、消去可能なプログラム可能読取り専用メモリー(EPROM)、およびアプリケーション専用集積回路(ASICs)を含む集積回路内のN−MOSFETデバイスで実施されてもよいが、これらに限定はされない。また本発明の方法は、広範囲の適用性を有しており、そして、この方法は、これらデバイスの製作に適用可能であるから、集積回路内のP−MOSFETおよびCMOSデバイスでも実施され得る。

【0009】

本発明の一つの態様に従って、半導体層、その半導体層上に形成された酸化物層、その酸化物層上に形成されたポリシリコン層、そのポリシリコン層から形成されるゲート構造を含む回路構造であって、そのゲート構造は、規定されたリーディング・エッジを有しており、そしてそのゲート構造の下で、そのリーディング・エッジに隣接するオーバーラップ領域は、そのオーバーラップ領域中での電気的ゲート酸化物厚さを増加させるのに十分である所定のイオン注入濃度を有している、回路構造が提供される。

【0010】

本発明のもう一つの態様に従って、半導体層上に酸化物層を形成させる工程;その酸化物層上にポリシリコン層を形成させる工程;そのポリシリコン層を、規定されたリーディング・エッジを有するゲート構造にパターン化し、そしてその酸化物層を露出させる工程;および、ゲート構造の下で、規定されたリーディング・エッジに隣接するオーバーラップ領域で、その酸化物層の厚さを増加させずに、オーバーラップ領域中だけで、その電気的ゲート酸化物厚さを増加させるのに十分な所定のイオン注入濃度までその酸化物層にイオンを注入する工程であって、そのイオンは半導体層の面に直交しない傾斜角度で注入される工程;を含む半導体層上に構造を作製するための方法が提供される。

【0011】

本発明のさらにもう一つの態様に従って、半導体基板上に、ゲート酸化物層、そのゲート酸化物層上のゲート電極およびその半導体基板内に形成された二つのソース/ドレイン領域を含む電界効果トランジスタ構造を形成させる工程;その半導体基板をアニーリングする工程;オーバーラップ領域を規定する、ゲート電極の下でドレイン領域に隣接しているゲート酸化物層に、そのオーバーラップ領域中だけで電気的ゲート酸化物厚さを増加させるのに十分な所定のイオン注入濃度までイオンを注入する工程であって、そのイオンは半導体基板の面に直交しない傾斜角度で注入される工程;およびその半導体基板の作製を完成する工程;を含む、電界効果トランジスタ(FETs)内のゲート誘起ドレイン漏洩(GIDL)電流を減らす方法が提供される。

【0012】

本発明の一つの目的は、集積回路の作製中に、そのゲート/ドレイン・オーバーラップ領域だけで、その電気的ゲート酸化物厚さを選択的に増加させることによりゲート誘起ドレイン漏洩電流を減らす方法を提供することである。

【0013】

本発明のもう一つの目的は、ゲート誘起ドレイン漏洩を減少させる結果になる集積回路を作製するための、量産可能な方法を提供することである。

他の目的、特徴および利点が、以下の考察の過程において、より十分に明らかにされるであろう。

【0014】

図1は、従来技術の常法により半導体基板上に形成された一部完成FET回路デバイスの横断面を例示した概略図であり;

図2A〜2Cは、本発明の一つの態様に従うゲート構造を作製する加工工程を例示しており;そして、

図3A〜3Dは、本発明の方法に従ってFETデバイスの作製を完成する逐次段階を例示する一連の横断面を例示した概略図である。

【0015】

同じ参照番号は、各態様図を通して同じ部分に対応する。

図1は、任意の既知の常用法により作製できる一部完成FETデバイス2の一部分を例示したものである。一例として、そして一般的に言って、このFETデバイス2は既知の局部シリコン酸化(LOCOS)法によって製造される:この方法では、半導体層または基板10の一部が、リソグラフ・マスクを通して、酸化され、電場分離領域(field isolation regions)12が形成される。電場分離領域12は、活性デバイス領域を規定し、そして基板10の表面内および表面上の同じマスクにより形成される隣接デバイスの間の横分離(lateral isolation)をも提供する。分かり易くするために、デバイス間の電場分離領域12は一部だけが示されている。さらにこのリソグラフ・マスクは常用のリソグラフ法とエッチング法により作製される。基板10は、様々なドーパント濃度、どちらか一方のドーパント極性そして様々な結晶学的配向を有する活性で操作可能な部分を含んでいる一つまたはそれ以上の半導体層または構造であってもよいが、望ましくは本発明は、100−結晶学的配向を有するシリコン構造上で実施されることに留意すべきである。さらに、本発明は、N−およびP−表面チャネル・デバイスの両方に、同等に上手く適用できるから、簡単のために、本発明者達は、N−MOSFETデバイスの場合だけを提示する。この方法はP−MOSFETの場合に類似している。従って、この基板10がP−ドープされているのは、その基板10の一次キャリアーが“正”孔であることを意味する。P−MOSFETデバイスでは、その第1導電率タイプは、そのn−ドープされた基板が一次キャリアーとして電子を有するので、“負”である。

【0016】

分離領域12が形成された後、この技術分野で常用されているような熱的酸化により、基板10のクリーンな活性デバイス領域の上に、誘電性層またはゲート酸化物層14が形成される。次いで、そのゲート酸化物層14の上に、その場で(in−situ)ドープされたポリシリコン層18を含むゲート電極16が、低圧化学気相堆積法(LPCVD)、プラズマ・エンハンスド化学気相堆積法(PECVD)または物理的気相堆積法(PVD)のような既知の方法により堆積される。このポリシリコン層18は、この技術分野での常用法でエッチングされ、基板10の活性領域内のゲート電極16に望ましいパターンが提供される。このゲート酸化物層14の厚さは約20〜約80オングストロームであるのが望ましいが、ゲート酸化物の厚さ(tox)はそのテクノロジー・ノード(technology node)に依存するから、本発明の方法は、より薄いゲート酸化物層が要求される任意のテクノロジー・ノードで有用であると信じられる。さらに、そしてまたテクノロジー・ノードに依存する場合でも、本発明の望ましい態様では、そのポリシリコン層18と、その高ドープされた(highly doped)ポリシリコン層からパターン化されたゲート電極16の総厚さは、約200〜約1000オングストロームであるのが望ましい。

【0017】

本発明の実施にとって必須ではないが、一般に、ゲート電極16のポリシリコン層18の上に追加の材料の層を形成させるために、さらなる材料が堆積されてもよい。これら層用の標準的材料に含まれるのは、このデバイスの電気的特性を改善する目的で用いられる、金属類、金属合金類、高ドープされたポリシリコン、ケイ化物類およびポリサイド類(ポリシリコン/金属ケイ化物−スタック)である。推奨される一つの態様では、窒化チタニウム(TiN)の比較的薄い層が、バリアー層20を形成するためにポリシリコン層18の上に堆積される。次いで、このバリアー層20はタングステン(W)層22で覆われて、ゲート電極16の形成が完了する。

【0018】

本発明の一つの態様に従う、ゲート構造を作製するプロセス工程を一般的に例示している図2A〜2Cに見られるように、ゲート酸化物層14は、望ましくはシリコン基板である半導体基板10上に熱酸化により成長させられる。酸化物層14の上にポリシリコン層が堆積され、そして光エッチング法を用いてパターン化されて、ゲート構造15が形成される。ゲート酸化物層14に接しているゲート構造15の表面はリーディング・エッジ17を有している。次いで、図2Bに示したように、その基板10の表面を覆ってフォトレジスト層23を取付け、そしてパターン化して酸化物層14とゲート構造15の両方の一部を露出させる。この酸化物層14のオーバーラップ領域26を、選択的にイオンでドープするために、常用の装置を用いて、傾斜角度をつけて、高注入量、低エネルギーで注入することで、イオンインプラント24が行われる。

【0019】

図2Cに示したように、オーバーラップ領域26は、ゲート構造15の下で、そのリーディング・エッジ17に隣接している。このイオンインプラント24は、望ましくはフッ素であり、そして代替として、塩素または酸化物層14の誘電率を低下させる任意の他のイオンでもよい。推奨される態様で、このフッ素イオンは:(1)その基板10の面に直交する軸から約5から約15度の傾斜角で、(2)平方センチメートル当たり約1E13から約1E14原子のイオン注入量で、そして(3)約10KeVから約20KeVのイオン注入エネルギーで、注入される。イオン注入に推奨される角度範囲は約5から約15度であるが、イオン注入角は、ゲート構造15のスタックの高さに依存することに留意すべきである。フッ素イオンインプラント24の注入は、オーバーラップ領域26で、ゲート構造15の下で、推奨されるイオン濃度:約1E18原子/cm3に達するように調整することが重要である。この推奨される濃度まで、オーバーラップ領域26を選択的にドーピングすると、そのオーバーラップ領域の近くのゲート酸化物層14の誘電率が変化する(低下する)。

【0020】

フォトレジスト層23を除去した図2Cに示したように、この推奨されるイオン濃度までドーピングすると、従来技術の方法におけるように、その酸化物層14のtoxが物理的に成長または増加することなく、オーバーラップ領域26における“電気的ゲート酸化物”厚さは増加する。そこで、本発明により形成されたこのゲート構造で、その半導体基板10の作製がさらに継続され、回路デバイスが完成されてもよい。

【0021】

本発明の方法により形成され得るこのようなデバイスの一つは、電界効果トランジスタである。このFETデバイスの製造が、一連の横断面図でその逐次段階を模式的に例示した図3A〜3Dにより示されている。最初の図3Aは、図1を参照して考察された従来技術の方法(しかし必須ではない)に従って作製された一部完成のFETデバイス2である。図2A〜2Cを参照して上に説明したように、オーバーラップ領域26でのイオン注入(イオンインプラント24)を行う前に、基板10で短い再酸化が行われる。半導体基板10の再酸化またはアニーリングのために、数種の方法が用いられてもよく、これら方法には、熱的方法、迅速熱処理(Rapid Thermal Processing:RTP)法およびレーザー支援処理法が含まれるが、これらに限定はされない。本発明の推奨される態様で、基板10は、熱的方法で、約800〜約900℃の温度で約10〜約15分間アニーリングされる。

【0022】

上の短い再酸化期間の後、ゲート酸化物層14のオーバーラップ領域26とゲート電極16のポリシリコン層18に、イオンで選択的にドープするためのイオン注入工程(イオンインプラント24)が、常用の装置で行われる。前述のように、このイオンインプラント24は、望ましくはフッ素であり、そして代替として、塩素またはゲート酸化物層14の誘電率を低下させる任意の他のイオンでもよい。さらに、重要なことは、標準的なFETデバイス2にとって、フッ素イオンインプラント24の望ましい注入工程は、ドレイン領域30bに隣接するゲート電極16の下のゲート−ポリ/ゲート酸化物界面で、約1E18原子/cm3のイオン濃度に達するように調整されることである。ゲート−ドレイン・オーバーラップ領域26を、この推奨されるイオン濃度まで選択的にドーピングすると、オーバーラップ領域26近くのゲート酸化物14の誘電率が変化し(低下し)、かくして、オーバーラップ領域26における“電気的ゲート酸化物”厚さは増すが、従来技術の方法におけるように、物理的に成長してより厚いゲート酸化物層24になることはない。

【0023】

図3B〜3Dに例示されているように、FETデバイス2を完成するために、上述の図3Aのイオン注入工程の後に、任意の常用の方法で、残りの製作工程が継続される。図3Bで示したように、FETデバイス2の上に、さらに、ゲート電極16の両側に隣接し、そしてその電場分離領域12にまで延びているソース領域28aおよびドレイン領域28bから成る不純物拡散領域が形成される。そのゲート電極16に隣接するソース/ドレイン領域28aおよび領域28bのエッジが、基板10の表面でチャネル領域29を規定する。ソース/ドレイン領域28aおよび領域28bは、普通、低ドープされたドレイン(lightly doped drain:LDD)を、そして次いで高ドープされたドレイン(heavily doped drain:HDD)を形成させるために、不純物ドーパント材料による二段階注入法で作製される。ソース/ドレイン領域28aおよび領域28bの作製に用いられた不純物ドーパント材料が、そのソース/ドレイン領域で一次キャリアーとして電子を用いるn−タイプであると、その場合得られるMOSFETは、N−MOSFET(“n−チャネル”)トランジスタ・デバイスである。例えば、ひ素またはリンが、cm2当たり約2E15〜約5E15原子の量で、そして約5KeV〜約15KeVのエネルギーで、このn−チャネル・ドープされたドレイン28aおよび28bを生成させるために用いられてもよい。逆に、ソース/ドレインドーパント用材料が、そのソース/ドレイン領域で一次キャリヤーとしてホール(空孔)を用いるp−タイプであると、その場合得られるMOSFETは、P−MOSFET(“p−チャネル”)トランジスタ・デバイスである。例えば、ジフッ化ホウ素が、cm2当たり約2E15〜約5E15原子の量で、そして約10KeV〜約25KeVのエネルギーで、そのp−チャネル・ドープされたドレイン28aおよび28bを生成させるために用いられてもよい。FETデバイス2が、同じ基板10の上にn−チャネルおよびp−チャネル・トランジスタの組合せで形成されていると、その時得られるMOSFETは相補型FET(CMOS)であり、そして同じ基板10上の、複数のN−MOSFETと複数の相補型P−MOSFETから構成されてもよい。

【0024】

このソース/ドレイン領域28aおよび28bを作る場合、第1イオン注入はLDDソース/ドレイン領域30aおよび30bのより低くドープされた部分を形成させるために、その基板をマスクするためのゲート電極16および電界分離領域12を用いて行われる。一般に、本発明の実施に必須ではないが、図3Cに示されるように、そのゲート電極16の両側に、電極スペーサ32が準備される。この電極スペーサ32は、酸化ケイ素、窒化ケイ素およびオキシ窒化ケイ素(silicon oxynitrides)のような絶縁性材料を含む材料(これらに限定はされない)から作られてもよい。電極スペーサ32を作るためには、様々な方法が用いられる。このような方法に含まれるのは、反応性イオンエッチング(Reactive Ion Etch:RIE)、および上述の材料堆積法である。普通、電極スペーサ32は、テトラエトキシシラン(TEOS)オキシドのような酸化物フィルムを、約600〜約720℃で、約300〜約700オングストロームの厚さに堆積させることにより作られる。第2イオン注入は、HDDソース/ドレイン領域34aおよび34bを有するソース/ドレイン領域28aおよび28bを完成するために行われる。例示したFETデバイス2で、このソース/ドレイン領域20は、n−タイプまたはp−タイプ・ドーパントでドープされてもよく、あるいは、異なる拡散特性を達成するために、異なるn−タイプドーパントまたはp−タイプ・ドーパントの組合せが用いられることもある。さらに、本発明の傾斜イオン注入工程は、希望によってLDD、スペーサあるいはまたHDDのどれか一つの生成の前または後にこの工程を行っても外見上の利点または欠点が無いので、FETデバイス2の製作のこの段階でも行われ得ることに留意すべきである。

【0025】

基板10へのソース/ドレイン領域28aおよび28bの取付けに次いで基板10は、ソース/ドレイン領域24aおよび24bを再結晶化させるために、もう一度アニーリングされる。前と同様にソース/ドレイン領域28aおよび28bのアニーリングも、熱的方法、急速熱処理(RTP)法およびレーザー支援法で行われてもよい。本発明の推奨される態様では、この半導体基板は、再結晶化されたソース/ドレイン領域28aおよび28bを生成させるために、約800〜約1000℃の温度で約10〜約20秒の間、RTP−法でアニーリングされる。

【0026】

さて図3Dを参照すると、本発明の推奨される態様に従ってFETを作製する最終の一連の加工工程が、横断面模式図として例示されている。図3Dに、パターン化されたインターレベル誘電体層36a、36bおよび36cが示されている。パターン化されたインターレベル誘電体層36a、36bおよび36cは、基板10上に作られたブランケットインターレベル誘電性層を、この分野で知られているような光リソグラフ法および光エッチング法でパターン化することにより作製される。ブランケット・インターレベル誘電性層は、酸化ケイ素、窒化ケイ素およびオキシ窒化ケイ素を含む絶縁性材料から作られてもよいが、それら材料に限定はされない。これらの絶縁性層は、化学気相堆積(CVD)法、プラズマ・エンハンスド化学気相堆積(PECVD)法または物理的堆積(PVD)法を含む方法により半導体基板の上に形成されてもよいが、これら方法に限定はされない。

【0027】

本発明の推奨される態様では、このパターン化されたインターレベル誘電体層36a、36bおよび36cは、この分野で知られているような光リソグラフ法および光エッチング法を用い、ソース材料としてテトラエチル・オルトシリケート(TEOS)を使用する化学気相堆積(CVD)法によって基板10上に堆積された酸化ケイ素材料から形成されているブランケット・インターレベル誘電性層をパターン化することにより作製される。他の方法と材料により作られた絶縁層も用いられてもよいが、この推奨される方法および材料は、簡単で、そしてこの技術分野で良く知られている方法である。パターン化されたインターレベル誘電体層36aおよび36bと、パターン化されたインターレベル誘電体層36bおよび36cの間の開口部の底部は、ゲート酸化物層14を通してエッチングされ、ソース/ドレイン領域28aと28bの表面がそれぞれ露出される。このパターン化されたインターレベル誘電体層36aおよび36bと、パターン化されたインターレベル誘電体層36bおよび36cの間の開口部にそれぞれ形成されている導電性コンタクトスタッド(conductive contact studs)38aと38bは、それぞれ、そのソース/ドレイン領域28aと28bの露出された表面と接している。この導電性コンタクトスタッド38aと38bは、この技術分野で常用されている物で、熱気相堆積法(thermal evaporation method)、電子ビーム支援気相堆積法およびCVD法を含む方法(これら方法に限定はされない)により半導体基材上に堆積された金属類、金属合金類およびポリシリコンを含む導電性材料(これら材料に限定はされない)から作られてもよい。本発明の推奨される態様では、この導電性コンタクトスタッド38aおよび38bは、厚さ約200〜約1000オングストロームの薄い窒化チタニウム・バリヤー層から作られるのが望ましく、その上に、より厚い導電性タングステン層が形成される。このタングステン層は、インターレベル誘電体層36a、36bおよび36c内の開口部を完全に充填するのに十分な厚さである。

【0028】

このパターン化されたインターレベル誘電体層36a、36bおよび36c内に導電性コンタクトスタッド38aと38bを形成させると、集積回路内に本発明の推奨される態様のFETデバイス2が作製され、このFETデバイスは、類似設計の従来のFETデバイスよりGIDLが少ない。本発明の方法は、sub−vtおよびドライブ(drives)のような他のデバイス特性を犠牲にすることなしに、GIDL電流が低下するという、従来技術より優れた利点を有していることが評価されるべきである。従って、本発明の方法を適用することにより作られた新しい電気的フロー(electrical flow)は、スケーリング則(scaling rules)によって、ディープ・サブミクロン(deep submicron)の幾何学的形状物で、ゲート酸化物の厚さを薄くすることが可能である。従って、本発明の方法は、DRAM、SRAM、EPROM、ASICなどのような集積回路デバイスを作るための任意の二重(またはそれ以上の多重の)ポリシリコン法で利用することができる。

【0029】

本発明は、詳細に、そしてその推奨される実施態様を引用することにより説明されたが、添付された特許請求の範囲に詳細に記載された本発明の範囲から逸脱することなしに、修正法および変法が可能であることは明らかであろう。

【図面の簡単な説明】

【図1】図1は、従来技術の常法により半導体基板上に形成された一部完成FET回路デバイスの横断面を例示した概略図である。

【図2】図2A〜2Cは、本発明の一つの態様に従うゲート構造を作製する加工工程を例示している。

【図3】図3A〜3Dは、本発明の方法に従ってFETデバイスの作製を完成する逐次段階を例示する一連の横断面を例示した概略図である。

同じ参照番号は、各態様図を通して同じ部分に対応する。

Claims (44)

- 半導体層;

該半導体層上に形成された酸化物層;

該酸化物層上に形成されたポリシリコン層;

該ポリシリコン層から形成された、規定されたリーディング・エッジを有するゲート構造;および

該ゲート構造の下で、そして該リーディング・エッジに隣接している、所定のイオン注入濃度を有するオーバーラップ領域であって、その注入濃度は、そのオーバーラップ領域での電気的ゲート酸化物厚さを増加させるのに十分であるオーバーラップ領域;

を含む回路構造。 - 該所定のイオン注入濃度が、フッ素のcm3当たり約1E18原子である請求項1に記載の回路構造。

- 半導体層;

該半導体層中の、第1導電率−タイプドーパントで低ドープされているソース

領域およびドレイン領域;

該ソース領域とドレイン領域の間に所在するチャネル領域;

該チャネル領域の表面に所在するゲート酸化物層;および

該ゲート酸化物層上に所在するゲート電極であって、該ゲート酸化物層の一部が、該ゲート電極の下で、そして該ドレイン領域に隣接しており、オーバーラップ領域を規定しており、そして該オーバーラップ領域中の表面電場を低下させるのに有効であるイオン注入濃度を有している、ゲート電極;を含む回路構造。 - 該イオン注入濃度が、フッ素のcm3当たり約1E18原子である請求項3に記載の回路構造。

- 該ソース領域と該ドレイン領域が、第2導電率ドーパントで高ドープされている、請求項3に記載の回路構造。

- 該ゲート電極に隣接する一対のスペースをさらに含んでいる、請求項3に記載の回路構造。

- 該ゲート電極がポリシリコンを含んでなる、請求項3に記載の回路構造。

- 該ゲート電極がゲート・スタックである、請求項3に記載の回路構造。

- 該ゲート電極が、ポリシリコンの層および、金属類、金属合金類、高ドープされたポリシリコン、ケイ化物類およびポリサイド類(ポリシリコン/金属ケイ化物−スタック)からなる群から選ばれる一つまたはそれ以上の追加の層を含んでなる、請求項3に記載の回路構造。

- 該ゲート電極が、ポリシリコンの層、該ポリシリコン層上に堆積された窒化チタニウムの層および該チタニウム層上に堆積されたタングステンの層を含んでなる、請求項3に記載の回路構造。

- 該半導体層上に取付けられた、一対の導電性スタッドとインターレベル誘電性層をさらに含んでおり、該インターレベル誘電性層が、各該対の導電性スタッドの一つをそれぞれ収容している一対の通孔(through bores)を有しており、そして各該対の導電性スタッドの一つが、各該ソース/ドレイン領域の一つに接しているところの、請求項3に記載の回路構造。

- 半導体層;第1ドーパント−タイプMOSトランジスタおよび、該第1ドーパント−タイプMOSトランジスタを相補する第2タイプードーパントMOSトランジスタ、を含む回路構造であって;

該第1ドーパント−タイプMOSトランジスタは、第1導電率−タイプ・ドーパントでドープされている該半導体層中のソース領域とドレイン領域;

該ソース領域とドレイン領域の間に所在するチャネル領域;

該チャネル領域の表面に所在するゲート酸化物層;および

該ゲート酸化物層(ゲート酸化物層の一部は、該ゲート電極の下にあって該ドレイン領域に隣接していて、そしてオーバーラップ領域を規定しており、該オーバーラップ領域内でその表面電場を低下させるのに有効なイオン注入濃度を有している)上に所在するゲート電極;

を有する該半導体層上に所在しており、そして;

該第2タイプードーパントMOSトランジスタは、該半導体層上に所在しており、そして第2ゲート酸化物層、第2導電率−タイプドーパントでドープされている二つの相補ソース/ドレイン領域、および該第2ゲート酸化物層上に所在する相補ゲート、を含んでいる;

回路構造。 - 該イオン注入濃度が、フッ素のcm3当たり約1E18原子である、請求項12に記載の回路構造。

- 該相補ゲート電極の下で、そして該相補ドレイン領域に隣接しており、そして第2オーバーラップ領域を規定する該第2ゲート酸化物層の一部が、該第2オーバーラップ領域中で、その表面電場を低下させるために有効なイオン注入濃度を有する、請求項12に記載の回路構造。

- 半導体層上に酸化物層を形成させる工程;該酸化物層上にポリシリコン層を形成させる工程;該ポリシリコン層を、規定されたリーディングエッジを有するゲート構造にパターン化し、そして該酸化物層を露出させる工程;および、該ゲート構造の下で、該規定されたリーディング・エッジに隣接するオーバーラップ領域で、該酸化物層の厚さを増加させずに、該オーバーラップ領域中だけでその電気的ゲート酸化物厚さを増加させるのに十分な所定のイオン注入濃度まで酸化物層にイオンを注入する工程であって、該イオンが該半導体層の面に非直交の傾斜角度で注入される工程、を含む半導体層上に構造を作製するための方法。

- 該所定のイオン注入濃度が、フッ素のcm3当たり約1E18原子である請求項15に記載の方法。

- 該傾斜角度が、その半導体層の面に直交する軸から約5〜約15度である請求項15に記載の方法。

- 該イオンが、フッ素と塩素からなる群から選ばれる請求項15に記載の方法。

- 該イオンがフッ素であり、そして該注入工程が、約1E13〜約1E14原子/cm2のイオン注入量で、そして約10KeV〜約20KeVのイオン注入エネルギーで、行われる、請求項15に記載の方法。

- 該半導体層を、約800〜約900℃の温度で、約10〜約15分の間アニーリングする工程をさらに含んでいる、請求項15に記載の方法。

- 該酸化物層の厚さが、約20〜約80オングストロームである請求項15に記載の方法。

- 該ゲート構造の両側に電極スペーサを形成させる工程をさらに含む、請求項15に記載の方法。

- 該ゲート構造がポリシリコンを含んでなる、請求項15に記載の方法。

- 該ゲート構造がゲート・スタックである、請求項15に記載の方法。

- 該ゲートスタックが、ポリシリコンの層および,金属類、金属合金類、高ドープされたポリシリコン、ケイ化物類およびポリサイド類(ポリシリコン/金属ケイ化物−スタック)からなる群から選ばれる追加の層、を含んでなる、請求項24に記載の方法。

- 該ゲート構造が、ポリシリコンの層、該ポリシリコンの層の頂部に堆積された窒化チタニウムの層および該チタニウム層の頂部に堆積されたタングステンの層を含んでなるゲート電極である、請求項15に記載の方法。

- 該酸化物層が、低圧化学気相堆積法により、約20〜約80オングストロームの厚さに形成される、請求項15に記載の方法。

- 該ゲート構造に隣接する半導体層内に低ドープされたドレインソース/ドレイン領域構造を形成させることをさらに含む、請求項15に記載の方法。

- 該低ドープされた領域が、リンおよびヒ素からなる群から選ばれるイオンを、約5〜約15KeVのエネルギーで、約2E15〜約5E15原子/cm2の量、注入することにより形成されるn−タイプ領域である、請求項28に記載の方法。

- 該低ドープされた領域が、ジフッ化ホウ素イオンを、約10〜約25KeVのエネルギーで、約2E15〜約5E15原子/cm2の量、注入することにより作製されるp−タイプ領域である、請求項28に記載の方法。

- そのゲート構造に隣接する半導体層内に、高ドープされたドレインソース/ドレイン領域構造を形成させる工程をさらに含む、請求項15に記載の方法。

- 該高ドープされた領域が、リンおよびヒ素からなる群から選ばれるイオンを、約5〜約15KeVのエネルギーで、約2E15〜約5E15原子/cm2の量、注入することにより作製されるn−タイプ領域である、請求項31に記載の方法。

- 該高ドープされた領域が、ジフッ化ホウ素イオンを、約10〜約25KeVのエネルギーで、約2E15〜約5E15原子/cm2の量、注入することにより作製されるp−タイプ領域である、請求項31に記載の方法。

- 該ゲート構造の両側に電極スペーサを形成させる工程をさらに含む、請求項15に記載の方法。

- 該電極スペーサが、約300〜約700オングストロームの幅を有する、請求項34に記載の方法。

- 該注入工程が、該ポリシリコン層を形成させる該工程の前に行われる、請求項15に記載の方法。

- 該注入工程が、該ポリシリコン層をパターン化する該工程の前に行われる、請求項15に記載の方法。

- 半導体層上に、ゲート酸化物層、そのゲート酸化物層上のゲート電極および該半導体層内に形成された二つのソース/ドレイン領域を含む電界効果トランジスタ構造を形成させる工程;

該半導体層をアニーリングする工程;

該ゲート電極の下で、該ドレイン領域に隣接しているオーバーラップ領域を規定するゲート酸化物層に、該オーバーラップ領域中だけでその電気的ゲート酸化物厚さを増加させるのに十分な所定のイオン注入濃度までイオンを注入する工程であって、そのイオンはその半導体層の面に非直交の傾斜角で注入される工程;

および

該半導体層の作製を完成する工程;

を含んでいる、電界効果トランジスタ(FETs)内のゲート誘起ドレイン漏洩(GIDL)電流を減らす方法。 - 該半導体層の上に形成された該FETが、第1ドーパントタイプを有する複数の第1FETであり、そして該半導体層は第2ドーパントタイプを有する複数の第2FETも含んでおり、該第2FETは、該第1FETに相補的である、請求項38に記載の方法。

- 該イオン注入濃度が、フッ素のcm3当たり約1E18原子である、請求項38に記載の方法。

- 該傾斜角度が、該半導体層の面に直交する軸から、約5〜約15度である、請求項38に記載の方法。

- 該イオンが、フッ素と塩素からなる群から選ばれる、請求項38に記載の方法。

- 該イオンがフッ素であり、そして該注入工程が、約1E13〜約1E14原子/cm2のイオン注入量で、そして約10KeV〜約20KeVのイオン注入エネルギーで、行われる請求項38に記載の方法。

- 該アニーリング工程が、約800〜約1000℃の温度で、約10〜約20秒の間行われる、請求項38に記載の方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/648,044 US7247919B1 (en) | 2000-08-25 | 2000-08-25 | Method and device to reduce gate-induced drain leakage (GIDL) current in thin gate oxides MOSFETs |

| PCT/US2001/026342 WO2002019431A2 (en) | 2000-08-25 | 2001-08-23 | Method and device to reduce gate-induced drain leakage (gidl) current in thin gate oxide mosfets |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004508717A true JP2004508717A (ja) | 2004-03-18 |

| JP2004508717A5 JP2004508717A5 (ja) | 2005-04-21 |

Family

ID=24599198

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002524227A Pending JP2004508717A (ja) | 2000-08-25 | 2001-08-23 | 薄いゲート酸化物MOSFETsでのゲート誘起ドレイン漏洩(GIDL)電流を減らす方法およびデバイス |

Country Status (7)

| Country | Link |

|---|---|

| US (3) | US7247919B1 (ja) |

| EP (1) | EP1312110A2 (ja) |

| JP (1) | JP2004508717A (ja) |

| KR (1) | KR100563398B1 (ja) |

| AU (1) | AU2001286666A1 (ja) |

| SG (1) | SG140464A1 (ja) |

| WO (1) | WO2002019431A2 (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4177192B2 (ja) * | 2003-08-05 | 2008-11-05 | 株式会社日立ハイテクノロジーズ | プラズマエッチング装置およびプラズマエッチング方法 |

| US6797555B1 (en) * | 2003-09-10 | 2004-09-28 | National Semiconductor Corporation | Direct implantation of fluorine into the channel region of a PMOS device |

| US7189292B2 (en) | 2003-10-31 | 2007-03-13 | International Business Machines Corporation | Self-encapsulated silver alloys for interconnects |

| US7245548B2 (en) * | 2004-07-27 | 2007-07-17 | Micron Technology, Inc. | Techniques for reducing leakage current in memory devices |

| US20060291114A1 (en) * | 2005-06-27 | 2006-12-28 | Teo Chee K | Electrostatic discharge protection circuit and method |

| US8154088B1 (en) | 2006-09-29 | 2012-04-10 | Cypress Semiconductor Corporation | Semiconductor topography and method for reducing gate induced drain leakage (GIDL) in MOS transistors |

| US20080286932A1 (en) * | 2007-05-17 | 2008-11-20 | Dongbu Hitek Co., Ltd. | Method of manufacturing semiconductor device |

| US20090090975A1 (en) * | 2007-10-09 | 2009-04-09 | Chartered Semiconductor Manufacturing Ltd. | Integrated circuit system employing fluorine doping |

| KR20120133652A (ko) * | 2011-05-31 | 2012-12-11 | 삼성전자주식회사 | 반도체 소자의 제조 방법 |

| CN102420228B (zh) * | 2011-06-17 | 2015-01-07 | 上海华力微电子有限公司 | 抑制gidl效应的后栅极工艺半导体器件及其制备方法 |

| US8896035B2 (en) | 2012-10-22 | 2014-11-25 | International Business Machines Corporation | Field effect transistor having phase transition material incorporated into one or more components for reduced leakage current |

| KR102065973B1 (ko) | 2013-07-12 | 2020-01-15 | 삼성전자 주식회사 | 반도체 장치 및 그 제조 방법 |

| US10734511B2 (en) | 2016-03-31 | 2020-08-04 | Intel Corporation | High mobility asymmetric field effect transistors with a band-offset semiconductor drain spacer |

| WO2018182570A1 (en) * | 2017-03-28 | 2018-10-04 | Intel IP Corporation | Assymetric transistor arrangements with smartly spaced drain regions |

| CN112864223A (zh) | 2019-11-28 | 2021-05-28 | 联华电子股份有限公司 | 半导体晶体管及其制作方法 |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2652108B2 (ja) * | 1991-09-05 | 1997-09-10 | 三菱電機株式会社 | 電界効果トランジスタおよびその製造方法 |

| JPH0653492A (ja) * | 1992-07-29 | 1994-02-25 | Kawasaki Steel Corp | 半導体装置及びその製造方法 |

| US5382533A (en) * | 1993-06-18 | 1995-01-17 | Micron Semiconductor, Inc. | Method of manufacturing small geometry MOS field-effect transistors having improved barrier layer to hot electron injection |

| US5372957A (en) | 1993-07-22 | 1994-12-13 | Taiwan Semiconductor Manufacturing Company | Multiple tilted angle ion implantation MOSFET method |

| JP3297173B2 (ja) * | 1993-11-02 | 2002-07-02 | 三菱電機株式会社 | 半導体記憶装置およびその製造方法 |

| KR0136932B1 (ko) | 1994-07-30 | 1998-04-24 | 문정환 | 반도체 소자 및 그의 제조방법 |

| SG50741A1 (en) * | 1995-07-26 | 1998-07-20 | Chartered Semiconductor Mfg | Method for minimizing the hot carrier effect in m-mosfet devices |

| US5719425A (en) | 1996-01-31 | 1998-02-17 | Micron Technology, Inc. | Multiple implant lightly doped drain (MILDD) field effect transistor |

| JPH1079506A (ja) | 1996-02-07 | 1998-03-24 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |

| US5672525A (en) | 1996-05-23 | 1997-09-30 | Chartered Semiconductor Manufacturing Pte Ltd. | Polysilicon gate reoxidation in a gas mixture of oxygen and nitrogen trifluoride gas by rapid thermal processing to improve hot carrier immunity |

| US5804496A (en) | 1997-01-08 | 1998-09-08 | Advanced Micro Devices | Semiconductor device having reduced overlap capacitance and method of manufacture thereof |

| US5840610A (en) * | 1997-01-16 | 1998-11-24 | Advanced Micro Devices, Inc. | Enhanced oxynitride gate dielectrics using NF3 gas |

| US5998274A (en) | 1997-04-10 | 1999-12-07 | Micron Technology, Inc. | Method of forming a multiple implant lightly doped drain (MILDD) field effect transistor |

| JPH1117174A (ja) | 1997-06-20 | 1999-01-22 | Sony Corp | Mis型トランジスタ素子のゲート電極及びその形成方法 |

| US5920782A (en) | 1997-07-18 | 1999-07-06 | United Microelectronics Corp. | Method for improving hot carrier degradation |

| JP2002509361A (ja) * | 1997-12-18 | 2002-03-26 | マイクロン テクノロジー, インク. | 半導体製造方法及び電界効果トランジスタ |

| US6030875A (en) | 1997-12-19 | 2000-02-29 | Advanced Micro Devices, Inc. | Method for making semiconductor device having nitrogen-rich active region-channel interface |

| US6188101B1 (en) | 1998-01-14 | 2001-02-13 | Advanced Micro Devices, Inc. | Flash EPROM cell with reduced short channel effect and method for providing same |

| US6238998B1 (en) | 1998-11-20 | 2001-05-29 | International Business Machines Corporation | Shallow trench isolation on a silicon substrate using nitrogen implant into the side wall |

| JP3376305B2 (ja) | 1998-12-25 | 2003-02-10 | 株式会社東芝 | 半導体装置の製造方法 |

| US6242334B1 (en) | 1999-03-23 | 2001-06-05 | United Microelectronics Corp. | Multi-step spacer formation of semiconductor devices |

| US6297098B1 (en) | 1999-11-01 | 2001-10-02 | Taiwan Semiconductor Manufacturing Company | Tilt-angle ion implant to improve junction breakdown in flash memory application |

| US6352912B1 (en) | 2000-03-30 | 2002-03-05 | International Business Machines Corporation | Reduction of reverse short channel effects by deep implantation of neutral dopants |

| US6352885B1 (en) * | 2000-05-25 | 2002-03-05 | Advanced Micro Devices, Inc. | Transistor having a peripherally increased gate insulation thickness and a method of fabricating the same |

-

2000

- 2000-08-25 US US09/648,044 patent/US7247919B1/en not_active Expired - Lifetime

-

2001

- 2001-08-23 AU AU2001286666A patent/AU2001286666A1/en not_active Abandoned

- 2001-08-23 SG SG200501097-0A patent/SG140464A1/en unknown

- 2001-08-23 EP EP01966127A patent/EP1312110A2/en not_active Ceased

- 2001-08-23 WO PCT/US2001/026342 patent/WO2002019431A2/en not_active Application Discontinuation

- 2001-08-23 KR KR1020037002699A patent/KR100563398B1/ko active IP Right Grant

- 2001-08-23 JP JP2002524227A patent/JP2004508717A/ja active Pending

- 2001-12-27 US US10/034,778 patent/US6693012B2/en not_active Expired - Lifetime

-

2006

- 2006-07-31 US US11/496,288 patent/US20060263964A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| WO2002019431A2 (en) | 2002-03-07 |

| US20060263964A1 (en) | 2006-11-23 |

| US7247919B1 (en) | 2007-07-24 |

| EP1312110A2 (en) | 2003-05-21 |

| US20020050621A1 (en) | 2002-05-02 |

| AU2001286666A1 (en) | 2002-03-13 |

| WO2002019431A3 (en) | 2002-10-17 |

| KR100563398B1 (ko) | 2006-03-23 |

| US6693012B2 (en) | 2004-02-17 |

| KR20030043939A (ko) | 2003-06-02 |

| SG140464A1 (en) | 2008-03-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20060263964A1 (en) | Method and device to reduce gate-induced drain leakage (GIDL) current in thin gate oxide MOSFETs | |

| US6365472B1 (en) | Semiconductor device and method of manufacturing the same | |

| US6828185B2 (en) | CMOS of semiconductor device and method for manufacturing the same | |

| JP2897004B2 (ja) | Cmosfet製造方法 | |

| US5930615A (en) | Method of forming CMOS having simultaneous formation of halo regions of PMOS and part of source/drain of NMOS | |

| JP2513402B2 (ja) | 半導体装置の構造及び製造方法 | |

| US5940710A (en) | Method for fabricating metal oxide semiconductor field effect transistor | |

| US6596594B1 (en) | Method for fabricating field effect transistor (FET) device with asymmetric channel region and asymmetric source and drain regions | |

| JPH0669229A (ja) | Gold構造を有する半導体素子の製造方法 | |

| US20060134874A1 (en) | Manufacture method of MOS semiconductor device having extension and pocket | |

| JP2927161B2 (ja) | 半導体メモリとその製法 | |

| JP2001156290A (ja) | 半導体装置 | |

| JP2004508717A5 (ja) | ||

| US6078079A (en) | Semiconductor device and method of manufacturing the same | |

| JPH01259560A (ja) | 半導体集積回路装置 | |

| JPH01283956A (ja) | 半導体装置およびその製造方法 | |

| JPH10256549A (ja) | 半導体装置及びその製造方法 | |

| JPH0738095A (ja) | 半導体装置及びその製造方法 | |

| JP4115769B2 (ja) | 半導体装置及びその製造方法 | |

| JPS6074663A (ja) | 相補型半導体装置の製造方法 | |

| JPH06140590A (ja) | 半導体装置の製造方法 | |

| JP3277912B2 (ja) | 半導体装置の製造方法 | |

| JPS62130563A (ja) | 半導体装置 | |

| JPH02302042A (ja) | 半導体装置の製造方法 | |

| JPH0737994A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20061101 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061116 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070216 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20070511 |