CN1172249C - 数据传送控制装置和电子设备 - Google Patents

数据传送控制装置和电子设备 Download PDFInfo

- Publication number

- CN1172249C CN1172249C CNB011448423A CN01144842A CN1172249C CN 1172249 C CN1172249 C CN 1172249C CN B011448423 A CNB011448423 A CN B011448423A CN 01144842 A CN01144842 A CN 01144842A CN 1172249 C CN1172249 C CN 1172249C

- Authority

- CN

- China

- Prior art keywords

- clock

- control device

- mentioned

- data transmission

- transmission control

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000005540 biological transmission Effects 0.000 claims description 103

- 238000012545 processing Methods 0.000 claims description 60

- 230000010355 oscillation Effects 0.000 claims description 53

- 230000000873 masking effect Effects 0.000 description 8

- 238000001914 filtration Methods 0.000 description 6

- 230000001360 synchronised effect Effects 0.000 description 6

- 239000002699 waste material Substances 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- 230000003534 oscillatory effect Effects 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 4

- 230000000052 comparative effect Effects 0.000 description 3

- 102100040858 Dual specificity protein kinase CLK4 Human genes 0.000 description 2

- 101000749298 Homo sapiens Dual specificity protein kinase CLK4 Proteins 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 238000009499 grossing Methods 0.000 description 2

- 238000000034 method Methods 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 238000005070 sampling Methods 0.000 description 2

- 230000001364 causal effect Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 230000005055 memory storage Effects 0.000 description 1

- 230000003278 mimic effect Effects 0.000 description 1

- 230000008054 signal transmission Effects 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/07—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop using several loops, e.g. for redundant clock signal generation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/06—Clock generators producing several clock signals

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/099—Details of the phase-locked loop concerning mainly the controlled oscillator of the loop

- H03L7/0995—Details of the phase-locked loop concerning mainly the controlled oscillator of the loop the oscillator comprising a ring oscillator

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/16—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop

- H03L7/18—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using a frequency divider or counter in the loop

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Information Transfer Systems (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Power Sources (AREA)

- Small-Scale Networks (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

- Facsimiles In General (AREA)

Abstract

本发明的目的在于提供可在不产生动作不良的情况下,动态地对待发生的时钟的频率进行切换的数据传送控制装置,以及电子设备。该数据传送控制装置包括时钟发生电路(440),该时钟发生电路发生时钟(CLKH,CLKF)对时钟发生电路(440)进行控制;时钟控制电路(450),该时钟控制电路(450)根据上述时钟(CLKH,CLKF),发生系统时钟(SYCLK)。在不执行发生时钟(CLKH)的PLL480M的自由振荡动作之前,实现发生时钟(CLKF)的PLL60M的自由振荡动作,在PLL60M的自由振荡动作稳定后,将系统时钟(SYCLK)的发生元从时钟(CLKH),切换到时钟(CLKF)。以时钟(CLKH)变为“0”为条件,仅仅在规定期间将系统时钟(SYCLK)设定在“0”,以时钟(CLKF)变为“0”为条件,根据时钟(CLKF),发生系统时钟(SYCLK)。在从USB2.0的HS,向FS模式切换时,不执行PLL480M的动作,实现节电。

Description

技术领域

本发明涉及一种数据传送控制装置和电子设备。

发明背景

近年来,作为用于将个人计算机与外围设备(从广义上说,为电子设备)连接的接口标准,USB(通用串行接口)受到人们的关注,该USB的优点在于在过去,可通过相同标准的接插件,连接通过不同标准的接插件连接的鼠标或键盘,或打印机等的外围设备,另外可实现所谓的插拨和热插拔。

该USB与作为相同的串行接口标准,与已使用的IEEE1394相比较,具有传送速度较慢的问题。

于是,人们制定USB2.0标准,其在使已有的USB1.1的标准保持下位互换性的同时,与USB1.1相比较,可实现更高速的480Mbps(HS模式)的数据传送速度,该标准受到人们的关注。另外,人们还制定对USB2.0的物理层电路,或逻辑层电路的接口类型进行定义的UTMI(USB2.0 Transceiver MacrocellInterface)。

另外,按照该USB2.0,除了由过去的USB1.1定义的FS(链Full Speed)模式以外,还配备有称为“HS(高速High Speed)模式的传送模式。按照该HS模式,由于以480Mbps进行数据传送,故与按照12Mbps进行数据传送的FS模式相比较,可实现更高速度的数据传送。因此,按照USB2.0,可向传送速度要求高速的硬盘驱动器,光盘驱动器等存储设备提供最适合的接口。

但是,在该HS模式的数据传送时,由于进行传送数据的取样,故具有下述问题,即必须发生480MHz的频率的时钟,发生这样的高频的时钟的电路(PLL)的耗电量非常大。另外,如果这样的电量还在低速FS模式的数据传送时消耗,故造成耗电量的浪费。

此外,在切换传送模式(HS模式,FS模式),切换待发生的时钟的场合,还具有下述课题,即必须防止数据传送控制装置或后级的电路发生误动作的情况。

发明概述

本发明是针对上述的技术课题而提出的,本发明的目的在于提供可在不产生动作不良的情况下,动态地对待发生的时钟的频率进行切换的数据传送控制装置,以及电子设备。

另外,本发明的另一目的在于提供可以较低的耗电量,实现不同传送模式的数据传送的数据传送控制装置和电子设备。

为了解决上述课题,本发明涉及一种数据传送控制装置,该数据传送控制装置用于通过总线进行数据传送,其特征在于其包括时钟发生装置,该时钟发生装置发生包括第一,第二时钟的多个时钟;时钟控制装置,该时钟控制装置对通过上述时钟发生装置中的时钟发生进行控制,根据通过上述时钟发生装置发生的时钟,发生数据传送控制装置和后级的数据处理装置中的至少一个所采用的系统时钟,上述时钟控制装置在不执行上述时钟发生装置的第一时钟的发生动作之前,实现上述时钟发生装置的第二时钟的发生动作,在判定第二时钟发生动作稳定后,将用于发生系统时钟的时钟,从第一时钟切换到第二时钟。

按照本发明,根据时钟发生装置发生的第一,第二时钟,发生数据传送控制装置内部,或后级的数据处理装置所采用的系统时钟。另外,按照本发明,在不执行时钟发生装置的第一时钟的发生动作之前,实现第二时钟的发生动作。接着,如果判定实现的第二时钟的发生动作保持稳定,则构成系统时钟的发生元的时钟从第一时钟,切换到第二时钟,可根据第二时钟,发生系统时钟,以代替第一时钟。

按照上述方式,在形成系统时钟的发生元的时钟的切换时,可确保从时钟发生装置,稳定地输出第一时钟。另外,形成系统时钟的发生元的时钟可从第二时钟,切换为上述稳定的第一时钟。因此,即使在时钟切换时,仍可将稳定的系统时钟,供给数据传送控制装置内部,或后级的数据处理装置,防止产生误动作等。

另外,如果在时钟切换后,不执行第一时钟的发生动作,则可节省第一时钟的发生动作所消耗的电量,使数据传送控制装置节省电力。

此外,本发明还可这样形成,即上述时钟发生装置包括用于发生第一时钟的第一PLL以及用于发生第二时钟的第二PLL,上述时钟控制装置在不执行上述第一PLL的自由振荡动作之前,实现上述第二PLL的自由振荡动作,在判定上述第二PLL的自由振荡动作稳定后,将用于发生系统时钟的时钟,从第一时钟切换到第二时钟。

按照上述方式,如果可将稳定的系统时钟,供给数据传送控制装置内部,或后级的数据处理装置,并且在时钟的切换后,不执行第一PLL的自由振荡动作,则可节省第一PLL所消耗的电量。

还有,本发明还可这样形成,即上述时钟控制装置在将用于发生系统时钟的时钟,从第一时钟切换到第二时钟时,仅仅在规定期间,将系统时钟设定在第一电平。

按照此方式,可防止通过切换处于不稳定的状态的时钟,作为系统时钟,供给数据传送控制装置内部,或后级的数据处理装置。另外,即使在第一,第二时钟的相位错开的情况下,适当地使它们接合成为一种可能,可防止数据传送控制装置,或后级的数据处理装置的误动作。

此外,将系统时钟设定在第一电平的处理、比如,可在时钟切换的规定期间,获得形成第一电平的掩蔽信号与第一或第二时钟的逻辑积等。

再有,本发明可这样形成,即将系统时钟设定在第一电平的上述规定期间,根据上述时钟发生装置中的时钟发生用的基准时钟设定。

按照上述方式,根据处于在时钟切换时稳定的信号状态的基准时钟,设定时钟的切换期间的长度等。因此可进一步使供给数据传送控制装置,或后级的数据处理装置的系统时钟保持稳定。

另外,本发明也可这样形成,即上述时钟控制装置以第一时钟变为第一电平为条件,将根据第一时钟而发生的系统时钟设定在第一电平,以第二时钟变为第一电平为条件,根据第二时钟,发生系统时钟。

按照此方式,在时钟切换时,第一时钟从第二电平,变化到第一电平后,在比如,从第一电平变化到第二电平之前,可将系统时钟固定在第一电平。由此,在时钟切换时,可有效地防止系统时钟产生频率突增(glitch)的情况。另外,第二时钟从第二电平变为第一电平后,比如,在第一电平变为第二电平之前,可根据第二时钟,发生系统时钟。于是,还可防止时钟的脉冲幅度变窄,造成频率突增(glitch)的情况。

此外,本发明涉及一种数据传送控制装置,该数据传送控制装置用于通过总线,进行数据传送,其特征在于该装置包括时钟发生装置,该时钟发生装置发生包括第一,第二时钟的多个时钟;时钟控制装置,该时钟控制装置对上述时钟发生装置中的时钟发生进行控制,根据通过上述时钟发生装置发生的时钟,发生数据传送控制装置和后级的数据处理装置中的至少一方所采用的系统时钟,上述时钟控制装置在将用于发生系统时钟的时钟从第一时钟切换到第二时钟时,仅仅在规定期间,将系统时钟设定在第一电平。

按照本发明,根据由时钟发生装置发生的第一,第二时钟,发生数据传送控制装置内部,或后级的数据处理装置所采用的系统时钟。另外,按照本发明,在形成系统时钟的发生元的时钟的切换时,将系统时钟设定在第一电平。因此,可防止处于由时钟的切换而处于不稳定的状态的时钟,作为系统时钟供给数据传送控制装置内部,或后级的数据处理装置的情况,即使在第一,第二时钟的相位错开的情况下,仍可适当使它们接合。

还有,本发明涉及一种数据传送控制装置,该数据传送控制装置用于通过总线,进行数据传送,其特征在于该装置包括时钟发生装置,该时钟发生装置发生包括第一,第二时钟的多个时钟;时钟控制装置,该时钟控制装置对上述时钟发生装置中的时钟发生进行控制,根据通过上述时钟发生装置发生的时钟,发生数据传送控制装置和后级的数据处理装置中的至少一方所采用的系统时钟,上述时钟控制装置以第一时钟变为第一电平为条件,将根据第一时钟而发生的系统时钟设定在第一电平,以第二时钟变为第一电平为条件,根据第二时钟,发生系统时钟。

按照本发明,根据由时钟发生装置发生的第一,第二时钟,发生数据传送控制装置内部,或后级的数据处理装置所采用的系统时钟。另外,按照本发明,在形成系统时钟的发生元的时钟切换时,在将系统时钟设定在第一电平后,可将系统时钟固定在第一电平。另外,如果按照上述方式,在将系统时钟固定在第一电平后,将第二时钟从第二电平,变为第一电平,则可根据第二时钟,发生系统时钟。通过采用这样的方式,可防止系统时钟发生频率突增(glitch)的情况,可保证数据传送控制装置,或后级的数据处理装置的稳定动作。

再有,本发明涉及一种数据传送控制装置,该数据传送控制装置用于采用高速的第一传送模式,或低速的第二传送模式,借助总线,进行数据传送,其特征在于该装置包括时钟发生装置,该时钟发生装置包括发生第一时钟的第一PLL和发生第二时钟的第二PLL;时钟控制装置,该时钟控制装置对上述时钟发生装置所包括的第一,第二PLL进行控制,上述时钟控制装置在传送模式从上述高速的第一传送模式,切换到上述低速的第二传送模式的场合,不执行发生上述第一传送模式用的第一时钟的第一PLL的自由振荡动作。

按照本发明,在高速的第一传送模式,可根据由第一PLL发生的第一时钟,进行,比如,数据传送或系统时钟的发生等。另外,如果从第一传送模式切换到低速的第二传送模式,则不执行第一PLL的自由振荡动作。因此,在第二传送模式,由于不需要的第一PLL在第二传送模式时不动作,故防止在第一PLL,耗电量浪费的情况,使数据传送装置实现省电。

另外,本发明还可这样形成,即在按照通过上述第一PLL发生的第一时钟动作的状态,对与总线连接的端口是否支持第一传送模式进行检测,在检测到不支持第一传送模式的场合,根据来自后级的数据处理装置的选择信号,不执行上述第一PLL的自由振荡动作。

按照此方式,在数据传送控制装置通过总线,与不支持第一传送模式的端口连接,按照第二传送模式动作的场合,可防止在第一PLL中,耗电量的浪费,实现数据传送控制装置的省电。

此外,本发明还可这样形成,即上述时钟控制装置在不执行上述第一PLL的自由振荡动作之前,实现上述第二PLL的自由振荡动作,在判定上述第二PLL的自由振荡动作保持稳定后,不执行上述第一PLL的自由振荡动作。

按照此方式,在切换使用来自第一PLL的第一时钟和来自第二PLL的第二时钟时,可采用稳定地输出的时钟,可保证数据传送控制装置的稳定动作。

另外,本发明还可进行符合USB的标准的数据传送。

按照该方式,比如,符合USB2.0标准的HS模式的数据传送等也有望实现。

此外,按照本发明,在从HS模式向FS模式的切换时,从FS模式向HS模式切换时,能够保证数据传送控制装置的稳定动作。

再有,本发明的电子设备还可包括上述任何一种数据传送控制装置,以及下述处理装置,该处理装置进行通过上述数据传送控制装置和上述总线传送的数据输出处理,获取处理,或存储处理装置等。

按照本发明,由于降低用于电子设备的数据传送控制装置的成本,使可靠性提高,故还使电子设备的成本降低,可靠性提高。另外,按照本发明,由于可通过高速的传送模式,进行数据传送,故可实现电子设备的的高速处理。

再有,按照本发明,由于可采用与传送数据相对应的适合的时钟,故还实现电子设备的省电。

附图简述

图1为表示本实施例的数据传送控制装置的结构实例的图;

图2为表示时针发生电路、时钟控制电路的结构实例的图;

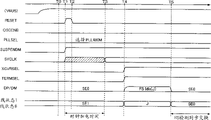

图3为用于对本实施例的动作进行说明的时序图;

图4为用于对本实施例的动作进行说明的时序图;

图5为用于对本实施例的动作进行说明的时序图;

图6为用于对本实施例的动作进行说明的状态变化图;

图7为用于对本实施例的动作进行说明的状态变化图;

图8为用于对本实施例的动作进行说明的状态变化图;

图9为表示PLL480M的结构实例的图;

图10为表示PLL480M所包含的VCO的结构实例的图;

图11为表示PLL60M的结构实例的图;

图12为表示PLL60M所包含的VCO的结构实例的图;

图13A,图13B为表示PLL60M所包含的VCO的结构实例的图;

图14为device attach的时序图;

图15为HS同步交换时的时序图;

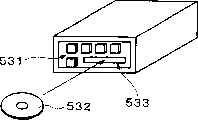

图16A,图16B,图16C为各种电子设备的内部方框图的实例;

图17A,图17B,图17C为各种电子设备的外观图的实例。

发明详述

下面参照附图,对本发明的优选实施例进行具体描述。

1.结构和动作

1.1数据传送控制装置

图1表示本实施例的数据传送控制装置的结构的实例。

本实施例的数据传送控制装置包括数据处理电路400,HS(高速HighSpeed)电路410,FS(全速Full Speed)电路420,模拟前端电路430,时钟发生电路440,时钟控制电路450。另外,本发明的数据传送控制装置不必包括图1所示的全部方框,其也可为省略这些方框中的一部分的结构。

数据处理电路400(从广义上说,用于传送数据的规定的电路)进行用于符合USB等的数据传送的各种处理。更具体地说,在发送信号时,对发送数据,进行附加SYNC(同步化,synchronization),SOP(数据分组的开始,Startof Packet),EOP(数据分组的结束,End of Packet)的处理,位填充处理等。在接收信号时,进行检测/删除接收数据的SYNC,SOP,EOP的处理,位填充处理等。在接收信号时,进行检测/删除接收数据的SYNC、SOP、EOP的处理,位非填充处理等。另外,还进行发生用于控制数据的发送接收信号的各种定时的处理。

另外,接收数据从数据处理电路400,输出给后级的电路(后级的数据处理装置)的SIE(串行接口引擎,Serial Interface Engine),上述发送数据从SIE,输入到数据处理电路400中。

HS电路410为用于进行数据传送速度为480Mbps的HS的数据的发送接收的逻辑电路,FS电路420为用于进行数据传送速度为12Mbps的FS的数据的发送接收的逻辑电路。

在这里,HS模式是由USB2.0新定义的传送模式。FS模式是按照过去的USB1.1定义的传送模式。

按照USB2.0,由于配备这样的HS模式,故不仅可实现打印机,音响,照相机等的数据传送,还可实现硬盘驱动器或光盘驱动器(CDROM,DVD)等的存储装置的数据传送。

HS电路410包括HSDLL(高速延迟线PLL,High Speed Delay Line PLL)电路10,缓冲存储器(elasticity buffer)12。

在这里,HSDLL电路10是根据来自接收数据和时钟发生电路440(PLL)的时钟,发生数据的取样时钟的电路。

另外,缓冲存储器12为用于吸收内部装置(数据传送控制装置)与外部装置(与总线连接的外部装置)的时钟频率差(时钟偏移)等的电路。

模拟前端电路430为包括用于进行FS或HS的信号发送接收的驱动器或接收器的模拟电路。按照USB,通过采用DP(Data+)与DM(Data-)的差动信号,发送接收数据。

时钟发生电路440发生在装置内部使用的480MHz的时钟,或在装置内部及SIE使用的60MHz的时钟。

时钟发生电路440包括OSC、PLL480M、PLL60M。

在这里,OSC(振荡电路)是通过与外部振荡器的组合,发生基准时钟。

PLL480M指下述PLL(锁相环),其发生HS模式所必需的480MHz的时钟,FS模式,装置内部和SIE所必需的60Mz的时钟。另外,在按照HS模式进行信号发送接收的场合,必须使该PLL480M的时钟发生有效。

PLL60M根据由OSC(振荡电路)发生的基准时钟,发生FS模式、装置内部和SIE所必需的60MHz的时钟。另外,在使该PLL60M的时钟发生有效时,不可进行HS模式的信号发送接收。

时钟控制电路450接收来自SIE的各种控制信号,进行控制时钟发生电路440的处理等。另外,由时钟发生电路440发生的60MHz的系统时钟通过时钟控制电路450,输出给SIE。

1.2时钟发生电路、时钟控制电路的结构

图2表示本实施例的时钟发生电路440(时钟发生装置),时钟控制电路450(时钟控制装置)的结构实例。

时钟发生电路440所包含的OSC(振荡电路)通过与XIN,XOUT连接的外部振荡器,进行振荡动作,发生基准时钟RCLK(比如,12~24MHz)。另外,将该基准时钟RCLK输出给PLL480M,PLL60M,时钟控制电路450。

另外,还可将输入到XIN中的外部时钟直接用作基准时钟。

此外,OSCENB为用于设定OSC的振荡和来自XI的外部时钟的输入的有效,非有效的信号。比如,如果OSCENB=“0”(逻辑电平。下面相同),则OSC的振荡和外部时钟的输入是非有效的,如果为“1”,则是有效的。比如,在通过SUSPENDM,装置处于中止状态时,如果使OSCEN为“0”,则可切换到OSC也不动作的完全中止模式。

时钟发生电路440所包括的PLL480M在来自时钟控制电路450的信号ENB480M为“1”的条件下,发生其相位与基准时钟RCLK相同的480MHz的时钟。另外,将通过对该480MHz的时钟进行分频而获得的60MHz的时钟作为CLKH,将其输出给时钟控制电路450。另外,还可在时钟控制电路450一侧,进行480MHz的时钟的分频。

时钟发生电路440所包含的PLL60M在来自时钟控制电路450的信号ENB60M为“1”的条件下,发生其相位与基准时钟RCLK相同的60MHz的时钟。另外,将该60MHz的时钟作为CLKF,将其输出给时钟控制电路450。

时钟控制电路450从SIE,接收信号SUSPENDM,PLLSEL,对时钟发生电路440中的时钟发生动作(PLL480M,PLL60M的自由振荡动作)进行控制。另外,根据由时钟发生电路440发生的时钟CLKH,CLKF,发生并输出数据传送控制装置内部或SIE(后级的数据处理装置)所采用系统时钟SYCLK(同步用的参考时钟)。

另外,信号SUSPENDM为用于对数据传送控制装置(无线电收发机装置)进行中止的信号,如果SUSPENDM为“0”,使数据传送控制装置中止,则OSC(振荡电路)以外的全部电路停止。

此外,信号PLLSEL为SIE选择使PLL480M与PLL60M中的哪个自由振荡动作用的信号,在PLLSEL为“0”时,选择PLL480M,在为“1”时,选择PLL60M。另外,在HS模式时,在线性调制脉冲(CHIRP)发送接收的场合,必须使PLLSEL为“0”,选择PLL480M。

1.2动作

下面通过图3的时序图,对本实施例的动作进行描述。

如果在图3的时刻T0,PLLSEL为“0”,则选择发生480MHz的时钟的PLL480M。另外,如果在时刻T1,SUSPENDM为“1”,解除中止,则ENB480M为“1”,无法实现PLL480M的自由振荡动作(时钟发生动作)。

还有,开始基于来自OSC的基准时钟RCLK(或对RCLK进行分频的时钟)的计数动作,如果在时刻T3,计数动作结束,STABLE480M为“1”。即,在假定PLL480M的自由振荡动作稳定的时刻(假定发生按照USB2.0的标准所要求的480MHz+/-500ppm的时钟的时刻)),STABLE480M为“1”。

于是,信号SYCLKENB(SYCLK的掩蔽信号)为“1”,在来自PLL480M的CLKH(对480MHz进行分频处理后的60MHz的时钟)发生的系统时钟SYCLK(相同的60MHz的时钟)可供给数据传送控制装置内部和SIE(后级的数据处理装置)。

另外,在图3中,为了测定时刻T1~T3的期间(PLL480M的自由振荡动作的稳定所要求的期间),进行基于来自振荡电路OSC的基准时钟RCLK的计数动作。该RCLK为在图2的信号OSCENB为“1”,振荡电路OSC的振荡动作稳定的场合,在其以后保持稳定的时钟。因此,可采用RCLK,稳定地测定T1~T3的期间。

如果在时刻T4,PLLSEL为“1”,则选择发生60MHz的时钟的PLL60M,ENB60M为“1”,实现PLL60M的自由振荡动作(时钟发生动作)。

接着,开始基于基准时钟RCLK的计数动作,如果在时刻T6,计数动作结束,则STABLE60M(表示PLL60M的自由振荡动作稳定的信号)为“1”,进行采用作为系统时钟SYCLK的掩蔽信号的SYCLKENB的时钟切换。更具体地说,在时钟切换之前,根据来自PLL480M的CLKH而发生的系统时钟SYCLK在时钟切换后,根据来自PLL60M的CLKF而发生,可将其供给数据传送控制装置内部和SIE。

在本实施例中,如图3中的AI所示的那样,不实现(结束)PLL480M的自由振荡动作(时钟发生动作)之前,如A2所示的那样,实现(开始)PLL60M的自由振荡动作。接着,如A3所示的那样,在判定PLL60M的自由振荡动作稳定后,如图4所示的那样,将用于发生系统时钟SYCLK的时钟从CLKH(PLL480M)切换到CLKF(PLL60M)。

按照上述方式,如图3中的A4所示、在时钟切换时,保证稳定地输出来自PLL60M的时钟CLKF(参照A3)。接着,形成系统时钟SYCLK的发生源的时钟从时钟CLKH,切换到该稳定的时钟CLKF。因此,如图3中的A4所示、即使在进行时钟切换的情况下,仍可将平时稳定的系统时钟SYCLK,供给数据传送控制装置或SIE,可防止该数据传送控制装置或SIE发生误动作的情况。

还有,如果进行这样的时钟(PLL)的切换,如图3中的A1所示,不实现PLL480M的自由振荡动作,此后,PLL480M不动作,仅仅PLL60M动作。因此,可使PLL480M的消电量几乎为零,可大幅度降低数据传送控制装置整体的耗电量。

即,按照高速的HS模式,PLL480M动作,在来自PLL480M的CLKH中,发生SYCLK,按照低速FS模式,PLL480M的动作停止,在来自PLL60M的CLKF中,发生SYCLK。因此,在FS模式中,PLL480M不动作。在FS模式中,防止耗电量的浪费,可大幅度降低FS模式的耗电量。

比如,在本实施例的比较实例,可考虑下述的方案,其中在时钟发生电路中,设置PLL480M,在FS模式时,对来自该PLL480M的时钟进行分频处理,形成系统时钟SYCLK。

但是,在该比较实例中,由于同样在FS模式时,PLL480M进行动作,在FS模式,消电量浪费,不能够减小FS模式的耗电量。

与此相对,按照本实施例,在FS模式,PLL480M不动作,仅仅耗电量很少的PLL60M动作,与上述比较实例相比较,可进一步减小FS模式的耗电量。

1.3时钟切换时的系统时钟的掩蔽

图4,图5表示用于说明时钟切换时(图3的时刻T4~T7)的本实施例的动作的具体的时序图。

如果在图4的时刻T4,PLLSEL为“1”,ENB60M为“1”,则不实现PLL60M的振荡动作。另外,如果在时刻T5,PLL60M的振荡动作从非稳定状态(斜线部分),到稳定状态,在时刻T6,基于时钟RCLK的计数动作结束,如图4中的B1所示,在RCLK的顶缘,计数结束信号COVER为“1”。由此,如B2所示,信号STABLE480M从“1”,变为“0”。

接着,如图4中的B3所示的那样,在RCLK的下一顶缘,信号DCOVER为“1”。由此,如B4所示,信号STABLE60M从“0”,变为“1”。

然后,通过取这些信号STABLF480M,STABLE60M的逻辑和,象图4中的B5所示,在时钟的切换期间,发生形成“0”(第一电平)的信号SYCLKENB。另外,通过该信号SYCLKENB,掩蔽系统时钟SYCLK(取SYCLKENB与SYCLK的逻辑积),如B6所示,SYCLK可仅仅在规定的期间TM设定在“0”(第一电平。也可为“1”)。

按照此方式,在本实施例中,在将用于形成系统时钟SYCLK的时钟从CLKH(PLL480M),切换到CLKF(PLL60M)时,仅仅在期间TM,SYCLK设定为“0”。于是,通过从CLKH向CLKF的切换,形成不稳定的状态的时钟,作为SYCLK,不供给数据传送控制装置或SIE(后级的数据处理装置)。另外,即使在CLKH的相位与CLKF的相位错开的情况下,仍可良好地使这些相位接合。其结果是,可有效地防止SYCLK所发生的频率突增(glitch)(细胡须状的脉冲)等构成原因的数据传送装置或SIE误动作的情况。

还有,在本实施例中,系统时钟SYCLK设定为“0”的期间TM,根据PLL480M或PLL60M的时钟发生用的基准时钟RCLK(比如,12~24MHz)而设定。即,期间TM为图4中的B1,B3所示的RCLK的边缘间的间距(RCLK的单位时钟的长度)。因此,根据即使在时钟切换时,仍处于稳定的信号状态的基准时钟RCLK,可设定时钟的切换期间TM的长度。另外,在时钟切换时,CLKH或CLKF可确实采用信号SYCLKENB,进行掩蔽。

1.4频率突增(glitch)发生的防止

在本实施例中,为了确实防止时钟切换时的频率突增的发生,采用下面描述的方式。

即,如图5中的CI所示,计数结束信号COVER方“1”,则寻求来自PLL480M的CLKH变为“0”的情况(等待变为“0”)。另外,以CLKH变为“0”(第一电平)为条件(在CLKH的底边),如图5中的C2所示,将掩蔽信号SYCLKENB设定为“0”,将根据SYCLKENB与CLKH的逻辑积而发生的系统时钟SYCLK固定在“0”电平。

按照此方式,在系统时钟SYCLK如图5中的C3所示,从“1”变为“0”后,在从“0”变为“1”之前,可使SYCLK固定在“0”电平。即,通过SYCLKENB的“0”电平,将C4所示的CLKH的时钟脉冲进行掩蔽,可确实防止在SYCLK中,发生“1”的电平的频率突增。

还有,在上述实施例中,如图5中的C5所示,重叠计算(count over)信号COVER滞后RCLK的1个时钟的信号DCOVER方“1”,则寻求来自PLL60M的CLKF为“0”的情况(等待变为“0”)。另外,以CLKF变为“0”(第一电平)为条件(在CLKF的底边),如图5中的C6所示,将掩蔽信号SYCLKENB设定为“1”,可根据SYCLKENB与CLKF的逻辑积而发生系统时钟SYCLK。

按照上述方式,系统时钟SYCLK,如图5中的C7所示,从“0”变为“1”之前,将信号SYCLKENB的“0”电平的掩蔽解除,CLKF可作为SYCLK输出。因此,可确实防止C8所示的SYCLK的时钟脉冲变细,造成频率突增。

如果按照上述方式采用本实施例,可确实防止在时钟的切换期间TM,产生频率突增。于是,可防止该频率突增造成的,数据传送控制装置,或SIE所包括的D双稳态电路保持误产生的数据的情况,可保证装置稳定的动作。

另外,象上述那样描述的图3,图4,图5中,给出了时钟从CLKH(PLL480M),向CLKF(PLL60M)切换时的时刻波形实例,但是时钟从CLKF(PLL60M),到CLKH(PLL480M)的切换也可按照与图3,图4,图5相同的时刻变形进行。

1.5时钟控制电路的具体动作

图6,图7,图8表示用于说明图2的时钟控制电路450的具体动作的状态变化图。

在装置的电源接通后,在完全停止的状态等待时(状态S0),如果信号SUSPENDM为“1”,则进行初始化处理(状态S1)。接着,在信号PLLSEL为“0”的场合,信号ENB480M为“1”(状态S2。图3中的T1),实现PLL480M的自由振荡动作。

接着,开设基准时钟RCLK的计数动作(状态S3),如果为重叠计算,则寻求来自PLL480M的时钟CLKH变为“0”的情况(状态S4)。然后,以时钟CLKH变为“0”为条件,将CLKH作为系统时钟输出(状态S5),转换到通常动作状态S6。按照上述方式,如果以CLKH变为“0”为条件,将CLKH作为SYCLK输出,则可有效地防止在SYCLK中产生频率突增(glitch)。

在于状态S1,信号PLLSEL为“1”的场合,信号ENB60M为1(状态S7),实现PLL60M的自由振荡动作。

接着,开始基准时钟RCLK的计算动作(状态S8),如果为重叠计算(countover),则寻求来自PLL60M的时钟CLKF变为“0”的情况(状态S9)。另外,以CLKF变为“0”为条件,将CLKF作为系统时钟SYCLK输出(状态S10),转换到通常动作状态S6。

如果在通常动作状态S6,信号SUSPENDM变为“0”,则寻求系统时钟SYCLK变为“0”的情况(状态S11),另外,如果SYCLK变为“0”,则停止SYCLK的输出(状态S12),则将信号ENB480M,ENB60M设定为“0”(状态S13),转换到完全停止状态S0。

另外,如果在通常动作状态S6,信号PLLSEL从“0”切换到“1”,则信号ENB60M设定为“1”(图7的状态S20)。于是,开始基准时钟RCLK的计算动作(状态S21),如果为重叠计算(count over),则寻求来自PLL480M的时钟动作CLKH变为“0”的情况(状态S22。图5的C1)。另外,如果CLKH为“0”,则采用掩蔽信号SYCLKENB,停止SYCLK的输出(状态S23。图5中的C2)。

接着,寻求来自PLL60M的时钟CLKF变为“0”的情况(状态S24。图5的C5)。另外,如果CLKF变为“0”,则将信号SYCLKENB设定为“1”(图5中的C6),将CLKF作为系统时钟SYCLK输出(状态S25),转移到图6所示的通常动作的状态S6。

如果象图7中的状态S22~S25那样,进行时钟切换,则在从CLKH向CLKF进行时钟切换时,可有效地防止系统时钟SYCLK发生频率突增。

如果在图6的通常动作状态S6,PLLSEL从“1”切换到“0”,则将信号ENB480M设定为“1”(图8的状态S30)。于是,开始基准时钟RCLK的计数动作(状态S31),如果为重叠计算,则寻求来自PLL60M的时钟CLKF变为“0”的情况(状态S32)。另外,如果CLKF变为“0”,则采用掩蔽信号SYCLKENB,停止SYCLK的输出(状态S33)。

然后,寻求来自PLL480M的时钟CLKF变为“0”的情况(状态S34)。另外,如果CLKH变为“0”,则将信号SYCLKENB设定在“1”,将CLKH作为系统时钟SYCLK输出(状态S35),转移到图6所示的正通动作的状态S6。

如果象图8中的S32~S35那样,进行时钟切换,则在从CLKF,向CLKH进行时钟切换时,可有效地防止系统时钟SYCLK发生频率突增。

1.6 PLL480M,PLL60M的具体实例

图9表示PLL480M的具体的结构实例。

PLL480M包括相位比较器80,供给泵电路82,滤波电路84,VCO(压控振荡器)86,分频器88等。

在这里,相位比较器80对基准时钟RCLK(比如,12~24MHz)与来自分频器88的时钟DCLK4的相位进行比较,输出相位误差信号PUP、PDW(PUP指相位前进信号,PDW指相位滞后信号)。

供给泵电路82根据来自相位比较器80的PUP、PDW,进行供给泵动作。更具体地说,如果PUP为有源的,则进行对滤波电路84所包括的电容器进行充电的动作,如果PDW为有源的,则进行对电容器进行放电的动作。另外,将通过滤波电路84进行平滑处理的控制电压VC供给VCO86。

VCO86对应于控制电压VC,进行以可改变的方式对其振荡频率进行控制的振荡动作,发生480MHz的时钟QCLK0~4。比如,如果控制电压VC增加,则振荡频率也增加,如果控制电压VC降低,则振荡频率也降低。

由VCO86发生的时钟QCLK0~4通过缓冲器BF00~04、BF10~14,作为CLK0~4,向外部输出。另外,BF20~23为用于与BF24的负载保持一致的虚(dummy)的缓冲器。

分频器88通过缓冲器BF04,BF24,对从VCO86输入的时钟QCLK4进行分频处理(1/N),将分频后的时钟DCLK4输出给相位比较器80。

按照图9方案的PLL480M,则可发生其相位与基准时钟RCLK同步的高频的480MHz的时钟CLK4。另外,已发生的时钟CLK4通过图中未显示出的分频器进行分频处理,作为60MHz的CLKH,输出给图2的时钟控制电路450。

图10表示图9的VCO86的结构实例。

该VCO86包括与5级(从广义上说,为奇数级)的串联的差动输出比较器DCP0~4(倒相电路),各DCP0~4的差动输出端子Q,XQ,输入给单端输出比较器SCP0~4的差动输入端子。另外,SCP0~4的输出变为VCO86的输出时钟QCLK0~4。另外,如果控制电压VC变化,则流过差动输出比较器DCP0~4的电流源的电流变化,振荡频率变化。

图11表示PLL60M的具体结构实例。

该PLL60M包括分频器89,相位比较器90,供给泵电路92,滤波电路94,VCO96,分频器97,98等。

在这里,相位比较器90对来自分频器89的时钟DRCLK(对基准时钟RCLK进行分频处理后的时钟)和来自分频器98的时钟DCLKF的相位进行比较,输出相位误差信号PUP,PDW。

供给泵电路92根据来自相位比较器90的PUP,PDW,进行供给泵动作。更具体地说,如果PUP是有源的,则进行对滤波电路94所包括的电容器充电的动作,如果PDW是有源的,则进行对电容器放电的动作。另外,将通过滤波电路94进行平滑处理的控制电压VC供给VCO96。

VCO96根据控制电压VC,进行以可变方式对其振荡频率进行控制的振荡动作,发生120MHz的时钟QCLK。

分频器97对从VCO96输入的时钟QCLK进行分频处理(1/2),将分频处理后的60MHz的时钟CLKF输出给图2的时钟控制电路450。

分频器98对从分频器97输入的时钟QCLKF进行分频处理(1/N),将分频处理后的时钟DCLKF输出给相位比较器90。

按照图11的结构的PLL60M,发生其相位与基准时钟RCLK同步的60MHz的时钟CLKF,可将其输出给图2的时钟控制电路450。

图12表示图11的VCO96的结构实例。

该VCO96包括与3级的串联差动输出比较器DCP10~12(倒相电路)。另外,最后一级的差动输出比较器DCP12的差动输出XQ,Q输入到单端输出比较器SCP10的差动输入端子,SCP10的输出变为VCO96的输出时钟QCLK连接。如果控制电压VC变化,则流过差动输出比较器DCP10~12的电流源的电流变化,振荡频率改变。

图13A表示图10,图12的VCO所包括的差动输出比较器(差动放大器)的结构实例。该差动输出比较器包括N型晶体管NT1,NT2,其中差动输入端子I,XI与栅极电极连接,差动输出端子XQ,Q与漏极连接;P型晶体管PT1,PT2,其中差动输出端子Q与栅极连接,差动输出端子XQ,Q与漏极连接;N型晶体管NT3(电流源),其中控制电压VC与栅极连接。

另外,在图12的VCO96(120MHz振荡)中,差动输出比较器DCP10~12,或单端输出比较器SCP10所包括的晶体管的大小等适合用于120MHz(60MHz)的振荡。因此,与图10的VCO86(480MHz振荡)相比较,图12的VCO96的耗电量进一步减小。由此,包括图10的VCO86的PLL480M的消耗电流相对比如,约为33mA的,非常大的值的情况,包括图12的VCO96的PLL60M的消耗电流比如,为1.5mA的,非常小的值。

因此,在于HS模式时采用PLL480M发生时钟,在FS模式时,停止PLL480M的动作,如果仅仅采用PLL60M发生时钟,则可使PLL的消耗电流比如,约为1/22倍,使数据传送控制装置实现节电。

此外,对于图9、图11的PLL480M、PLL60M,也可采用不设置供给泵电路82、92的方案。另外,还可设置电流控制的振荡装置,以代替VCO86、96。

还有,包含在VCO86、96中的倒相电路不限于图13所示的差动输出比较器,可按照各种变换形式实施。比如,在图13B所示的倒相电路中,P型晶体管PT4、PT5,N型晶体管T4、NT5串联。另外,流过这些晶体管的电流通过与PT4、NT5的栅极连接的控制电压VCQ、VC控制,以可改变的方式对振荡频率进行控制。

1.7时钟的切换时刻

下面对USB2.0的时钟的适合切换时刻进行描述。

图14为本实施例的数据传送控制装置(电子设备)与总线连接时(接入设备)的时序图的实例。

在接入设备时,本实施例的数据传送控制装置按照HS模式开始动作。由此,信号PLLSEL设定为“0”(选择PLL480M)。另外,信号XCVRSEL(在为“0”时,HS无线电收发机有效,在为“1”时,FS无线电收发机有效的信号),信号TERMSEL(在为“0”时,HS终端有效,在为“1”时,FS终端(termination)有效的信号)均设定为“0”。

如果图14的时刻T0,判定VBUS是有效的,则在时刻T1,把SIE认定(assert)为信号RESET,并且取消信号SUSPENDM。另外,在接入设备时,由于将PLLSEL设定为“0”,选择PLL480M,故在时刻T1,实现PLL480M的自由振荡动作。

接着,在时刻T2,取消信号RESET,在时刻T3,可输出PLL480M保持稳定的时钟CLKH。另外,将根据该CLKH而发生的系统时钟SYCLK供给SIE。

然后,在时刻T4,信号XCVRSEL,TERMSEL为“1”,FS无线电收发机和FS终端(termination)有效。接着,在时刻T5,从后级的的端口,发出复位信号(reset)(SEO),开始HS检测的同步交换。

图15为本实施例的数据传送控制装置与不支持HS模式的端口连接的场合的,HS检测同步交换的时序图的实例。

在图15的时刻T0,开始HS检测同步交换。另外,在时刻T1,信号XCVRSEL为“0”,HS无线电收发机是有效的。然后,开始线性调频脉冲(K)的发送。另外,在该线性调频脉冲(K)发送时,不实现位填充(BS)处理和NRZI处理,输出由“0”隐埋数据。

在时刻T2,结束线性调频脉冲(K)的发送。另外,后级的端口支持HS模式的场合,从时刻T3起,开始线性调频脉冲(K)的发送。但是,在时刻T4,由于未检测线性调频脉冲,故在该时刻,本实施例的数据传送控制装置返回到FS模式,等待复位(reset)程序结束。另外,在时刻T6,复位(reset)程序结束,在时刻T4,转换到FS模式的通常动作。

按照此方式,如果处于时刻T4,则传送模式确定为FS模式。另外,由于在时刻T4和T6之间,处于FS模式的复位(reset)状态,故也不发送接收信息包。于是,在本实施例中,如图15所示,在时刻T4和T6之间的时刻T5,SIE将信号PLLSEL设定为“1”,不进行PLL480M的自由振荡动作,并且实现PLL60M的自由振荡动作。于是,进行图3所述的时钟切换,形成系统时钟SYCLK的发生元的时钟从PLL480M的时钟CLKH,切换到PLL60M的时钟CLKF。

按照此方式,在本实施例中,在于来自PLL480M的时钟CLKH动作的状态,检测与总线连接的端口是否支持HS模式(第一传送模式)。

另外,在检测到与总线连接的端口不支持HS模式的场合,根据来自SIE(后级的数据处理装置)的信号PLLSEL(选择信号),不执行PLL480M的自由振荡动作。由此,在此以后,按照来自PLL60M的时钟CLKF,数据传送控制装置和SIE可动作。接着,由于不执行PLL480M的自由振荡动作,故可防止在该PLL480M中,消电量的浪费,使数据传送控制装置节电。

另外,作为时钟从PLL60M的CLKF,切换到PLL480M的CLKH的场合,可将其视为下述场合,在该场合,在按照FS模式动作的状态,将本实施例的数据传送控制装置与总线脱开,此后,将上述装置与连接有HS模式的端口的总线连接。

2.电子设备

下面对包括本实施例的数据传送控制装置的电子设备的实例进行描述。

比如,图16A表示作为电子设备的打印机的内部方框图,图17A表示其外观图。CPU(微型计算机)510进行系统整体的控制等处理。操作部511是用户对打印机进行操作用的部分。在ROM516中,存储有控制程序、字体(font)等,RAM517用作CPU510的工作区域。DMAC518为不通过CPU510进行数据传送用的DMA控制器。显示面板519是用于使用户了解打印机的动作状态的部分。

通过USB,从个人计算机等的其它装置传送来的串行的打印数据,通过数据传送控制装置500,转换为并行的打印数据。另外,转换后的并行打印数据通过CPU510或DMA518,发送给打印处理部(打印机)512。此外,在打印处理部512,对并行打印数据,进行规定的处理,由打印头等形成的打印部(进行数据的输出处理的装置)514,对纸进行打印,实现输出。

图16B表示电子设备中的一个的扫描仪的内部方框图,图17B表示其外观图。CPU520进行系统整体的控制等处理。操作部521是用户对扫描仪进行操作的部分。在ROM526中,存储控制程序等,RAM527用作CPU520的工作区域。DMAC528为DMA控制器。

通过由光源,光电转换器等形成的图象读取部(进行数据的获取处理的装置)522,读取原稿的图象,经读取的图象的数据通过图象处理部(扫描仪)524处理。接着,处理后的图象数据通过CPU520,或DMAC528,发送给数据传送控制装置500。数据传送控制装置500将该并行的图象数据,转换为串行数据,通过USB,发送给个人计算机等的其它装置。

图16C表示电子设备中的一个的CD-RW驱动器的内部方框图,图17C表示其外观图。CPU530进行系统整体的控制等的处理。操作部531是用户对CD-RW进行操作用的部分。在ROM536中,存储控制程序等,RAM537用作CPU530的工作区域。DMAC538为DMA控制器。

通过由激光器、马达、光线系统等形成的读取写入部(进行数据的获取处理的装置或数据的存储处理用的装置)533,从CD-RW532读取的数据输入到信号处理部534中,进行错误订正处理等的规定信号处理。接着,进行了信号处理的数据通过CPU530或DMAC538,传送给数据传送控制装置500。该数据传送控制装置500将该并行的数据转换为串行数据,通过USB,发送给个人计算机等的其它装置。

通过USB,从其它的装置传送来的串行的数据通过该数据传送控制装置500,转换为并行的数据。另外,该并行的数据通过CPU530或DMAC538,传送给信号处理部534。接着,在该信号处理部534,对该并行数据进行规定的信号处理,通过读取和写入部533,将其存储于CD-RW532中。

还有,在图16A、图16B、图16C中,除了CPU510、520、530以外,还可单独设置数据传送控制装置500中的数据传送控制用的CPU。

如果本实施例的数据传送控制装置用于电子设备,则可进行USB2.0的HS模式的数据传送。于是,在用户通过个人计算机,进行打印输出指示时,在时间滞后很少的情况下,完成打印。另外,在扫描仪的图象获取指示后,用户可在很少时间滞后的情况下,看到读取图象。此外,可高速地进行来自CD-RW的数据的读取,CD-RW的数据的写入。

再有,如果本实施例的数据传送控制装置用于电子设备,则按照与和总线连接的其它电子设备的传送模式(HS模式、FS模式)相对应的适合的时钟,可使数据传送控制装置,或电子设备动作。由此,实现电子设备的省电。此外,由于可防止在时钟切换时,产生动作不良的情况,可提高电子设备的动作稳定性、可靠性。

此外,作为可采用本实施例的数据传送控制装置的电子设备,除了上述装置以外,还可考虑比如,各种光盘驱动器(CD-ROM、DVD),光磁盘驱动器(MO)、硬盘驱动器,TV、VTR、摄像机,音响设备,电话机,投影机,个人计算机,电子笔记本,文字处理器等的各种装置。

另外,本发明不限于本实施例,可在本发明的主要内容的范围内,按照各种变换方式实施。

比如,本发明的数据传送控制装置的结构不限于图1所示的结构。

此外,时钟发生装置,时钟控制装置的结构,动作也不限于图2~7所描述的类型,其可按照各种变形方式实施。

还有,第一,第二PLL(PLL480M、PLL60M)的结构也不限于图9~13B所描述的形式。比如,也可在第一、第二PLL之间,共同采用第一、第二PLL的振荡装置(VCO86、96)以外的时钟(相位比较装置、供给泵装置、滤波装置或分频装置等)的一部分或全部。按照此方式,可使包括第一、第二PLL的时钟发生装置的规模减小。

再有,本发明特别是最好用于USB2.0的数据传送,但是并不限制于此场合,比如,本发明还可适合于比如,基于与USB2.0相同构思的标准,或对USB2.0进行了发展了的标准的数据传送。

Claims (13)

1.一种数据传送控制装置,该数据传送控制装置用于通过总线进行数据传送,其特征在于其包括:

时钟发生装置,该时钟发生装置发生包括第一,第二时钟的多个时钟;

时钟控制装置,该时钟控制装置对上述时钟发生装置中的时钟发生进行控制,根据上述时钟发生装置发生的时钟,发生数据传送控制装置和后级的数据处理装置中的至少一个所采用的系统时钟;

上述时钟控制装置在不执行上述时钟发生装置的第一时钟的发生动作之前,实现上述时钟发生装置的第二时钟的发生动作,在判定第二时钟发生动作稳定后,将用于发生系统时钟的时钟,从第一时钟切换到第二时钟。

2.根据权利要求1所述的数据传送控制装置,其特征在于:

上述时钟发生装置包括用于发生第一时钟的第一锁相环以及用于发生第二时钟的第二锁相环;

上述时钟控制装置在不执行上述第一锁相环的自由振荡动作之前,实现上述第二锁相环的自由振荡动作,在判定上述第二锁相环的自由振荡动作稳定后,将用于发生系统时钟的时钟,从第一时钟切换到第二时钟。

3.根据权利要求1所述的数据传送控制装置,其特征在于:

上述时钟控制装置在将用于发生系统时钟的时钟,从第一时钟切换到第二时钟时,仅仅在规定期间,将系统时钟设定在第一电平。

4.根据权利要求3所述的数据传送控制装置,其特征在于:

上述时钟发生装置具有第一时钟发生装置和第二时钟发生装置,根据输入到第一时钟发生装置和第二时钟发生装置的基准时钟,来设定将系统时钟设定在第一电平的上述规定期间。

5.根据权利要求1所述的数据传送控制装置,其特征在于:

上述时钟控制装置以第一时钟变为第一电平为条件,将根据第一时钟而发生的系统时钟设定在第一电平,以第二时钟变为第一电平为条件,根据第二时钟,发生系统时钟。

6.一种数据传送控制装置,该数据传送控制装置用于通过总线,进行数据传送,其特征在于该装置包括:

时钟发生装置,该时钟发生装置发生包括第一,第二时钟的多个时钟;

时钟控制装置,该时钟控制装置对上述时钟发生装置中的时钟发生进行控制,根据上述时钟发生装置发生的时钟,发生数据传送控制装置和后级的数据处理装置中的至少一个所采用的系统时钟;

上述时钟控制装置在将用于发生系统时钟的时钟从第一时钟切换到第二时钟时,仅仅在规定期间,将系统时钟设定在第一电平。

7.根据权利要求6所述的数据传送控制装置,其特征在于:

上述时钟发生装置具有第一时钟发生装置和第二时钟发生装置,根据输入到第一时钟发生装置和第二时钟发生装置的基准时钟,来设定将系统时钟设定在第一电平的上述规定期间。

8.一种数据传送控制装置,该数据传送控制装置用于通过总线,进行数据传送,其特征在于该装置包括:

时钟发生装置,该时钟发生装置发生包括第一,第二时钟的多个时钟;

时钟控制装置,该时钟控制装置对上述时钟发生装置中的时钟发生进行控制,根据上述时钟发生装置发生的时钟,发生数据传送控制装置和后级的数据处理装置中的至少一个所采用的系统时钟;

上述时钟控制装置以第一时钟变为第一电平为条件,将根据第一时钟而发生的系统时钟设定在第一电平,以第二时钟变为第一电平为条件,根据第二时钟,发生系统时钟。

9.一种数据传送控制装置,该数据传送控制装置用于采用高速的第一传送模式,或低速的第二传送模式,借助总线,进行数据传送,其特征在于该装置包括:

时钟发生装置,该时钟发生装置包括发生第一时钟的第一锁相环和发生第二时钟的第二锁相环;

时钟控制装置,该时钟控制装置对上述时钟发生装置所包括的第一,第二锁相环进行控制;

上述时钟控制装置在传送模式从上述高速的第一传送模式,切换到上述低速的第二传送模式的场合,不执行发生上述第一传送模式用的第一时钟的第一锁相环的自由振荡动作。

10.根据权利要求9所述的数据传送控制装置,其特征在于在按照通过上述第一锁相环发生的第一时钟动作的状态,对与总线连接的端口是否支持第一传送模式进行检测,在检测到不支持第一传送模式的场合,根据来自后级的数据处理装置的选择信号,不执行上述第一锁相环的自由振荡动作。

11.根据权利要求9所述的数据传送控制装置,其特征在于上述时钟控制装置在不执行上述第一的自由振荡动作之前,实现上述第二锁相环的自由振荡动作,在判定上述第二锁相环的自由振荡动作保持稳定后,不执行上述第一锁相环的自由振荡动作。

12.根据权利要求1、6、8或9所述的数据传送控制装置,其特征在于进行符合USB的标准的数据传送。

13.一种电子设备,其特征在于:包括

权利要求1~12中的任何一项所述的数据传送控制装置;

对通过上述数据传送控制装置以及上述总线传送的数据进行输出处理、获取处理或存储处理的装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000332493A JP3587162B2 (ja) | 2000-10-31 | 2000-10-31 | データ転送制御装置及び電子機器 |

| JP332493/2000 | 2000-10-31 | ||

| JP332493/00 | 2000-10-31 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1363891A CN1363891A (zh) | 2002-08-14 |

| CN1172249C true CN1172249C (zh) | 2004-10-20 |

Family

ID=18808692

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB011448423A Expired - Fee Related CN1172249C (zh) | 2000-10-31 | 2001-10-31 | 数据传送控制装置和电子设备 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7047434B2 (zh) |

| EP (1) | EP1202151A3 (zh) |

| JP (1) | JP3587162B2 (zh) |

| KR (1) | KR100430908B1 (zh) |

| CN (1) | CN1172249C (zh) |

| TW (1) | TW563025B (zh) |

Families Citing this family (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100907394B1 (ko) * | 2002-07-15 | 2009-07-10 | 매그나칩 반도체 유한회사 | 동기식 회로의 클럭 발생 장치 |

| US7278047B2 (en) * | 2002-10-14 | 2007-10-02 | Lexmark International, Inc. | Providing different clock frequencies for different interfaces of a device |

| US7131023B2 (en) * | 2003-05-30 | 2006-10-31 | Lucent Technologies Inc. | Programmable clock management component reconfiguration upon receipt of one or more control signals to be able to process one or more frequency signals |

| JPWO2004109676A1 (ja) * | 2003-06-05 | 2006-07-20 | 富士通株式会社 | 情報記録再生装置および方法 |

| JP4812066B2 (ja) | 2003-10-09 | 2011-11-09 | ルネサスエレクトロニクス株式会社 | 半導体集積回路 |

| JP4345471B2 (ja) | 2003-12-18 | 2009-10-14 | セイコーエプソン株式会社 | 物理層回路、データ転送制御装置、及び電子機器 |

| CN100361040C (zh) * | 2004-02-24 | 2008-01-09 | 中国科学院计算技术研究所 | 一种soc架构下的处理器核动态变频装置和方法 |

| KR100990484B1 (ko) * | 2004-03-29 | 2010-10-29 | 삼성전자주식회사 | 직렬 버스 통신을 위한 송신 클럭 신호 발생기 |

| US7630395B2 (en) * | 2004-05-24 | 2009-12-08 | The United States Of America As Represented By The Secretary Of The Air Force | Apparatus and method for providing a data interface to a plurality of radio transceivers |

| CN1306428C (zh) * | 2004-07-13 | 2007-03-21 | 海信集团有限公司 | 通信网络中移动台的高速程序下载系统及其方法 |

| TW200832916A (en) * | 2007-01-23 | 2008-08-01 | Holtek Semiconductor Inc | Clock generating circuit and method thereof |

| ITMI20070997A1 (it) * | 2007-05-17 | 2008-11-18 | Incard Sa | Ic card con clock a bassa precisione |

| KR101174768B1 (ko) * | 2007-12-31 | 2012-08-17 | 엘지디스플레이 주식회사 | 평판 표시 장치의 데이터 인터페이스 장치 및 방법 |

| JP2010015318A (ja) * | 2008-07-02 | 2010-01-21 | Toshiba Corp | Usbホストコントローラ、情報処理装置及びプログラム |

| US8266486B2 (en) * | 2008-08-21 | 2012-09-11 | Texas Instruments Incorporated | Preventing erroneous operation in a system which may enable unsupported features |

| JP2011049877A (ja) * | 2009-08-27 | 2011-03-10 | Fujitsu Semiconductor Ltd | クロック信号制御回路及びクロック信号制御方法 |

| CN102571080A (zh) * | 2010-12-27 | 2012-07-11 | 北京中电华大电子设计有限责任公司 | 一种支持动态校准的时钟恢复方法和电路 |

| JP5739727B2 (ja) * | 2011-05-27 | 2015-06-24 | ルネサスエレクトロニクス株式会社 | クロック発生回路 |

| US9503103B2 (en) | 2012-04-30 | 2016-11-22 | Taiwan Semiconductor Manufacturing Company, Ltd. | Phase locked loop with a frequency multiplier and method of configuring the phase locked loop |

| CN103378855B (zh) * | 2012-04-30 | 2016-09-14 | 台湾积体电路制造股份有限公司 | 具有倍频器的锁相环及构造锁相环的方法 |

| CN103414468B (zh) * | 2013-06-25 | 2016-08-31 | 广州思信电子科技有限公司 | 锁相环系统 |

| US9509318B2 (en) * | 2015-03-13 | 2016-11-29 | Qualcomm Incorporated | Apparatuses, methods, and systems for glitch-free clock switching |

| CN105406984B (zh) * | 2015-10-22 | 2019-05-31 | 上海斐讯数据通信技术有限公司 | 一种实现主备倒换背板时钟的系统及方法 |

| TWI781134B (zh) | 2017-01-25 | 2022-10-21 | 日商精工愛普生股份有限公司 | 電路裝置、電子機器及束線器 |

| TWI599889B (zh) * | 2017-03-14 | 2017-09-21 | 芯籟半導體股份有限公司 | 自動產生時脈的通用序列匯流排控制器及其使用方法 |

| CN107273327B (zh) * | 2017-05-11 | 2021-06-01 | 建荣集成电路科技(珠海)有限公司 | 可变速率串行通信方法、装置、通信芯片、存储装置及系统 |

| JP6897307B2 (ja) | 2017-05-19 | 2021-06-30 | セイコーエプソン株式会社 | 回路装置、電子機器、ケーブルハーネス及びデータ転送方法 |

| JP7069931B2 (ja) | 2018-03-27 | 2022-05-18 | セイコーエプソン株式会社 | 回路装置、電子機器及びケーブルハーネス |

| JP2019175308A (ja) | 2018-03-29 | 2019-10-10 | セイコーエプソン株式会社 | 回路装置、電子機器及びケーブルハーネス |

| JP2019175309A (ja) | 2018-03-29 | 2019-10-10 | セイコーエプソン株式会社 | 回路装置、電子機器及びケーブルハーネス |

| CN110568905A (zh) * | 2019-08-09 | 2019-12-13 | 苏州浪潮智能科技有限公司 | 一种硬盘背板、信号处理方法及介质 |

| CN114564099B (zh) * | 2022-01-20 | 2024-06-04 | 珠海亿智电子科技有限公司 | 一种降低usb传输功耗的方法及电子装置 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0778696B2 (ja) | 1988-10-31 | 1995-08-23 | 富士通株式会社 | クロック切り替え制御方式 |

| US5095280A (en) | 1990-11-26 | 1992-03-10 | Integrated Circuit Systems, Inc. | Dual dot clock signal generator |

| US6219797B1 (en) * | 1993-02-09 | 2001-04-17 | Dallas Semiconductor Corporation | Microcontroller with selectable oscillator source |

| JPH07123001A (ja) | 1993-10-28 | 1995-05-12 | Hitachi Ltd | クロック信号供給回路 |

| JPH0830351A (ja) | 1994-07-11 | 1996-02-02 | Hitachi Ltd | マイクロプロセッサ |

| US5774701A (en) | 1995-07-10 | 1998-06-30 | Hitachi, Ltd. | Microprocessor operating at high and low clok frequencies |

| US5790609A (en) * | 1996-11-04 | 1998-08-04 | Texas Instruments Incorporated | Apparatus for cleanly switching between various clock sources in a data processing system |

| US5838205A (en) | 1997-02-18 | 1998-11-17 | International Business Machines Corporation | Variable-speed phase-locked loop system with on-the-fly switching and method therefor |

| US5844435A (en) * | 1997-03-11 | 1998-12-01 | Lucent Technologies Inc | Low power, high accuracy clock circuit and method for integrated circuits |

| JP3176313B2 (ja) | 1997-04-01 | 2001-06-18 | 埼玉日本電気株式会社 | Pllシンセサイザ回路 |

| US6275546B1 (en) | 1998-06-30 | 2001-08-14 | Hewlett-Packard Company | Glitchless clock switch circuit |

| KR100578112B1 (ko) | 1998-10-16 | 2006-07-25 | 삼성전자주식회사 | 메모리 클럭 신호를 제어하는 컴퓨터 시스템 및그 방법 |

| US6157265A (en) * | 1998-10-30 | 2000-12-05 | Fairchild Semiconductor Corporation | Programmable multi-scheme clocking circuit |

| JP2000183894A (ja) | 1998-12-11 | 2000-06-30 | Toshiba Corp | 伝送制御装置 |

| KR100553674B1 (ko) | 1999-03-26 | 2006-02-24 | 삼성전자주식회사 | 피씨아이 버스 클럭주파수의 개별적 제어 장치 |

| JP2000293257A (ja) | 1999-04-07 | 2000-10-20 | Sanyo Electric Co Ltd | マイクロコンピュータ |

| JP2001051747A (ja) * | 1999-08-12 | 2001-02-23 | Fujitsu Ltd | クロック制御回路 |

| US6618456B1 (en) * | 1999-10-21 | 2003-09-09 | Semtech Corporation | Asynchronous timing oscillator re-synchronizer and method |

| US6587954B1 (en) * | 1999-11-24 | 2003-07-01 | Advanced Micro Devices, Inc. | Method and interface for clock switching |

| JP3551907B2 (ja) | 2000-09-11 | 2004-08-11 | セイコーエプソン株式会社 | クロック信号供給装置およびその制御方法 |

| US6452426B1 (en) * | 2001-04-16 | 2002-09-17 | Nagesh Tamarapalli | Circuit for switching between multiple clocks |

-

2000

- 2000-10-31 JP JP2000332493A patent/JP3587162B2/ja not_active Expired - Fee Related

-

2001

- 2001-10-29 US US09/984,218 patent/US7047434B2/en not_active Expired - Lifetime

- 2001-10-30 TW TW090126937A patent/TW563025B/zh not_active IP Right Cessation

- 2001-10-30 KR KR10-2001-0067003A patent/KR100430908B1/ko not_active IP Right Cessation

- 2001-10-31 EP EP01125404A patent/EP1202151A3/en not_active Withdrawn

- 2001-10-31 CN CNB011448423A patent/CN1172249C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN1363891A (zh) | 2002-08-14 |

| US7047434B2 (en) | 2006-05-16 |

| US20020062457A1 (en) | 2002-05-23 |

| EP1202151A2 (en) | 2002-05-02 |

| TW563025B (en) | 2003-11-21 |

| JP2002141911A (ja) | 2002-05-17 |

| JP3587162B2 (ja) | 2004-11-10 |

| KR100430908B1 (ko) | 2004-05-10 |

| EP1202151A3 (en) | 2003-05-21 |

| KR20020034912A (ko) | 2002-05-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1172249C (zh) | 数据传送控制装置和电子设备 | |

| CN1165850C (zh) | 采样时钟生成电路、数据传送控制装置和电子设备 | |

| CN1228721C (zh) | 集成电路装置、电子装置 | |

| CN1201242C (zh) | 数据传送控制装置和电子装置 | |

| CN1287256C (zh) | 电子设备与功率控制方法 | |

| CN1402495A (zh) | 电源控制电路、电子仪器、及其充电方法 | |

| CN1220142C (zh) | 存储控制装置以及大规模集成电路 | |

| CN1354425A (zh) | 串行/并行转换电路、数据传送控制装置和电子设备 | |

| CN1114267C (zh) | 由时钟信号控制的电平转换电路 | |

| CN1771662A (zh) | 数据传输控制装置及电子设备 | |

| CN1551592A (zh) | 数据传输控制装置、电子设备及数据传输控制方法 | |

| EP2299681B1 (en) | Image forming apparatus and power control method thereof | |

| CN1819926A (zh) | 电源装置及通信系统 | |

| CN1941170A (zh) | 延迟锁定环路电路 | |

| CN1725234A (zh) | 数据处理装置、数据处理方法和便携式通信终端装置 | |

| CN1190742C (zh) | 发送电路、数据传输控制装置及电子机器 | |

| CN1292121A (zh) | 数据传输控制装置及电子设备 | |

| CN1213372C (zh) | 数据传送控制装置、电子机器及数据传送控制方法 | |

| CN1237718C (zh) | 振荡器电路及其控制方法和配备有该电路的器件和存储器件 | |

| CN1146801C (zh) | 数据传送控制装置和电子装置 | |

| CN1266840C (zh) | 分别具备时钟生成电路和时钟延迟电路的信息处理装置 | |

| CN1421993A (zh) | 时钟产生电路和时钟产生方法 | |

| CN100351733C (zh) | 以低功率动作的时钟控制的时序电路及其电路变更方法 | |

| CN1138213C (zh) | 微型计算机 | |

| CN1260655C (zh) | 数据的锁存时刻调整装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20041020 Termination date: 20181031 |