JP3551907B2 - クロック信号供給装置およびその制御方法 - Google Patents

クロック信号供給装置およびその制御方法 Download PDFInfo

- Publication number

- JP3551907B2 JP3551907B2 JP2000275489A JP2000275489A JP3551907B2 JP 3551907 B2 JP3551907 B2 JP 3551907B2 JP 2000275489 A JP2000275489 A JP 2000275489A JP 2000275489 A JP2000275489 A JP 2000275489A JP 3551907 B2 JP3551907 B2 JP 3551907B2

- Authority

- JP

- Japan

- Prior art keywords

- clock signal

- signal

- unit

- control

- operation clock

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

本発明は、例えば、基準クロック信号および動作クロック信号によって駆動されるツインクロック方式のマイクロコンピュータに用いて好適なクロック信号供給装置およびその制御方法に関する。

【0002】

【従来の技術】

携帯電話、ページャ、コードレス電話等の移動体通信機器、ワープロ、複写器、ファックス等のOA機器、パーソナルコンピュータ、このパソコンの周辺機器等のOA機器、テレビ、ビデオ、エアコン等の電化製品、さらにこれらの製品をリモコン制御するリモコン装置等には、時計機能あるいはタイマ機能を具備したものがあり、これらの機器にはツインクロック方式のマイクロコンピュータが搭載されている。

【0003】

例えば、これらの機器の一例としては、離れた主装置(例えば、テレビ)の動作をリモコン信号によって制御するリモコン装置があり、このリモコン装置には液晶パネルと赤外線発信部とが設けられている。

リモコン装置に搭載されたマイクロコンピュータは、基準クロック信号(例えば、32.768kHz)によって駆動される時刻&カレンダ機能と、動作クロック信号(例えば、4MHz)によって駆動されるリモコン信号処理機能とを備えている。また、マイクロコンピュータの入力側には操作スイッチ、出力側には液晶パネルを制御駆動する液晶表示用ドライバ、赤外線発信部からリモコン信号を発信させるリモコン信号用ドライバ等が接続されている。

そして、マイクロコンピュータは、ユーザが操作スイッチを操作していない待機状態にあっては、基準クロック信号を受けて液晶パネル上に月日および時刻を表示させ、操作スイッチを操作した動作状態にあっては、動作クロック信号を受けて赤外線発信部から赤外線によるリモコン信号を主装置に向けて発信させるものである。

【0004】

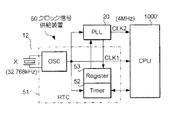

ここで、図9および図10を参照しつつ、マイクロコンピュータを駆動するクロック発振器の接続状態について、2つの例を挙げて説明する。

図9は、ツインクロック方式のマイクロコンピュータ(以下、CPUユニット1000という)に基準クロック発振器110および動作クロック発振器120を接続したものである。

【0005】

このCPUユニット1000には、基準クロック発振器110からの基準クロック信号を受けて駆動される時刻&カレンダ機能と、動作クロック発振器120からの動作クロック信号を受けて装置自体を動作させる機能(例えば、リモコン信号処理機能)とを備えている。

基準クロック発振器110は、例えば32.768kHzの周波数を有する基準クロック信号を発生させるもので、音叉型水晶振動子等からなる振動子X1と、この振動子X1から安定した信号を取り出すための発振回路OSC1とを具備している。

動作クロック発振器120は、例えば4MHzの周波数を有する動作クロック信号を発生させるもので、AT(厚みすべり)型水晶振動子あるいは圧電セラミック振動子等からなる振動子X2と、この振動子X2から安定した信号を取り出すための発振回路OSC2とを具備している。そして、発振回路OSC2は、CPUユニット1000からの指令信号に基づいてON/OFF制御されるものである。

【0006】

そして、CPUユニット1000は、装置自体の機能を動作させていない待機状態にあっては、このCPUユニット1000からはOFFの指令信号が発振回路OSC2に向けて出力され、動作クロック発振器120から動作クロック信号がCPUユニット1000に供給されるのを停止する。これにより、CPUユニット1000は、基準クロック発振器110からの基準クロック信号のみを受け、この基準クロック信号に基づいて時刻&カレンダ機能のみを動作させる。

この際、前述した如く、CPUユニット1000に液晶表示ドライバおよび液晶パネルを接続した場合には、この液晶パネルに月日および時刻を表示させる。

【0007】

一方、装置自体の機能を動作させる動作状態にあっては、CPUユニット1000からはONの指令信号が発振回路OSC2に向けて出力され、動作クロック発振器120から動作クロック信号が供給される。これにより、CPUユニット1000は、この動作クロック信号を受けて、装置自体の機能動作(例えば、リモコン信号の発信動作)を行わせる。

【0008】

また、図10は、他の従来技術を示したものである。この従来技術では、基準クロック発振器110に代えて、RTC(Real Time Clock)を有する基準クロック発振器130をツインクロック方式のCPUユニット1000´に接続したものである。

【0009】

この基準クロック発振器130は、振動子X1、発振回路OSC1および時刻&カレンダ機能を有するRTCとして構成されている。そして、時刻&カレンダ機能は、低周波クロックによって時刻およびカレンダを常に計時し、CPUユニット1000´からの指令信号に基づき、これらの情報を選択的にCPUユニット1000´に供給するものである。

ここで、基準クロック発振器130はRTCとして構成されているため、CPUユニット1000´には基準クロック信号に基づいて動作される時刻&カレンダ機能を備える必要がない。

【0010】

【発明が解決しようとする課題】

ところで、動作クロック発振器120を構成する振動子X2には、高周波の動作クロック信号を生成させるため、AT(厚みすべり)型水晶振動子あるいは圧電セラミック振動子等が採用されている。これらの振動子は機械的な振動で振動子X1よりもはるかに高い周波数で振動するため、動作クロック発振器120の消費電流が数mAとなる。

一方、基準クロック発振器110,130を構成する振動子X1には、音叉型水晶振動子等が採用され、その消費電流が数μAとなる。

これらの従来技術のように、CPUユニットに対して周波数の高い動作クロック信号を生成する動作クロック発振器120を接続した場合には、その消費電流が大きくなってしまう、という問題があった。

【0011】

本発明は、以上の問題に鑑みてなされたものであり、比較的低い周波数のクロック信号を発生する1つの発振源を用いて、2つの異なった周波数のクロック信号を低消費電力で発生させることのできるクロック信号供給装置およびその制御方法を提供することを目的としている。

【0012】

【課題を解決するための手段】

上記課題を解決するため、請求項1記載の発明は、基準クロック信号および動作クロック信号を外部の処理ユニットに供給するクロック信号供給装置であって

、

一定の周波数の基準クロック信号を発生する発振源と、

前記基準クロック信号と比較信号との位相を比較して位相差検出信号を出力する位相比較部と、前記位相差検出信号を直流に変換して制御信号を生成する制御信号生成部と、前記制御信号に応じた周波数の前記動作クロック信号を発生する電圧制御発振部と、前記動作クロック信号を逓倍あるいは分周して前記比較信号を生成する比較信号生成部と、を具備した周波数シンセサイザ手段と、

前記動作クロック信号の周波数がロック状態であるときに、ロック信号を出力するロック判定手段と、

前記処理ユニットに対して前記動作クロック信号の供給を行う動作クロック信号出力手段と、

前記位相比較部、制御信号生成部、比較信号生成部およびロック判定手段を駆動させる第1駆動手段と、前記第1駆動手段による駆動の後、前記動作クロック信号の周波数が「+」となる側に前記制御信号生成部をチャージし、前記電圧制御発振部を駆動させる第2駆動手段と、前記第2駆動手段による駆動の後、前記ロック判定手段からロック信号が出力されたとき、前記動作クロック信号出力手段を駆動させる第3駆動手段と、を具備し、前記周波数シンセサイザ手段を制御すると共に、前記ロック信号に基づいて前記動作クロック信号出力手段を制御する制御手段と、を備えた

ことを特徴としている。

【0014】

請求項2記載の発明は、基準クロック信号または動作クロック信号を外部の処理ユニットに選択的に供給するクロック信号供給装置であって、

一定の周波数の基準クロック信号を発生する発振源と、

前記基準クロック信号と比較信号との位相を比較して位相差検出信号を出力する位相比較部と、前記位相差検出信号を直流に変換して制御信号を生成する制御信号生成部と、前記制御信号に応じた周波数の前記動作クロック信号を発生する電圧制御発振部と、前記動作クロック信号を逓倍あるいは分周して前記比較信号を生成する比較信号生成部と、を具備した周波数シンセサイザ手段と、

前記動作クロック信号の周波数がロック状態であるときに、ロック信号を出力するロック判定手段と、

前記処理ユニットに対して前記動作クロック信号の供給を行う動作クロック信号出力手段と、

前記基準クロック信号または動作クロック信号出力手段を介して供給される前記動作クロック信号を選択出力する選択出力手段と、

前記位相比較部、制御信号生成部、比較信号生成部およびロック判定手段を駆動させる第1駆動手段と、前記第1駆動手段による駆動の後、前記動作クロック信号の周波数が「+」となる側に前記制御信号生成部をチャージし、前記電圧制御発振部を駆動させる第2駆動手段と、前記第2駆動手段による駆動の後、前記ロック判定手段からロック信号が出力されたとき、前記動作クロック信号出力手段を駆動させる第3駆動手段と、を具備し、前記周波数シンセサイザ手段の制御、前記ロック信号に基づいた前記動作クロック信号出力手段の制御を行うと共に、前記処理ユニットからの指令信号に基づいた前記選択出力手段の制御を行う制御手段と、を備えた

ことを特徴としている。

【0019】

請求項3記載の発明は、請求項1または2記載のクロック信号供給装置において、

前記ロック判定手段は、制御信号生成部から出力される制御信号が所定範囲にあるか否かに基づいて前記動作クロック信号のロック状態を判定する

ことを特徴としている。

【0020】

請求項4記載の発明は、請求項1または2記載のクロック信号供給装置において、

前記制御手段を基準クロック信号によって時計動作またはカレンダ動作の少なくともいずれかを計時するRTC(Real Time Clock)回路内に設けた

ことを特徴としている。

【0021】

請求項5記載の発明は、請求項1または2記載のクロック信号供給装置において、

前記制御手段を前記基準クロック信号によって計時する動作を行うRTC(Real Time Clock)回路内に設けた

ことを特徴としている。

【0022】

請求項6記載の発明は、請求項1または2記載のクロック信号供給装置において、

前記発振源は、圧電振動子と、この圧電振動子から安定した信号を取り出すための発振回路とを備えた

ことを特徴としている。

【0023】

請求項7記載の発明は、請求項6記載のクロック信号供給装置において、

前記圧電振動子は、音叉型水晶振動子である

ことを特徴としている。

【0024】

請求項8記載の発明は、請求項1または2記載のクロック信号供給装置において、

前記周波数シンセサイザ手段は、その設定値を変えることにより周波数の異なる前記動作クロック信号を発生可能な手段であり、前記制御手段は複数の前記設定値から所定の周波数で発振するための設定値を前記周波数シンセサイザ手段に設定する設定手段を備えている

ことを特徴としている。

【0025】

請求項9記載の発明は、一定の周波数の基準クロック信号を発生する発振源と、前記基準クロック信号を逓倍あるいは分周して前記動作クロック信号を生成する周波数シンセサイザ回路と、前記動作クロック信号の周波数がロック状態であるときに、ロック信号を出力するロック判定回路と、前記処理ユニットに対して前記動作クロック信号の供給を行う動作クロック信号出力回路と、前記周波数シンセサイザ回路を制御すると共に、前記ロック信号に基づいて前記動作クロック信号出力回路を制御する制御回路と、を備え、

前記周波数シンセサイザ回路は、入力される基準クロック信号と比較信号との位相を比較して位相差検出信号を出力する位相比較部と、前記位相差検出信号を直流に変換して制御信号を生成する制御信号生成部と、前記制御信号に応じた周波数のクロック信号を発生する電圧制御発振部と、前記クロック信号を逓倍あるいは分周して前記比較信号を生成する比較信号生成部と、を具備し、

基準クロック信号および動作クロック信号を外部の処理ユニットに供給するクロック信号供給装置の制御方法であって、

前記位相比較部、制御信号生成部、比較信号生成部およびロック判定回路を駆動させる第1駆動工程と、

前記動作クロック信号の周波数が「+」となる側に前記制御信号生成部をチャージし、前記電圧制御発振部を駆動させる第2駆動工程と、

前記ロック判定回路からロック信号が出力されたとき、前記動作クロック信号出力回路を駆動させる第3駆動工程と、を順次行う

ことを特徴としている。

【0027】

請求項10記載の発明は、一定の周波数の基準クロック信号を発生する発振源と、前記基準クロック信号を逓倍あるいは分周して動作クロック信号を生成する周波数シンセサイザ回路と、前記動作クロック信号の周波数がロック状態であるときに、ロック信号を出力するロック判定回路と、前記処理ユニットに対して前記動作クロック信号の供給を行う動作クロック信号出力回路と、前記基準クロック信号または動作クロック信号出力回路を介して供給される前記動作クロック信号を選択出力する選択出力回路と、前記周波数シンセサイザ回路の制御、前記ロック信号に基づいた前記動作クロック信号出力回路の制御を行うと共に、前記処理ユニットからの指令信号に基づいた前記選択出力回路の制御を行う制御手段と、を備え、

前記周波数シンセサイザ回路は、入力される基準クロック信号と比較信号との位相を比較して位相差検出信号を出力する位相比較部と、前記位相差検出信号を直流に変換して制御信号を生成する制御信号生成部と、前記制御信号に応じた周波数のクロック信号を発生する電圧制御発振部と、前記クロック信号を逓倍あるいは分周して前記比較信号を生成する比較信号生成部と、を具備し、

基準クロック信号または動作クロック信号を外部の処理ユニットに選択的に供給するクロック信号供給装置の制御方法であって、

前記位相比較部、制御信号生成部、比較信号生成部およびロック判定回路を駆動させる第1駆動工程と、

前記動作クロック信号の周波数が「+」となる側に前記制御信号生成部をチャージし、前記電圧制御発振部を駆動させる第2駆動工程と、

前記ロック判定回路からロック信号が出力されたとき、前記動作クロック信号出力回路を駆動させる第3駆動工程と、を順次行う

ことを特徴としている。

【0028】

請求項11記載の発明は、請求項9または10記載のクロック信号供給装置の制御方法において、

前記ロック判定回路から出力されるロック信号を監視し、当該クロック信号供給装置の動作開始から所定時間を経過しても前記ロック信号がアクティブにならない場合、当該クロック信号供給装置を故障として診断する工程を設けた

ことを特徴としている。

【0029】

請求項12記載の発明は、請求項9または10記載のクロック信号供給装置の制御方法において、

前記制御信号生成部から出力される制御信号が予め決められた所定範囲から逸脱している場合、当該クロック信号供給装置を故障として診断する工程を設けたことを特徴としている。

【0030】

【発明の実施の形態】

次に、図面を参照して本発明の好適な実施形態について説明する。

【0031】

[1] 第1実施形態

[1・1] 第1実施形態の大略構成

図1は、第1実施形態によるクロック信号供給装置10の構成を示している。このクロック信号供給装置10は、例えば、携帯電話、ページャ、コードレス電話等の移動体通信機器、ワープロ、複写器、ファックス等のOA機器、パーソナルコンピュータ、このパソコンの周辺機器等のOA機器、テレビ、ビデオ、エアコン等の電化製品、さらにこれらの製品をリモコン制御するリモコン装置等に搭載されたマイクロコンピュータを駆動させるクロックとして用いられるものである。

次に、クロック信号供給装置10の詳細について説明する。

このクロック信号供給装置10は、RTC11と、PLL(Phase Lo cked Loop)20とによって大略構成されている。

【0032】

[1・2] RTC11の構成

ここで、RTC11は、音叉型水晶振動子等からなる振動子Xおよびこの振動子Xから安定した基準クロック信号CLK1(例えば、32.768kHz)を取り出すための発振回路OSCからなる基準クロック発振器12と、この基準クロック発振器12からの基準クロック信号CLK1を受けて、時刻&カレンダを計時する時刻&カレンダ機能およびPLL20の動作を制御するPLL制御処理機能とを有するモジュール13とを備え、このモジュール13にはレジスタ14が付設されている。

【0033】

そして、基準クロック発振器12は、CPUユニット1000´に基準クロック信号CLK1を直接供給すると共に、モジュール13およびPLL20に供給する。モジュール13は、この基準クロック信号CLK1を受けて時刻&カレンダ機能を動作させる。この時刻&カレンダ機能は、基準クロック信号CLK1によって時刻およびカレンダを常に計時し、CPUユニット1000´からの指令信号に基づき、これらの情報を選択的にCPUユニット1000´に供給するものである。一方、モジュール13の持つPLL制御処理機能については、後に説明するものとする。

【0034】

[1・3] PLL20の構成

また、PLL20は、図2に示すように、モジュール13からの設定値Nを受けて所定の周波数(例えば、4MHz)の動作クロック信号CLK2を生成する周波数シンセサイザとして構成されている。

【0035】

このPLL20は、入力される基準クロック信号CLK1と比較信号との位相を比較して位相差検出信号を出力する位相比較器21と、この位相差検出信号を直流に変換して制御信号を生成するローパスフィルタ(以下、LPFという)22と、この制御信号に応じた周波数の制御クロック信号を発生する電圧制御発振回路(以下、VCOという)23と、前記制御クロック信号をモジュール12から供給される設定値Nに基づいて逓倍あるいは分周して前記比較信号を生成するプログラマブル分周器24とを具備し、さらに、このPLL20には、制御クロック信号の周波数が所定周波数範囲内にあるロック状態であるときにロック信号を出力するロック判定回路25と、制御クロック信号を動作クロック信号CLK2としてCPUユニット1000´に向けて供給するのを許可するバッファ26とが設けられている。

また、本実施形態では、位相比較器21にはチャージポンプ21Aが付設されている。

【0036】

ここで、PLL20のうち、位相比較器21、LPF22、VCO23およびプログラマブル分周器24による制御クロック信号(周波数:N×32.768kHz)の発生動作は一般的であるため、その詳細については省略するものとする。

【0037】

本実施形態によるPLL20では、このPLL20を構成する個々の回路がモジュール13から供給される駆動信号ON1、ON2、ON3によって順次駆動制御される。このため、PLL20は、位相比較器21、LPF22、プログラマブル分周器24およびロック判定回路25が第1駆動部20A、VCO23が第2駆動部20B、バッファ26が第3駆動部20Cに区分される。

【0038】

次に、モジュール13からPLL20に供給される信号について説明する。

駆動信号ON1、ON2、ON3は、その電圧値が各回路を駆動させるために必要な値VCCとなっている。

設定値Nは、プログラマブル分周器24の分周比を設定するもので、この設定値Nを変えることにより、PLL20から出力される動作クロックの周波数を多段階に設定するものである。

DF信号は、LPF22の遮断周波数f0を設定するもので、このf0はトレードオフ関係にあるロックアップタイムと周波数安定度を重視した値となる。

【0039】

[1・4] ロック判定回路25の動作

次に、ロック判定回路25のロック状態の検出動作について、図3を参照しつつ説明する。この図3は、LPF22から出力される制御信号(直流電圧)と位相差との関係を表示したものである。

即ち、制御信号の電圧が0[V]の場合には位相差が「0°」となり、この場合にはVCO23から出力される制御クロック信号が所定周波数になっている。制御信号の電圧がV+[V]の場合には位相差が「−180°」となり、制御信号の電圧がV−[V]の場合には位相差が「180°」になっている。

そして、ロック判定回路25は、LPF22から出力される制御信号の電圧値と予め決められた所定範囲(−Vx〜+Vx)とを比較することにより、VCO23から出力される制御クロック信号の周波数が所定周波数に設定されているか否かを監視するものである。

このロック判定回路25は、例えばウィンドコンパレータによって制御信号の値が所定範囲(−Vx〜+Vx)内に所定時間の間存在した場合にロック状態とし、アクティブにしたロック信号Lockをモジュール13に向けて出力する。

【0040】

[1・5] モジュール13によるPLL20の制御処理

次に、本実施形態によるモジュール13によるPLL20の制御動作について、この処理を図式化した図4の流れ図に基づいて説明する。

【0041】

▲1▼駆動信号ON1の供給

まず、モジュール13は第1駆動部20Aに駆動信号ON1を供給する(ステップS1)。これにより、位相比較器21、LPF22、プログラマブル分周器24およびロック判定回路25が駆動される。この際、VCO23が駆動していないため、プログラマブル分周器24からの比較信号は出力されず、消費電流は主として位相比較器21のチャージポンプ21Aで消費され、周波数fが「+」となる側にチャージされることになる。

【0042】

▲2▼駆動信号ON2の供給

次に、所定時間経過後にモジュール13は第2駆動部20Bに駆動信号ON2を供給する(ステップS2)。これにより、VCO23が駆動され、LPF23から出力される制御信号に基づいた周波数fを有する制御クロック信号を発生する。そして、プログラマブル分周器24では、この制御クロック信号を受けてカウントを開始する。このため、消費電流は、VCO23およびプログラマブル分周器24で増えることになる。

そして、モジュール13はタイマTをスタートさせる(ステップS3)。

【0043】

▲3▼駆動信号ON3の供給

さらに、モジュール13は、ロック判定回路25からアクティブなロック信号Lockが供給されたか否かを監視し(ステップS4)、供給されるまでこの状態(駆動信号ON1、ON2を供給した状態)を維持する(ステップS4;NO)と共に、タイマTが所定時間T0を経過したか否かを判定する(ステップS5)。

ここで、ロック信号Lockが供給された場合(ステップS4;YES)、第3駆動部20Cに駆動信号ON3を供給する(ステップS6)。これにより、バッファ26が駆動してVCO23からバッファ26に供給される制御クロック信号を動作クロック信号CLK2としてCPUユニット1000´に向けて供給する。

【0044】

一方、モジュール13は、タイマTが所定時間T0を経過してもロック信号Lockが供給されない場合には、PLL20が故障していると判断して(ステップS7)、この処理を終了する。この際、バッファ26(第3駆動部20C)に駆動信号ON3を供給するのを停止するため、動作クロック信号CLK2を供給するのを強制的に禁止する。

【0045】

[1・6] 第1実施形態の効果

このように、本実施形態によるクロック信号供給装置10は、比較的低い周波数(32.768kHz)の基準クロック信号CLK1を発生する1個の基準クロック発振器12を有するRTC11およびPLL20によって構成することにより、周波数の異なった基準クロック信号CLK1および動作クロック信号CLK2を発生する。

このRTC11およびPLL20の消費電流は、従来技術の動作クロック発振器120の消費電流に比べて小さい。このため、従来技術のように、CPUユニットを駆動するのに基準クロック発振器110および動作クロック発振器120の両方を用いた場合に比べ、本実施形態によるクロック信号供給装置10では消費電流を大幅に低減させることができる。

【0046】

また、クロック信号供給装置10では、PLL20にロック判定回路25を設けると共に、PLL20を第1駆動部20A、第2駆動部20B、第3駆動部20Cに区分してモジュール13から供給される駆動信号ON1、ON2、ON3によって順次駆動させるようにしている。これにより、クロック信号供給装置10は、VCO23から出力される制御クロック信号の周波数がロック状態になった後にバッファ26を駆動して動作クロック信号CLK2をCPUユニット1000´に供給することができ、動作クロック信号CLK2の周波数変動を抑制することができる。

【0047】

しかも、PLL20を多段階で駆動させるようにして、駆動部20A、20B、20Cを確実に動作させた上で、動作クロック信号CLK2を出力するようにしているため、PLL20の各回路を一度に駆動させて動作クロック信号CLK2の周波数を安定させる場合に比べて、動作クロック信号CLK2が安定した状態に立ち上がるまでの時間を大幅に短縮させることができる。

【0048】

さらに、基準クロック発振器12を基準クロック信号CLK1を発生させるだけでなく、動作クロック信号CLK2を発生するPLL20の発振源としても用いると共に、RTC11のモジュール13にPLLの制御処理機能を持たせてタイミング回路等を共有させるようにしたから、コスト低減を図ることができる。

【0049】

また、モジュール13によるPLLの制御処理には、図4のステップS3、S4、S5、S7に示すようなPLL20の故障判断を持たせて、クロック信号供給装置10の故障診断を行うことにより、装置の信頼性を高めることができる。

【0050】

[1・7] 第1実施形態の変形例

[1・7・1] 変形例1

第1実施形態では、ロック信号Lockがアクティブにならない時間を計測してクロック信号供給装置10の故障診断を行うようにしたが、本発明はこれに限らず、図5に示すように、予め決められた所定範囲(−Vx〜+Vx)よりも大きい第2所定範囲(−Vy〜+Vy)を設定し、この範囲(−Vy〜+Vy)よりも大きい制御信号となった場合に故障と診断するようにしてもよい。

【0051】

[1・7・2] 変形例2

第1実施形態では、PLLの制御機能を時刻&カレンダ動作を行う時刻&カレンダ機能を有するモジュール13に持たせた場合について述べたが、本発明はこれに限らず、図6に示すクロック信号供給装置50のRTC51のように、時間の計時動作を行うタイマ機能を有するモジュール52に持たせるようにしてもよい。

【0052】

[2] 第2実施形態

本実施形態によるクロック信号供給装置の特徴は、基準クロック信号CLK1または動作クロック信号CLK2を選択的に供給した点にある。なお、前述した第1実施形態と同一の構成要素に同一の符号を付し、その説明を省略するものとする。

【0053】

[2・1] 第2実施形態の大略構成

図7は、第2実施形態によるクロック信号供給装置60を示している。

このクロック信号供給装置60は、基準クロック信号CLK1を発生する基準クロック発振器12と、基準クロック信号CLK1を受けて動作クロック信号CLK2を発生するPLL61と、基準クロック信号CLK1または動作クロック信号CLK2を選択して出力する選択回路62と、この選択回路62を制御するコントローラ63とによって大略構成されている。

【0054】

[2・2] PLL61の構成

また、PLL61は、コントローラ63からの設定値Nを受けて所定の周波数(例えば、4MHz)の動作クロック信号CLK2を生成する周波数シンセサイザとして構成されている。

【0055】

このPLL61は、入力される基準クロック信号CLK1をM分周した分周信号を出力するM分周器64と、分周信号と比較信号との位相差を検出する位相比較器21と、LPF22と、VCO23と、プログラマブル分周器24とを具備し、さらに、このPLL61にはロック判定回路25が設けられている。

【0056】

そして、このPLL61は、構成する個々の回路がコントローラ63から供給される駆動信号ON1、ON2によって順次駆動制御されるため、M分周器64、位相比較器21、LPF22、プログラマブル分周器24およびロック判定回路25が第1駆動部61A、VCO23が第2駆動部61Bに区分されている。そして、これらの駆動部61A、61Bは、順に供給される駆動信号ON1、ON2によって順に駆動されることにより、動作クロック信号の立ち上がりを速めるようにしている。

【0057】

[2・3] 選択回路62

選択回路62は、基準クロック発振器12からの基準クロック信号CLK1またはPLL61からの動作クロック信号CLK2を選択して出力するもので、コントローラ63からの指示信号に基づいてクロック信号を選択出力するものである。

【0058】

[2・4] コントローラ63

コントローラ63は、その入力側にロック判定回路25およびCPUユニット(図示せず)が接続され、出力側に選択回路62が接続されている。そして、コントローラ63は、ロック判定回路25からのロック信号Lockを監視すると共に、ロック信号Lockがアクティブ状態でかつCPUユニットから動作クロック信号を要求する指令信号が供給されたときのみ、選択回路62に向けてクロック信号を動作クロック信号CLK2に切換える指示信号を出力するものである。

また、コントローラ63は、第1実施形態で述べた如く、ロック判定回路25からのロック信号Lockが所定時間経過してもアクティブにならない場合には、PLL61が故障しているとしてその旨をCPUユニットに送信する。

【0059】

[2・5] 第2実施形態の効果

このように構成されるクロック信号供給装置60においても、PLL61の2つの駆動部61A、61Bに区分して、コントローラ63からの駆動信号ON1、ON2によって順次駆動するようにしたから、前述した第1実施形態によるクロック信号供給装置10と同様の効果を奏することができる。

しかも、コントローラ63は、ロック信号Lock信号に基づいて選択回路62を制御している。このため、クロック信号供給装置60では、CPUユニットからの指令信号が動作クロック信号を要求した場合であっても、PLL61から出力される動作クロック信号がロック状態にない場合には供給するのを禁止することができる。

【0060】

[2・6] 第2実施形態の変形例

この変形例によるクロック信号供給装置60´を図8に示す。

この変形例は、PLL61´に第1実施形態で述べたバッファ26を設け、このバッファ26を第3駆動部61Cとしてコントローラ63から出力される駆動信号ON3によって駆動制御したものである。

このように、クロック供給装置60´を構成した場合であっては、動作クロック信号がロック状態になった場合にバッファ26が駆動することになり、周波数が安定した動作クロック信号を選択回路62に供給することが可能となる。

【0061】

[3] 変形例

なお、前述した各実施形態によるクロック信号供給装置では、基準クロック信号CLK1の周波数を32.768kHz、動作クロック信号CLK2の周波数を4MHzとしたが、これに限定されるものではなく。特に動作クロック信号CLK2は設定値Nによって任意に設定することが可能である。

【発明の効果】

以上に説明したように、本発明に係るクロック信号供給装置は、比較的低い周波数のクロック信号を発生する1つの発振源を用いて、2つの異なった周波数のクロック信号を低消費電力で発生させる。

【図面の簡単な説明】

【図1】第1実施形態のクロック供給装置を示すブロック図である。

【図2】同実施形態のPLLの構成を示すブロック図である。

【図3】制御信号と位相差との関係を示す図である。

【図4】同実施形態によるPLL制御処理を示す流れ図である。

【図5】第1実施形態の変形例による制御信号と位相差との関係を示す図である。

【図6】第1実施形態の変形例によるクロック供給装置を示すブロック図である。

【図7】第2実施形態のクロック供給装置を示すブロック図である。

【図8】第2実施形態の変形例によるクロック供給装置を示すブロック図である。

【図9】従来技術によるクロック発振器の接続状態を示すブロック図である。

【図10】他の従来技術によるクロック発振器の接続状態を示すブロック図である。

【符号の説明】

10、50、60、60´…クロック信号供給装置

11、51…RTC

12…基準クロック発振器

13、52…モジュール

14、53…レジスタ

20、61、61´…PLL

20A、61A…第1駆動部

20B、61B…第2駆動部

20C、61C…第3駆動部

21…位相比較器

22…LPF

23…VCO

24…プログラマブル分周器

25…ロック判定回路

26…バッファ

62…選択回路

63…コントローラ

Claims (12)

- 基準クロック信号および動作クロック信号を外部の処理ユニットに供給するクロック信号供給装置であって、

一定の周波数の基準クロック信号を発生する発振源と、

前記基準クロック信号と比較信号との位相を比較して位相差検出信号を出力する位相比較部と、前記位相差検出信号を直流に変換して制御信号を生成する制御信号生成部と、前記制御信号に応じた周波数の前記動作クロック信号を発生する電圧制御発振部と、前記動作クロック信号を逓倍あるいは分周して前記比較信号を生成する比較信号生成部と、を具備した周波数シンセサイザ手段と、

前記動作クロック信号の周波数がロック状態であるときに、ロック信号を出力するロック判定手段と、

前記処理ユニットに対して前記動作クロック信号の供給を行う動作クロック信号出力手段と、

前記位相比較部、制御信号生成部、比較信号生成部およびロック判定手段を駆動させる第1駆動手段と、前記第1駆動手段による駆動の後、前記動作クロック信号の周波数が「+」となる側に前記制御信号生成部をチャージし、前記電圧制御発振部を駆動させる第2駆動手段と、前記第2駆動手段による駆動の後、前記ロック判定手段からロック信号が出力されたとき、前記動作クロック信号出力手段を駆動させる第3駆動手段と、を具備し、前記周波数シンセサイザ手段を制御すると共に、前記ロック信号に基づいて前記動作クロック信号出力手段を制御する制御手段と、を備えた

ことを特徴とするクロック信号供給装置。 - 基準クロック信号または動作クロック信号を外部の処理ユニットに選択的に供給するクロック信号供給装置であって、

一定の周波数の基準クロック信号を発生する発振源と、

前記基準クロック信号と比較信号との位相を比較して位相差検出信号を出力する位相比較部と、前記位相差検出信号を直流に変換して制御信号を生成する制御信号生成部と、前記制御信号に応じた周波数の前記動作クロック信号を発生する電圧制御発振部と、前記動作クロック信号を逓倍あるいは分周して前記比較信号を生成する比較信号生成部と、を具備した周波数シンセサイザ手段と、

前記動作クロック信号の周波数がロック状態であるときに、ロック信号を出力するロック判定手段と、

前記処理ユニットに対して前記動作クロック信号の供給を行う動作クロック信号出力手段と、

前記基準クロック信号または動作クロック信号出力手段を介して供給される前記動作クロック信号を選択出力する選択出力手段と、

前記位相比較部、制御信号生成部、比較信号生成部およびロック判定手段を駆動させる第1駆動手段と、前記第1駆動手段による駆動の後、前記動作クロック信号の周波数が「+」となる側に前記制御信号生成部をチャージし、前記電圧制御発振部を駆動させる第2駆動手段と、前記第2駆動手段による駆動の後、前記ロック判定手段からロック信号が出力されたとき、前記動作クロック信号出力手段を駆動させる第3駆動手段と、を具備し、前記周波数シンセサイザ手段の制御、前記ロック信号に基づいた前記動作クロック信号出力手段の制御を行うと共に、前記処理ユニットからの指令信号に基づいた前記選択出力手段の制御を行う制御手段と、を備えた

ことを特徴とするクロック信号供給装置。 - 請求項1または2記載のクロック信号供給装置において、

前記ロック判定手段は、前記制御信号生成部から出力される制御信号が所定範囲にあるか否かに基づいて前記動作クロック信号のロック状態を判定する

ことを特徴とするクロック信号供給装置。 - 請求項1または2記載のクロック信号供給装置において、

前記制御手段を前記基準クロック信号によって時計動作またはカレンダ動作の少なくともいずれかを計時するRTC(Real Time Clock)回路内に設けた

ことを特徴とするクロック信号供給装置。 - 請求項1または2記載のクロック信号供給装置において、

前記制御手段を前記基準クロック信号によって計時する動作を行うRTC(Real Time Clock)回路内に設けた

ことを特徴とするクロック信号供給装置。 - 請求項1または2記載のクロック信号供給装置において、

前記発振源は、圧電振動子と、この圧電振動子から安定した信号を取り出すための発振回路とを備えた

ことを特徴とするクロック信号供給装置。 - 請求項6記載のクロック信号供給装置において、

前記圧電振動子は、音叉型水晶振動子である

ことを特徴とするクロック信号供給装置。 - 請求項1または2記載のクロック信号供給装置において、

前記周波数シンセサイザ手段は、その設定値を変えることにより周波数の異なる前記動作クロック信号を発生可能な手段であり、前記制御手段は複数の前記設定値から所定の周波数で発振するための設定値を前記周波数シンセサイザ手段に設定する設定手段を備えている

ことを特徴とするクロック信号供給装置。 - 一定の周波数の基準クロック信号を発生する発振源と、前記基準クロック信号を逓倍あるいは分周して前記動作クロック信号を生成する周波数シンセサイザ回路と、前記動作クロック信号の周波数がロック状態であるときに、ロック信号を出力するロック判定回路と、前記処理ユニットに対して前記動作クロック信号の供給を行う動作クロック信号出力回路と、前記周波数シンセサイザ回路を制御すると共に、前記ロック信号に基づいて前記動作クロック信号出力回路を制御する制御回路と、を備え、

前記周波数シンセサイザ回路は、入力される基準クロック信号と比較信号との位相を比較して位相差検出信号を出力する位相比較部と、前記位相差検出信号を直流に変換して制御信号を生成する制御信号生成部と、前記制御信号に応じた周波数のクロック信号を発生する電圧制御発振部と、前記クロック信号を逓倍あるいは分周して前記比較信号を生成する比較信号生成部と、を具備し、

基準クロック信号および動作クロック信号を外部の処理ユニットに供給するクロック信号供給装置の制御方法であって、

前記位相比較部、制御信号生成部、比較信号生成部およびロック判定回路を駆動させる第1駆動工程と、

前記動作クロック信号の周波数が「+」となる側に前記制御信号生成部をチャージし、前記電圧制御発振部を駆動させる第2駆動工程と、

前記ロック判定回路からロック信号が出力されたとき、前記動作クロック信号出力回路を駆動させる第3駆動工程と、を順次行う

ことを特徴とするクロック信号供給装置の制御方法。 - 一定の周波数の基準クロック信号を発生する発振源と、前記基準クロック信号を逓倍あるいは分周して動作クロック信号を生成する周波数シンセサイザ回路と、前記動作クロック信号の周波数がロック状態であるときに、ロック信号を出力するロック判定回路と、前記処理ユニットに対して前記動作クロック信号の供給を行う動作クロック信号出力回路と、前記基準クロック信号または動作クロック信号出力回路を介して供給される前記動作クロック信号を選択出力する選択出力回路と、前記周波数シンセサイザ回路の制御、前記ロック信号に基づいた前記動作クロック信号出力回路の制御を行うと共に、前記処理ユニットからの指令信号に基づいた前記選択出力回路の制御を行う制御手段と、を備え、

前記周波数シンセサイザ回路は、入力される基準クロック信号と比較信号との位相を比較して位相差検出信号を出力する位相比較部と、前記位相差検出信号を直流に変換して制御信号を生成する制御信号生成部と、前記制御信号に応じた周波数のクロック信号を発生する電圧制御発振部と、前記クロック信号を逓倍あるいは分周して前記比較信号を生成する比較信号生成部と、を具備し、

基準クロック信号または動作クロック信号を外部の処理ユニットに選択的に供給するクロック信号供給装置の制御方法であって、

前記位相比較部、制御信号生成部、比較信号生成部およびロック判定回路を駆動させる第1駆動工程と、

前記動作クロック信号の周波数が「+」となる側に前記制御信号生成部をチャージし、前記電圧制御発振部を駆動させる第2駆動工程と、

前記ロック判定回路からロック信号が出力されたとき、前記動作クロック信号出力回路を駆動させる第3駆動工程と、を順次行う

ことを特徴とするクロック信号供給装置の制御方法。 - 請求項9または10記載のクロック信号供給装置の制御方法において、

前記ロック判定回路から出力されるロック信号を監視し、当該クロック信号供給装置の動作開始から所定時間を経過しても前記ロック信号がアクティブにならない場合、当該クロック信号供給装置を故障として診断する工程を設けた

ことを特徴とするクロック信号供給装置の制御方法。 - 請求項9または10記載のクロック信号供給装置の制御方法において、

前記制御信号生成部から出力される制御信号が予め決められた所定範囲から逸脱している場合、当該クロック信号供給装置を故障として診断する工程を設けた

ことを特徴とするクロック信号供給装置の制御方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000275489A JP3551907B2 (ja) | 2000-09-11 | 2000-09-11 | クロック信号供給装置およびその制御方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000275489A JP3551907B2 (ja) | 2000-09-11 | 2000-09-11 | クロック信号供給装置およびその制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002091606A JP2002091606A (ja) | 2002-03-29 |

| JP3551907B2 true JP3551907B2 (ja) | 2004-08-11 |

Family

ID=18761102

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000275489A Expired - Fee Related JP3551907B2 (ja) | 2000-09-11 | 2000-09-11 | クロック信号供給装置およびその制御方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3551907B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3587162B2 (ja) | 2000-10-31 | 2004-11-10 | セイコーエプソン株式会社 | データ転送制御装置及び電子機器 |

| JP4650754B2 (ja) * | 2002-01-11 | 2011-03-16 | 有限会社ピエデック技術研究所 | 水晶ユニットの製造方法と水晶発振器の製造方法 |

| US6943639B2 (en) | 2002-06-07 | 2005-09-13 | Infineon Technologies Ag | Arrangement for low power clock generation |

| SE0201774L (sv) * | 2002-06-07 | 2003-12-08 | Ericsson Telefon Ab L M | Anordning för effektsnål klockgenerering |

| JP4618642B2 (ja) * | 2005-05-17 | 2011-01-26 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置 |

| JP2010206432A (ja) * | 2009-03-03 | 2010-09-16 | Citizen Finetech Miyota Co Ltd | 水晶発振器 |

| CN112100120A (zh) * | 2020-09-14 | 2020-12-18 | 上海艾为电子技术股份有限公司 | 一种soc芯片及其上电控制方法 |

-

2000

- 2000-09-11 JP JP2000275489A patent/JP3551907B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002091606A (ja) | 2002-03-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| USRE42293E1 (en) | System and method for optimizing clock speed generation in a computer | |

| JP3551907B2 (ja) | クロック信号供給装置およびその制御方法 | |

| TW200908562A (en) | Frequency synthesizer | |

| KR960024805A (ko) | 클럭발생회로 | |

| JP3702768B2 (ja) | クロック信号供給装置 | |

| JPH11308102A (ja) | 位相同期回路 | |

| JP2004258045A (ja) | クロック信号供給装置およびその制御方法 | |

| JP2007071654A (ja) | 振動ジャイロ | |

| JPH06187063A (ja) | 半導体装置 | |

| JP2004304253A (ja) | 発振器とこれを用いた電子機器 | |

| JP3427924B2 (ja) | バッテリ・バックアップ・クロックを駆動する方法、回路及び装置 | |

| JP2766787B2 (ja) | 超音波振動子の駆動装置 | |

| JP3838844B2 (ja) | 基準信号生成装置及びその信号生成方法 | |

| JPH05303444A (ja) | クロック信号供給装置 | |

| JP2001117546A (ja) | 表示装置 | |

| JP3458838B2 (ja) | Pll回路 | |

| JP2000050621A (ja) | 半導体集積回路用電源回路 | |

| JPH06259164A (ja) | クロック信号生成集積回路 | |

| JPH0537367A (ja) | 内部クロツク発生回路 | |

| JP3000360U (ja) | 通信機器用基準信号生成回路 | |

| JP2924846B2 (ja) | 半導体集積回路 | |

| JPH1075575A (ja) | 圧電トランスの制御回路 | |

| JP3516664B2 (ja) | 基準クロック発生装置 | |

| JPH04171516A (ja) | リセット回路 | |

| JP2001223582A (ja) | 周波数シンセサイザ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040406 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040419 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080514 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090514 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100514 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110514 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120514 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130514 Year of fee payment: 9 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140514 Year of fee payment: 10 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |