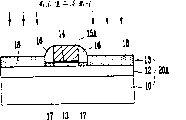

CN1050701C - 半导体器件中的晶体管及其制造方法 - Google Patents

半导体器件中的晶体管及其制造方法 Download PDFInfo

- Publication number

- CN1050701C CN1050701C CN96108211A CN96108211A CN1050701C CN 1050701 C CN1050701 C CN 1050701C CN 96108211 A CN96108211 A CN 96108211A CN 96108211 A CN96108211 A CN 96108211A CN 1050701 C CN1050701 C CN 1050701C

- Authority

- CN

- China

- Prior art keywords

- trench

- transistor

- soi layer

- liner

- soi

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0223—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate

- H10D30/0227—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate having both lightly-doped source and drain extensions and source and drain regions self-aligned to the sides of the gate, e.g. lightly-doped drain [LDD] MOSFET or double-diffused drain [DDD] MOSFET

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/021—Manufacture or treatment using multiple gate spacer layers, e.g. bilayered sidewall spacers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0135—Manufacturing their gate conductors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/40—Formation of materials, e.g. in the shape of layers or pillars of conductive or resistive materials

- H10P14/416—Formation of materials, e.g. in the shape of layers or pillars of conductive or resistive materials of highly doped semiconductor materials, e.g. polysilicon layers or amorphous silicon layers

Landscapes

- Thin Film Transistor (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019950016420A KR100227644B1 (ko) | 1995-06-20 | 1995-06-20 | 반도체 소자의 트랜지스터 제조방법 |

| KR16420/95 | 1995-06-20 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1148273A CN1148273A (zh) | 1997-04-23 |

| CN1050701C true CN1050701C (zh) | 2000-03-22 |

Family

ID=19417585

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN96108211A Expired - Fee Related CN1050701C (zh) | 1995-06-20 | 1996-06-19 | 半导体器件中的晶体管及其制造方法 |

Country Status (4)

| Country | Link |

|---|---|

| JP (1) | JPH098308A (enExample) |

| KR (1) | KR100227644B1 (enExample) |

| CN (1) | CN1050701C (enExample) |

| TW (1) | TW301034B (enExample) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3408437B2 (ja) | 1998-10-30 | 2003-05-19 | シャープ株式会社 | 半導体装置の製造方法 |

| KR100343472B1 (ko) * | 2000-08-31 | 2002-07-18 | 박종섭 | 모스 트랜지스터의 제조방법 |

| US6780686B2 (en) * | 2002-03-21 | 2004-08-24 | Advanced Micro Devices, Inc. | Doping methods for fully-depleted SOI structures, and device comprising the resulting doped regions |

| US7022575B2 (en) * | 2003-10-29 | 2006-04-04 | Sanyo Electric Co., Ltd. | Manufacturing method of semiconductor device |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0487220A2 (en) * | 1990-11-19 | 1992-05-27 | Mitsubishi Denki Kabushiki Kaisha | SOI-Field effect transistor and method of manufacturing the same |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02185068A (ja) * | 1989-01-12 | 1990-07-19 | Toshiba Corp | 電界効果型トランジスタの製造方法 |

| JPH0766972B2 (ja) * | 1989-06-22 | 1995-07-19 | 三菱電機株式会社 | 半導体装置の製造方法 |

| JPH03155166A (ja) * | 1989-11-14 | 1991-07-03 | Fuji Electric Co Ltd | 薄膜半導体素子 |

| JPH05259457A (ja) * | 1992-03-16 | 1993-10-08 | Sharp Corp | 薄膜トランジスタ |

-

1995

- 1995-06-20 KR KR1019950016420A patent/KR100227644B1/ko not_active Expired - Fee Related

-

1996

- 1996-06-06 TW TW085106813A patent/TW301034B/zh active

- 1996-06-13 JP JP8152113A patent/JPH098308A/ja active Pending

- 1996-06-19 CN CN96108211A patent/CN1050701C/zh not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0487220A2 (en) * | 1990-11-19 | 1992-05-27 | Mitsubishi Denki Kabushiki Kaisha | SOI-Field effect transistor and method of manufacturing the same |

Also Published As

| Publication number | Publication date |

|---|---|

| KR970004069A (ko) | 1997-01-29 |

| CN1148273A (zh) | 1997-04-23 |

| TW301034B (enExample) | 1997-03-21 |

| JPH098308A (ja) | 1997-01-10 |

| KR100227644B1 (ko) | 1999-11-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20020003256A1 (en) | MOS semiconductor device and method of manufacturing the same | |

| CN1050700C (zh) | 半导体器件中的晶体管及其制造方法 | |

| JPH0799310A (ja) | 電界効果型トランジスタとその製造方法 | |

| KR19980020943A (ko) | 절연막 터널링 트랜지스터 및 그 제조방법 | |

| CN1050701C (zh) | 半导体器件中的晶体管及其制造方法 | |

| US5610424A (en) | Metal oxide semiconductor field effect transistor | |

| KR100752194B1 (ko) | 반도체 소자의 제조 방법 | |

| US6551883B1 (en) | MOS device with dual gate insulators and method of forming the same | |

| CN1146048C (zh) | Cmos器件及其制造方法 | |

| JPH0936243A (ja) | 半導体装置とその製造方法 | |

| JPH0454970B2 (enExample) | ||

| KR20040081048A (ko) | 반도체 장치 및 그 제조 방법 | |

| JPH11135739A (ja) | Dramチップの改良された製造法 | |

| US6987038B2 (en) | Method for fabricating MOS field effect transistor | |

| US6440787B1 (en) | Manufacturing method of semiconductor device | |

| JP2004235527A (ja) | 絶縁ゲート型半導体装置及びその製造方法 | |

| CN1146627A (zh) | 制造半导体器件的晶体管的方法 | |

| KR20050010152A (ko) | 반도체 소자의 저전압 트랜지스터 및 그 제조방법 | |

| KR960012262B1 (ko) | 모스(mos) 트랜지스터 제조방법 | |

| KR940005292B1 (ko) | 반도체 소자 제조방법 | |

| KR100257756B1 (ko) | 모스트랜지스터 제조 방법 | |

| JP2966037B2 (ja) | 半導体装置の製造方法 | |

| JP2985845B2 (ja) | 半導体装置およびその製造方法 | |

| JPH06196643A (ja) | 半導体装置 | |

| CN121310587A (zh) | 半导体结构及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20000322 |