WO2009102060A1 - 半導体装置とその製造方法 - Google Patents

半導体装置とその製造方法 Download PDFInfo

- Publication number

- WO2009102060A1 WO2009102060A1 PCT/JP2009/052558 JP2009052558W WO2009102060A1 WO 2009102060 A1 WO2009102060 A1 WO 2009102060A1 JP 2009052558 W JP2009052558 W JP 2009052558W WO 2009102060 A1 WO2009102060 A1 WO 2009102060A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- silicon layer

- columnar

- conductivity type

- layer

- forming

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 342

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 154

- 238000000034 method Methods 0.000 title claims description 107

- 229910052751 metal Inorganic materials 0.000 claims abstract description 108

- 239000002184 metal Substances 0.000 claims abstract description 108

- 150000001875 compounds Chemical class 0.000 claims abstract description 24

- 238000011109 contamination Methods 0.000 claims abstract description 12

- 239000010410 layer Substances 0.000 claims description 705

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 483

- 229910052710 silicon Inorganic materials 0.000 claims description 483

- 239000010703 silicon Substances 0.000 claims description 483

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 98

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 98

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 93

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 93

- 238000005530 etching Methods 0.000 claims description 83

- 239000012535 impurity Substances 0.000 claims description 43

- 239000011229 interlayer Substances 0.000 claims description 43

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 41

- 229920005591 polysilicon Polymers 0.000 claims description 41

- 229910021417 amorphous silicon Inorganic materials 0.000 claims description 40

- 238000001312 dry etching Methods 0.000 claims description 39

- 238000005498 polishing Methods 0.000 claims description 34

- 238000009792 diffusion process Methods 0.000 claims description 32

- 238000001459 lithography Methods 0.000 claims description 28

- 238000002513 implantation Methods 0.000 claims description 27

- 239000000126 substance Substances 0.000 claims description 26

- 239000010949 copper Substances 0.000 claims description 25

- 230000003647 oxidation Effects 0.000 claims description 22

- 238000007254 oxidation reaction Methods 0.000 claims description 22

- 239000000758 substrate Substances 0.000 claims description 22

- 239000010936 titanium Substances 0.000 claims description 16

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 15

- 229910052802 copper Inorganic materials 0.000 claims description 15

- 238000000151 deposition Methods 0.000 claims description 13

- 230000004888 barrier function Effects 0.000 claims description 12

- 230000000149 penetrating effect Effects 0.000 claims description 11

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims description 10

- 238000012545 processing Methods 0.000 claims description 9

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 claims description 9

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 8

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 8

- 229910045601 alloy Inorganic materials 0.000 claims description 8

- 239000000956 alloy Substances 0.000 claims description 8

- 238000010438 heat treatment Methods 0.000 claims description 8

- 238000007747 plating Methods 0.000 claims description 8

- 238000004544 sputter deposition Methods 0.000 claims description 8

- 229910052719 titanium Inorganic materials 0.000 claims description 8

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 8

- 229910052721 tungsten Inorganic materials 0.000 claims description 8

- 239000010937 tungsten Substances 0.000 claims description 8

- 238000001039 wet etching Methods 0.000 claims description 8

- 229910052715 tantalum Inorganic materials 0.000 claims description 7

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 claims description 7

- 238000009413 insulation Methods 0.000 claims description 6

- 230000004913 activation Effects 0.000 claims description 5

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 claims description 5

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 4

- 238000000137 annealing Methods 0.000 claims description 4

- 239000006227 byproduct Substances 0.000 claims description 4

- 229910052799 carbon Inorganic materials 0.000 claims description 4

- 238000009826 distribution Methods 0.000 claims description 4

- 229910052759 nickel Inorganic materials 0.000 claims description 4

- 238000000059 patterning Methods 0.000 claims description 4

- 239000010941 cobalt Substances 0.000 claims description 3

- 229910017052 cobalt Inorganic materials 0.000 claims description 3

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 claims description 3

- 238000013329 compounding Methods 0.000 claims description 3

- 229910000449 hafnium oxide Inorganic materials 0.000 claims description 3

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 claims description 3

- 238000009740 moulding (composite fabrication) Methods 0.000 claims description 3

- 238000005259 measurement Methods 0.000 description 23

- 238000007689 inspection Methods 0.000 description 19

- 238000004140 cleaning Methods 0.000 description 13

- 229910021332 silicide Inorganic materials 0.000 description 11

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 11

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 10

- 150000004767 nitrides Chemical class 0.000 description 10

- 230000015572 biosynthetic process Effects 0.000 description 8

- 230000000694 effects Effects 0.000 description 6

- 230000008021 deposition Effects 0.000 description 5

- 238000005457 optimization Methods 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 229910052785 arsenic Inorganic materials 0.000 description 2

- 238000012790 confirmation Methods 0.000 description 2

- 238000001514 detection method Methods 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 239000005416 organic matter Substances 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 238000011282 treatment Methods 0.000 description 2

- 229910004129 HfSiO Inorganic materials 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 239000007943 implant Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000001465 metallisation Methods 0.000 description 1

- 230000007261 regionalization Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

- H01L29/42392—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor fully surrounding the channel, e.g. gate-all-around

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66666—Vertical transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7827—Vertical transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78609—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device for preventing leakage current

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78642—Vertical transistors

Definitions

- the present invention relates to a semiconductor device and a manufacturing method thereof.

- SGT Surrounding Gate Transistor

- the SGT provides a channel region so as to surround the side surface of the columnar semiconductor, a large gate width is realized in a small occupied area. That is, it is required to flow a large on-current in a small occupied area. Since a large on-current flows, it is difficult to apply a desired voltage to the source, drain, and gate when the resistance of the source, drain, and gate is high. Therefore, an SGT manufacturing method including a design for reducing the resistance of the source, drain, and gate is required. In addition, since a large on-current flows, it is necessary to reduce the contact resistance.

- a gate is formed by depositing a gate material, transferring a gate pattern to a resist on a substrate by lithography, and etching the gate material. That is, in the conventional MOS transistor, the gate length is designed by the gate pattern.

- the gate length is not designed by the gate pattern, but is designed by the manufacturing method, so that the variation in the gate length and the gate length is determined by the manufacturing method.

- SGT needs to reduce the manufacturing cost like a conventional MOS transistor. Therefore, it is required to reduce the number of manufacturing processes.

- the post-process after forming the metal gate must always be a manufacturing process that considers metal contamination by the metal gate.

- a method of manufacturing a semiconductor device the step of forming a planar semiconductor layer on an oxide film formed on a substrate and forming a columnar first conductivity type semiconductor layer on the planar semiconductor layer; Forming a second conductivity type semiconductor layer in a planar semiconductor layer below the columnar first conductivity type semiconductor layer; Forming a gate insulating film and a gate electrode made of metal around the columnar first conductive semiconductor layer; Forming an insulating film in a sidewall shape on the upper side wall of the first conductive type semiconductor layer in a columnar shape above the gate; A step of forming an insulating film on the side wall of the gate in a sidewall shape, a step of forming a second conductivity type semiconductor layer on top of the columnar first conductivity type semiconductor layer, Forming a metal-semiconductor compound in a second conductive semiconductor layer formed in a planar semiconductor layer below the columnar first conductive semiconductor layer; Forming a compound of a metal and a semiconductor in a second conduct

- At least one of the columnar first conductive semiconductor layers is: The length from the center of the columnar first conductivity type semiconductor layer to the end of the planar semiconductor layer is: The length from the center of the columnar first conductivity type semiconductor layer to the side wall; The thickness of the gate insulating film, The thickness of the gate electrode, The thickness of the insulating film formed in a sidewall shape on the side wall of the gate; The method for manufacturing the semiconductor device is characterized in that the sum is greater than.

- the planar semiconductor layer is a planar silicon layer

- the first conductivity type semiconductor layer is a first conductivity type silicon layer

- the second conductivity type semiconductor layer is a second conductivity type silicon layer.

- the planar semiconductor layer is a planar silicon layer

- the first conductivity type semiconductor layer is a p-type silicon layer or a non-doped silicon layer

- the second conductivity type semiconductor layer is an n-type silicon layer. Is the method.

- the planar semiconductor layer is a planar silicon layer

- the first conductivity type semiconductor layer is an n-type silicon layer or a non-doped silicon layer

- the second conductivity type semiconductor layer is a p-type silicon layer. Is the method.

- a silicon layer for forming a columnar first conductivity type silicon layer and a planar silicon layer is formed on the oxide film formed on the substrate, Forming a pad oxide film on the silicon layer forming the columnar first conductivity type silicon layer and the planar silicon layer; Impurity implantation for threshold adjustment is performed on the silicon layer forming the columnar first conductivity type silicon layer and the planar silicon layer through the pad oxide film, and annealing is performed for impurity activation and diffusion.

- the method of manufacturing a semiconductor device includes a step of forming a silicon nitride film that is used as a mask when forming the columnar first conductivity type silicon layer.

- a silicon layer for forming a columnar first conductivity type silicon layer and a planar silicon layer is formed on the oxide film formed on the substrate, Forming a pad oxide film on the silicon layer forming the columnar first conductivity type silicon layer and the planar silicon layer, and forming a silicon nitride film used as a mask when forming the columnar first conductivity type silicon layer And a process of Forming a silicon oxide film on the silicon nitride film; A step of applying a resist, forming a pattern in which the columnar first conductivity type silicon layer is inverted by lithography using lithography, and forming a hole penetrating the silicon oxide film at a position where the columnar first conductivity type silicon layer is formed When, Forming amorphous silicon or polysilicon so as to fill holes formed in the silicon oxide film; Polishing and removing the amorphous silicon or polysilicon of the silicon oxide film by chemical mechanical polishing; By removing the silicon oxide film by etching, Forming

- a silicon layer for forming a columnar first conductivity type silicon layer and a planar silicon layer is formed on the oxide film formed on the substrate, Forming a pad oxide film on the silicon layer forming the columnar first conductivity type silicon layer and the planar silicon layer, and forming a silicon nitride film used as a mask when forming the columnar first conductivity type silicon layer And a process of Forming a silicon oxide film on the silicon nitride film; A step of applying a resist, forming a pattern in which the columnar first conductivity type silicon layer is inverted by lithography using lithography, and forming a hole penetrating the silicon oxide film at a position where the columnar first conductivity type silicon layer is formed When, Depositing an oxide film and performing etch back to reduce the diameter of the hole penetrating the silicon oxide film;

- a method for manufacturing the semiconductor device comprising:

- amorphous silicon or polysilicon mask as the second hard mask as a mask

- etching the silicon nitride film and the pad oxide film by dry etching to form a silicon nitride film mask as the first hard mask Forming a columnar first conductivity type silicon layer by dry etching using the first hard mask and the second hard mask as a mask

- Including The amorphous silicon or polysilicon mask that is the second hard mask is all etched, and the plasma emission intensity that can be detected by the dry etching apparatus changes. By detecting this change in plasma emission intensity,

- the semiconductor device manufacturing method is characterized in that end point detection is performed and the height of the columnar first conductivity type silicon layer is controlled.

- the thickness of the amorphous silicon or polysilicon mask which is the second hard mask is smaller than the height of the columnar first conductivity type silicon layer.

- the columnar shape is due to the relief of unevenness on the side wall of the columnar substitutional conductivity type silicon layer that becomes the channel part, the removal of the silicon surface in which carbon or the like is implanted during dry etching, and contamination of by-products generated during the next dry etching.

- the method for manufacturing a semiconductor device includes a step of dry-etching the planar silicon layer to form a planar silicon layer below the columnar first conductivity type silicon layer and removing the resist.

- impurities of the second conductivity type are introduced into the surface of the planar silicon layer by impurity implantation or the like, and the lower portion of the columnar first conductivity type silicon layer is introduced.

- a method of manufacturing a semiconductor device comprising: forming a second conductivity type silicon layer formed on the planar silicon layer.

- the column diameter of the columnar first conductivity type silicon layer is The semiconductor device manufacturing method is characterized in that it is smaller than a column diameter of a silicon nitride film mask which is a first hard mask.

- the implantation angle of the impurity implantation used for forming the second conductivity type silicon layer formed in the planar silicon layer below the columnar first conductivity type silicon layer is 0 to 6 degrees. It is a manufacturing method.

- the second conductivity type silicon layer formed on the planar silicon layer below the columnar first conductivity type silicon layer is formed without implanting impurities into the upper portion of the columnar first conductivity type semiconductor layer.

- the gate insulating film having a high dielectric constant is removed by dry etching performed later.

- Etching back the metal that is the gate electrode to form a gate electrode having a desired gate length A step of forming a silicon oxide film on the surface of the metal and the columnar first conductivity type silicon layer as the gate electrode; Including With this silicon oxide film, the metal is covered so that it can be processed without considering metal contamination in the subsequent process, and the gate upper surface is protected from wet processing or dry processing, and the gate length variation or gate insulation from the gate upper surface is protected.

- the semiconductor device manufacturing method is characterized in that damage to the film can be suppressed.

- BARC layer antireflection film layer

- the compounding of a metal and a semiconductor from the side wall of the columnar first conductivity type silicon layer is controlled by covering the side wall of the upper portion of the columnar first conductivity type silicon layer with a silicon nitride film. It is a manufacturing method.

- a silicon nitride film or the like as a contact stopper; A step of planarizing by chemical mechanical polishing after forming a silicon oxide film as an interlayer film; On the second conductivity type silicon layer formed on the planar silicon layer below the columnar first conductivity type silicon layer, on the gate electrode, and on the second conductivity type silicon layer formed on the top of the columnar first conductivity type silicon layer And a step of forming a contact hole by etching, After forming a barrier metal such as tantalum (Ta), tantalum nitride (TaN), titanium (Ti), or titanium nitride (TiN) in the contact hole, a metal such as tungsten (W), copper (Cu), or an alloy containing copper Forming a contact plug by chemical mechanical polishing, forming a film by sputtering or plating, and Forming a first layer wiring etching stopper such as silicon carbide (SiC), and subsequently forming a barrier metal such as tantalum (Ta),

- the contact hole on the columnar silicon layer and the contact hole on the gate wiring After the interlayer film etching process of the contact hole on the columnar silicon layer and the contact hole on the gate wiring, Perform the interlayer film etching process of the contact hole on the planar silicon layer under the columnar silicon layer, Thereafter, the contact hole on the columnar silicon layer, the contact hole on the gate wiring, and the contact stopper on the contact hole on the planar silicon layer below the columnar silicon layer are etched.

- the contact hole on the planar silicon layer below the columnar silicon layer After the interlayer etching process of the contact hole on the planar silicon layer below the columnar silicon layer, Perform an interlayer etching process between the contact hole on the top of the columnar silicon layer and the contact hole on the gate wiring, Thereafter, the contact hole on the columnar silicon layer, the contact hole on the gate wiring, and the contact stopper on the contact hole on the planar silicon layer below the columnar silicon layer are etched.

- the contact hole on the columnar silicon layer, the contact hole on the gate wiring, and the contact stopper on the contact hole on the planar silicon layer below the columnar silicon layer are etched.

- the contact hole on the columnar silicon layer, the contact hole on the gate wiring, and the contact stopper on the contact hole on the planar silicon layer below the columnar silicon layer are etched.

- a semiconductor device A planar semiconductor layer formed on a substrate and having a second conductivity type semiconductor layer formed thereon, wherein the second conductivity type semiconductor layer is a planar semiconductor layer in which a compound of a metal and a semiconductor is formed; A columnar first conductive type semiconductor layer formed on the planar semiconductor layer and having a second conductive type semiconductor layer formed thereon, wherein a compound of a metal and a semiconductor is formed on the second conductive type semiconductor layer.

- the length from the center of the columnar first conductivity type semiconductor layer to the end of the planar semiconductor layer is: A length from the center to the side wall of the columnar first conductive semiconductor layer; A thickness of the gate insulating film; The thickness of the gate electrode; The insulating film formed in a sidewall shape on the side wall of the gate electrode; The semiconductor device as described above, which is larger than the sum of

- a method of manufacturing a semiconductor device the step of forming a planar semiconductor layer on an oxide film formed on a substrate and forming a columnar first conductivity type semiconductor layer on the planar semiconductor layer; Forming a second conductivity type semiconductor layer in a planar semiconductor layer below the columnar first conductivity type semiconductor layer; Forming a gate insulating film and a gate electrode made of metal around the columnar first conductive semiconductor layer; Forming an insulating film in a sidewall shape on the upper side wall of the first conductive type semiconductor layer in a columnar shape above the gate; A step of forming an insulating film on the side wall of the gate in a sidewall shape, a step of forming a second conductivity type semiconductor layer on top of the columnar first conductivity type semiconductor layer, Forming a metal-semiconductor compound in a second conductive semiconductor layer formed in a planar semiconductor layer below the columnar first conductive semiconductor layer; Forming a compound of a metal and a semiconductor in a second conductivity type

- At least one of the columnar first conductive semiconductor layers is: The length from the center of the columnar first conductivity type semiconductor layer to the end of the planar semiconductor layer is: The length from the center of the columnar first conductivity type semiconductor layer to the side wall; The thickness of the gate insulating film, The thickness of the gate electrode, The thickness of the insulating film formed in a sidewall shape on the side wall of the gate; By being greater than the sum of A compound of a metal and a semiconductor can be formed on the second conductive semiconductor layer formed on the planar semiconductor layer below the columnar first conductive semiconductor layer, The resistance of the second conductive semiconductor layer formed in the planar semiconductor layer below the columnar first conductive semiconductor layer can be reduced.

- the sum of the thickness of the gate electrode made of metal and the thickness of the gate insulating film is By being larger than the sum of the thicknesses of the insulating films formed in a sidewall shape on the upper side wall of the first conductive type semiconductor layer in the upper part of the columnar shape, Metal and semiconductor compounds can be formed on the gate electrode, The resistance of the gate electrode can be reduced.

- a silicon layer for forming a columnar first conductivity type silicon layer and a planar silicon layer is formed on the oxide film formed on the substrate, Forming a pad oxide film on the silicon layer forming the columnar first conductivity type silicon layer and the planar silicon layer; Impurity implantation for threshold adjustment is performed on the silicon layer forming the columnar first conductivity type silicon layer and the planar silicon layer through the pad oxide film, and annealing is performed for impurity activation and diffusion.

- a silicon layer for forming a columnar first conductivity type silicon layer and a planar silicon layer is formed on the oxide film formed on the substrate, Forming a pad oxide film on the silicon layer forming the columnar first conductivity type silicon layer and the planar silicon layer, and forming a silicon nitride film used as a mask when forming the columnar first conductivity type silicon layer And a process of Forming a silicon oxide film on the silicon nitride film; A step of applying a resist, forming a pattern in which the columnar first conductivity type silicon layer is inverted by lithography using lithography, and forming a hole penetrating the silicon oxide film at a position where the columnar first conductivity type silicon layer is formed When, Forming amorphous silicon or polysilicon so as to fill holes formed in the silicon oxide film; Polishing and removing the amorphous silicon or polysilicon of the silicon oxide film by chemical mechanical polishing; By removing the silicon oxide film by etching, Forming an amorphous silicon oxide film by

- a silicon layer for forming a columnar first conductivity type silicon layer and a planar silicon layer is formed on the oxide film formed on the substrate, Forming a pad oxide film on the silicon layer forming the columnar first conductivity type silicon layer and the planar silicon layer, and forming a silicon nitride film used as a mask when forming the columnar first conductivity type silicon layer And a process of Forming a silicon oxide film on the silicon nitride film; A step of applying a resist, forming a pattern in which the columnar first conductivity type silicon layer is inverted by lithography using lithography, and forming a hole penetrating the silicon oxide film at a position where the columnar first conductivity type silicon layer is formed When, By depositing an oxide film and performing etch back to reduce the diameter of the hole penetrating the silicon oxide film, By reducing the column diameter of the columnar first conductivity type silicon layer formed later, the short channel effect of the transistor can be suppressed and the leakage current can be reduced.

- amorphous silicon or polysilicon mask as the second hard mask as a mask, etching the silicon nitride film and the pad oxide film by dry etching to form a silicon nitride film mask as the first hard mask;

- a step of forming a columnar first conductivity type silicon layer by dry etching By using the first hard mask and the second hard mask as a mask, a step of forming a columnar first conductivity type silicon layer by dry etching, The amorphous silicon or polysilicon mask that is the second hard mask is all etched, and the plasma emission intensity that can be detected by the dry etching apparatus changes. By detecting this change in plasma emission intensity, The end point can be detected, and the height of the columnar first conductivity type silicon layer can be controlled.

- the thickness of the amorphous silicon or polysilicon mask as the second hard mask is smaller than the height of the columnar first conductivity type silicon layer, the end point of dry etching can be detected.

- the columnar shape is due to the relief of unevenness on the side wall of the columnar substitutional conductivity type silicon layer that becomes the channel part, the removal of the silicon surface in which carbon or the like is implanted during dry etching, and contamination of by-products generated during the next dry etching.

- Sacrificial oxidation of the formed columnar first conductivity type silicon layer to protect the first conductivity type silicon layer Applying a resist and forming a pattern of a second conductivity type silicon layer formed on the planar silicon layer below the columnar first conductivity type silicon layer by lithography using lithography; Including a step of dry etching the planar silicon layer to form a planar silicon layer below the columnar first conductivity type silicon layer and removing the resist; Since the oxide film formed by sacrificial oxidation is used as the first conductive type silicon layer protective film, the number of manufacturing steps can be reduced and the manufacturing cost can be reduced.

- the present invention Using the sacrificial oxide film formed during the sacrificial oxidation of the first conductivity type silicon layer as a through oxide film, impurities of the second conductivity type are introduced into the surface of the planar silicon layer by impurity implantation or the like, and the lower portion of the columnar first conductivity type silicon layer is introduced.

- impurities of the second conductivity type are introduced into the surface of the planar silicon layer by impurity implantation or the like, and the lower portion of the columnar first conductivity type silicon layer is introduced.

- the column diameter of the columnar first conductivity type silicon layer is By being smaller than the column diameter of the silicon nitride film mask which is the first hard mask, Impurities can be prevented from being implanted from the side walls of the first conductivity type silicon layer during implantation.

- the impurity implantation angle used for forming the second conductivity type silicon layer formed in the planar silicon layer below the columnar first conductivity type silicon layer is 0 ° to 6 °, Impurities can be prevented from being implanted from the side wall of the columnar first conductivity type silicon layer during implantation.

- the present invention By forming a second conductivity type silicon layer formed on the planar silicon layer below the columnar first conductivity type silicon layer without implanting impurities into the upper portion of the columnar first conductivity type semiconductor layer, Since the implantation conditions of the upper part of the columnar first conductivity type silicon layer and the planar silicon layer below the columnar first conductivity type silicon layer can be easily optimized, the short channel effect can be suppressed and the leakage current can be suppressed. it can.

- Etching back the metal that is the gate electrode to form a gate electrode having a desired gate length A step of forming a silicon oxide film on the surface of the metal and the columnar first conductivity type silicon layer as the gate electrode;

- the metal is covered so that it can be processed without considering metal contamination in the subsequent process, and the gate upper surface is protected from wet processing or dry processing, and the gate length variation or gate insulation from the gate upper surface is protected. Damage to the film can be suppressed.

- BARC layer An antireflection film layer

- Forming a silicon nitride film or the like as a contact stopper A step of planarizing by chemical mechanical polishing after forming a silicon oxide film as an interlayer film; On the second conductivity type silicon layer formed on the planar silicon layer below the columnar first conductivity type silicon layer, on the gate electrode, and on the second conductivity type silicon layer formed on the top of the columnar first conductivity type silicon layer And a step of forming a contact hole by etching, After forming a barrier metal such as tantalum (Ta), tantalum nitride (TaN), titanium (Ti), or titanium nitride (TiN) in the contact hole, a metal such as tungsten (W), copper (Cu), or an alloy containing copper Forming a contact plug by chemical mechanical polishing, forming a film by sputtering or plating, and Forming a first layer wiring etching stopper such as silicon carbide (SiC), and subsequently forming a low dielectric constant film

- the interlayer film etching process of the contact hole on the columnar silicon layer and the contact hole on the gate wiring Perform the interlayer film etching process of the contact hole on the planar silicon layer under the columnar silicon layer, After that, by etching the contact holes on the upper part of the columnar silicon layer, the contact hole on the gate wiring, and the contact stopper on the planar silicon layer below the columnar silicon layer, Optimization of etching conditions for contact holes on the pillar-shaped silicon layer and contact holes on the gate wiring, It is also possible to optimize the etching conditions for the contact holes on the planar silicon layer below the columnar silicon layer.

- the interlayer etching process of the contact hole on the planar silicon layer below the columnar silicon layer After the interlayer etching process of the contact hole on the planar silicon layer below the columnar silicon layer, Perform an interlayer etching process between the contact hole on the top of the columnar silicon layer and the contact hole on the gate wiring, After that, by etching the contact holes on the upper part of the columnar silicon layer, the contact hole on the gate wiring, and the contact stopper on the planar silicon layer below the columnar silicon layer, Optimization of etching conditions for contact holes on the pillar-shaped silicon layer and contact holes on the gate wiring, It is also possible to optimize the etching conditions for the contact holes on the planar silicon layer below the columnar silicon layer.

- a semiconductor device A planar semiconductor layer formed on a substrate and having a second conductivity type semiconductor layer formed thereon, wherein the second conductivity type semiconductor layer is a planar semiconductor layer in which a compound of a metal and a semiconductor is formed; A columnar first conductive type semiconductor layer formed on the planar semiconductor layer and having a second conductive type semiconductor layer formed thereon, wherein a compound of a metal and a semiconductor is formed on the second conductive type semiconductor layer.

- the length from the center of the columnar first conductivity type semiconductor layer to the end of the planar semiconductor layer is: A length from the center to the side wall of the columnar first conductive semiconductor layer; A thickness of the gate insulating film; The thickness of the gate electrode; The insulating film formed in a sidewall shape on the side wall of the gate electrode; Is greater than the sum of A compound of a metal and a semiconductor can be formed on the second conductive semiconductor layer formed on the planar semiconductor layer below the columnar first conductive semiconductor layer, The resistance of the second conductive semiconductor layer formed in the planar semiconductor layer below the columnar first conductive semiconductor layer can be reduced.

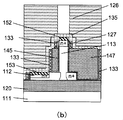

- FIG. 37 (a) is a plan view of an NMOS SGT formed using the present invention

- FIG. 37 (b) is a cross-sectional view taken along the cut line AA ′ of FIG. 37 (a).

- An NMOS SGT formed using the present invention will be described below with reference to FIG.

- a planar silicon layer 112 is formed on the BOX layer 120 formed on the Si substrate 111

- a columnar silicon layer 113 is formed on the planar silicon layer 112, and a high dielectric film is formed around the columnar silicon layer 113.

- a gate insulating film 145 and a metal gate electrode 147 are formed.

- N + source diffusion layer 200 is formed on the planar silicon layer 112 below the columnar silicon layer, and an N + drain diffusion layer 201 is formed on the columnar silicon layer.

- a contact 174 is formed on the N + source diffusion layer 200, a contact 173 is formed on the N + drain diffusion layer 201, and a contact 172 is formed on the gate wiring 147b extending from the gate electrode 147a.

- FIG. 38 is a cross-sectional view taken along the cut line BB ′ of FIG.

- Wa is the length from the center of the silicon pillar 113 to the end of the planar silicon layer 112

- Wp is the length from the center of the silicon pillar 113 to the side wall

- Wox is the thickness of the gate insulating film 145

- Wg is the gate electrode 147.

- Ws is the width of the oxide film sidewall and the nitride film sidewall, that is, the width of the insulating film.

- the SGT operates as a transistor by connecting the N + source diffusion layer to the GND potential, connecting the N + drain diffusion layer to the Vcc potential, and applying a potential of 0 to Vcc to the gate electrode.

- the N + diffusion layer formed on the columnar silicon layer may be an N + source diffusion layer

- the N + diffusion layer formed on the planar silicon layer below the columnar silicon layer may be an N + drain diffusion layer.

- FIG. 1 shows a manufacturing process for forming the SGT of the present invention

- FIGS. 2 to 37 show an example of manufacturing the SGT according to the present invention.

- (A) is a plan view

- (b) is a cross-sectional view along A-A ′.

- pad oxide film 121 is formed on SOI layer 110 using an SOI substrate in which BOX layer 120 is formed on Si substrate 111 and silicon layer 110 is formed on BOX layer 120. .

- lot formation may be performed, laser mark formation may be performed, and pad oxide film cleaning may be performed. Further, the pad oxide film thickness may be measured after the pad oxidation (steps 1, 2, 3, 4, 5 in FIG. 1).

- Impurity implantation for threshold adjustment may be performed on the SOI layer through the pad oxide film, annealing may be performed for impurity activation and diffusion, and the impurity distribution in the SOI layer may be made uniform. At this time, the number of manufacturing steps can be reduced by using a pad oxide film formed as a through oxide film at the time of impurity implantation in order to relieve stress between the silicon nitride film and silicon formed in the next process. And manufacturing costs can be reduced.

- a silicon nitride film 130 as a first hard mask is formed, and then a silicon oxide film 122 is formed.

- the nitride film thickness may be measured.

- the oxide film thickness may be measured after the silicon oxide film is deposited (steps 6, 7, 8, and 9 in FIG. 1).

- a resist is applied, a pattern is formed by inverting the columnar silicon layer with lithography using lithography, and a hole penetrating the silicon oxide film 122 is formed at a position where the columnar silicon layer is formed by dry etching. .

- Dimensional measurement and inspection may be performed after lithography. Further, cleaning may be performed after etching (steps 10, 11, 12, 13, 14, 15, 16, and 17 in FIG. 1).

- an oxide film 129 is deposited, and referring to FIG. 41, the oxide film 129 is etched back to reduce the diameter of the hole penetrating the silicon oxide film 122. it can.

- amorphous silicon or polysilicon 140 is formed so as to fill holes formed in silicon oxide film 122. Cleaning may be performed before depositing amorphous silicon or polysilicon. In addition, the film thickness may be measured after deposition (steps 18, 19, and 20 in FIG. 1).

- amorphous silicon or polysilicon 140 on silicon oxide film 122 is polished and removed by CMP (chemical mechanical polishing). After polishing, the film thickness may be measured (steps 21 and 22 in FIG. 1).

- the silicon oxide film 122 is removed by wet etching using hydrofluoric acid or the like, or by dry etching, so that amorphous silicon or poly silicon serving as a second hard mask at the time of dry etching of the columnar silicon layer in a later process is obtained. Silicon 140 is formed. (Step 23 in FIG. 1)

- amorphous silicon or polysilicon 140 is sacrificial oxidized to form silicon oxide film 128, and the dimensions of amorphous silicon or polysilicon are reduced.

- cleaning before sacrificial oxidation may be performed.

- the film thickness may be measured after oxidation (steps 24, 25, and 26 in FIG. 1).

- the silicon oxide film 128 on the surface of amorphous silicon or polysilicon 140 is removed by wet etching using hydrofluoric acid or dry etching. (Step 27 in FIG. 1).

- silicon nitride film 130 and pad oxide film 121 as the first hard mask are etched by dry etching using amorphous silicon or polysilicon 140 as the second hard mask as a mask. (Steps 28 and 29 in FIG. 1).

- columnar silicon layer 113 is formed by dry etching using silicon nitride film 130 as the first hard mask and amorphous silicon or polysilicon 140 as the second hard mask as a mask. After etching, organic matter removal, inspection using SEM, and step confirmation may be performed (steps 30, 31, 32, and 33 in FIG. 1). During dry etching, the amorphous silicon or polysilicon 140, which is the second hard mask, is also etched. When all of the amorphous silicon or polysilicon 140 is etched, the plasma emission intensity that can be detected by the dry etching apparatus changes. Therefore, by detecting the change in the plasma emission intensity, the end point of etching can be detected, and the height of the columnar silicon layer 113 can be stably controlled regardless of the etching rate.

- the film thickness of amorphous silicon or polysilicon 140 before the columnar silicon layer dry etching needs to be smaller than the height of the columnar silicon layer.

- the planar silicon layer 112 is formed on the buried oxide film layer 120.

- the surface of the columnar silicon layer and the planar silicon layer are used to alleviate the unevenness of the side wall of the columnar silicon layer 113 serving as a channel portion and to remove the silicon surface into which carbon or the like is implanted during dry etching.

- Sacrificial oxidation is performed to form a sacrificial oxide film 123.

- cleaning before sacrificial oxidation may be performed.

- the sacrificial oxide film thickness may be measured after the sacrificial oxidation (steps 34, 35, and 36 in FIG. 1).

- a resist 150 is applied, and a pattern of the source diffusion layer is formed from the resist using lithography.

- overlay error measurement, dimension measurement, and inspection may be performed (steps 37, 38, 39, 40, and 41 in FIG. 1).

- the sacrificial oxide film 123 formed by the above-described sacrificial oxidation on the columnar silicon layer 113 and the planar silicon layer 112 protects the silicon surface from contamination such as by-products generated during the next dry etching.

- planar silicon layer 112 is processed by dry etching, and planar silicon layer 112 is separated. (FIG. 1, steps 42 and 43)

- step confirmation may be performed (steps 44, 45, and 46 in FIG. 1).

- impurities such as P and As are introduced into the surface of planar silicon layer 112 by impurity implantation or the like to form N + source diffusion layer 200 (steps 47 and 48 in FIG. 1).

- the number of manufacturing steps can be reduced by using the sacrificial oxide film 123 formed during the sacrificial oxidation of the columnar silicon layer 113 and the planar silicon layer 112 as a through oxide film.

- the transistor characteristics may fluctuate. Therefore, it is essential that the widths Wp1 and pWp2 of the columnar silicon pillars are smaller than Wn which is the width of the nitride film 130.

- Wp1 is the width of the lower part of the columnar silicon layer

- Wp2 is the width of the upper part of the columnar silicon layer.

- the impurities are not implanted from the side wall of the columnar silicon layer 113 at the time of implantation, it is preferable to implant the impurities at a small angle, that is, 0 to 6 degrees.

- the silicon nitride film 130 formed on the columnar silicon layer 113 is not implanted into the upper portion of the columnar silicon layer 113.

- the implantation into the N + source diffusion layer 200 is preferably 0 °, but the implantation into the drain diffusion layer, which will be formed later on the columnar silicon layer 113, is formed in a self-aligned manner with the gate electrode. It is preferable to inject it.

- the silicon surface is oxidized to form oxide film 124, and nitride film 130 is thinned by wet etching. Cleaning may be performed before oxidation. In addition, the film thickness may be measured after oxidation. (Steps 49, 50, 51, 52 in FIG. 1). This step is for removing the high-K gate insulating film using dry etching in FIG. 22, and the width Wn of the nitride film 130 needs to be smaller than the widths Wp1 and Wp2 of the silicon pillar 113.

- sacrificial oxide film 123 and oxide film 124 are removed by wet etching using hydrofluoric acid or the like. (Step 53 in FIG. 1)

- HfSiO and HfSiON are formed as high-K gate insulating film 145. Cleaning may be performed before forming the insulating film. Further, heat treatment may be performed after the formation (steps 54, 55, and 56 in FIG. 1).

- metal 147 is formed as a gate conductive film so as to embed columnar silicon layer 113. (Step 57 in FIG. 1)

- metal 147 is polished by CMP to planarize the upper surface of the gate conductive film.

- CMP by using the silicon nitride film 130, which is the first hard mask, as a CMP stopper, the CMP polishing amount can be controlled with good reproducibility. (Step 58 in FIG. 1)

- the gate length is determined by etching back metal 147 which is a gate conductive film.

- the high-K gate insulating film is also etched (step 59 in FIG. 1).

- the film thickness may be measured after metal deposition (step 60 in FIG. 1).

- a silicon oxide film 125 is formed on the surfaces of metal 147 and silicon pillar 113 which are gate conductive films. By covering the metal 147 with the silicon oxide film 125, it can be processed without considering metal contamination in a later process. In addition, since the gate upper surface is protected from wet processing or dry processing, variation in gate length, that is, variation in gate length and damage to the gate insulating film 145 from the gate upper surface can be suppressed. (FIG. 1, step 61)

- a silicon nitride film 131 thicker than the desired gate electrode is formed. After film formation, the nitride film thickness may be measured (steps 62 and 63 in FIG. 1).

- silicon nitride film 131 is etched back to form silicon nitride film 131 sidewalls.

- the silicon oxide film 125 is also etched.

- organic substance removal and shape measurement may be performed (steps 64, 65, 66 in FIG. 1). Since the sum of the thickness of the silicon nitride film sidewall 131 and the thickness of the silicon oxide film is the sum of the thickness of the gate electrode formed of the gate electrode 147 made of the metal 147 and the thickness of the high-K gate insulating film.

- a gate electrode having a desired film thickness can be formed.

- BARC layer 161 and resist 160 are applied, and a gate wiring pattern is formed by resist 160 using lithography. After pattern formation, overlay error measurement, dimension measurement, and inspection may be performed (steps 67, 68, 69, 70, 71 in FIG. 1).

- BARC layer 161 gate conductive film metal 147, and high-K gate insulating film are etched to form gate electrode 147a and gate wiring pattern 147b. And the BARC layer is removed. Thereafter, shape measurement may be performed (steps 72, 73, 74, 75, and 76 in FIG. 1).

- silicon nitride film 130 and silicon nitride film sidewall 131 and silicon oxide films 121 and 125 on columnar silicon 113, and oxide film 124 on a planar silicon layer are removed by dry etching or wet etching (see FIG. 28).

- a silicon oxide film 127 and a silicon nitride film 132 are formed. After film formation, the film thickness may be measured (steps 78, 79, and 80 in FIG. 1).

- silicon nitride film 132 is etched back, silicon oxide film 127 is etched to expose the upper surface of N + source diffusion layer 200 and the upper surface of columnar silicon 113, and the sidewall and gate of columnar silicon layer 113. 147 side walls are covered with silicon nitride films 133 and 134. After etching, organic matter removal and shape measurement may be performed (steps 81, 82, and 83 in FIG. 1). Since the nitride films 133 and 134 separate the gate electrode 147, the source diffusion layer 200, and the N + drain diffusion layer formed later on the columnar silicon, the gate electrodes 147, 147, the source diffusion layer 200, and the drain diffusion layer made of silicide are separated. Can be prevented.

- the silicon nitride films 133 and 134 are silicon oxide films, they are etched by hydrofluoric acid used for cleaning / peeling process and silicide pretreatment, so that the silicon nitride films 133 and 134 are films not soluble in hydrofluoric acid such as silicon nitride films. Preferably there is.

- an impurity such as P or As is introduced into the upper portion of columnar silicon layer 113 by impurity implantation or the like, and N + drain diffusion layer 201 is formed. Activation may be performed after the introduction of impurities (steps 84 and 85 in FIG. 1).

- a metal film such as Ni or Co is sputtered, and heat treatment is applied to make the surface of source 200 drain 201 a silicide of a metal and a semiconductor, that is, silicidation, thereby removing the unreacted metal film.

- a silicide layer 152 on the diffusion layer 201 and a silicide layer 153 on the source diffusion layer 200 are formed.

- the oxide film may be removed (steps 86, 87, 88, 89 in FIG. 1).

- a silicon nitride film or the like is formed as contact stopper 135. (Step 90 in FIG. 1)

- a silicon oxide film is formed as interlayer film 126, it is planarized by CMP. After film formation, the film thickness may be measured. Further, the film thickness may be measured after planarization. Further, the nitride film thickness may be measured (steps 91, 92, 93, 94, 95 in FIG. 1).

- contact holes are formed by etching on drain diffusion layer 201 above columnar silicon layer 113, on gate wiring 147b, and on source diffusion layer 200. Before etching the contact hole, contact mask exposure is performed. Further, dimension measurement, overlay error measurement, and inspection may be performed. Further, after the contact hole is formed, the plasma resist is peeled off. Thereafter, cleaning may be performed, and dimension measurement, oxide film thickness measurement, inspection, and wafer container replacement may be performed (FIG. 1 steps 96, 97, 98, 99, 100, 101, 102, 103, 104, 105, 106, 107, 108).

- the etching depth of the contact hole on the columnar silicon layer and the contact hole on the gate wiring is different from the etching depth of the contact hole on the planar silicon layer below the columnar silicon layer.

- the interlayer film between the contact hole on the silicon layer and the contact hole on the gate wiring is etched.

- the interlayer between the contact holes on the planar silicon layer below the columnar silicon layer is masked using the resist 162 as a mask.

- the contact stopper may be etched after the film is etched and the interlayer film is etched.

- the interlayer film of the contact hole on the upper part of the columnar silicon layer is etched, and the contact hole on the gate wiring and the contact on the planar silicon layer below the columnar silicon layer are referred to with reference to FIG.

- the contact stopper may be etched after the interlayer film of the hole is etched and the interlayer film is etched.

- the upper part of the pillar-shaped silicon layer is etched by separately etching the interlayer film in the contact hole above the pillar-shaped silicon layer and the interlayer film in the contact hole on the planar silicon layer below the pillar-shaped silicon layer and the contact hole on the gate wiring. It is also possible to optimize the etching conditions for the contact holes and the etching conditions for the contact holes on the gate wiring and the contact holes on the planar silicon layer below the columnar silicon layer.

- tantalum (Ta), tantalum nitride (TaN) or the like, which is barrier metal 171 is formed in the contact hole, and then copper (Cu) 170 is formed by sputtering or plating, and contact 172 is formed by CMP. , 173, 174.

- Titanium (Ti) or titanium nitride (TiN) may be used as the barrier metal.

- tungsten (W) may be used.

- an alloy containing copper may be used.

- backside treatment, inspection, and heat treatment may be performed. Further, inspection may be performed after CMP (steps 111, 112, 113, 114, and 115 in FIG. 1).

- SiC 180 (silicon carbide) is formed as an etching stopper for the first layer wiring, and subsequently, a Low-k film 190 which is an interlayer film of the first wiring layer is formed.

- the film thickness may be measured and inspected (steps 116, 117, 118, and 119 in FIG. 1).

- the first layer wiring is patterned to form a groove pattern of the first wiring layer. After patterning, dimension measurement, overlay error measurement, and inspection may be performed. After forming the groove pattern, the plasma resist may be stripped and inspected (steps 120, 121, 122, 123, 124, 125, 126, 127 in FIG. 1).

- first layer wirings 177, 178, 179 are formed by CMP.

- Titanium (Ti) or titanium nitride (TiN) may be used as the barrier metal.

- tungsten (W) may be used.

- an alloy containing copper may be used.

- backside treatment, inspection, and heat treatment may be performed. In addition, inspection may be performed after CMP (steps 128, 129, 130, 131, 132, 133, and 134 in FIG. 1).

- nitride film deposition, interlayer insulating film deposition, and interlayer insulating film thickness measurement may be performed (steps 135, 136, and 137 in FIG. 1).

- Multi-layer wiring may be performed before the pad via.

- the manufacturing method of the semiconductor device of this invention The top view which shows the manufacture example of the semiconductor device which concerns on this invention.

- A-A 'sectional process drawing showing a manufacturing example of a semiconductor device according to the present invention The top view which shows the manufacture example of the semiconductor device which concerns on this invention.

- A-A 'sectional process drawing showing a manufacturing example of a semiconductor device according to the present invention The top view which shows the manufacture example of the semiconductor device which concerns on this invention.

- A-A 'sectional process drawing showing a manufacturing example of a semiconductor device according to the present invention The top view which shows the manufacture example of the semiconductor device which concerns on this invention.

- A-A 'sectional process drawing showing a manufacturing example of a semiconductor device according to the present invention The top view which shows the manufacture example of the semiconductor device which concerns on this invention.

- A-A 'sectional process drawing showing a manufacturing example of a semiconductor device according to the present invention The top view which shows the manufacture example of the semiconductor device which concerns on this invention.

- A-A 'sectional process drawing showing a manufacturing example of a semiconductor device according to the present invention The top view which shows the manufacture example of the semiconductor device which concerns on this invention.

- A-A 'sectional process drawing showing a manufacturing example of a semiconductor device according to the present invention The top view which shows the manufacture example of the semiconductor device which concerns on this invention.

- FIG. 38 is a cross-sectional view of FIG.

- A-A 'sectional process drawing showing a manufacturing example of a semiconductor device according to the present invention The top view which shows the manufacture example of the semiconductor device which concerns on this invention.

- A-A 'sectional process drawing showing a manufacturing example of a semiconductor device according to the present invention The top view which shows the manufacture example of the semiconductor device which concerns on this invention.

- Silicide layer 153 Silicide layer 160. Resist 161. BARC layer 162. Resist 170. Cu 171. Barrier metal 172. Contact 173. Contact 174. Contact 175. Barrier metal 176. Cu 177. First layer wiring 178. First layer wiring 179. First layer wiring 200. N + source diffusion layer 201. N + drain diffusion layer

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

- Semiconductor Memories (AREA)

Abstract

Description

SGTは、柱状半導体の側面がチャネル領域であるため、基板に対して垂直に、電流が流れる。すなわち、SGTにおいて、ゲート長は、ゲートパターンにより設計されず、製造方法により設計されるため、製造方法によりゲート長とゲート長のばらつきが決定される。

ソース、ドレイン、ゲートの低抵抗化のための構造と所望のゲート長、ソース、ドレイン形状と柱状半導体の直径が得られるSGTの製造方法を提供することを課題とする。

半導体装置の製造方法であって、基板上に形成された酸化膜上に、平面状半導体層が形成され、平面状半導体層上に柱状の第1導電型半導体層を形成する工程と、

柱状の第1導電型半導体層の下部の平面状半導体層に第2導電型半導体層を形成する工程と、

柱状の第1導電型半導体層の周囲にゲート絶縁膜および金属からなるゲート電極を形成する工程と、

ゲートの上部且つ柱状の第1導電型半導体層の上部側壁に、絶縁膜をサイドウォール状に形成する工程と、

ゲートの側壁に絶縁膜をサイドウォール状に形成する工程と

柱状の第1導電型半導体層の上部に第2導電型半導体層を形成する工程と、

柱状の第1導電型半導体層の下部の平面状半導体層に形成した第2導電型半導体層に金属と半導体の化合物を形成する工程と、

柱状の第1導電型半導体層の上部に形成した第2導電型半導体層に金属と半導体の化合物を形成する工程と、

ゲートに金属と半導体の化合物を形成する工程と、

柱状の第1導電型半導体層の下部の平面状半導体層に形成した第2導電型半導体層上にコンタクトを形成する工程と、

柱状の第1導電型半導体層の上部に形成した第2導電型半導体層上にコンタクトを形成する工程と、を含むことを特徴とする半導体装置の製造方法である。

前記柱状の第1導電型半導体層のうち少なくとも一つは、

柱状の第1導電型半導体層の中心から平面状半導体層の端までの長さは、

柱状の第1導電型半導体層の中心から側壁までの長さと、

ゲート絶縁膜の厚さと、

ゲート電極の厚さと、

ゲートの側壁にサイドウォール状に形成した絶縁膜の厚さと、

の和より大きいことを特徴とする前記半導体装置の製造方法である。

平面状半導体層は平面状シリコン層であり、第1導電型半導体層は第1導電型シリコン層であり、第2導電型半導体層は第2導電型シリコン層である前記半導体装置の製造方法である。

平面状半導体層は平面状シリコン層であり、第1導電型半導体層はp型シリコン層または、ノンドープのシリコン層であり、第2導電型半導体層はn型シリコン層である前記半導体装置の製造方法である。

平面状半導体層は平面状シリコン層であり、第1導電型半導体層はn型シリコン層または、ノンドープのシリコン層であり、第2導電型半導体層はp型シリコン層である前記半導体装置の製造方法である。

基板上に形成された酸化膜上に、柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層が形成され、

柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層上に、パット酸化膜を成膜する工程と、

パット酸化膜越しに、柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層にしきい値調整用の不純物注入を行い、不純物の活性化及び拡散のためにアニールを行い、柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層の不純物分布を均一化する工程と、

柱状の第1導電型シリコン層を形成時にマスクとして用いるシリコン窒化膜を成膜する工程を含むことを特徴とする前記半導体装置の製造方法である。

基板上に形成された酸化膜上に、柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層が形成され、

柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層上に、パット酸化膜を成膜する工程と

柱状の第1導電型シリコン層を形成時にマスクとして用いるシリコン窒化膜を成膜する工程と、

シリコン窒化膜上にシリコン酸化膜を形成する工程と、

レジストを塗布し、リソグラフィーを用いてレジストにより柱状の第1導電型シリコン層を反転したパターンを形成し、柱状の第1導電型シリコン層の形成箇所にシリコン酸化膜を貫通するホールを形成する工程と、

アモルファスシリコンあるいはポリシリコンをシリコン酸化膜に形成されたホールを埋め込むように成膜する工程と、

化学機械研磨によりシリコン酸化膜のアモルファスシリコンあるいはポリシリコンを研磨して除去する工程と、

エッチングにより、シリコン酸化膜を除去することにより、

第2のハードマスクであるアモルファスシリコンあるいはポリシリコンマスクを形成する工程と、

アモルファスシリコンあるいはポリシリコンマスクを犠牲酸化して、アモルファスシリコンあるいはポリシリコンマスクの寸法を縮小する工程と、

アモルファスシリコンあるいはポリシリコンマスク表面のシリコン酸化膜をエッチングにより除去する工程と、

を含むことを特徴とする前記半導体装置の製造方法である。

基板上に形成された酸化膜上に、柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層が形成され、

柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層上に、パット酸化膜を成膜する工程と

柱状の第1導電型シリコン層を形成時にマスクとして用いるシリコン窒化膜を成膜する工程と、

シリコン窒化膜上にシリコン酸化膜を形成する工程と、

レジストを塗布し、リソグラフィーを用いてレジストにより柱状の第1導電型シリコン層を反転したパターンを形成し、柱状の第1導電型シリコン層の形成箇所にシリコン酸化膜を貫通するホールを形成する工程と、

酸化膜を堆積し、エッチバックを行うことで、前記シリコン酸化膜を貫通するホールの径を小さくする工程と、

を含むことを特徴とする前記半導体装置の製造方法である。

第2のハードマスクであるアモルファスシリコンあるいはポリシリコンマスクをマスクとして、ドライエッチングによりシリコン窒化膜及びパット酸化膜をエッチングし、第1のハードマスクであるシリコン窒化膜マスクを形成する工程と、

第1のハードマスク及び第2のハードマスクをマスクとして、柱状の第1導電型シリコン層をドライエッチングにより形成する工程と、

を含み、

第2のハードマスクであるアモルファスシリコンあるいはポリシリコンマスクが全てエッチングされ、ドライエッチング装置において検出することが可能なプラズマ発光強度が変化し、このプラズマ発光強度の変化を検出することにより、ドライエッチングの終点検出を行い、柱状の第1導電型シリコン層の高さを制御することを特徴とする前記半導体装置の製造方法である。

第2のハードマスクであるアモルファスシリコンあるいはポリシリコンマスクの厚さは、柱状の第1導電型シリコン層の高さより小さいことを特徴とする前記半導体装置の製造方法である。

チャネル部となる柱状の代導電型シリコン層の側壁の凹凸の緩和や、ドライエッチング中にカーボンなどが打ち込まれたシリコン表面の除去と、次工程のドライエッチング時に生じる副生成物等の汚染から柱状の第1導電型シリコン層を保護するため、形成された柱状の第1導電型シリコン層を犠牲酸化する工程と、

レジストを塗布し、リソグラフィーを用いてレジストにより柱状の第1導電型シリコン層の下部の平面状シリコン層に形成する第2導電型シリコン層のパターンを形成する工程と、

平面状シリコン層をドライエッチングし、柱状の第1導電型シリコン層の下部の平面状シリコン層を形成し、レジストを除去する工程を含むことを特徴とする前記半導体装置の製造方法である。

第1導電型シリコン層犠牲酸化時に形成された犠牲酸化膜をスルー酸化膜として不純物注入等により平面状シリコン層表面に第2導電型の不純物を導入し、柱状の第1導電型シリコン層の下部の平面状シリコン層に形成する第2導電型シリコン層を形成することを特徴とする前記半導体装置の製造方法である。

柱状の第1導電型シリコン層の柱径は、

第1のハードマスクであるシリコン窒化膜マスクの柱径より小さいことを特徴とする前記半導体装置の製造方法である。

柱状の第1導電型シリコン層の下部の平面状シリコン層に形成する第2導電型シリコン層形成に用いる不純物注入の注入角は、0度~6度であることを特徴とする前記半導体装置の製造方法である。

柱状の第1導電型半導体層の上部に不純物を注入せず、柱状の第1導電型シリコン層の下部の平面状シリコン層に形成する第2導電型シリコン層を形成することを特徴とする前記半導体装置の製造方法である。

シリコン表面の酸化を行い、シリコン窒化膜マスクのエッチングを行い、

シリコン窒化膜マスクの柱径を、柱状の第1導電型シリコン層の柱径より小さくする工程を含み、

後に行われるドライエッチングを用いて高誘電率のゲート絶縁膜を除去することを特徴とする前記半導体装置の製造方法である。

犠牲酸化膜をエッチングで除去し、ハフニウムオキサイドなどの高誘電率のゲート絶縁膜を形成し、ゲート電極として金属を、柱状の第1導電型シリコン層を埋め込むように成膜する工程と、

化学機械研磨により金属を研磨し、ゲート電極の上面を平坦化する工程と、

を含み、

化学機械研磨において、第1のハードマスクであるシリコン窒化膜を化学機械研磨のストッパーとして使用することにより、再現性よく化学機械研磨の研磨量を抑制することを特徴とする前記半導体装置の製造方法である。

ゲート電極である金属をエッチバックすることにより、所望のゲート長を持つゲート電極を形成する工程と、

ゲート電極である金属および柱状の第1導電型シリコン層の表面にシリコン酸化膜を成膜する工程と、

を含み、

このシリコン酸化膜により、金属が覆われることにより後工程においてメタル汚染を考慮することなく処理でき、また、ウェット処理またはドライ処理からゲート上面が保護され、ゲート長の変動やゲート上面からのゲート絶縁膜へのダメージを抑制することができることを特徴とする前記半導体装置の製造方法である。

所望のゲート電極の膜厚とゲート絶縁膜の膜厚の和からシリコン酸化膜の膜厚を減じた膜厚のシリコン窒化膜を成膜する工程と、

シリコン窒化膜とシリコン酸化膜をエッチバックすることによりシリコン酸化膜サイドウォールとシリコン窒化膜サイドウォールを形成する工程と

を含み、

シリコン窒化膜サイドウォールの膜厚とシリコン酸化膜サイドウォールの膜厚の和が金属からなるゲート電極の膜厚とゲート絶縁膜の膜厚の和となるため、シリコン窒化膜の成膜膜厚及びエッチバック条件を調整することによって、所望の膜厚のゲート電極を形成することができることを特徴とし、

反射防止膜層(BARC層)及びレジストを塗布し、リソグラフィーを用いてレジストによりゲート配線パターンを形成し、

レジストをマスクとして、反射防止膜層(BARC層)、シリコン酸化膜及びゲート電極である金属をエッチングして、ゲート電極及びゲート配線を形成する工程と、

柱状の第1導電型シリコン層上部のシリコン窒化膜及びシリコン酸化膜サイドウォールとシリコン窒化膜サイドウォールをドライエッチングもしくはウェットエッチングにより除去する工程と、

シリコン酸化膜とシリコン窒化膜を成膜し、

シリコン窒化膜をエッチバックし、シリコン酸化膜をエッチングし、柱状の第1導電型シリコン層の下部の平面状シリコン層に形成した第2導電型シリコン層及び柱状の第1導電型シリコン層の上部を露出し、

ゲート電極の上部且つ柱状の第1導電型シリコン層の上部側壁に、シリコン酸化膜サイドウォールとシリコン窒化膜サイドウォールを形成し、ゲート電極の側壁にシリコン酸化膜サイドウォールとシリコン窒化膜サイドウォール、すなわち絶縁膜サイドウォールを形成する工程と、

不純物注入等により柱状の第1導電型シリコン層の上部に第2導電型の不純物を導入し、柱状の第1導電型シリコン層の上部に第2導電型シリコン層を形成する工程と、

ニッケル(Ni)もしくはコバルト(Co)等の金属膜をスパッタし、熱処理を加えることで、

柱状の第1導電型シリコン層の下部の平面状シリコン層に形成した第2導電型シリコン層と、

柱状の第1導電型シリコン層の上部に形成した第2導電型シリコン層の表面を金属と半導体の化合物化し、未反応の金属膜を除去することによって

柱状の第1導電型シリコン層の下部の平面状シリコン層に形成した第2導電型シリコン層と、柱状の第1導電型シリコン層の上部に形成した第2導電型シリコン層上に金属と半導体の化合物を形成する工程と、

を含み、

シリコン酸化膜サイドウォールとシリコン窒化膜サイドウォールにより

ゲート電極と

柱状の第1導電型シリコン層の下部の平面状シリコン層に形成した第2導電型シリコン層及び柱状の第1導電型シリコン層の上部に形成した第2導電型シリコン層が分離されるため、

金属と半導体の化合物によるゲート電極と柱状の第1導電型シリコン層の下部の平面状シリコン層に形成した第2導電型シリコン層及び柱状の第1導電型シリコン層の上部に形成した第2導電型シリコン層の短絡を防止できることを特徴とし、

柱状の第1導電型シリコン層上部の側壁をシリコン窒化膜で覆うことにより、柱状の第1導電型シリコン層の側壁からの金属と半導体の化合物化を制御することを特徴とする前記半導体装置の製造方法である。

コンタクトストッパーとしてシリコン窒化膜等を成膜する工程と、

層間膜としてシリコン酸化膜を成膜後、化学機械研磨により平坦化する工程と、

柱状の第1導電型シリコン層の下部の平面状シリコン層に形成した第2導電型シリコン層上、ゲート電極上、柱状の第1導電型シリコン層の上部に形成した第2導電型シリコン層上に、エッチングによりコンタクト孔を形成する工程と、

コンタクト孔にタンタル(Ta)や窒化タンタル(TaN)や、チタン(Ti)や窒化チタン(TiN)といったバリアメタルを成膜後、タングステン(W)や銅(Cu)及び銅を含む合金などのメタルをスパッタやめっきにより成膜して、化学機械研磨によってコンタクトプラグを形成する工程と、

炭化ケイ素(SiC)などの第1層配線のエッチングストッパーを成膜し、続いて第1配線層の層間膜である低誘電率膜を成膜する工程と、

第1層配線をパターニングして、第1配線層の溝パターンを形成し、

タンタル(Ta)や窒化タンタル(TaN)や、チタン(Ti)や窒化チタン(TiN)といったバリアメタルを成膜後、タングステン(W)や銅(Cu)及び銅を含む合金などのメタルをスパッタやめっきにより成膜して、化学機械研磨によって第1層配線を形成する工程とを含む前記半導体装置の製造方法である。

柱状シリコン層上部のコンタクト孔とゲート配線上のコンタクト孔の層間膜エッチング工程の後、

柱状シリコン層下部の平面状シリコン層上のコンタクト孔の層間膜エッチング工程を行い、

その後、柱状シリコン層上部のコンタクト孔とゲート配線上のコンタクト孔と

柱状シリコン層下部の平面状シリコン層上のコンタクト孔の

コンタクトストッパーをエッチングすること

を特徴とする前記半導体装置の製造方法である。

柱状シリコン層下部の平面状シリコン層上のコンタクト孔の層間膜エッチング工程の後に、

柱状シリコン層上部のコンタクト孔とゲート配線上のコンタクト孔の層間膜エッチング工程を行い、

その後、柱状シリコン層上部のコンタクト孔とゲート配線上のコンタクト孔と

柱状シリコン層下部の平面状シリコン層上のコンタクト孔の

コンタクトストッパーをエッチングすること

を特徴とする前記半導体装置の製造方法である。

柱状シリコン層上部のコンタクト孔の層間膜エッチング工程の後、

ゲート配線上のコンタクト孔と柱状シリコン層下部の平面状シリコン層上のコンタクト孔の層間膜エッチング工程を行い、

その後、柱状シリコン層上部のコンタクト孔と

ゲート配線上のコンタクト孔と柱状シリコン層下部の平面状シリコン層上のコンタクト孔のコンタクトストッパーをエッチングすること

を特徴とする前記半導体装置の製造方法である。

ゲート配線上のコンタクト孔と柱状シリコン層下部の平面状シリコン層上のコンタクト孔の層間膜エッチング工程の後、

柱状シリコン層上部のコンタクト孔の層間膜エッチング工程を行い、

その後、柱状シリコン層上部のコンタクト孔と

ゲート配線上のコンタクト孔と柱状シリコン層下部の平面状シリコン層上のコンタクト孔のコンタクトストッパーをエッチングすること

を特徴とする前記半導体装置の製造方法である。

半導体装置であって、

基板の上に形成され、第2導電型半導体層が形成された平面状半導体層であって、該第2導電型半導体層に金属と半導体との化合物が形成された平面状半導体層と、

該平面状半導体層の上に形成され、上部に第2導電型半導体層が形成された柱状の第1導電型半導体層であって、該第2導電型半導体層に金属と半導体との化合物が形成された柱状の第1導電型半導体層と、

該柱状の第1導電型半導体層の周囲に形成されたゲート絶縁膜と、

該ゲート絶縁膜を囲む金属からなるゲート電極と、

該ゲート電極の上部であって前記柱状の第1導電型半導体層の上部側壁に、サイドウォール状に形成されるとともに、前記ゲート電極の側壁にサイドウォール状に形成された、絶縁膜と、

を具備することを特徴とする半導体装置である。

前記柱状の第1導電型半導体層の中心から前記平面状半導体層の端までの長さが、

前記柱状の第1導電型半導体層の中心から側壁までの長さと、

前記ゲート絶縁膜の厚さと、

前記ゲート電極の厚さと、

前記ゲート電極の側壁にサイドウォール状に形成された前記絶縁膜と、

の和より大きい、前記記載の半導体装置である。

半導体装置の製造方法であって、基板上に形成された酸化膜上に、平面状半導体層が形成され、平面状半導体層上に柱状の第1導電型半導体層を形成する工程と、

柱状の第1導電型半導体層の下部の平面状半導体層に第2導電型半導体層を形成する工程と、

柱状の第1導電型半導体層の周囲にゲート絶縁膜および金属からなるゲート電極を形成する工程と、

ゲートの上部且つ柱状の第1導電型半導体層の上部側壁に、絶縁膜をサイドウォール状に形成する工程と、

ゲートの側壁に絶縁膜をサイドウォール状に形成する工程と

柱状の第1導電型半導体層の上部に第2導電型半導体層を形成する工程と、

柱状の第1導電型半導体層の下部の平面状半導体層に形成した第2導電型半導体層に金属と半導体の化合物を形成する工程と、

柱状の第1導電型半導体層の上部に形成した第2導電型半導体層に金属と半導体の化合物を形成する工程と、

ゲートに金属と半導体の化合物を形成する工程と、

柱状の第1導電型半導体層の下部の平面状半導体層に形成した第2導電型半導体層上にコンタクトを形成する工程と、

柱状の第1導電型半導体層の上部に形成した第2導電型半導体層上にコンタクトを形成する工程と、を含むことを特徴とする半導体装置の製造方法により、

ゲート電極にメタルを用い、メタル汚染を考慮した製造工程を含み、

ソース、ドレイン、ゲートの低抵抗化のための構造と所望のゲート長、ソース、ドレイン形状と柱状半導体の直径が得られるSGTの製造方法を提供する。

前記柱状の第1導電型半導体層のうち少なくとも一つは、

柱状の第1導電型半導体層の中心から平面状半導体層の端までの長さは、

柱状の第1導電型半導体層の中心から側壁までの長さと、

ゲート絶縁膜の厚さと、

ゲート電極の厚さと、

ゲートの側壁にサイドウォール状に形成した絶縁膜の厚さと、

の和より大きいことを特徴とすることにより、

柱状の第1導電型半導体層の下部の平面状半導体層に形成した第2導電型半導体層に金属と半導体の化合物を形成することができ、

柱状の第1導電型半導体層の下部の平面状半導体層に形成した第2導電型半導体層を低抵抗化することができる。

金属からなるゲート電極の厚さと

ゲート絶縁膜の厚さの和は、

ゲートの上部且つ柱状の第1導電型半導体層の上部側壁にサイドウォール状に形成した絶縁膜の厚さの和

より大きいことにより、

ゲート電極に金属と半導体の化合物を形成することができ、

ゲート電極を低抵抗化することができる。

基板上に形成された酸化膜上に、柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層が形成され、

柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層上に、パット酸化膜を成膜する工程と、

パット酸化膜越しに、柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層にしきい値調整用の不純物注入を行い、不純物の活性化及び拡散のためにアニールを行い、柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層の不純物分布を均一化する工程と、

柱状の第1導電型シリコン層を形成時にマスクとして用いるシリコン窒化膜を成膜する工程を含むことにより

次工程で成膜するシリコン窒化膜とシリコンとの応力を緩和するために成膜するパッド酸化膜を不純物注入時のスルー酸化膜としても用いることで、製造工程数を削減することができ、製造コストを下げることができる。

基板上に形成された酸化膜上に、柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層が形成され、

柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層上に、パット酸化膜を成膜する工程と

柱状の第1導電型シリコン層を形成時にマスクとして用いるシリコン窒化膜を成膜する工程と、

シリコン窒化膜上にシリコン酸化膜を形成する工程と、

レジストを塗布し、リソグラフィーを用いてレジストにより柱状の第1導電型シリコン層を反転したパターンを形成し、柱状の第1導電型シリコン層の形成箇所にシリコン酸化膜を貫通するホールを形成する工程と、

アモルファスシリコンあるいはポリシリコンをシリコン酸化膜に形成されたホールを埋め込むように成膜する工程と、

化学機械研磨によりシリコン酸化膜のアモルファスシリコンあるいはポリシリコンを研磨して除去する工程と、

エッチングにより、シリコン酸化膜を除去することにより、

第2のハードマスクであるアモルファスシリコンあるいはポリシリコンマスクを形成する工程と、

アモルファスシリコンあるいはポリシリコンマスクを犠牲酸化して、アモルファスシリコンあるいはポリシリコンマスクの寸法を縮小する工程と

アモルファスシリコンあるいはポリシリコンマスク表面のシリコン酸化膜をエッチングにより除去する工程と

を含むことにより、

後に形成される柱状の第1導電型シリコン層の柱径を小さくできることにより、トランジスタのショートチャネル効果を抑制し、リーク電流を低減できる。

基板上に形成された酸化膜上に、柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層が形成され、

柱状の第1導電型シリコン層と平面状シリコン層を形成するシリコン層上に、パット酸化膜を成膜する工程と

柱状の第1導電型シリコン層を形成時にマスクとして用いるシリコン窒化膜を成膜する工程と、

シリコン窒化膜上にシリコン酸化膜を形成する工程と、

レジストを塗布し、リソグラフィーを用いてレジストにより柱状の第1導電型シリコン層を反転したパターンを形成し、柱状の第1導電型シリコン層の形成箇所にシリコン酸化膜を貫通するホールを形成する工程と、

酸化膜を堆積し、エッチバックを行うことで、前記シリコン酸化膜を貫通するホールの径を小さくする工程と

を含むことにより、

後に形成される柱状の第1導電型シリコン層の柱径を小さくできることにより、トランジスタのショートチャネル効果を抑制し、リーク電流を低減できる。

第2のハードマスクであるアモルファスシリコンあるいはポリシリコンマスクをマスクとして、ドライエッチングによりシリコン窒化膜及びパット酸化膜をエッチングし、第1のハードマスクであるシリコン窒化膜マスクを形成する工程と、

第1のハードマスク及び第2のハードマスクをマスクとして、柱状の第1導電型シリコン層をドライエッチングにより形成する工程により、

第2のハードマスクであるアモルファスシリコンあるいはポリシリコンマスクが全てエッチングされ、ドライエッチング装置において検出することが可能なプラズマ発光強度が変化し、このプラズマ発光強度の変化を検出することにより、ドライエッチングの終点検出を行い、柱状の第1導電型シリコン層の高さを制御することができる。

第2のハードマスクであるアモルファスシリコンあるいはポリシリコンマスクの厚さは、柱状の第1導電型シリコン層の高さより小さいことを特徴とすることにより、ドライエッチングの終点検出を行うことができる。

チャネル部となる柱状の代導電型シリコン層の側壁の凹凸の緩和や、ドライエッチング中にカーボンなどが打ち込まれたシリコン表面の除去と、次工程のドライエッチング時に生じる副生成物等の汚染から柱状の第1導電型シリコン層を保護するため、形成された柱状の第1導電型シリコン層を犠牲酸化する工程と、

レジストを塗布し、リソグラフィーを用いてレジストにより柱状の第1導電型シリコン層の下部の平面状シリコン層に形成する第2導電型シリコン層のパターンを形成する工程と、

平面状シリコン層をドライエッチングし、柱状の第1導電型シリコン層の下部の平面状シリコン層を形成し、レジストを除去する工程を含むことにより、

犠牲酸化により形成された酸化膜を第1導電型シリコン層保護膜として使用するため、製造工程数を削減することができ、製造コストを下げることができる。

第1導電型シリコン層犠牲酸化時に形成された犠牲酸化膜をスルー酸化膜として不純物注入等により平面状シリコン層表面に第2導電型の不純物を導入し、柱状の第1導電型シリコン層の下部の平面状シリコン層に形成する第2導電型シリコン層を形成することにより、

犠牲酸化により形成された酸化膜を第1導電型シリコン層保護膜として使用し、さらに不純物注入時のスルー酸化膜として使用するため、製造工程数を削減することができ、製造コストを下げることができる。

柱状の第1導電型シリコン層の柱径は、

第1のハードマスクであるシリコン窒化膜マスクの柱径より小さいことを特徴とすることにより、

注入時に第1導電型シリコン層の側壁から不純物が打ち込まれることを防ぐことができる。

柱状の第1導電型シリコン層の下部の平面状シリコン層に形成する第2導電型シリコン層形成に用いる不純物注入の注入角は、0度~6度度であることを特徴とすることにより、

注入時に柱状の第1導電型シリコン層の側壁から不純物が打ち込まれることを防ぐことができる。

柱状の第1導電型半導体層の上部に不純物を注入せず、柱状の第1導電型シリコン層の下部の平面状シリコン層に形成する第2導電型シリコン層を形成することにより、

柱状の第1導電型シリコン層上部と、柱状の第1導電型シリコン層の下部の平面状シリコン層の注入条件を容易に最適化できるため、ショートチャネル効果を抑制しリーク電流を抑制することができる。

シリコン表面の酸化を行い、シリコン窒化膜マスクのエッチングを行い、

シリコン窒化膜マスクの柱径を、柱状の第1導電型シリコン層の柱径より小さくする工程を含むことにより、

後に行われるドライエッチングを用いて高誘電率のゲート絶縁膜を除去することができる。

犠牲酸化膜をエッチングで除去し、ハフニウムオキサイドなどの高誘電率のゲート絶縁膜を形成し、ゲート電極として金属を、柱状の第1導電型シリコン層を埋め込むように成膜する工程と、

化学機械研磨により金属を研磨し、ゲート電極の上面を平坦化する工程と、を含むことにより、

化学機械研磨において、第1のハードマスクであるシリコン窒化膜を化学機械研磨のストッパーとして使用することにより、再現性よく化学機械研磨の研磨量を抑制することができる。

ゲート電極である金属をエッチバックすることにより、所望のゲート長を持つゲート電極を形成する工程と、

ゲート電極である金属および柱状の第1導電型シリコン層の表面にシリコン酸化膜を成膜する工程と、

を含むことにより、

このシリコン酸化膜により、金属が覆われることにより後工程においてメタル汚染を考慮することなく処理でき、また、ウェット処理またはドライ処理からゲート上面が保護され、ゲート長の変動やゲート上面からのゲート絶縁膜へのダメージを抑制することができる。

所望のゲート電極の膜厚とゲート絶縁膜の膜厚の和からシリコン酸化膜の膜厚を減じた膜厚のシリコン窒化膜を成膜する工程と、

シリコン窒化膜とシリコン酸化膜をエッチバックすることによりシリコン酸化膜サイドウォールとシリコン窒化膜サイドウォールを形成する工程と

を含むことにより、

シリコン窒化膜サイドウォールの膜厚とシリコン酸化膜サイドウォールの膜厚の和が金属からなるゲート電極の膜厚とゲート絶縁膜の膜厚の和となるため、シリコン窒化膜の成膜膜厚及びエッチバック条件を調整することによって、所望の膜厚のゲート電極を形成することができ、