KR930004626B1 - 불휘발성 기억장치 - Google Patents

불휘발성 기억장치 Download PDFInfo

- Publication number

- KR930004626B1 KR930004626B1 KR1019890010763A KR890010763A KR930004626B1 KR 930004626 B1 KR930004626 B1 KR 930004626B1 KR 1019890010763 A KR1019890010763 A KR 1019890010763A KR 890010763 A KR890010763 A KR 890010763A KR 930004626 B1 KR930004626 B1 KR 930004626B1

- Authority

- KR

- South Korea

- Prior art keywords

- transistor

- electrode

- gate

- memory

- drain electrode

- Prior art date

Links

- 238000002347 injection Methods 0.000 claims description 40

- 239000007924 injection Substances 0.000 claims description 40

- 239000003990 capacitor Substances 0.000 claims description 14

- 238000000034 method Methods 0.000 claims description 8

- 239000004065 semiconductor Substances 0.000 claims description 7

- 238000000605 extraction Methods 0.000 claims description 4

- 238000009792 diffusion process Methods 0.000 description 32

- 238000010586 diagram Methods 0.000 description 27

- 230000008859 change Effects 0.000 description 14

- 238000006243 chemical reaction Methods 0.000 description 10

- 230000005684 electric field Effects 0.000 description 10

- 230000004044 response Effects 0.000 description 7

- 239000000758 substrate Substances 0.000 description 6

- 238000004088 simulation Methods 0.000 description 5

- 230000000052 comparative effect Effects 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 3

- 230000010354 integration Effects 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 2

- 230000009471 action Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

- G11C11/5635—Erasing circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5642—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1006—Data managing, e.g. manipulating data before writing or reading out, data bus switches or control circuits therefor

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Read Only Memory (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Abstract

내용 없음.

Description

제1도는 이 발명의 한 실시예에 의한 EEPROM의 구성을 표시하는 개략 블럭도.

제2도는 이 발명의 한 실시예에 의한 1비트의 메모리셀의 구성을 표시하는 개략 회로도.

제3도는 이 발명의 한 실시예에 있어서 메모리 트랜지스터의 게이트 전압과 드레인 전류와의 관계를 표시한 특성도.

제4도는 일반적인 메모리 트랜지스터의 소거 동작시에 있어서 터널 산화막에 관한 전계변화의 시뮬레이션(simulation)에 사용한 전원전압의 파형도.

제5도는 제4도에 표시한 터널 산화막에 관한 전계변화의 시뮬레이션 결과를 표시한 도면.

제6도는 이 발명의 다른 실시예에 의한 메모리 어레이 구성을 표시하는 회로도.

제7도는 이 발명의 다른 실시예에 있어서 1비트의 메모리셀에 관련하는 컬럼래치(column ratch) 및 고전압 스위치의 구성을 표시하는 회로도.

제8도는 이 발명의 다른 실시예에 있어서 입력정보 변환회로 및 정전압 전환회로의 구성을 표시하는 회로도.

제9도는 이 발명의 다른 실시예에 있어서 센스앰프의 구성을 표시하는 회로도.

제10도는 이 발명의 다른 실시예에 있어서 출력정보 변환회로의 구성을 표시하는 회로도.

제11도는 이 발명의 또 다른 실시예에 의한 1비트의 메모리셀에 대응한 기입 종료 센스회로를 중심으로 한 구성을 표시하는 회로도.

제12도는 종래의 EEPROM의 구성을 표시하는 블럭도.

제13도는 종래의 EEPROM의 1비트의 메모리셀 주위의 구성을 표시하는 회로도.

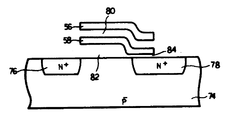

제14도는 일반의 EEPROM의 구조를 표시하는 개략 단면도.

제15도는 종래의 EEPROM의 게이트 전압과 드레인 전류와의 관계를 표시하는 특성도.

* 도면의 주요부분에 대한 부호의 설명

3 : 메모리 트랜지스터 5 : 콘트롤 게이트선

6 : 비트선 7 : 메모리셀

8 : 메모리셀 어레이 9 : 컬럼래치 및 고전압 스위치

12 : Y게이트 회로 40 : 입력정보 변환회로

42 : 출력정보 변환회로 44 : 정전압 전환회로

50 : 센스앰프 56 : 콘트롤 게이트

58 : 플로우팅 게이트

68 : 기입 종료 센스회로, 또한 각 도중, 동일 부호는 동일 또는 상당부분을 표시한다.

이 발명은 전기적으로 소거 및 기입이 가능한 불휘발성 기억장치(EEPROM)에 관하여, 특히 다치정보(多値)를 기억하고, 고집적화에 적합한 불휘발성 기억장치에 관한 것이다.

제12도는 종래의 EEPROM의 개략 블럭구성도이다. 이하, 도면을 참조하여 그 구성에 관하여 설명한다. 이 EEPROM는, 메모리셀(7)을 포함하는 메모리셀 어레이(8)와, 외부에서 입력되는 어드레스 정보를 유지하는 어드레스 버퍼(14)와, 어드레스 버퍼(14)의 신호에 의하여 워드선(1)을 선택하는 X데코더(16)와, 어드레스버퍼(14)의 신호에 의하여 Y게이트회로(12)의 트랜지스터(20), (22)를 선택하는 Y데코더(18)와, 기억동작을 제어하는 제어신호(24)와, 제어신호(24)에 의하여 읽어내기 기입동작의 준비를 제어하는 읽어내기 기입 스텐드바이(stand-by) 제어회로(26)와, 기입신호를 발생하는 기입회로(28)와, 읽어내기 신호를 발생하는 읽어내기 회로(32)와, 기입회로(28)의 신호에 응답하여, 메모리셀 어레이(8)에 인가하는 고전압을 발생시키는 승압회로 및 타이머회로(30)와, 선택된 워드선(1)에 고전압을 인가하는 고전압 스위치(10)와, Y데코더(18)에 의하여 선택된 비트선(6) 및 콘트롤 게이트선(5)에 고전압을 인가하고, 그 고전압 상태를 래치하는 컬럼래치 및 고전압 스위치(9)와, 기입회로(28)의 신호에 의하여 콘트롤 게이트선(5)를 제어하는 콘트롤 게이트회로(46)와, 기입회로(28)의 신호에 의하여 비트선(6)의 전압신호를 제어하는 라이트 드라이버(Write-driver)회로(48)와, 선택된 비트선(6)의 정보를 증폭하는 센스앰프(50)와, 입출력 신호를 유지하는 입출력 버퍼(34)와, 입력신호를 유지하는 입력 버퍼(36)와, 읽어내기 회로(32)와 센스 앰프(50)와의 출력정보에 응답하여, 출력신호를 유지하는 출력 버퍼(38)를 포함한다.

또, 도면에 있어서는 메모리셀 어레이(8) 중에서 1비트선분의 메모리셀(7)의 구성회로가 표시되어 있다. 그 구성에 대하여 이하에 표시한다. Y게이트 회로(12)의 트랜지스터(22)에 접속하는 비트선(6)은, 컬럼래치 및 고전압 스위치(9)에 접속하여 그 접속점과 접지전원과의 사이에 트랜지스터(2), 메모리 트랜지스터(3) 및 트랜지스터(72)가 직렬적으로 접속된다.

Y게이트 회로(12)의 트랜지스터(20)에 접속하는 콘트롤 게이트선(5)은, 컬럼래치 및 고전압 스위치(9)에 접속하고, 그 접속점은 트랜지스터(4)를 거쳐서 콘트롤 게이트선(54)에 의하여 메모리 트랜지스터(3)의 콘트롤 게이트에 접속된다. 트랜지스터(72)의 게이트는, 접속선(70)을 거쳐서 기입회로(28)에 접속된다.

제13도는, 종래의 EEPROM의 1비트분의 메모리 트랜지스터 주위의 회로도이다. 도면에 있어서 센스 앰프(50)와 접지전원과의 사이에, Y게이트 회로(12)에 포함되는 트랜지스터(22), X데코더(16)에 의하여 선택된 트랜지스터(2), 전하가 주입 혹은 빼내어지는 메모리 트랜지스터(3) 및 기입회로(28)의 신호에 의하여 온·오프(ON·OFF)되는 트랜지스터(72)가 직렬로 접속된다.

트랜지스터(22)의 게이트에는, Y데코더(18)로부터의 신호선(52)이 접속된다. 트랜지스터(2)의 게이트에는, X선 데코더(16)에 접속하는 워드선(1)이 접속된다. 메모리 트랜지스터(3)에는, 콘트롤 게이트(56) 및 플로우팅 게이트(58)가 포함되어, 콘트롤 게이트(56)에는 콘트롤 게이트선(54)이 접속된다. 트랜지스터(72)의 게이트에는, 기입회로(28)로부터의 접속선(70)이 접속된다. 또, 트랜지스터(22)와 트랜지스터(2)와의 접속점에는, 고전압 스위치(9a)로부터의 접속선이 접속된다. 고전압 스위치(9a)의 구성은, 전원전압 VPP와 승압펄스 신호 ø1과의 사이에 트랜지스터 Q3와 콘덴서 C1이 직렬로 접속되고, 트랜지스터 Q3와 콘덴서 C1의 사이의 접속점과, 트랜지스터(22)와 트랜지스터(2)와의 접속점(노드 N1)과의 사이에 트랜지스터(Q4)가 접속된다. 트랜지스터(Q3)의 게이트는 노드(N1)와 트랜지스터(Q4)와의 사이의 접속점이 접속된다.

트랜지스터(Q4)의 게이트는, 트랜지스터(Q4)와 노드(N2)와의 사이의 접속점에 접속된다.

이하, 고전압 스위치(9a)의 기능에 대하여 간단히 설명한다.

전원전압 VPP는 트랜지스터(Q3)의 온에 의하면 고전압이 노드(N2)에 인가되어, 다시금 승압펄스 신호 ø1의 승압전압이 노드(N2)에 있어서 겹쳐진다. 그 승압된 전압으로서 트랜지스터(Q4)가 도통되어, 승압된 전압이 노드(N1)에 인가된다. 따라서, 이 승압된 전압은 워드선(1)의 선택에 의하여 온되며는 트랜지스터(2)를 거쳐서 메모리 트랜지스터(3)의 드레인 영역에 인가되는 것이 된다.

제14도는 일반적으로 EEPROM의 메모리 트랜지스터 주위의 개략 단면도이다. 이하 그 구성에 관하여 설명한다. 반도체 기판(74)의 주면에 소정 간격에서 형성된 N+의 드레인 확산영역(78)과 N+의 소스 확산 영역(76)이 형성된다. 소스 확산영역(76)과 드레인 확산영역(78)과의 사이의 채널영역으로 될 반도체 기판(74)의 영역상방에는, 게이트 산화막 B(82)를 거쳐서 플로우팅 게이트(58)가 형성된다.

다시, 플로우팅 게이트(58) 상방에는 게이트 산화막 A(80)을 거쳐서 콘트롤 게이트(56)가 형성된다. 콘트롤 게이트(56) 및 플로우팅 게이트(58)는, 도면에 표시한 것과 같이 드레인 확산영역(78) 상방에 있어서 반도체 기판(74)이 가까워지는 방향으로 변형하고 있다. 따라서, 플로우팅 게이트(58)와 드레인 확산영역(78)과의 사이는 게이트 산화막 B(82)의 두께보다 더욱 접근하고, 그 부분이 터널 산화막(84)이 된다. 이하 EEPROM의 동작에 관하여 설명한다.

우선 소거동작에 관하여 설명한다. 콘트롤 게이트(56)에 정의 고전압(예를들어 20V)을 인가하고, 드레인 확산영역(78), 소스 확산영역(76) 및 반도체 기판(74)의 전위는 0V로 한다. 이 상태에 있어, 플로우팅 게이트(58)에는 터널 산화막(84), 게이트 산화막 A(80) 및 게이트 산화막 B(82)의 각각의 용량으로 나눈 전압(예를들면 14V)가 인가된다. 즉, 이 전압 14V를 터널 산화막(84)의 막의 두께, 예를들면 100Å로 나눈 전계(14㎹/㎝)가 터널 산화막(84)에 인가되는 것이 된다. 따라서, 드레인 확산영역(78) 중의 전자가 이 인가전압에 의한 터널현상에 의하여 플로우팅 게이트(58)에 주입된다. 다음에 기입동작에 관하여 설명한다.

드레인 확산영역(78)에 고전압(예를들어 20V)을 인가하고, 콘트롤 게이트(56) 및 반도체 기판(74)의 전위를 0V로 한다. 여기서 소스 확산영역(76)에 접속하는 트랜지스터(72)를 오프하는 것에 의하여 소스 확산 영역(76)을 플로우팅으로 한다. 이 상태에 있어서, 터널 산화막(84)에는 전술의 소거의 동작일때는 역방향으로 고전계가 인가된다. 따라서, 플로우팅 게이트(58)중의 전자가 이 고전계에 의하여, 터널 산화막(84)을 거쳐서 드레인 확산영역(78)으로 뽑히는 것이 된다.

이것이 플로우팅 게이트(58)가 과잉으로 전자가 뽑힌 상태로 되어, 기입동작이 행하여진다. 이상과 같이, 플로우팅 게이트(58) 중의 전자의 상태에 의하여 정보를 기억할 수가 있다.

다음에 읽어내기 동작에 관하여 설명한다.

드레인 확산영역(78)의 전압을 소정전압(예를들면 1V)에 인가하여 소스 확산영역(76)을 접지하고, 다시 콘트롤 게이트(56)는 0V를 인가한다. 이때의 플로우팅 게이트(58)의 전자의 보유상태에 의하여 생기는 드레인 확산영역(78)과 소스 확산영역(76)과의 사이의 전류를 검지하는 것에 의하여, 정보를 읽어낼 수가 있다. 제15도는, 종래의 EEPROM의 게이트 전압/드레인 전류의 특성을 표시한 도면이다.

그림에 있어, 횡축에는 콘트롤 게이트의 게이트 전압이 잡히고, 종축에는 드레인 확산영역과 소스 확산영역과의 사이에 생기는 드레인 전류가 잡혀져 있다. 그림은 드레인 확산영역의 전압을 1V로 했을 때의 특성이다.

직선(60)은 기입동작이 행하여진 상태로서, 플로우팅 게이트(2)는 전자가 과잉으로 뽑혀진 상태로 되어 있기 때문에 디플레이션(deplation)형으로 되어 있다. 그 스레시홀드(threshold)값은, -4V이다. 한편, 직선(64)은 소거동작이 행하여진 상태에서 플로우팅 게이트 중에는 전자가 주입된 상태로 되어 있기 때문에 인한스멘트(enhancemeant)형으로 되어 있다. 그 스레시홀드 값은 4V이다.

따라서, 읽어내기시에 있어서 콘트롤 게이트에는 0V를 인가하고, 그때의 드레인 전류를 어떤 센스레벨 Isen을 기초로 하여 검지하면 된다. 즉, 드레인 전류가 센스레벨 Isen이상으로 흐르면 “0”, Isen미만이면 “1”의 정보라고 하고, 센스앰프로서 판별할 수가 있다.

상기와 같은 종래의 EEPROM의 메모리 트랜지스터는 이상과 같이 구성되어 있었으므로, 1개의 메모리 트랜지스터에 있어서는, 플로우팅 게이트의 전자의 보유상태에 의하여 정보의 “1” 또는 “0”의 2개의 값 즉, 2값 밖에 기억할 수가 없었다. 이것은, DRAM의 집적도에 대하여 뒤떨어진 EEPROM의 고집적화에 있어 큰 문제로 되어 있었다.

이 발명은, 이같은 과제를 해결하기 위하여 이루어진 것으로서, 종래 2값 밖에 기억되지 않았다고 하는 1개의 메모리 트랜지스터에 3값 이상의 많은 값을 기억할 수 있도록 하여, 대용량의 정보를 기억하는 것을 가능하게 하는 EEPROM를 제공하는 것을 목적으로 한다.

본 발명에 의한 불휘발성 기억장치는, 전하의 주입 및 인발(引拔)이 행하여지는 플로우팅 게이트와, 플로우팅 게이트에 전하를 주입하는 전하주입수단과, 전하주입수단에 의한 전하의 주입량을 제어하는 전하주입량 제어수단과를 구비하고, 주입된 전하의 양에 기초하여 스레시홀드 전압을 결정하는 것이다. 전하주입수단에 의한 전하의 주입량에 의하여, 스레시홀드 전압을 변화시키므로 플로우팅 게이트에 많은 정보를 기억할 수가 있다.

또한 본 발명은 통상의 복수의 메모리셀을 가지는 EEPROM에 적용한 경우, 일반적으로 전하주입수단의 각각은, 공통의 전원전압에 접속된다. 그것 때문에 각 메모리셀에 있어서 기입동작이 행하여지고 있을 때, 1개의 메모리셀의 메모리트랜지스터의 기입이 정지하면 다른 메모리셀의 메모리 트랜지스터의 기입에 영향을 주는 경우가 있다. 이같은 문제를 피하기 위하여, 발명의 불휘발성 기억장치는, 그 불휘발성 기억장치가 복수개 존재하고, 불휘발성 기억장치의 전하주입수단의 각각은 공통의 전원전압에 접속되어, 전하주입수단에 의한 플로우팅 게이트에의 전하의 주입이 정지한 때, 전원전압과의 접속을 해제하는 전원해제 수단을 각각 구비한 것이다. 따라서, 각각의 플로우팅 게이트에의 전하의 주입이 다른 플로우팅 게이트의 전하의 주입에 영향을 주지 않으므로, 플로우팅 게이트의 다치(多値) 정보기억에 있어 신뢰성을 증진시킨다.

상술한 바와 같은 본 발명에 의한 불휘발성 기억장치의 구성을 첨부도면의 참조번호와 함께 기재하면 다음과 같습니다.

본 발명의 일특징에 의한 불휘발성 기억장치는 전하의 주입 및 인발이 행하여지는 플로우팅 게이트(58), 콘트롤 게이트(56), 소스전극(76) 및 드레인전극(78)을 갖는 메모리 트랜지스터(3)를 구비한 메모리셀(7)과, 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전하를 주입하는 주입수단 전하(9, 46, 48)과, 상기 전하주입수단(9, 46, 48)에 의한 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)로의 전하주입량을 제어하기 위한 전하주입량 제어수단(44)을 구비한다.

상기 구성에서, 상기 전하주입수단(9, 46, 48)은 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전하를 주입할 때에 상기 메모리 트랜지스터(3)의 콘트롤 게이트(56)에 정(+)의 고전위를 인가하는 동시에 상기 메모리 트랜지스터(3)의 상기 드레인 전극(78)을 접지전위로 하고, 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)로부터 전하를 인발할 때에 상기 메모리 트랜지스터(3)의 콘트롤 게이트(56)를 접지전위로 하는 동시에 상기 메모리 트랜지스터(3)의 드레인 전극(78)에 정(+)의 고전위를 인가한다.

또한, 상기 전하주입수단(9, 46, 48)은 상기 메모리 트랜지스터(3)의 드레인 전극(78)에 접속되는 소스전극을 갖으며, 게이트 전극과 드레인 전극이 접속된 트랜지스터(Q4)와, 정(+)의 고전위 VPP가 공급되는 고전압노드와 상기 트랜지스터(Q4)의 드레인전극 사이에 접속되어 게이트전극이 상기 트랜지스터(Q4)의 소스전극에 접속된 트랜지스터(Q3)와, 한편의 전극이 상기 트랜지스터(Q4)의 드레인 전극에 접속되고 타방의 전극에는 클록신호 ø1가 인가되는 콘덴서(C1)를 포함하는 고전위 스위치(9a)를 구비한다. 게다가, 상기 전하 주입수단(9, 46, 48)은 제1고전압 스위치(9a)와 제2고전압 스위치(9b)를 구비하되, 상기 제1고전압 스위치(9a)는 상기 메모리 트랜지스터(3)의 드레인 전극(78)에 접속된 소스전극을 갖고 아울러 게이트전극과 드레인 전극이 접속된 제1트랜지스터(Q4)와, 정(+)의 고전압 VPP이 공급된 고전압 노드와 상기 제1트랜지스터(Q4)의 드레인 전극의 사이에 접속된 게이트전극이 상기 제1트랜지스터(Q4)의 소스전극에 접속된 제2트랜지스터(Q3)와, 한쪽의 전극이 상기 제1트랜지스터(Q4)의 드레인 전극에 접속되고 타쪽의 전극에 클록신호 ø1가 인가된 제1콘덴서를 구비하며, 상기 제2고전압 스위치(9b)는 상기 메모리 트랜지스터(3)의 콘트롤 게이트(56)에 접속된 소스전극을 갖되 게이트 전극과 드레인 전극이 접속된 제3트랜지스터와, 정(+)의 고전압 VPP이 공급된 고전압 노드와 상기 제3트랜지스터의 드레인 전극과의 사이에 접속된 게이트 전극이 제3트랜지스터의 소스전극에 접속된 제4트랜지스터와, 한편의 전극이 상기 제3트랜지스터의 드레인 전극에 접속되고 타방의 전극에는 클록신호 ø2가 인가된 콘덴서를 구비한다.

상기 구성에서, 상기 전하주입량 제어수단(44)은, 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전자를 준입할 때에 메모리 트랜지스터(3)의 소스전극(76)을 접지전위로 하고, 상기 메모리 트랜지스터(3)의 플로우팅 게이트(38)에서 전하를 인발할 때에 상기 메모리 트랜지스터(3)의 소스전극(76)에 복수의 정(+)의 전위에서 하나의 정(+)의 전위를 선택적으로 인가하는 정전압 전환회로(44)이다.

본 발명의 다른 특징에 의한 불휘발성 기억장치는, 전하의 주입 및 인발이 행하여지는 플로우팅 게이트(58), 콘트롤 게이트(56), 소스전극(76) 및 드레인 전극(78)을 갖는 메모리 트랜지스터(3)을 구비한 메모리셀(7)을 복수행, 복수열로 배치된 메모리셀 어레이(8)와, 복수열로 배치되어, 각각이 대응된 열에 배치되고, 또한 선택된 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전자를 주입할 때에 이 선택된 메모리 트랜지스터(3)의 드레인 전극(78)을 접지전위로 하며, 상기 선택된 트랜지스터(3)의 플로우팅 게이트(58)에서 잔자를 인발할 때에 상기 메모리 트랜지스터(3)의 드레인 전극(78)에 정(+)의 고전위를 인가하기 위한 복수의 제1고전위 발생수단(9, 48)과, 복수열로 배치되어, 각각이 대응된 열로 배치되고, 또한 선택된 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전자를 주입할 때에 이 선택된 메모리 트랜지스터(3)의 콘트롤 게이트(56)에 정(+)의 고전위를 인가하며, 상기 선택된 메모리 트랜지스터(3)의 플로우팅 게이트(58)에서 전자를 인발할 때에 상기 메모리 트랜지스터(3)의 콘트롤 게이트(56)를 접지전위로 하는 복수의 제2고전위 발생수단(9, 46)과, 선택된 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전자를 주입할 때에 이 선택된 메모리 트랜지스터(3)의 소스전극(76)을 접지전위로 하고, 선택된 메모리 트랜지스터(3)의 플로우팅 게이트(58)에서 전하를 인발할 때에 이 메모리 트랜지스터(3)의 소스전극(76)에 복수의 정(+)의 전위에서 하나의 정(+)의 전위를 선택적으로 인가하는 전하주입량 제어수단(44)을 구비한다.

상기 구성에서, 상기 제1고전위 발생수단(9, 48)의 각각은, 메모리 트랜지스터(3)의 드레인 전극(78)에 접속되어 있는 소스전극을 갖되, 게이트전극과 드레인전극이 접속된 트랜지스터(Q4)와, 정(+)의 고전압 VPP가 공급된 고전압 노드와 상기 트랜지스터(Q4)의 드레인 전극과의 사이에 접속된 게이트전극이 상기 트랜지스터(Q4)의 소스전극에 접속된 트랜지스터(Q3)와, 일단의 전극이 상기 트랜지스터(Q4)의 드레인 전극에 접속되고 타단의 전극에 클록신호 ø1가 인가된 콘덴서(C1)를 맞는 고전압 스위치(9a)를 구비한다.

또한, 상기 제1고전위 발생수단(9, 48)의 각각은, 메모리 트랜지스터(3)의 드레인 전극(78)에 접속된 소스전극을 갖되, 게이트 전극과 드레인 전극이 접속된 제1트랜지스터(Q4)와, 정(+)의 고전압 VPP가 공급된 고전압 노드와 상기 제1트랜지스터(Q4)의 드레인 전극과의 사이에 접속된 게이트 전극이 상기 제1트랜지스터(Q4)의 소스전극에 접속된 제2트랜지스터(Q3)와, 일단의 전극이 제1트랜지스터(Q4)의 드레인 전극에 접속되고 타단의 전극에 클록신호 ø1이 인가된 제1콘덴서(C1)를 갖는 제1고전압 스위치(9a)를 구비하며, 상기 제2고전위 발생수단(9, 46)의 각각은, 상기 메모리 트랜지스터(3)의 콘트롤 게이트(56)에 접속된 소스전극을 갖되, 게이트 전극과 드레인 전극이 접속된 제3트랜지스터와, 정(+)의 고전압 VPP가 공급된 고전압 노드와 제3트랜지스터의 드레인 전극과의 사이에 접속된 게이트 전극이 제3트랜지스터의 소스전극에 접속된 제4트랜지스터와, 일단의 전극이 제3트랜지스터의 드레인 전극에 접속되고 타단의 전극에는 클록신호 ø2가 인가되는 콘덴서를 갖는 제2고전압 스위칭(9b)을 구비한다.

게다가, 상기 전하주입량 제어수단(44)은, 복수열로 배치된 복수의 정전압 전환회로(44)를 구비한다.

[실시예]

제1도는 이 발명의 한 실시예에 의한 EEPROM의 구성을 표시하는 개략 블럭도이다.

이하, 도면을 참조하여 제12도에서 표시한 종래의 EEPROM의 블럭도에 대하여 서로 틀린점에 대하여 설명한다. 우선, 메모리셀(7)의 메모리 트랜지스터(3)의 소스영역은, 종래예와 같이 접지전원에 접속하는 것이 아니고, 정전압 전환회로(44)에 접속하여 있다. 정전압 전환회로(44)는 입력정보 변환회로(40)에 의하여 출력된 신호에 기초하여, 메모리 트랜지스터(3)에의 기입동작시에 있어서 소스영역에 인가하는 전압레벨을 변화시킨다.

입력정보 변환회로(40)는, 입출력 버퍼(34)를 거쳐서 입력 버퍼(36)에서 출력된 입력신호를 기초로 하여 그 신호를 소정의 신호로 변환한다. 센스 앰프(50)에 의하여 출력된 신호는, 출력정보 변환회로(42)를 거쳐 출력 버퍼(38)에 출력된다. 출력정보 변환회로(42)는, 센스 앰프(50)에 의하여 출력된 다치신호를 종래와 같이 2값 신호로 변환하는 것이다.

따라서, 이 실시예에 있어서 입출력 버퍼(34)를 거쳐서 입력 혹은 출력되는 신호는, 종래의 장치에 있어서 입출력 버퍼를 거쳐서 입력 또는 출력되는 신호와 대신하는 것은 아니다.

그것때문에 EEPROM의 주변 기기와의 정보의 교환에 관하여는, 전혀 고려할 필요없이 종래와 같이 기억 유지동작을 가능하게 하는 것이다. 제2도는, 이 발명의 한 실시예로서 종래예의 제13도에 상당하는 1비트의 메모리셀의 구성회로를 간략화하여 표시한 도면이다.

이하, 그림을 참조하여 종래예에 비하여 특징부분에 관하여 설명한다. 콘트롤 게이트(56) 및 플로우팅 게이트(58)를 포함하는 메모리 트랜지스터(3)의 소스 영역은, 전하주입량 제어수단인 정전압 전환회로(44)에 접속된다.

상기 전하주입량 제어수단인 정전압 전환회로(44)는 하기에서 상세히 그 동작이 설명되겠지만, 추후 설명될 전하주입수단(4, 46, 48)에 의해 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)로 주입되는 전하량을 제어하는 기능을 갖는다. 또한, 컬럼 래치 및 고전압 스위치(9)와 콘트롤 게이트 회로(48) 및 라이트 드라이버회로(48)는 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전하를 주입하는 전하주입 수단으로서 기능한다. 즉, 정전압 전환회로(44)는, 앞서 말한 것과 같이 입력신호에 응하여 메모리 트랜지스터(3)의 기입시에 있어서 소스영역의 전압을 임의로 변화시키는 것이다.

제3도는 이 발명의 한 실시예에 있어서 메모리 트랜지스터의 게이트 전압/드레인 전류와의 관계를 표시한 도면이다. 도면에 있어서, 횡축에 메모리트랜지스터의 게이트 전압이 잡히고, 종축에 메모리 트랜지스터의 드레인 전류가 잡혀져 있다. 또, 3종류의 특성을 표시하는 직선(60), (62), (64)이 표시되어 있고, 2종류의 리퍼렌스 레벨(reference level) Iref1, Iref2가 점선으로 표시되어 있다.

이하, 제2도 및 제3도를 참조하여 이 발명의 한 실시예에 있어서 EEPROM의 동작에 관하여 설명한다. 우선, 소거동작에 관하여는 종래예와 같으므로 여기서는 설명을 생략한다. 이 상태에서는 메모리 트랜지스터의 스레시홀드는 4V이며, 제3도에서는 직선(64)으로서 그 특성이 표시되어 있다.

다음에 기입동작에 관하여 설명한다.

정전압 전환회로(44)에 의하여 발생한 전압을 메모리 트랜지스터(3)의 소스 영역에 부여하는 이외는 종래와 같이 행한다. 즉, 콘트롤 게이트(54)에는 0V, 메모리 트랜지스터의 드레인 영역에는, 고전압(예를들면 20V) 및 메모리 트랜지스터(3)의 소스 영역에는, 정전압 전환회로(44)에 의하여 예를들면 2V를 인가한다. 그러면 종래예와 같이, 플로우팅 게이트(58)와 메모리 트랜지스터(3)의 드레인 영역과의 사이의 터널 산화막을 사이에 두고, 터널 현상에 의하여 플로우팅 게이트(58)의 전자가 드레인 확산영역에 뽑힌다. 따라서, 메모리 트랜지스터(3)의 스레시홀드는 서서히 작아져서 나중에는 -2V에 도달한다.

이 상태에 있어서, 소스 확산영역은 2V, 콘트롤 게이트(56)는 0V가 되어, 그 스레시홀드가 -2V로 되어 있으므로 이 메모리 트랜지스터는 온이 된다. 그것때문에 드레인 확산영역과 소스 확산영역에 끼인 반도체 기판의 채널영역에 전류가 흐르기 시작한다. 즉, 고전압 스위치 및 컬럼 스위치(9)에서 트랜지스터(22), (2)를 사이에 두어 메모리 트랜지스터(3)의 방향에 전류가 흐르게 된다.

통상 EEPROM의 고전압의 발생에는, 챠지 펌프(charge pump)라는 승압회로를 사용하고 있기 때문에, 전류공급 능력은 없다. 따라서 메모리 트랜지스터(3)에 전류가 흐르면 승압 회로는 고전압을 유지할 수 없게 되어, 그 고전압의 레벨이 저하한다. 그러면, 터널 산화막에는 충분한 전계가 인가되지 않으므로 그 결과 터널현상은 일어나지 않고, 기입동작이 계속되지 않는다.

다시말하면, 메모리 트랜지스터(3)의 소스 영역에 정전압을 인가하고, 기입을 행하면 메모리 트랜지스터의 채널영역이 도통하기 까지에는, 그 스레시홀드는 디플레이션측에 이동한다. 그러나, 채널영역이 도통하면 기입동작은 그 이상 진전되지 않고 그 상태에서 정지한다.

상기의 예에 있어서는, 이 상태에서의 스레시홀드가 -2V가 되는 것이 되어, 제3도에 있어서 직선(62)으로 표시된 특성이 된다. 똑같이, 메모리 트랜지스터(3)의 소스 확산영역에 전하주입량 제어수단인 정전압 전환회로(44)에 의하여 발생한 전압 예를들면 4V를 가하면, 같은 동작이 행하여져서 스레시홀드가 -4V가 될때까지는, 스레시홀드가 변화하지만 그 이상의 스레시홀드의 변화는 진전하지 않게 된다. 이 상태에서의 스레시홀드는 -4V이며, 제3도에 있어서 직선(60)으로 표시된 특성이 된다.

이같이 상기 정전압 전환회로(44)에 의하여 발생한 소정의 정전압을 메모리 트랜지스터(3)의 소스 확산영역에 인가하여 기입동작을 행하는 것에 의하여, 메모리 트랜지스터의 기입깊이(스레시홀드)를 제어할 수가 있다. 여기서 터널 산화막에 관한 진계변화에 관하여 제4도 및 제5도를 참조하여 설명한다. 제4도는, 소거동작시에 있어서 스레시홀드 변화 및 전계변화의 시뮬레이션에 사용한 전원전압 VPP의 파형도이다. 이것에 의하면 0V에서 20V의 전원전압 VPP에의 상승시간이 600μs로 되어 있다.

제5도는, 스레시홀드 변화와 전계변화와를 시간변화에 대응하여 표시한 도표이다. 그림에 있어서 횡축에 시간변화를 잡고, 오른쪽의 종축에는 스레시홀드 전압, 왼쪽의 종축에는 전계가 각각 잡혀져 있다. 이 시뮬레이션 결과에 의하여, 스레시홀드의 변화는 우선 시간의 변화에 대하여 전계가 크게 변화하고, 그후 이어서 스레시홀드의 변화가 시작되고 있는 것이 표시되어 있다. 그리고 소정시간 경과 후에 있어서는 전계 및 스레시홀드 다같이 그 변화량은 작아져서, 안정된 상태에 자리잡는 것을 알 수 있다. 이 소거시의 시뮬레이션 결과에 의하여, 기입동작시에 있어서도 같은 경향을 표시한다고 생각할 수가 있다. 따라서, 기입시에는 소정시간 경화 후에 있어서는 전계의 변화량이 적어져서, 그것에 수반하여 스레시홀드의 변화량도 극히 미소하게 되어서 어떤 스레시홀드에 자리잡는 것이 된다. 이어서 읽어내기 동작에 관하여 설명한다.

이 경우, 드레인 확산영역에 1V, 콘트롤 게이트(56) 및 소스 확산영역에 0V를 인가한 상태에서 행한다. 제3도에 있어서 소거상태의 특성(64) 또는 기입상태의 특성(60), (62)을 읽어내기 위하여, 센스 앰프(50)에 비교 레벨로서 2종류의 리퍼렌스 레벨 Iref1, Iref2를 설정한다. 이때 메모리 트랜지스터의 소스 확산영역과 드레인 확산 영역과의 사이에 발생하는 드레인 전류 ID가, Iref2<ID일때, 정보의 “1”에 Iref1<ID<Iref2일때 정보의 “2”에 ID<Iref1일때 정보의 “3”에 대응하도록 한다.

이같이 하는 것에 의하여, 종래의 EEPROM이면 2종류의 정보밖에 기억하지 못하였던 것이 “1”, “2” 및 “3”의 3종류의 정보를 기억할 수가 있다. 또한, 상기 실시예에서는 소스 영역에 부여하는 정전압을 2V와 4V와의 2종류로 하고, 소거상태와 합하여 3값의 메모리 정보로 하고 있으나, 소스 확산영역에 부여하는 정전압의 종류를 다시금 증가시키는 것에 의하여 4값, 5값 또는 그 이상의 다치에까지 확장하여 가는 것도 가능하다.

제6도는, 이 발명의 다른 실시예에 의한 메모리셀 어레이의 구성을 표시하는 개략 회로도이다. 이하, 그림을 참조하여 그 구성에 관하여 설명한다. 그림에 있어서, 트랜지스터(2)와 메모리 트랜지스터(3)와에 의하여 구성되는 1비트의 메모리셀(7)이 병렬로 4비트분 구성되어, 다시 그 메모리 트랜지스터(3)의 각각의 콘트롤 게이트에 접속하는 콘트롤 게이트선(54)이 접속되는 트랜지스터(4)와를 합하여 1바이트(66)가 형성된다. 즉, 트랜지스터(2)의 각각은 Y게이트 회로(12)의 Y데코더 접속선(Y1)에 그 게이트가 접속되는 트랜지스터(22)의 각각을 사이에 두고 입출력 I/O0∼I/O3에 접속된다.

트랜지스터(4)는 접속선(Y1)에 그 게이트가 접속되는 트랜지스터(20)를 사이에 두고 콘트롤 게이트 신호 CG에 접속된다. 트랜지스터(4)와 트랜지스터(20)와의 접속점은, 콘트롤 게이트선 CG1을 사이에 두고 컬럼래치 및 고전압 스위치(9)에 접속된다. 트랜지스터(2)와 트랜지스터(22)와의 접속점은, 각각 비트선 BL1,∼BL4를 사이에 두고 래치 및 고전압 스위치(9)의 각각에 접속된다. 메모리 트랜지스터(3)의 소스 영역은, 각각 정전압 전환회로(44)에 접속된다. 같은 요령에 의하여 접속선 Y2∼Yn 및 워드선 X2∼Xm에 대하여 1바이트씩 구성되어, 각각 같이 래치 및 고전압 스위치(9) 및 정전압 전환회로(44)에 접속된다.

이경우 메모리 트랜지스터(3)의 기억정보는 종래의 2값에 대하여 4값으로 있는 것이다. 이 실시예에 있어서는, 종래의 일반의 EEPROM이면 1바이트가 콘트롤 게이트용의 트랜지스터 1개와 8비트분의 메모리셀에 의하여 구성되어 있었던 것에 대하여 콘트롤 게이트용의 트랜지스터 1개와 4비트분의 메모리셀에 의하여 구성되어 있는 것이 된다. 더욱, 정보의 기억용량으로서는 종래예와 틀린 것이 없으므로, 4비트분의 메모리셀이 점하는 영역만큼 점유면적은 작게되어 고집적화가 도모되는 것이 된다.

제7도는 제6도의 콘트롤 게이트선을 포함한 1비트분의 메모리셀에 대한 래치 및 고전압 스위치의 내부회로를 표시한 도면이다. 이하, 도면을 참조하여 그 구성에 관하여 설명한다. 고전압 스위치(9a)의 내부회로에 관하여는, 종래예의 제13도에 표시한 것과 같은 것이므로 여기서의 설명은 생략한다. 각 비트선마다 설치된 제1고전압 스위치(9a)와 콘트롤 게이트선(5)에 설치된 제2고전압 스위치(9b)에 각각 승압된 고전압의 공급전원 VPP가 분기되어서 접속 공급된다.

상기 제1고전압 스위치(9A)와 메모리셀(7)과는 비트선(6)을 사이에 두고 접속되어, 비트선(6)의 도중에는 접지전원과의 사이에 트랜지스터(Q1)가 접속된다. 트랜지스터(Q1)의 게이트에는 리세트 신호(Resert1)가 접속된다. 같이 콘트롤 게이트선(5)의 도중에도, 접지전원과의 사이에 트랜지스터(Q2)가 접속된다. 트랜지스터(Q2)의 게이트에는 리세트 신호(Resert2)가 접속된다. 이들의 리세트 신호의 작용에 의하여, 비트선(6) 및 콘트롤 게이트선(5)의 접지가 가능하게 되어, 기입동작 또는 소거동작 중에 있어서 인가된 비트선(6) 및 콘트롤 게이트선(5)의 고전압의 잔류에 의한 오동작을 방지할 수 있다.

제1고전압 스위치(9a)와 데이타래치(9c)가 트랜지스터(Q5)를 사이에 두고 접속된다. 같이 제2고전압스위치(9b)와 콘트롤 게이트선 래치(9d)도 같이 트랜지스터를 사이에 두고 접속된다. 데이타래치(9c)의 구성은, 전원전압 VPP과 접지전원과의 사이에 트랜지스터(Q6) 및 트랜지스터(Q7)와 트랜지스터(Q8) 및 트랜지스터(Q9)가 각각 직렬로 접속된다. 트랜지스터(Q6), 트랜지스터(Q8)의 각각의 게이트에는, 선택신호가 접속된다. 트랜지스터(Q6)와 트랜지스터(Q7)와의 접속점은 트랜지스터(Q9)의 게이트에 접속되어, 트랜지스터(Q8)와 트랜지스터(Q9)와의 접속점은 트랜지스터(Q7)의 게이트에 접속되어, 플립플롭 회로를 구성한다. 트랜지스터(Q6)와 트랜지스터(Q7)의 접속점은, 또 트랜지스터(Q5)에 접속된다. 콘트롤 게이트선 래치(9d)의 구성도 데이타래치(9c)의 구성과 같다.

이상과 같이 구성되는 것에 의하여, 비트선(6)에 주어진 입출력 신호 I/O는 트랜지스터(Q5)를 사이에 두고 데이타래치(9c)에 도달하고, 거기서 그 신호가 래치된다. 같이 콘트롤 게이트선(5)에 트랜지스터(20)를 사이에 두고 주어진 제어신호 CG는, 콘트롤 게이트선 래치(9d)에 도달하여 그곳에서 그 신호가 래치된다. 제8도는, 제6도에서 표시한 이 발명의 다른 실시예에 있어서 입력정보 변환회로의 정전압 전환회로의 구체적인 구성을 표시하는 회로도이다.

이하, 그림을 참조하여 그 구성에 관하여 설명한다. 입력정보 변환회로(40)의 구성은, D0입력 버퍼(36a)의 출력이 NAND게이트 N1, N2에 입력된다. 또, D0입력버퍼(36a)의 출력은 다시금 인버터 I1을 사이에 두고 NAND게이트 N3, N4에 입력된다. 한편 D1입력 버퍼(36b)의 출력이 NAND게이트 N1, N3에 입력된다. 또, D1입력 버퍼(36b)의 출력은 다시금 인버터 I2를 사이에 두고 NAND게이트 N2, N4에 입력된다. NAND게이트 N1, N2, N3및 N4의 출력은, 각각 인버터 I3, I4, I5및 I6를 사이에 두고 정전압 전환회로(44)에 접속된다.

정전압 전환회로(44)의 구성은, 정전압 회로 A(66a), 정전압 회로 B(66b), 정전압 회로 C(66c) 정전압 회로 D(66d)를 포함한다. 정전압 회로 A(66a)는, 전원전압 VPP와 접지전원과의 사이에 직렬로 접속되는 트랜지스터(Q10), 트랜지스터(Q11) 및 트랜지스터(Q12)를 포함한다. 트랜지스터(Q10), (Q11) 및 (Q12)의 각각의 게이트는, 각각 전원전압 VPP측의 노드에 접속된다. 트랜지스터(Q10) 및 (Q11)과의 접속점은, 트랜지스터(Q13)을 사이에 두고 출력되고, 각각의 정전압 전환회로에 대응하는 메모리 트랜지스터의 소스 확산 영역에 접속된다.

트랜지스터(Q13)의 게이트에는 인버터 I3의 출력이 접속된다. 같이 정전압 회로 B·C·D의 출력도 트랜지스터를 사이에 두고, 트랜지스터(Q13)의 출력측에 접속된다. 정전압 회로 B·C·D의 내부 구성은 기본적으로는 정전압 회로 A와 같다. 그러나 각각 그 트랜지스터의 사이즈를 변화시키는 것에 의하여, 출력되는 전압이 서로 다르다. 여기서, 이 구성에 의하면 종래의 1바이트(D0∼D7의 8비트)분의 정보가 4비트(D0, D1, D2, D3, D4, D5, D6, D7)로서 같이 기억유지되는 것을 알 수 있다. 즉, 제8도는 이 1비트(D0, D1)에 관하여 입력정보의 변환을 표시하는 것이다.

구체적으로는 D0입력 버퍼에는, 종래와 같이 2값의 정보가 입력되고, D1입력 버퍼에도 같이 2값의 정보가 입력된다. 따라서, D0와 D1과의 각각의 2값의 정보의 조합에 의하여 4종류의 정보가 발행하는 것이 된다. 이 4종류의 정보에 기초하여 정전압 전환회로에서 4종류의 정전압의 어느 것인가가 발생하고, 메모리 트랜지스터의 소스 확산영역에 기입시에 있어서 인가된다.

그 결과, D0및 D1의 종래이면 2비트분의 데이타가 1개의 메모리 트랜지스터에 1비트분의 데아타로서 입력되고, 기억유지되는 것이다. 이와같이 하여, 제6도와 같이 종래의 8비트에서 이루어지는 1바이트분의 데이타를 실시예에 있어서는, 4비트에서 이루어지는 1바이트의 구성에 있어서 치환할 수가 있다. 제9도는 제6도에서 표시한 이 발명의 다른 실시예에 있어서 센스 앰프의 구성을 표시하는 회로도이다. 이하, 도면을 참조하여 그 구성에 관하여 설명한다.

센스 앰프는 제6도에서 표시한 입출력 I/O0∼I/O3의 각각의 라인에 관하여 설치되어 있으나, 여기에서는 그중의 1개의 입출력선이 접속하는 센스 앰프에 관하여 설명한다. 입력 출력선 I/O와 전원전압 VPP와의 사이에 트랜지스터(Q12)가 접속된다. 전원전압 VPP와 접지전원과의 사이에 P형 트랜지스터(Q10)와 N형 트랜지스터(Q11)가 직렬로 접속된다. 트랜지스터(Q10) 및 (Q11)의 각각의 게이트는, 트랜지스터(Q12)와 입출력 I/O와의 접속점에 접속된다. 또, 그 접속점과 전원전압 VPP와의 사이에 P형 트랜지스터(Q13)와 N형 트랜지스터(Q14)가 직렬로 접속된다.

트랜지스터(Q13)의 게이트는 접지전원에 접속되고, 트랜지스터(Q12) 및 (Q14)의 게이트는 트랜지스터(Q10) 및 (Q11)의 접속점에 접속된다. 센스 앰프는, 센스 앰프 A(50a), 센스 앰프 B(50b) 및 센스 앰프 C(50c)에 의하여 구성된다. 트랜지스터(Q13)과 (Q14)와의 사이의 접속점은, 센스 앰프 A, B, C에 각각 접속된다. 센스 앰프 A(50a)를 대표로 하고, 그 구성에 관하여 설명한다.

P형 트랜지스터(Q15)와 N형 트랜지스터(Q16)와는, 직렬로 전원전압 VPP에 접속하고, 한편 P형 트랜지스터(Q18)과 N형 트랜지스터(Q19)는 같이 전원전압 VPP에 직접 접속한다. 트랜지스터(Q16) 및 (Q19)는 트랜지스터(Q17)을 사이에 두고 접지전원에 접속한다. 트랜지스터(Q15), 트랜지스터(Q18)의 게이트는 트랜지스터(Q15)와 트랜지스터(Q16)의 접속점에 접속된다. 트랜지스터(Q19)의 게이트에는 비교전위 Vref1이 인가된다.

트랜지스터(Q18)와 트랜지스터(Q19)와의 접속점은 인버터 I7을 사이에 두고 출력신호 SA1이 된다. 센스 앰프 B(50b)와 센스 앰프 C(50c)의 내부 구성은, 기본적으로는 센스 앰프A(50a)와 같다. 단, 비교전위 Vref2 및 Vref3의 전위가 달라, 각각 해당하는 트랜지스터의 게이트에 인가되어 있다. 이하, 이 회로의 기능에 관하여 설명한다.

입출력선 I/O에 발생한 메모리 트랜지스터의 드레인 전류는 소정전위에 변환되어, 트랜지스터(Q16)의 게이트에 인가된다. 트랜지스터(Q16)의 게이트에 인가된 전위와, 비교전위 Vref1의 전위에 응한 신호가, 인버터(I7)를 사이에 두고 출력신호 SA1로서 꺼집어 내어진다. 같이 트랜지스터(Q16)의 게이트에 인가된 전위는 센스 앰프(B) 및 센스 앰프(C)에도 인가된다. 따라서, 비교전위 Vref2 및 Vref3의 전위에 각각 대응한 출력신호 SA2 및 SA3가 같이 출력된다. 이들의 출력신호 SA1, SA2 및 SA3의 신호정보에 의하여, 메모리 트랜지스터에 유지된 4값 정보가 2값 정보로 변환되는 것이다.

제10도는, 제6도에서 표시한 이 발명의 다른 실시예에 있어서 출력정보 변환회로(42)의 개략회로 구성이다. 그림에 있어서, 제9도의 센스 앰프 A∼C의 각각에 의하여 출력신호 SA1∼SA3는, 1비트(D0, D1)로서의 2값 정보로 변환된다. 구체적으로는 출력신호 SA2는 비트 D1의 2값 신호로서 접속되고, 출력신호 SA2, SA1 및 SA3는 각각 NOR게이트 NO1의 입력에 접속되어, NOR게이트 NO1의 출력신호는, 비트 D0의 2값 정보로서 처리된다. 이같이, 종래의 2비트분의 데이타가 1개의 메모리 트랜지스터에 1비트로서 4값 정보로서 채용되고, 그 출력정보가 재차 종래의 2비트의 각 비트마다의 2값 정보로서 꺼집어 내어지는 것이 된다.

제11도는, 이 발명의 또다른 실시예에 있어서 고전압 스위치 주변의 구성을 표시하는 회로도이다. 이하, 도면을 참조하여 그 구성에 관하여 설명한다. 고전압 스위치(9a)의 구성 그것자체는, 앞서 실시예에 있어서 제7도의 고전압 스위치(9a)의 구성과 동일하다. 그러나, 이 실시예에 있어서는 트랜지스터(Q4)와, 트랜지스터(22)와 트랜지스터(2)와의 접속점과의 접속선(비트선 6)중에, 기입 종료 센스앰프(68)가 설치되어 있다. 기입 종료 센스회로(68)의 구성에 관하여 이하 설명한다. 전원전압 VPP와 접지전원과의 사이에 P형 트랜지스터(Q21)과 N형 트랜지스터(Q22)가 직렬로 접속된다. 트랜지스터(Q21), (Q22)의 게이트는, 노드 N3에 접속된다. 전원전압 VPP와 노드 N3와의 사이에 트랜지스터(Q23)가 접속된다.

다시, 전원전압 VPP와 노드 N3과의 사이에 P형 트랜지스터(Q24)와 N형 트랜지스터(Q25)가 직렬로 접속된다. 트랜지스터(Q23), (Q25)의 게이트는 트랜지스터(Q21)과 트랜지스터(Q22)와의 접속점에 접속된다. 트랜지스터(Q24)의 게이트는 접지된다. 전원전압 VPP와 접지전원과의 사이에 P형 트랜지스터(Q26)과 N형 트랜지스터(Q27)이 직렬로 접속된다. 트랜지스터(Q26), (Q27)의 게이트는 트랜지스터(Q24)와 트랜지스터(Q25)와의 접속점에 접속된다. 한편, 노드 N4와 접지전원과의 사이에 트랜지스터(Q20)가 접속된다.

트랜지스터(Q20)의 게이트는, 트랜지스터(Q26)과 트랜지스터(Q27)과의 접속점에 접속된다. 이하, 이 구성에 의한 동작을 설명한다. 메모리 트랜지스터(3)에 기입이 행하여지고 있을 때, 정전압 전환회로(44)에 의하여 설정된 정전압에 응한 스레시홀드 전압에 메모리 트랜지스터(3)가 달하면, 메모리 트랜지스터(3)의 채널 영역에 전류가 흐른다. 따라서, 고전압 스위치(9a)에서 메모리셀을 향하여 비트선(6)에 전류가 흐른다. 그런데 고전압 스위치(9a)에 공급되는 승압된 전원전압 VPP는, 챠지 펌프에 의하여 승압되어 있기 때문에 전원공급 능력은 없다.

또, 제7도에 표시한 것과 같이, 이 전원전압 VPP는 다른 비트선에 대응하는 고전압 스위치에도 고전압을 공급하고 있다. 따라서, 트랜지스터(Q3)가 온(ON)인 상태에서 비트선(6)에 전류가 흐르기 시작하면 그 고전압이 유지하지 못하게 된다. 즉, 1개의 메모리 트랜지스터에 전류가 흐르기 시작하면 고전압의 전위레벨 자체의 값이 내려가버리고 만다. 그것 때문에 다른 비트선에 있어서의 메모리 트랜지스터의 스레시홀드가, 소정레벨에 달하지 않은 경우라 할지라도 그 이상의 기입이 행햐여지지 않게 될 염려가 있다.

이것을 방지하기 위하여는 메모리 트랜지스터(3)의 기입이 종료한 시점에서 트랜지스터(Q3)를 확실하게 오프(OFF)할 필요가 있다. 그것 때문에 설치된 것이, 이 기입종료 센스회로(68)이다. 즉, 기입종료 센스회로(68)에 있어서 비트선(6)의 노드 N3에 흐르는 전류를 검출하고, 그 전류가 어떤 일정한 값 이상이 되는 트랜지스터(Q20)를 오프시킨다. 그러면, 트랜지스터(Q20)이 접속하는 비트라인(6)의 노드 N4의 전위는 접지레벨이 되어, 확실히 트랜지스터(Q3)를 오프시키는 것이 된다. 그 결과, 비트선(6)을 사이에 둔 리크전류를 컷(cut)할 수가 있으므로, 승압된 전원전압 VPP에 영향을 주지 않고, 신뢰할 수 있는 기입동작을 가능하게 하고 있다. 더욱이, 기입종료 센스회로를 설치하는 대신 아래와 같은 고전압 스위치(9a)를 설정하는 것도 가능하다. 메모리 트렌지스터(3)에의 기입동작 종료시에 있어서 비트선의 리크전류를 미리 계산하여 두고, 그 리크 전류를 기초로 노드 N4의 전위를 비트선(6)의 저항 등을 기초로 하여 계산하고, 그 노드 N4의 전위에 의하여 확실히 오프하는 트랜지스터(Q3)를 선정하면 같은 효과를 얻게 된다.

또한, 제6도에서 표시한 실시예에 있어서는 1바이트를 4비트의 메모리셀로서 구성하여 종래의 8비트분의 데이타를 기억하고 있으나, 종래와 같이 1바이트를 8비트의 메모리셀로서 구성하여 종래의 16비트분의 데이타를 기억하는 것도 가능하다. 또, 상기 실시예에서는, EEPROM의 입출력 정보로서의 2값의 데이타를 변환하여 메모리 트랜지스터에 다치정보를 기억하고 있으나, EEPROM의 입출력 정보 자체를 다치 데이타로서 사용할 수 있는 것은 말할 것도 없다.

즉, EEPROM의 주변장치와의 데이타의 주고 받는 것이 2진법에 기초한 디지탈 정보 뿐만 아니라, 3진법 이상의 다치정보로 하는 것에도 적용할 수 있다. 다시금, 상기 실시예에는 N채널형의 EEPROM에 적용하고 있으나, P채널형의 EEPROM에도 같이 이 발명의 사상이 적용할 수 있는 것은 말할 것도 없다.

이상과 같이, 청구범위 1항에 관한 발명에 의하면 기입시에 소스 영역에 정전압을 부여하도록 하고, 그 정전압을 임의로 변화시키는 것에 의하여, 종래 1개의 메모리 트랜지스터에서는 2값의 정보 밖에 기억할 수 없었던 것이, 여러 값의 정보를 기억할 수 있게 되어, 대용량화 또는 고집적화를 도모하는 EEPROM를 얻을 수 있는 효과가 있다. 또, 청구범위 2항에 관한 발명에 의하면 1비트의 메모리 트랜지스터에의 여러값 정보의 기입동작이, 다른 비트에의 기입동작에 영향을 주지 않으므로 신뢰성 높은 EEPROM이 되는 효과가 있다.

Claims (9)

- 전하의 주입 및 인발이 행하여지는 플로우팅 게이트(58), 콘트롤 게이트(56), 소스전극(76) 및 드레인 전극(78)을 갖는 메모리 트랜지스터(3)를 구비한 메모리셀(7)과, 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전하를 주입하는 전하주입수단(9, 46, 48)과, 상기 전하주입수단(9, 46, 48)에 의한 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)로의 전하 주입량을 제어하기 위한 전하주입량 제어수단(44)을 포함하는 불휘발성 기억장치.

- 제1항에 있어서, 상기 전하주입수단(9, 46, 48)은 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전하를 주입할 때에 상기 메모리 트랜지스터(3)의 콘트롤 게이트(56)에 정(+)의 고전위를 인가하는 동시에 상기 메모리 트랜지스터(3)의 상기 드레인 전극(78)을 접지 전위로 하고, 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)로부터 전하를 인발할 때에 상기 메모리 트랜지스터(3)의 콘트롤 게이트(56)를 접지전위로 하는 동시에 상기 메모리 트랜지스터(3)의 드레인 전극(78)에 정(+)의 고전위를 인가하는 것을 특징으로 하는 불휘발성 기억장치.

- 제1항에 있어서, 상기 전하주입수단(9, 46, 48)은 상기 메모리 트랜지스터(3)의 드레인 전극(78)에 접속되는 소스전극을 갖으며, 게이트 전극과 드레인 전극이 접속된 트랜지스터(Q4)와, 정(+)의 고전위 VPP가 공급되는 고전압 노드와 상기 트랜지스터(Q4)의 드레인전극 사이에 접속되어 게이트 전극이 상기 트랜지스터(Q4)의 소스전극에 접속된 트랜지스터(Q3)와, 한편의 전극이 상기 트랜지스터(Q4)의 드레인 전극에 접속되고 타방의 전극에는 클록신호 ø1가 인가되는 콘덴서(C1)를 포함하는 고전위 스위치(9a)를 구비한 것을 특징으로 하는 불휘발성 기억장치.

- 제1항에 있어서, 상기 전하주입수단(9, 46, 48)은 제1고전압 스위치(9a)와 제2고전압 스위치(9b)를 구비하되, 상기 제1고전압 스위치(9a)는 상기 메모리 트랜지스터(3)의 드레인 전극(78)에 접속된 소스전극을 갖고 아울러 게이트전극과 드레인전극이 접속된 제1트랜지스터(Q4)와, 정(+)의 고전압 VPP이 공급된 고전압 노드와 상기 제1트랜지스터(Q4)의 드레인 전극의 사이에 접속된 게이트전극이 상기 제1트랜지스터(Q4)의 소스전극에 접속된 제2트랜지스터(Q3)와, 한쪽의 전극이 상기 제1트랜지스터(Q4)의 드레인 전극에 접속되고 타쪽의 전극에 클록신호 ø1가 인가된 제1콘덴서를 구비하며, 상기 제2고전압 스위치(9b)는 상기 메모리 트랜지스터(3)의 콘트롤 게이트(56)에 접속된 소스전극을 갖되 게이트 전극과 드레인 전극이 접속된 제3트랜지스터와, 정(+)의 고전압 VPP이 공급된 고전압 노드와 상기 제3트랜지스터의 드레인 전극과의 사이에 접속된 게이트 전극이 제3트랜지스터의 소스전극에 접속된 제4트랜지스터와, 한편의 전극이 상기 제3트랜지스터의 드레인 전극에 접속되고 타방의 전극에는 클록신호 ø2가 인가된 콘덴서를 구비한 것을 특징으로 하는 불휘발성 기억장치.

- 제1항 내지 제4항 중 어느 한 항에 있어서, 상기 전하주입량 제어수단(44)은, 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전자를 준입할 때에 메모리 트랜지스터(3)의 소스전극(76)을 접지전위로 하고, 상기 메모리 트랜지스터(3)의 플로우팅 게이트(58)에서 전하를 인발할 때에 상기 메모리 트랜지스터(3)의 소스전극(76)에 복수의 정(+)의 전위에서 하나의 정(+)의 전위를 선택적으로 인가하는 정전압 전환회로(44)인 것을 특징으로 하는 불휘발성 기억장치.

- 전하의 주입 및 인발이 행하여지는 플로우팅 게이트(58), 콘트롤 게이트(56), 소스전극(76) 및 드레인 전극(78)을 갖는 메모리 트랜지스터(3)을 구비한 메모리셀(7)을 복수행, 복수열로 배치된 메모리셀 어레이(8)와, 복수열로 배치되어, 각각이 대응된 열에 배치되고, 또한 선택된 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전자를 주입할 때에 이 선택된 메모리 트랜지스터(3)의 드레인 전극(78)을 접지전위로 하며, 상기 선택된 메모리 트랜지스터(3)의 플로우팅 게이트(58)에서 전자를 인발할 때에 상기 메모리 트랜지스터(3)의 드레인 전극(78)에 정(+)의 고전위를 인가하기 위한 복수의 제1고전위 발생수단(9, 48)과, 복수열로 배치되어, 각각이 대응된 열로 배치되고, 또한 선택된 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전자를 주입할 때에 이 선택된 메모리 트랜지스터(3)의 콘트롤 게이트(56)에 정(+)의 고전위를 인가하며, 상기 선택된 메모리 트랜지스터(3)의 플로우팅 게이트(58)에서 전자를 인발할 때에 상기 메모리 트랜지스터(3)의 콘트롤 게이트(56)를 접지전위로 하는 복수의 제2고전위 발생수단(9, 46)과, 선택된 메모리 트랜지스터(3)의 플로우팅 게이트(58)에 전자를 주입할 때에 이 선택된 메모리 트랜지스터(3)의 소스전극(76)을 접지전위로 하고, 선택된 메모리 트랜지스터(3)의 플로우팅 게이트(58)에서 전하를 인발할 때에 이 메모리 트랜지스터(3)의 소스전극(76)에 복수의 정(+)의 전위에서 하나의 정(+)의 전위를 선택적으로 인가하는 전하주입량 제어수단(44)을 구비한 불휘발성 기억장치.

- 제6항에 있어서, 상기 제1고전위 발생수단(9, 48)의 각각은, 메모리 트랜지스터(3)의 드레인 전극(78)에 접속되어 있는 소스전극을 갖되, 게이트전극과 드레인전극이 접속된 트랜지스터(Q4)와, 정(+)의 고전압 VPP가 공급된 고전압 노드와 상기 트랜지스터(Q4)의 드레인 전극과의 사이에 접속된 게이트전극이 상기 트랜지스터(Q4)의 소스 전극에 접속된 트랜지스터(Q3)와, 일단의 전극이 상기 트랜지스터(Q4)의 드레인 전극에 접속되고 타단의 전극에 클록신호 ø1가 인가된 콘덴서(C1)를 맞는 고전압 스위치(9a)를 구비한 것을 특징으로 하는 불휘발성 기억장치.

- 제6항에 있어서, 상기 제1고전위 발생수단(9, 48)의 각각은, 메모리 트랜지스터(3)의 드레인 전극(78)에 접속된 소스전극을 갖되, 게이트 전극과 드레인 전극이 접속된 제1트랜지스터(Q4)와, 정(+)의 고전압 VPP가 공급된 고전압 노드와 상기 제1트랜지스터(Q4)의 드레인 전극과의 사이에 접속된 게이트 전극이 상기 제1트랜지스터(Q4)의 소스전극에 접속된 제2트랜지스터(Q3)와, 일단의 전극이 제1트랜지스터(Q4)의 드레인 전극에 접속되고 타단의 전극에 클록신호 ø1이 인가된 제1콘덴서(C1)를 갖는 제1고전압스위치(9a)를 구비하며, 상기 제2고전위 발생수단(9, 46)의 각각은, 상기 메모리 트랜지스터(3)의 콘트롤 게이트(56)에 접속된 소스전극을 갖되, 게이트 전극과 드레인 전극이 접속된 제3트랜지스터와, 정(+)의 고전압 VPP가 공급된 고전압 노드와 제3트랜지스터의 드레인 전극과의 사이에 접속된 게이트 전극이 제3트랜지스터의 소스전극에 접속된 제4트랜지스터와, 일단의 전극이 제3트랜지스터의 드레인 전극에 접속되고 타단의 전극에는 클록신호 ø2가 인가되는 콘덴서를 갖는 제2고전압 스위칭(9b)을 구비한 것을 특징으로 하는 불휘발성 기억장치.

- 제6항 내지 제8항중 어느 한 항에 있어서, 상기 전하주입량 제어수단(44)은, 복수열로 배치된 복수의 정전압 전환회로(44)를 구비한 것을 특징으로 하는 불휘발성 반도체 기억장치.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP88-191382 | 1988-07-29 | ||

| JP19138288A JPH07105146B2 (ja) | 1988-07-29 | 1988-07-29 | 不揮発性記憶装置 |

| JP63-191382 | 1988-07-29 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR910003659A KR910003659A (ko) | 1991-02-28 |

| KR930004626B1 true KR930004626B1 (ko) | 1993-06-02 |

Family

ID=16273665

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019890010763A KR930004626B1 (ko) | 1988-07-29 | 1989-07-28 | 불휘발성 기억장치 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US5262984A (ko) |

| JP (1) | JPH07105146B2 (ko) |

| KR (1) | KR930004626B1 (ko) |

| DE (1) | DE3925153A1 (ko) |

Families Citing this family (88)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03296266A (ja) * | 1990-04-13 | 1991-12-26 | Seikosha Co Ltd | 記憶回路および記憶制御装置 |

| US5218569A (en) | 1991-02-08 | 1993-06-08 | Banks Gerald J | Electrically alterable non-volatile memory with n-bits per memory cell |

| US6002614A (en) * | 1991-02-08 | 1999-12-14 | Btg International Inc. | Memory apparatus including programmable non-volatile multi-bit memory cell, and apparatus and method for demarcating memory states of the cell |

| US5541878A (en) * | 1991-05-09 | 1996-07-30 | Synaptics, Incorporated | Writable analog reference voltage storage device |

| US6222762B1 (en) | 1992-01-14 | 2001-04-24 | Sandisk Corporation | Multi-state memory |

| US5657332A (en) | 1992-05-20 | 1997-08-12 | Sandisk Corporation | Soft errors handling in EEPROM devices |

| JP2822791B2 (ja) * | 1992-06-30 | 1998-11-11 | 日本電気株式会社 | 半導体装置 |

| US5359896A (en) * | 1992-09-03 | 1994-11-01 | The United States Of America As Represented By The Administrator Of The National Aeronautics And Space Administration | Acceleration recorder and playback module |

| JPH06318683A (ja) * | 1993-05-01 | 1994-11-15 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| US5432735A (en) * | 1993-07-08 | 1995-07-11 | Dellusa, L.P. | Ternary storage dynamic RAM |

| US5887145A (en) * | 1993-09-01 | 1999-03-23 | Sandisk Corporation | Removable mother/daughter peripheral card |

| US7137011B1 (en) * | 1993-09-01 | 2006-11-14 | Sandisk Corporation | Removable mother/daughter peripheral card |

| US5440505A (en) * | 1994-01-21 | 1995-08-08 | Intel Corporation | Method and circuitry for storing discrete amounts of charge in a single memory element |

| WO1995034075A1 (en) * | 1994-06-02 | 1995-12-14 | Intel Corporation | Sensing schemes for flash memory with multilevel cells |

| US5497354A (en) * | 1994-06-02 | 1996-03-05 | Intel Corporation | Bit map addressing schemes for flash memory |

| US5515317A (en) * | 1994-06-02 | 1996-05-07 | Intel Corporation | Addressing modes for a dynamic single bit per cell to multiple bit per cell memory |

| JP3563452B2 (ja) * | 1994-08-10 | 2004-09-08 | 株式会社東芝 | セル閾値分布検知回路およびセル閾値分布検知方法 |

| US5469384A (en) * | 1994-09-27 | 1995-11-21 | Cypress Semiconductor Corp. | Decoding scheme for reliable multi bit hot electron programming |

| KR970005645B1 (ko) * | 1994-10-01 | 1997-04-18 | 삼성전자 주식회사 | 불휘발성 반도체 메모리의 부분 프로그램을 위한 데이터 로딩회로 |

| US5694356A (en) * | 1994-11-02 | 1997-12-02 | Invoice Technology, Inc. | High resolution analog storage EPROM and flash EPROM |

| FR2728380A1 (fr) * | 1994-12-20 | 1996-06-21 | Sgs Thomson Microelectronics | Procede d'ecriture de donnees dans une memoire et memoire electriquement programmable correspondante |

| JP2629626B2 (ja) * | 1994-12-26 | 1997-07-09 | 日本電気株式会社 | 半導体記憶装置およびその製造方法 |

| KR100566464B1 (ko) | 1995-01-31 | 2006-03-31 | 가부시끼가이샤 히다치 세이사꾸쇼 | 반도체 메모리 장치 |

| US5682496A (en) | 1995-02-10 | 1997-10-28 | Micron Quantum Devices, Inc. | Filtered serial event controlled command port for memory |

| ATE218003T1 (de) * | 1995-02-10 | 2002-06-15 | Micron Technology Inc | Schneller leseverstärker für einen flash-speicher |

| US6108237A (en) | 1997-07-17 | 2000-08-22 | Micron Technology, Inc. | Fast-sensing amplifier for flash memory |

| US6353554B1 (en) | 1995-02-27 | 2002-03-05 | Btg International Inc. | Memory apparatus including programmable non-volatile multi-bit memory cell, and apparatus and method for demarcating memory states of the cell |

| JP2768321B2 (ja) * | 1995-02-28 | 1998-06-25 | 日本電気株式会社 | 半導体記憶装置 |

| KR0152914B1 (ko) * | 1995-04-21 | 1998-12-01 | 문정환 | 반도체 메모리장치 |

| EP0764952B1 (en) * | 1995-07-25 | 2003-02-05 | Texas Instruments Incorporated | An apparatus and method for a data path implemented using non-differential current mode techniques |

| US5572462A (en) * | 1995-08-02 | 1996-11-05 | Aplus Integrated Circuits, Inc. | Multistate prom and decompressor |

| KR100221523B1 (ko) * | 1995-08-31 | 1999-09-15 | 다카노 야스아키 | 다치 정보를 기억 가능한 메모리셀을 갖는 불휘발성 다치 메모리 장치 |

| US5815434A (en) * | 1995-09-29 | 1998-09-29 | Intel Corporation | Multiple writes per a single erase for a nonvolatile memory |

| KR0161867B1 (ko) * | 1995-10-11 | 1998-12-01 | 문정환 | 반도체 소자의 가변 문턱전압 조절회로 |

| US5729489A (en) * | 1995-12-14 | 1998-03-17 | Intel Corporation | Programming flash memory using predictive learning methods |

| US5701266A (en) * | 1995-12-14 | 1997-12-23 | Intel Corporation | Programming flash memory using distributed learning methods |

| US5737265A (en) * | 1995-12-14 | 1998-04-07 | Intel Corporation | Programming flash memory using data stream analysis |

| US5677869A (en) * | 1995-12-14 | 1997-10-14 | Intel Corporation | Programming flash memory using strict ordering of states |

| US5663925A (en) * | 1995-12-18 | 1997-09-02 | Micron Technology, Inc. | Method and apparatus for timing control in a memory device |

| US5680341A (en) * | 1996-01-16 | 1997-10-21 | Invoice Technology | Pipelined record and playback for analog non-volatile memory |

| JP3740212B2 (ja) | 1996-05-01 | 2006-02-01 | 株式会社ルネサステクノロジ | 不揮発性半導体記憶装置 |

| KR100223868B1 (ko) * | 1996-07-12 | 1999-10-15 | 구본준 | 비휘발성 메모리를 프로그램하는 방법 |

| DE69626075T2 (de) * | 1996-07-25 | 2003-10-02 | Texas Instruments Inc | Anordnung und Verfahren zur Ausführung eines Datenpfads mit Gebrauch von nicht differentieller Strommodustechnik |

| EP0825611B1 (en) * | 1996-08-22 | 2003-04-09 | STMicroelectronics S.r.l. | Multilevel non-volatile memory devices |

| JP3204119B2 (ja) * | 1996-09-30 | 2001-09-04 | 日本電気株式会社 | 不揮発性半導体メモリおよびそのデータ書込方法 |

| FR2754100B1 (fr) * | 1996-09-30 | 1998-11-20 | Sgs Thomson Microelectronics | Memoire a acces serie avec securisation de l'ecriture |

| US6081453A (en) * | 1997-04-15 | 2000-06-27 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device |

| US5847991A (en) * | 1997-05-20 | 1998-12-08 | Tong; Hing S. | System for recording voice as analog values programmed into single bit cells EEPROMs or flash EEPROM |

| JP3602294B2 (ja) * | 1997-05-28 | 2004-12-15 | 株式会社ルネサステクノロジ | 半導体メモリおよび情報記憶装置 |

| US5909449A (en) * | 1997-09-08 | 1999-06-01 | Invox Technology | Multibit-per-cell non-volatile memory with error detection and correction |

| US5910914A (en) * | 1997-11-07 | 1999-06-08 | Silicon Storage Technology, Inc. | Sensing circuit for a floating gate memory device having multiple levels of storage in a cell |

| KR100266748B1 (ko) | 1997-12-31 | 2000-10-02 | 윤종용 | 반도체 메모리 장치 및 그 장치의 에러 정정 방법 |

| US6606267B2 (en) * | 1998-06-23 | 2003-08-12 | Sandisk Corporation | High data rate write process for non-volatile flash memories |

| US5969986A (en) * | 1998-06-23 | 1999-10-19 | Invox Technology | High-bandwidth read and write architectures for non-volatile memories |

| JP2000082294A (ja) | 1998-06-23 | 2000-03-21 | Invox Technol | 不揮発メモリ及び不揮発メモリへの書込み方法 |

| KR100299872B1 (ko) * | 1998-06-29 | 2001-10-27 | 박종섭 | 다비트데이터기록제어회로 |

| FR2786910B1 (fr) * | 1998-12-04 | 2002-11-29 | St Microelectronics Sa | Memoire a grille flottante multiniveau |

| US6269017B1 (en) | 1999-03-04 | 2001-07-31 | Macronix International Co., Ltd. | Multi level mask ROM with single current path |

| US6335698B1 (en) | 1999-10-08 | 2002-01-01 | Industrial Technology Research Institute | Programmable analog-to-digital converter with programmable non-volatile memory cells |

| US6363008B1 (en) | 2000-02-17 | 2002-03-26 | Multi Level Memory Technology | Multi-bit-cell non-volatile memory with maximized data capacity |

| US6707713B1 (en) * | 2000-03-01 | 2004-03-16 | Advanced Micro Devices, Inc. | Interlaced multi-level memory |

| EP1193715A1 (en) * | 2000-09-20 | 2002-04-03 | STMicroelectronics S.r.l. | Nonvolatile memory device, having parts with different access time, reliability and capacity |

| US7042770B2 (en) * | 2001-07-23 | 2006-05-09 | Samsung Electronics Co., Ltd. | Memory devices with page buffer having dual registers and method of using the same |

| US6909985B2 (en) * | 2002-11-27 | 2005-06-21 | Lockheed Martin Corporation | Method and apparatus for recording changes associated with acceleration of a structure |

| JP4667719B2 (ja) * | 2003-01-17 | 2011-04-13 | スパンション エルエルシー | 不揮発性多値半導体メモリ |

| US7012835B2 (en) | 2003-10-03 | 2006-03-14 | Sandisk Corporation | Flash memory data correction and scrub techniques |

| US6963506B1 (en) * | 2003-10-03 | 2005-11-08 | Advanced Micro Devices, Inc. | Circuit and technique for accurately sensing low voltage flash memory devices |

| US7173852B2 (en) * | 2003-10-03 | 2007-02-06 | Sandisk Corporation | Corrected data storage and handling methods |

| US7315916B2 (en) | 2004-12-16 | 2008-01-01 | Sandisk Corporation | Scratch pad block |

| US7395404B2 (en) * | 2004-12-16 | 2008-07-01 | Sandisk Corporation | Cluster auto-alignment for storing addressable data packets in a non-volatile memory array |

| KR100602320B1 (ko) * | 2005-05-03 | 2006-07-18 | 주식회사 하이닉스반도체 | 프로그램 속도가 균일한 비휘발성 메모리 소자 |

| WO2006127959A2 (en) * | 2005-05-25 | 2006-11-30 | Thunder Creative Technologies, Inc. | Control signal interface circuit for computer memory modules |

| US7716538B2 (en) | 2006-09-27 | 2010-05-11 | Sandisk Corporation | Memory with cell population distribution assisted read margining |

| US7886204B2 (en) | 2006-09-27 | 2011-02-08 | Sandisk Corporation | Methods of cell population distribution assisted read margining |

| US7573773B2 (en) * | 2007-03-28 | 2009-08-11 | Sandisk Corporation | Flash memory with data refresh triggered by controlled scrub data reads |

| US7477547B2 (en) * | 2007-03-28 | 2009-01-13 | Sandisk Corporation | Flash memory refresh techniques triggered by controlled scrub data reads |

| JP5384012B2 (ja) * | 2008-01-24 | 2014-01-08 | ローム株式会社 | Eepromおよびそれを用いた電子機器 |

| CN102498475A (zh) * | 2009-07-10 | 2012-06-13 | 柰米闪芯积体电路有限公司 | 高速高密度以nand为基础的双晶体管-nor闪存的新构成 |

| JP2011170942A (ja) * | 2010-02-22 | 2011-09-01 | Elpida Memory Inc | 半導体装置 |

| US8687421B2 (en) | 2011-11-21 | 2014-04-01 | Sandisk Technologies Inc. | Scrub techniques for use with dynamic read |

| US9230689B2 (en) | 2014-03-17 | 2016-01-05 | Sandisk Technologies Inc. | Finding read disturbs on non-volatile memories |

| US9552171B2 (en) | 2014-10-29 | 2017-01-24 | Sandisk Technologies Llc | Read scrub with adaptive counter management |

| US9978456B2 (en) | 2014-11-17 | 2018-05-22 | Sandisk Technologies Llc | Techniques for reducing read disturb in partially written blocks of non-volatile memory |

| US9349479B1 (en) | 2014-11-18 | 2016-05-24 | Sandisk Technologies Inc. | Boundary word line operation in nonvolatile memory |

| US9449700B2 (en) | 2015-02-13 | 2016-09-20 | Sandisk Technologies Llc | Boundary word line search and open block read methods with reduced read disturb |

| US9577854B1 (en) | 2015-08-20 | 2017-02-21 | Micron Technology, Inc. | Apparatuses and methods for asymmetric bi-directional signaling incorporating multi-level encoding |

| US9653154B2 (en) | 2015-09-21 | 2017-05-16 | Sandisk Technologies Llc | Write abort detection for multi-state memories |

| US10164817B2 (en) | 2017-03-21 | 2018-12-25 | Micron Technology, Inc. | Methods and apparatuses for signal translation in a buffered memory |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4449203A (en) * | 1981-02-25 | 1984-05-15 | Motorola, Inc. | Memory with reference voltage generator |

| JPS5886777A (ja) * | 1981-11-18 | 1983-05-24 | Citizen Watch Co Ltd | Mnos記憶素子のしきい値電圧の設定方法 |

| US4627027A (en) * | 1982-09-01 | 1986-12-02 | Sanyo Electric Co., Ltd. | Analog storing and reproducing apparatus utilizing non-volatile memory elements |

| JPS5942697A (ja) * | 1982-09-01 | 1984-03-09 | Sanyo Electric Co Ltd | 不揮発性アナログメモリ装置 |

| US4771404A (en) * | 1984-09-05 | 1988-09-13 | Nippon Telegraph And Telephone Corporation | Memory device employing multilevel storage circuits |

| JPS63153799A (ja) * | 1986-08-08 | 1988-06-27 | Nec Corp | 半導体メモリ |

| JPS6342100A (ja) * | 1986-08-08 | 1988-02-23 | Fujitsu Ltd | 3値レベルrom |

| FR2630573B1 (fr) * | 1988-04-26 | 1990-07-13 | Sgs Thomson Microelectronics | Memoire programmable electriquement avec plusieurs bits d'information par cellule |

| US5043940A (en) * | 1988-06-08 | 1991-08-27 | Eliyahou Harari | Flash EEPROM memory systems having multistate storage cells |

| US5172338B1 (en) * | 1989-04-13 | 1997-07-08 | Sandisk Corp | Multi-state eeprom read and write circuits and techniques |

-

1988

- 1988-07-29 JP JP19138288A patent/JPH07105146B2/ja not_active Expired - Lifetime

-

1989

- 1989-07-28 US US07/386,484 patent/US5262984A/en not_active Expired - Lifetime

- 1989-07-28 KR KR1019890010763A patent/KR930004626B1/ko not_active IP Right Cessation

- 1989-07-28 DE DE3925153A patent/DE3925153A1/de active Granted

Also Published As

| Publication number | Publication date |

|---|---|

| KR910003659A (ko) | 1991-02-28 |

| US5262984A (en) | 1993-11-16 |

| DE3925153C2 (ko) | 1992-11-05 |

| DE3925153A1 (de) | 1990-02-01 |

| JPH07105146B2 (ja) | 1995-11-13 |

| JPH0240198A (ja) | 1990-02-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR930004626B1 (ko) | 불휘발성 기억장치 | |

| JP4084922B2 (ja) | 不揮発性記憶装置の書込み方法 | |

| US6269021B1 (en) | Memory cell of nonvolatile semiconductor memory device | |

| EP0255963B1 (en) | Nonvolatile semiconductor memory including means for detecting completion of writing operation | |

| EP0558404A2 (en) | Single transistor flash electrically programmable memory | |

| US4999812A (en) | Architecture for a flash erase EEPROM memory | |

| JP3743453B2 (ja) | 不揮発性半導体記憶装置 | |

| US4543647A (en) | Electrically programmable non-volatile semiconductor memory device | |

| JPS6013398A (ja) | 半導体多値記憶装置 | |

| US6480057B2 (en) | Charge pump circuit allowing efficient electric charge transfer | |

| KR20020003074A (ko) | 다중치 데이터를 저장하는 불휘발성 메모리 | |

| KR19980066245A (ko) | 메모리 셀 당 2개 이상의 저장 상태들을 갖는 불휘발성 반도체 | |

| US6515907B2 (en) | Complementary non-volatile memory circuit | |

| JP3701160B2 (ja) | 冗長機能を有する不揮発性半導体メモリ装置 | |

| KR100242517B1 (ko) | 소거 동작시 간단한 구조의 플래시 메모리 셀에 소거 가능 전압을 공급할 수 있는 비휘발성 반도체 기억 장치 | |

| KR19980032507A (ko) | 저감된 소거 동작 회수를 갖는 멀티레벨 비휘발성 메모리 셀 프로그래밍 방법 | |

| JPH0935488A (ja) | 不揮発性記憶装置 | |

| KR19990014206A (ko) | 불휘발성 반도체 기억장치 | |

| KR100273626B1 (ko) | 다치(多値) 정보를 기록할 수 있는 비휘발성 반도체 메모리 | |

| JP7074417B1 (ja) | 半導体記憶装置 | |

| JP3908432B2 (ja) | 不揮発性半導体記憶装置及びその書き込み方法 | |

| US5546339A (en) | Nonvolatile semiconductor memory device equipped with means for suppressing drain disturbance phenomenon | |

| KR100222811B1 (ko) | 불휘발성 반도체 기억 장치 | |

| JP3103457B2 (ja) | 不揮発性半導体記憶装置及びその書き込み方法ならびに読み出し方法 | |

| JPH06314497A (ja) | 半導体メモリ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20090525 Year of fee payment: 17 |

|

| EXPY | Expiration of term |