KR900005305B1 - 종단 회로의 배선 구조 - Google Patents

종단 회로의 배선 구조 Download PDFInfo

- Publication number

- KR900005305B1 KR900005305B1 KR1019860700477A KR860700477A KR900005305B1 KR 900005305 B1 KR900005305 B1 KR 900005305B1 KR 1019860700477 A KR1019860700477 A KR 1019860700477A KR 860700477 A KR860700477 A KR 860700477A KR 900005305 B1 KR900005305 B1 KR 900005305B1

- Authority

- KR

- South Korea

- Prior art keywords

- lead

- hole

- circuit

- layer

- pattern

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5383—Multilayer substrates

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/111—Pads for surface mounting, e.g. lay-out

- H05K1/112—Pads for surface mounting, e.g. lay-out directly combined with via connections

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

- H01L2924/15192—Resurf arrangement of the internal vias

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3011—Impedance

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/115—Via connections; Lands around holes or via connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09218—Conductive traces

- H05K2201/09227—Layout details of a plurality of traces, e.g. escape layout for Ball Grid Array [BGA] mounting

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09627—Special connections between adjacent vias, not for grounding vias

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10431—Details of mounted components

- H05K2201/10507—Involving several components

- H05K2201/10522—Adjacent components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10621—Components characterised by their electrical contacts

- H05K2201/10689—Leaded Integrated Circuit [IC] package, e.g. dual-in-line [DIL]

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4611—Manufacturing multilayer circuits by laminating two or more circuit boards

- H05K3/4623—Manufacturing multilayer circuits by laminating two or more circuit boards the circuit boards having internal via connections between two or more circuit layers before lamination, e.g. double-sided circuit boards

Abstract

내용 없음.

Description

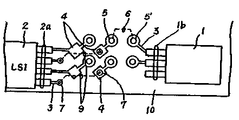

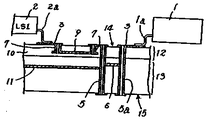

제1도는 본 발명의 종단 회로 배선 구조의 실시예를 설명하기 위하여 주어졌으며,

제1a도는 요부 평면도.

제1b도는 요부 측면 단면도.

제2도는 종래의 종단 회로 배선 구조를 설명하기 위한 것이며,

제2a도는 요부 평면도.

제2b도는 요부 측면 단면도.

* 도면의 주요부분에 대한 부호의 설명

1 : 종단 회로 2 : LSI

3 : 리드(lead)패턴 4 : 본딩 패드(bonding pad)

5 : 관통공 7 : 브라인드(blind) 관통공

8 : 고정 회로 패턴 10 : 다층 프린트 기판

12 : 인출층 13 : 신호층

14 : 부품설치면 15 : 프린트 기판

본 발명은 다층 프린트 기판상에 설치된 종단 회로와 집적 회로(이후 LSI라함) 사이에 배선 구조의 개선에 관한 것이며, 특히 다층 프린트 기판에서 신호층의 배선량을 줄임으로써 프린트 기판의 품질과 성능을 개선하기 위하여 사용되는 종단 회로의 배선 구조에 관한 것이다.

최근에 많은 LSI가 설치된 프린트 기판이 광범위하게 사용되고 있다. 각 LSI가 대응하는 종단 회로를 설치하므로 프린트 기판의 회로 배선이 점점 복잡하게 된다.

특히 일반 회로용 관통공과 종단 회로용 관통공을 접속하는 회로 배선 패턴이 프린트 기판의 신호층에 존재하는 경우에 다음의 문제가 야기된다.

1. 종단 회로와 LSI사이의 도체 임피던스가 높아진다.

2. 신호층의 회로 사이의 간섭이 증가한다. 더우기 상기 언급된 구조에 있어서, 종단 회로로의 요구된 회로 배선의 수가 각 LSI의 배선량의 증가로 불가피하게 증가되므로 프린트 기판에서 신호층의 회로 배선이 점점 복잡하게 되는 그러한 악순환이 일어난다.

본 발명의 목적은 상기 언급된 문제를 해결하기 위한 것이다. 즉 다층 프린트 기판에 신호층의 회로 배선량의 증가를 억제하는 것이다.

본 발명의 관통공을 통하여 전기적으로 접속된 LSI와 종단 회로를 설치하는 다층 프린트 기판에 있어서, 상기 종단 회로와 상기 LSI 및 상기 관통공을 전기적으로 접속하는 회로 배선이 상기 다층 프린트 기판의 표면에 가장 가까운 인출층에 제공된 고정 패턴으로 대체되는 구성을 제공한다.

본 발명의 가장 특이한 특성은 LSI의 회로 배선이 집중되어 있는 신호층내의 회로의 밀집은 기판내의 신호층으로부터 표면 프린트 기판에 가장 가까운 인출층으로 다층 프린트 기판의 종단 회로 배선 패턴의 배선 위치를 이동시킴으로써 완하된다는 것이다.

먼저 본 발명의 기초인 종단 회로의 배선 구조를 제2도를 참조하여 설명하겠다. 제2도는 종래의 종단 회로의 배선 구조를 설명하기 위하여 주여졌다. 제2a도는 요부 평면도이고, 제2b도는 그 측단면도이다. 제2a도와 제2b도는 종래의 가장 전형적인 종단 회로 배선 구조를 나타내고 있다. 이 경우에 회로 배선 패턴 6은 종단 회로용 관통공 5a와 일반적인 회로용 관통공 5를 접속하기 위하여 프린트 기판의 내층의 신호층 13에 제공된다. 제2b도에 도시된 바와 같이, LSI 사이의 일반적인 회로 배선 패턴 11이 신호층 13에 제공된다.

리드 패턴 3, 브라인드 관통공 7, 인출 패턴 9, 본딩 패드 4, 일반 회로용 관통공 5, 회로배선 패턴 6, 및 종단 회로용 관통공 5a과 같은 많은 도체가 다층 프린트 기판 10상에 설치된 종단 회로의 단자 1a와 LSI 2의 신호 단자 2a를 연결하기 위하여 사용된다.

그러므로 일반 회로용 관통공 5와 종단 회로용 관통공 5a를 연결하기 위한 회로 배선 패턴 6이 제2b도에 나타난 바와 같이 상기 프린트 기판의 신호층 13에 존재하고, 상기 언급된 바와 같이 다음 문제가 발생한다.

1. 종단 회로와 LSI 2 사이의 도체 임피던스가 높아진다.

2. 신호층 13내의 회로 사이의 간섭이 증가한다.

본 발명의 종단 회로의 배선 구조에 따르면, 상술한 문제가 해소될 수 있다.

제1도에 나타난 본 발명의 제안된 실시예를 상세히 설명한다.

제1도는 본 발명의 종단 회로 배선구조의 실시예를 설명하기 위하여 주어졌다. 제1a도는 요부 평면도이며, 제1b도는 그 측단면도이다. 주어진 도면을 통하여 동일 대상물은 동일 기회로 표시하였다.

제1a도와 제1b도에 나타난 바와 같이 본 발명의 종단 회로 배선 구조는 다층 프린트 기판의 부품 설치면 14에 가장 가까운 인출층 12내에 브라인드 관통공 7을 통하여 종단 회로 1과 관통공 5를 전기적으로 접속되는 고정 패턴 8이 제공되는 구조이다.

즉 본 발명의 종단 회로 배선 구조는 제2도의 종래 것에 언급된 회로 배선 패턴 6이 신호층 13으로부터 인출층 12로 위치를 이동시킴으로써 고정 회로 패턴 8로 제공되는 것을 특징으로 하고 있다. 그것에 의하여 신호층 13에서 종단 회로 1의 배선은 제거되고 LSI 2와 같은 일반 회로가 종래 것보다 신호층 13에 더 효과적으로 배선된다.

상기 언급된 브라인드 관통공 7은 프린트 기판 10의 압과 뒷면 양쪽을 관통하지 않고 단자 1a와 회로 패턴 8사이를 그리고 리드패턴 3과 본딩 패드 4 및 인출 패턴 9사이를 전기적으로 접속하는 소위 "단족(短足)형"의 특수 관통공이다. 그러므로 이 관통공은 전후면을 관통하는 다른 관통공 5와의 간섭을 피할 수 있고 상기 신호층 13의 여백은 효과적으로 사용될 수 있다는 잇점을 갖는다.

상기 언급한 바와 같이 본 발명의 종단 회로 배선 구조는 다층 프린트 기판의 표면에 가장 가까운 인출층으로 신호층에서 제공된 종단 회로 배선 패턴을 이동시킴으로써 프린트 기판의 신호 배선 밀도를 특히 개선 할 수 있다는 효과를 제공한다.

본 발명에 있어서, 설명된 종단 회로의 배선 구조가 어떤 형태의 다층 프린트 기판에 대하여 사용될 수 있고, 특히 LSI를 설치하는 고밀도 배선 패턴을 가지는 프린트 기판에 사용하는 것이 효과적이다.

Claims (1)

- 관통공(5)(5')에 의하여 내부층 위에 형성된 회로 배선 패턴(6)에 의해 전기적으로 연결된 종단 회로(1)와 신호 단자(2a)를 가지는 집적 회로(2)를 설치하기 위한 다층 프린트 기판(15)의 종단 회로(1)의 배선 구조에 있어서, 상기 배선 구조가 신호층(13), 상기 신호층(13)에 형성된 배선 패턴(11), 상기 신호층(13)위에 형성된 인출층(12), 상기 인출층(12)의 부분에 형성된 인출 패턴(9), 상기 신호층(13)과 상기 인출층(12)을 동하여 확장하는 첫번째 관통공(5), 상기 집적회로(2)의 신호 단자(2a)에 연결되고 상기 인출층(12)위에 형성된 리드 패턴(3), 상기 리드 패턴(3)과 상기 인출 패턴(9)을 연결하고 상기 인출층(12)에 형성된 첫번째 브라인드 관통공(7), 상기 첫번째 브라인드 관통공(7)에 연결되고 상기 인출공(12)위에 형성된 리드 패턴(3), 상기 리드 패턴(3)과 상기 인출 패턴(9)을 연결하고 상기 인출층(12)에 형성된 두번째 브라인드 관통공(7), 상기 종단 회로(1)의 단자(1a)에 연결되고 상기 인출층(12)위에 형성된 리드 패턴(3), 상기 리드 패턴(3)에 연결되고 상기 인출층(12)에 형성된 세번째 브라인드 관통공(7) 및 상기 세번째 브라인드 관통공(7)과 상기 첫번째 광통공(5)을 연결하고 상기 인출층(12)에 형성된 고정 회로 패턴(8)으로 이루어지는 종단 회로의 배선 구조.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP84-253562 | 1984-11-29 | ||

| JP59253562A JPS61131498A (ja) | 1984-11-29 | 1984-11-29 | 終端回路配線構造 |

| PCT/JP1985/000661 WO1986003365A1 (en) | 1984-11-29 | 1985-11-28 | Wiring structure of a terminal circuit |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR880700614A KR880700614A (ko) | 1988-03-15 |

| KR900005305B1 true KR900005305B1 (ko) | 1990-07-27 |

Family

ID=17253090

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019860700477A KR900005305B1 (ko) | 1984-11-29 | 1985-11-28 | 종단 회로의 배선 구조 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US4785141A (ko) |

| EP (1) | EP0204004B1 (ko) |

| JP (1) | JPS61131498A (ko) |

| KR (1) | KR900005305B1 (ko) |

| AU (1) | AU580828B2 (ko) |

| BR (1) | BR8507078A (ko) |

| DE (1) | DE3585445D1 (ko) |

| WO (1) | WO1986003365A1 (ko) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63195772U (ko) * | 1987-06-05 | 1988-12-16 | ||

| US5001605A (en) * | 1988-11-30 | 1991-03-19 | Hughes Aircraft Company | Multilayer printed wiring board with single layer vias |

| DE8903913U1 (ko) * | 1989-03-30 | 1989-05-18 | Siemens Ag, 1000 Berlin Und 8000 Muenchen, De | |

| JPH04109838U (ja) * | 1991-03-08 | 1992-09-24 | オークマ株式会社 | パレツト交換装置におけるパレツト把持装置 |

| US5117331A (en) * | 1991-05-16 | 1992-05-26 | Compaq Computer Corporation | Bus control signal routing and termination |

| US5175515A (en) * | 1991-06-21 | 1992-12-29 | Compaq Computer Corporation | Signal routing technique for electronic systems |

| US5414219A (en) * | 1994-04-22 | 1995-05-09 | At&T Corp. | Printed circuit board circuit control device |

| US7269028B2 (en) * | 1997-10-16 | 2007-09-11 | Celestica, Inc. | Trace-pad interface for improved signal quality |

| US10716210B2 (en) * | 2015-09-15 | 2020-07-14 | Hewlett Packard Enterprise Development Lp | Printed circuit board including through-hole vias |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3243498A (en) * | 1964-12-24 | 1966-03-29 | Ibm | Method for making circuit connections to internal layers of a multilayer circuit card and circuit card produced thereby |

| FR2241946B1 (ko) * | 1973-08-24 | 1976-11-19 | Honeywell Bull Soc Ind | |

| JPS53129863A (en) * | 1977-04-19 | 1978-11-13 | Fujitsu Ltd | Multilayer printed board |

| FR2404990A1 (fr) * | 1977-10-03 | 1979-04-27 | Cii Honeywell Bull | Substrat d'interconnexion de composants electroniques a circuits integres, muni d'un dispositif de reparation |

| US4245273A (en) * | 1979-06-29 | 1981-01-13 | International Business Machines Corporation | Package for mounting and interconnecting a plurality of large scale integrated semiconductor devices |

| FR2555011B1 (fr) * | 1983-11-15 | 1986-01-24 | Thomson Csf | Carte imprimee a empreintes |

| JPS60136294A (ja) * | 1983-12-23 | 1985-07-19 | 株式会社日立製作所 | セラミック多層配線回路板 |

| US4562513A (en) * | 1984-05-21 | 1985-12-31 | International Business Machines Corporation | Process for forming a high density metallurgy system on a substrate and structure thereof |

| US4546413A (en) * | 1984-06-29 | 1985-10-08 | International Business Machines Corporation | Engineering change facility on both major surfaces of chip module |

| JPS61131497A (ja) * | 1984-11-29 | 1986-06-19 | 富士通株式会社 | 多層プリント基板 |

-

1984

- 1984-11-29 JP JP59253562A patent/JPS61131498A/ja active Granted

-

1985

- 1985-11-28 WO PCT/JP1985/000661 patent/WO1986003365A1/ja active IP Right Grant

- 1985-11-28 EP EP85906087A patent/EP0204004B1/en not_active Expired - Lifetime

- 1985-11-28 DE DE8585906087T patent/DE3585445D1/de not_active Expired - Fee Related

- 1985-11-28 AU AU51938/86A patent/AU580828B2/en not_active Ceased

- 1985-11-28 BR BR8507078A patent/BR8507078A/pt not_active IP Right Cessation

- 1985-11-28 KR KR1019860700477A patent/KR900005305B1/ko not_active IP Right Cessation

-

1987

- 1987-11-18 US US07/124,418 patent/US4785141A/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| AU5193886A (en) | 1986-06-18 |

| BR8507078A (pt) | 1987-03-31 |

| AU580828B2 (en) | 1989-02-02 |

| EP0204004A4 (en) | 1987-07-30 |

| DE3585445D1 (de) | 1992-04-02 |

| US4785141A (en) | 1988-11-15 |

| WO1986003365A1 (en) | 1986-06-05 |

| EP0204004B1 (en) | 1992-02-26 |

| JPH0227836B2 (ko) | 1990-06-20 |

| KR880700614A (ko) | 1988-03-15 |

| EP0204004A1 (en) | 1986-12-10 |

| JPS61131498A (ja) | 1986-06-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP0379686B1 (en) | Printed circuit board | |

| US4856184A (en) | Method of fabricating a circuit board | |

| US5220135A (en) | Printed wiring board having shielding layer | |

| KR900005305B1 (ko) | 종단 회로의 배선 구조 | |

| US3568312A (en) | Method of making printed circuit boards | |

| KR20010062723A (ko) | 프린트기판 및 그 전기부품설치방법 | |

| JP2846803B2 (ja) | 多層配線基板 | |

| JPS6120397A (ja) | 多層プリント回路板 | |

| JPH057072A (ja) | プリント配線板 | |

| JPH05152702A (ja) | プリント配線板 | |

| JP2000244128A (ja) | 多層プリント配線基板及びそれを用いたチップ型3端子ノイズフィルタの実装構造 | |

| JPH0231800Y2 (ko) | ||

| JPH01789A (ja) | 超電導配線プリント板 | |

| JP2943987B2 (ja) | 電子部品搭載用基板 | |

| JPH06314885A (ja) | プリント多層配線基板モジュール | |

| JPH08779Y2 (ja) | 多層プリント板 | |

| JPS6240460Y2 (ko) | ||

| JPH0429585Y2 (ko) | ||

| JP2755029B2 (ja) | 多層印刷配線板 | |

| JP2908918B2 (ja) | 厚膜薄膜混成多層回路基板 | |

| JPH03255691A (ja) | プリント配線板 | |

| JPH05267851A (ja) | 多層印刷配線板 | |

| JPH06350216A (ja) | プリント基板 | |

| JPH04349698A (ja) | 高速回路用多層配線板 | |

| JPS60127798A (ja) | 多層プリント配線基板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 19930507 Year of fee payment: 4 |

|

| LAPS | Lapse due to unpaid annual fee |