KR20180098343A - 단결정층, 특히 압전층의 제조방법 - Google Patents

단결정층, 특히 압전층의 제조방법 Download PDFInfo

- Publication number

- KR20180098343A KR20180098343A KR1020187021267A KR20187021267A KR20180098343A KR 20180098343 A KR20180098343 A KR 20180098343A KR 1020187021267 A KR1020187021267 A KR 1020187021267A KR 20187021267 A KR20187021267 A KR 20187021267A KR 20180098343 A KR20180098343 A KR 20180098343A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- substrate

- composition

- single crystal

- donor substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B25/00—Single-crystal growth by chemical reaction of reactive gases, e.g. chemical vapour-deposition growth

- C30B25/02—Epitaxial-layer growth

- C30B25/18—Epitaxial-layer growth characterised by the substrate

- C30B25/186—Epitaxial-layer growth characterised by the substrate being specially pre-treated by, e.g. chemical or physical means

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N30/00—Piezoelectric or electrostrictive devices

- H10N30/01—Manufacture or treatment

- H10N30/09—Forming piezoelectric or electrostrictive materials

- H10N30/093—Forming inorganic materials

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B25/00—Single-crystal growth by chemical reaction of reactive gases, e.g. chemical vapour-deposition growth

- C30B25/02—Epitaxial-layer growth

- C30B25/18—Epitaxial-layer growth characterised by the substrate

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B29/00—Single crystals or homogeneous polycrystalline material with defined structure characterised by the material or by their shape

- C30B29/10—Inorganic compounds or compositions

- C30B29/16—Oxides

- C30B29/22—Complex oxides

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B29/00—Single crystals or homogeneous polycrystalline material with defined structure characterised by the material or by their shape

- C30B29/10—Inorganic compounds or compositions

- C30B29/16—Oxides

- C30B29/22—Complex oxides

- C30B29/30—Niobates; Vanadates; Tantalates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02587—Structure

- H01L21/0259—Microstructure

- H01L21/02598—Microstructure monocrystalline

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H01L41/047—

-

- H01L41/09—

-

- H01L41/312—

-

- H01L41/316—

-

- H01L41/319—

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H9/00—Networks comprising electromechanical or electro-acoustic elements; Electromechanical resonators

- H03H9/02—Details

- H03H9/02007—Details of bulk acoustic wave devices

- H03H9/02015—Characteristics of piezoelectric layers, e.g. cutting angles

- H03H9/02031—Characteristics of piezoelectric layers, e.g. cutting angles consisting of ceramic

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H9/00—Networks comprising electromechanical or electro-acoustic elements; Electromechanical resonators

- H03H9/02—Details

- H03H9/02535—Details of surface acoustic wave devices

- H03H9/02543—Characteristics of substrate, e.g. cutting angles

- H03H9/02574—Characteristics of substrate, e.g. cutting angles of combined substrates, multilayered substrates, piezoelectrical layers on not-piezoelectrical substrate

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H9/00—Networks comprising electromechanical or electro-acoustic elements; Electromechanical resonators

- H03H9/46—Filters

- H03H9/54—Filters comprising resonators of piezoelectric or electrostrictive material

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H9/00—Networks comprising electromechanical or electro-acoustic elements; Electromechanical resonators

- H03H9/46—Filters

- H03H9/64—Filters using surface acoustic waves

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N30/00—Piezoelectric or electrostrictive devices

- H10N30/01—Manufacture or treatment

- H10N30/07—Forming of piezoelectric or electrostrictive parts or bodies on an electrical element or another base

- H10N30/072—Forming of piezoelectric or electrostrictive parts or bodies on an electrical element or another base by laminating or bonding of piezoelectric or electrostrictive bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N30/00—Piezoelectric or electrostrictive devices

- H10N30/01—Manufacture or treatment

- H10N30/07—Forming of piezoelectric or electrostrictive parts or bodies on an electrical element or another base

- H10N30/074—Forming of piezoelectric or electrostrictive parts or bodies on an electrical element or another base by depositing piezoelectric or electrostrictive layers, e.g. aerosol or screen printing

- H10N30/076—Forming of piezoelectric or electrostrictive parts or bodies on an electrical element or another base by depositing piezoelectric or electrostrictive layers, e.g. aerosol or screen printing by vapour phase deposition

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N30/00—Piezoelectric or electrostrictive devices

- H10N30/01—Manufacture or treatment

- H10N30/07—Forming of piezoelectric or electrostrictive parts or bodies on an electrical element or another base

- H10N30/074—Forming of piezoelectric or electrostrictive parts or bodies on an electrical element or another base by depositing piezoelectric or electrostrictive layers, e.g. aerosol or screen printing

- H10N30/079—Forming of piezoelectric or electrostrictive parts or bodies on an electrical element or another base by depositing piezoelectric or electrostrictive layers, e.g. aerosol or screen printing using intermediate layers, e.g. for growth control

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N30/00—Piezoelectric or electrostrictive devices

- H10N30/20—Piezoelectric or electrostrictive devices with electrical input and mechanical output, e.g. functioning as actuators or vibrators

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N30/00—Piezoelectric or electrostrictive devices

- H10N30/80—Constructional details

- H10N30/85—Piezoelectric or electrostrictive active materials

- H10N30/853—Ceramic compositions

- H10N30/8542—Alkali metal based oxides, e.g. lithium, sodium or potassium niobates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N30/00—Piezoelectric or electrostrictive devices

- H10N30/80—Constructional details

- H10N30/87—Electrodes or interconnections, e.g. leads or terminals

-

- H10P14/3458—

-

- H10P90/1916—

-

- H10W10/181—

-

- C—CHEMISTRY; METALLURGY

- C01—INORGANIC CHEMISTRY

- C01G—COMPOUNDS CONTAINING METALS NOT COVERED BY SUBCLASSES C01D OR C01F

- C01G31/00—Compounds of vanadium

- C01G31/02—Oxides

-

- C—CHEMISTRY; METALLURGY

- C01—INORGANIC CHEMISTRY

- C01G—COMPOUNDS CONTAINING METALS NOT COVERED BY SUBCLASSES C01D OR C01F

- C01G33/00—Compounds of niobium

-

- C—CHEMISTRY; METALLURGY

- C01—INORGANIC CHEMISTRY

- C01G—COMPOUNDS CONTAINING METALS NOT COVERED BY SUBCLASSES C01D OR C01F

- C01G35/00—Compounds of tantalum

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Materials Engineering (AREA)

- Crystallography & Structural Chemistry (AREA)

- Manufacturing & Machinery (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Inorganic Chemistry (AREA)

- Physics & Mathematics (AREA)

- Acoustics & Sound (AREA)

- Ceramic Engineering (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Surface Acoustic Wave Elements And Circuit Networks Thereof (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Crystals, And After-Treatments Of Crystals (AREA)

- Piezo-Electric Or Mechanical Vibrators, Or Delay Or Filter Circuits (AREA)

- Silicates, Zeolites, And Molecular Sieves (AREA)

Abstract

Description

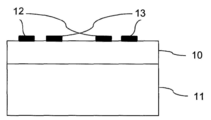

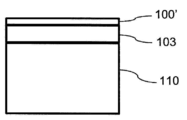

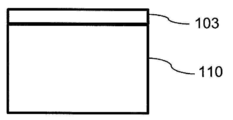

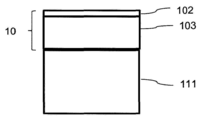

도 1은 표면 음향파 필터의 단면 기능도이며,

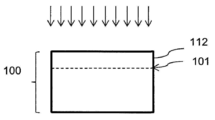

도 2는 벌크 음향파 필터의 단면 기능도이며,

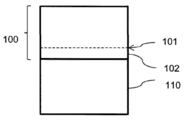

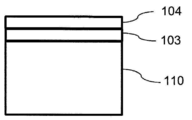

도 3a 내지 3e는 본 발명의 제1 실시 예에 따른 단결정 층을 제조하는 방법의 연속적인 단계들을 보여주며,

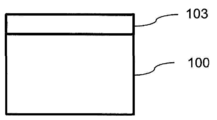

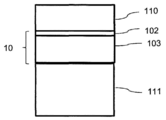

도 4a 내지 4e는 본 발명의 제2 실시 예에 따른 단결정 층을 제조하는 방법의 연속적인 단계들을 보여주며,

도 4f는 도 4a 내지 4e에 도시된 실시 예의 변형으로 구현된 부가적인 단계를 보여주며,

도 5a 내지 도 5c는 상기 단계의 선택적인 연속 단계들을 보여준다.

도면들의 판독성을 위해, 도시된 요소들은 반드시 스케일로 나타내지는 않았다. 상이한 도면들에서 동일한 참조 부호들에 의해 지시 된 요소들은 동일하다.

| 씨드층 | 0.5 ㎛ | 0.05 ㎛ | 0.1 ㎛ | 0.03 ㎛ |

| 에피택셜층 | 2.5 ㎛ | 0.95 ㎛ | 5 ㎛ | 0.15 ㎛ |

Claims (29)

- 단결정 층(10)의 제조 방법으로서,

- 조성 ABO3의 압전 물질을 포함하는 도너 기판(100)을 제공하는 단계로서, 여기서 A는 Li, Na, K, H 중의 적어도 하나의 원소로 구성되며, B는 Nb, Ta, Sb, V 중의 적어도 하나의 원소로 구성되는, 상기 제공하는 단계;

- 리시버 기판(110)을 공급하는 단계;

- 상기 리시버 기판 상에 상기 도너 기판을 결합시킴으로써 상기 리시버 기판(110) 상으로 상기 도너 기판(100)으로부터 "씨드층"이라 지칭되는 층(102)을 전사하는 단계로서, 상기 씨드층(102)은 결합 계면에 있게 하며, 상기 씨드층(102)까지 상기 도너 기판(100)의 박막화(thinning)가 이어지는, 상기 전사하는 단계;

- 상기 씨드층(102)의 압전 물질 ABO3 상에 에피택시에 의해 조성 A'B'O3의 단결정층(103)을 성장시키는 단계로서, 여기서 A'는 다음 원소들 Li, Na, K, H 중의 적어도 하나로 구성되며, B'는 다음 원소들 Nb, Ta, Sb, V 중의 적어도 하나로 구성되며, A'는 A와 상이하거나 또는 B'는 B와 상이한, 상기 성장시키는 단계;

를 연속적으로 포함하는 것을 특징으로 하는 단결정 층의 제조 방법. - 청구항 1에 있어서,

A'는 A와 마찬가지로 적어도 하나의 원소를 포함하며, 및/또는 B'는 B와 마찬가지로 적어도 하나의 원소를 포함하는 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 1에 있어서,

B'가 B와 상이할 경우 A'는 A와 동일하며, 그리고 A'가 A와 상이할 경우 B'는 B와 동일한 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 1 내지 청구항 3 중의 어느 한 항에 있어서,

A는 단일 원소로 구성되며, 그리고 B도 단일 원소로 구성되는 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 1 내지 청구항 4 중의 어느 한 항에 있어서,

상기 씨드층(102)을 전사하는 단계는,

- 상기 조성 ABO3의 압전 물질을 포함하며, 상기 씨드층이라 지칭되는 층을 제한하도록 상기 도너 기판(100)에 취성 영역(101)을 형성하는 단계;

- 상기 씨드층(102)이 결합 계면에 있도록, 상기 리시버 기판(110) 상에 상기 도너 기판(100)을 결합시키는 단계;

- 상기 씨드층(102)을 상기 리시버 기판(110) 상으로 전사하기 위해 상기 취성 영역(101)을 따라 상기 도너 기판(100)을 분리하는 단계;

를 포함하는 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 5에 있어서,

상기 에피택시의 단계 전에, 상기 리시버 기판(110) 상으로 전사된 상기 씨드층(102)의 두께의 일부가 제거되는 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 1 내지 청구항 6 중의 어느 한 항에 있어서,

상기 씨드층(102)의 두께는 2 ㎛ 미만이며, 바람직하게는 1 ㎛ 미만인 것을 특징으로 하는 단결정 층의 제조 방법. - 청구항 1 내지 청구항 7 중의 어느 한 항에 있어서,

상기 리시버 기판은 반도체 물질로 이루어지며, 그리고 상기 씨드층과 상기 리시버 기판 사이에 중간 전하-트랩핑 층을 포함하는 것을 특징으로 하는 단결정 층의 제조방법. - 단결정 층(10)의 제조 방법으로서,

- 조성 A'B'O3의 압전 물질을 포함하는 도너 기판(100)을 제공하는 단계로서, 여기서 A'는 다음 원소들 Li, Na, K, H 중의 적어도 하나 이상으로 구성되며, B'는 다음 원소들 Nb, Ta, Sb, V 중의 적어도 하나 이상으로 구성되는, 상기 제공하는 단계;

- 상기 압전 물질 A'B'O3 상에 에피택시에 의해 조성 A''B''O3의 단결정층(103)을 성장시키는 단계로서, 여기서 A''는 다음 원소들 Li, Na, K, H 중의 하나 이상으로 구성되며, B''는 다음 원소들 Nb, Ta, Sb, V 중의 하나 이상으로 구성되는, 상기 성장시키는 단계;

- 리시버 기판(110)을 공급하는 단계;

- 에피택셜 층(103)을 통하여 상기 리시버 기판(110) 상에 상기 도너 기판(100)을 결합시킴으로써 상기 리시버 기판(110) 상으로 조성 A''B''O3의 상기 에피택셜 층(103)의 적어도 일부를 전사하는 단계로서, 조성 A''B''O3의 상기 에피택셜 층(103)까지 상기 도너 기판(100)의 박막화가 이어지는, 상기 전사하는 단계;

를 연속적으로 포함하는 것을 특징으로 하는 단결정 층의 제조 방법. - 청구항 9에 있어서,

조성 A''B''O3의 층(103)이 상기 리시버 기판 상으로 전사된 후에, 상기 조성 A''B''O3의 물질 상에, 에피택시에 의해 조성 A'''B'''O3의 단결정 층(104)을 성장시키는 단계를 포함하며, 여기서 A'''는 다음 원소들 Li, Na, K, H 중의 하나 이상으로 구성되며, B'''는 다음 원소들 Nb, Ta, Sb, V 중의 하나 이상으로 구성되는, 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 10에 있어서,

A'''는 A''와 상이하거나 또는 B'''는 B''와 상이한 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 9 내지 청구항 11 중의 어느 한 항에 있어서,

상기 리시버 기판(110) 상으로 조성 A''B''O3의 상기 에피택셜층(103)의 적어도 일부를 전사하는 단계는,

- 전사되어지는 층을 제한하기 위해, 상기 도너 기판(100) 내에 또는 조성 A''B''O3의 상기 에피택셜층(103) 내에 취성 영역(101)을 형성하는 단계;

- 조성 A''B''O3의 상기 에피택셜층(103)이 결합 계면에 있도록, 상기 리시버 기판(110) 상에 상기 도너 기판(100)을 결합시키는 단계;

- 상기 취성 영역(101)을 따라 상기 도너 기판(100) 또는 상기 에피택셜층(103)을 분리하는 단계;

를 포함하는 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 12에 있어서,

상기 취성 영역(101)은 상기 도너 기판(100) 내에 형성되며, 상기 전사하는 단계 후에, 전사된 상기 층(100',100)은 조성 A''B''O3의 물질을 노출시키도록 박막화되는 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 9 내지 청구항 13 중의 어느 한 항에 있어서,

A''는 A'와 상이하거나 또는 B''는 B'와 상이한 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 9 내지 청구항 13 중의 어느 한 항에 있어서,

A''는 A'와 마찬가지로 적어도 하나의 원소를 포함하며, 및/또는 B''는 B'와 마찬가지로 적어도 하나의 원소를 포함하는 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 9 내지 청구항 13 중의 어느 한 항에 있어서,

B''가 B'와 상이할 경우 A''는 A'와 동일하며, 그리고 A''가 A'와 상이할 경우 B''는 B'와 동일한 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 9 내지 청구항 16 중의 어느 한 항에 있어서,

A'는 단일 원소로 구성되며, 그리고 B'도 단일 원소로 구성되는 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 5 또는 청구항 12에 있어서,

상기 취성 영역(101)은 상기 도너 기판(100) 내에 이온 주입에 의해 형성되는 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 1 내지 청구항 18 중의 어느 한 항에 있어서,

에피택시 단계 후에, 조성 A''B''O3의 단결정 층(103)의 두께는 0.2 내지 20 ㎛ 인 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 1 내지 청구항 19 중의 어느 한 항에 있어서,

상기 리시버 기판과 상기 도너 기판 사이의 계면에 적어도 하나의 전기적 절연층 및/또는 적어도 하나의 전기적 도전층이 형성되는 것을 특징으로 하는 단결정 층의 제조방법. - 청구항 1 내지 청구항 20 중의 어느 한 항에 있어서,

최종 기판(111) 상으로 상기 리시버 비판의 단결정 층(103,104)의 적어도 일부를 전사시키는 단계를 포함하는 것을 특징으로 하는 단결정 층의 제조방법. - 마이크로일렉트로닉, 포토닉 또는 옵티컬 장치를 위한 기판으로서,

지지 기판(110),

상기 지지 기판 상에 조성 A''B''O3의 단결정 층(103)으로서, 여기서 A''는 다음 원소들 Li, Na, K, H 중의 하나 이상으로 구성되며, B''는 다음 원소들 Nb, Ta, Sb, V 중의 하나 이상으로 구성되며, A'' 및 B'' 중의 적어도 하나는 적어도 두개의 원소들로 구성되는, 상기 단결정 층(103),

그리고 상기 지지 기판(110)과 조성 A''B''O3의 상기 층(103) 사이에 조성 A'B'O3의 층(102)으로서, 여기서 A'는 다음 원소들 Li, Na, K, H 중의 적어도 하나의 원소로 구성되며, B'는 다음 원소들 Nb, Ta, Sb, V 중의 적어도 하나의 원소로 구성되는, 상기 층(102),을 포함하는 것을 특징으로 하는 기판. - 청구항 22에 있어서,

조성 A''B''O3의 상기 층(103) 상에, 조성 A'''B'''O3의 단결정 층(104)을 더 포함하며, 여기서 A'''는 다음 원소들 Li, Na, K, H 중의 하나 이상으로 구성되며, B'''는 다음 원소들 Nb, Ta, Sb, V 중의 하나 이상으로 구성되는 것을 특징으로 하는 기판. - 단결정 압전층(10)의 표면에 전극들(12,13)을 퇴적하는 단계를 포함하는 표면 음향파 장치의 제조방법으로서, 청구항 1 내지 청구항 21 중의 어느 하나의 청구항에 따른 제조방법에 의하여 상기 압전층을 제조하는 것을 포함하는 것을 특징으로 하는 표면 음향파 장치의 제조방법.

- 표면 음향파 장치로서,

청구항 1 내지 청구항 21 중의 어느 하나의 청구항에 따른 제조방법에 의해 얻어질 수 있는 단결정 압전층(10), 및

상기 단결정 압전층의 표면에 형성된 두개의 전극들(12,13)을 포함하는 것을 특징으로 하는 표면 음향파 장치. - 단결정 압전층(10)의 두 개의 반대측 면들 상에 전극들(12,13)을 퇴적하는 단계를 포함하는 벌크 음향파 장치의 제조방법으로서, 청구항 1 내지 청구항 21 중의 어느 하나의 청구항에 따른 제조방법에 의하여 상기 압전층을 제조하는 것을 포함하는 것을 특징으로 하는 벌크 음향파 장치의 제조방법.

- 벌크 음향파 장치로서,

청구항 1 내지 청구항 21 중의 어느 하나의 청구항에 따른 제조방법에 의해 얻어질 수 있는 단결정 압전층(10), 및

상기 단결정 압전층의 두 개의 반대측 면들에 형성된 두 개의 전극들(12,13)을 포함하는 것을 특징으로 하는 벌크 음향파 장치. - 외부 응력에 의해 야기된 변형을 측정하기 위해 설계된 마이크로-센서로서, 청구항 1 내지 청구항 21 중의 어느 하나의 청구항에 따른 제조방법에 의해 얻어질 수 있는 단결정 압전층(10)을 포함하는 것을 특징으로 하는 마이크로-센서.

- 연속적 또는 가변적 전기장의 인가를 통하여, 성분의 변형 또는 이동 부분의 이동을 야기하도록 설계된 마이크로-액츄에이터로서, 청구항 1 내지 청구항 21 중의 어느 하나의 청구항에 따른 제조방법에 의해 얻어질 수 있는 단결정 압전층(10)을 포함하는 것을 특징으로 하는 마이크로-액츄에이터.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| FR1563055A FR3045677B1 (fr) | 2015-12-22 | 2015-12-22 | Procede de fabrication d'une couche monocristalline, notamment piezoelectrique |

| FR1563055 | 2015-12-22 | ||

| PCT/EP2016/082245 WO2017108994A1 (fr) | 2015-12-22 | 2016-12-21 | Procede de fabrication d'une couche monocristalline, notamment piezoelectrique |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20180098343A true KR20180098343A (ko) | 2018-09-03 |

| KR102681655B1 KR102681655B1 (ko) | 2024-07-05 |

Family

ID=55590008

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020187021267A Active KR102681655B1 (ko) | 2015-12-22 | 2016-12-21 | 단결정층, 특히 압전층의 제조방법 |

Country Status (8)

| Country | Link |

|---|---|

| US (3) | US11101428B2 (ko) |

| EP (1) | EP3394324A1 (ko) |

| JP (1) | JP6816147B2 (ko) |

| KR (1) | KR102681655B1 (ko) |

| CN (2) | CN108603305A (ko) |

| FR (1) | FR3045677B1 (ko) |

| SG (1) | SG11201805382SA (ko) |

| WO (1) | WO2017108994A1 (ko) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20180048283A1 (en) * | 2015-04-16 | 2018-02-15 | Shin-Etsu Chemical Co., Ltd. | Lithium tantalate single crystal substrate, bonded substrate, manufacturing method of the bonded substrate, and surface acoustic wave device using the bonded substrate |

| FR3045677B1 (fr) * | 2015-12-22 | 2019-07-19 | Soitec | Procede de fabrication d'une couche monocristalline, notamment piezoelectrique |

| JP6654435B2 (ja) * | 2016-01-07 | 2020-02-26 | 株式会社ディスコ | ウエーハ生成方法 |

| US11193049B2 (en) | 2016-11-25 | 2021-12-07 | Lg Chem, Ltd. | Curable composition |

| FR3073083B1 (fr) * | 2017-10-31 | 2019-10-11 | Soitec | Procede de fabrication d'un film sur un feuillet flexible |

| CN113926680B (zh) * | 2021-09-01 | 2022-12-13 | 中国电子科技集团公司第三研究所 | 超声换能器、超声扫描显微镜以及超声换能器的制作方法 |

| FR3131800B1 (fr) * | 2022-01-07 | 2024-03-22 | Soitec Silicon On Insulator | Procédé de traitement de substrats |

| CN114774844A (zh) * | 2022-03-31 | 2022-07-22 | 清华大学 | 在原子级别调控薄膜平整表面成分的方法 |

| CN115472734A (zh) * | 2022-08-31 | 2022-12-13 | 中国电子科技集团公司第二十六研究所 | 一种钙钛矿型Relaxor-PT固溶体单晶薄膜复合材料及制备方法 |

| FR3141308B1 (fr) * | 2022-10-20 | 2024-10-11 | Soitec Silicon On Insulator | Procede de fabrication d’une couche piezoelectrique sur un substrat |

| EP4414482A1 (en) * | 2023-02-07 | 2024-08-14 | Max-Planck-Gesellschaft zur Förderung der Wissenschaften e.V. | Composite substrates for the epitaxial growth of thin films and method for fabricating such substrates |

| CN117156947B (zh) * | 2023-10-31 | 2024-02-20 | 北京青禾晶元半导体科技有限责任公司 | 一种复合压电衬底的制备方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6593212B1 (en) * | 2001-10-29 | 2003-07-15 | The United States Of America As Represented By The Secretary Of The Navy | Method for making electro-optical devices using a hydrogenion splitting technique |

| KR20120084295A (ko) * | 2009-10-09 | 2012-07-27 | 꼼미사리아 아 레네르지 아토미끄 에뜨 옥스 에너지스 앨터네이티브즈 | 표면파 필터 및 벌크파 필터를 포함하는 음향파 디바이스, 및 그 제조 방법 |

| KR20190061070A (ko) * | 2016-10-10 | 2019-06-04 | 소이텍 | 전면형 이미지 센서 및 그 센서를 제조하는 방법 |

Family Cites Families (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US2738939A (en) | 1954-07-13 | 1956-03-20 | Francis M Johnson | Personnel retriever for helicopters |

| US4019200A (en) | 1975-06-11 | 1977-04-19 | Rockwell International Corporation | Monolithic surface acoustic wave signal storage device |

| JPH08153915A (ja) | 1994-11-30 | 1996-06-11 | Matsushita Electric Ind Co Ltd | 複合圧電基板とその製造方法 |

| CN1048126C (zh) * | 1994-12-06 | 2000-01-05 | 株式会社村田制作所 | 表面声波器件的电极形成方法 |

| US5935641A (en) | 1996-10-23 | 1999-08-10 | Texas Instruments Incorporated | Method of forming a piezoelectric layer with improved texture |

| US6540827B1 (en) * | 1998-02-17 | 2003-04-01 | Trustees Of Columbia University In The City Of New York | Slicing of single-crystal films using ion implantation |

| US6120597A (en) * | 1998-02-17 | 2000-09-19 | The Trustees Of Columbia University In The City Of New York | Crystal ion-slicing of single-crystal films |

| JP2001122699A (ja) * | 1999-10-21 | 2001-05-08 | Murata Mfg Co Ltd | エピタキシャル膜製造用の酸化物基板、エピタキシャル膜の製造方法および圧電デバイス |

| JP3704017B2 (ja) * | 2000-03-28 | 2005-10-05 | ヤマハ株式会社 | 弾性表面波素子 |

| US6555946B1 (en) | 2000-07-24 | 2003-04-29 | Motorola, Inc. | Acoustic wave device and process for forming the same |

| JP4055405B2 (ja) | 2001-12-03 | 2008-03-05 | ソニー株式会社 | 電子部品及びその製造方法 |

| US6767749B2 (en) * | 2002-04-22 | 2004-07-27 | The United States Of America As Represented By The Secretary Of The Navy | Method for making piezoelectric resonator and surface acoustic wave device using hydrogen implant layer splitting |

| FR2845523B1 (fr) | 2002-10-07 | 2005-10-28 | Procede pour realiser un substrat par transfert d'une plaquette donneuse comportant des especes etrangeres, et plaquette donneuse associee | |

| FR2847076B1 (fr) * | 2002-11-07 | 2005-02-18 | Soitec Silicon On Insulator | Procede de detachement d'une couche mince a temperature moderee apres co-implantation |

| JP3774782B2 (ja) | 2003-05-14 | 2006-05-17 | 富士通メディアデバイス株式会社 | 弾性表面波素子の製造方法 |

| JPWO2005050836A1 (ja) | 2003-11-19 | 2007-06-14 | 株式会社村田製作所 | 端面反射型弾性表面波装置及びその製造方法 |

| US7863157B2 (en) | 2006-03-17 | 2011-01-04 | Silicon Genesis Corporation | Method and structure for fabricating solar cells using a layer transfer process |

| JP4091641B2 (ja) | 2006-04-07 | 2008-05-28 | 富士フイルム株式会社 | 圧電素子とその製造方法、及びインクジェット式記録ヘッド |

| JP2008211277A (ja) | 2007-02-23 | 2008-09-11 | Matsushita Electric Ind Co Ltd | 弾性表面波素子 |

| JP5201602B2 (ja) * | 2007-04-13 | 2013-06-05 | 国立大学法人京都大学 | 音源分離システム、音源分離方法及び音源分離用コンピュータプログラム |

| US7750406B2 (en) | 2007-04-20 | 2010-07-06 | International Business Machines Corporation | Design structure incorporating a hybrid substrate |

| US7982363B2 (en) | 2007-05-14 | 2011-07-19 | Cree, Inc. | Bulk acoustic device and method for fabricating |

| JP5181649B2 (ja) * | 2007-09-18 | 2013-04-10 | 日立電線株式会社 | 圧電素子 |

| WO2009081651A1 (ja) | 2007-12-25 | 2009-07-02 | Murata Manufacturing Co., Ltd. | 複合圧電基板の製造方法 |

| US8115365B2 (en) * | 2008-04-15 | 2012-02-14 | Ngk Insulators, Ltd. | Surface acoustic wave devices |

| ATE555494T1 (de) | 2009-02-19 | 2012-05-15 | S O I Tec Silicon | Relaxation und übertragung von verspannten materialschichten |

| JP5429200B2 (ja) | 2010-05-17 | 2014-02-26 | 株式会社村田製作所 | 複合圧電基板の製造方法および圧電デバイス |

| JP2012106902A (ja) * | 2010-10-25 | 2012-06-07 | Fujifilm Corp | ペロブスカイト型酸化物膜及びそれを用いた強誘電体膜、強誘電体素子、ペロブスカイト型酸化物膜の製造方法 |

| WO2012128268A1 (ja) * | 2011-03-22 | 2012-09-27 | 株式会社村田製作所 | 圧電デバイス、圧電デバイスの製造方法 |

| CN102253451B (zh) | 2011-05-13 | 2013-03-20 | 华中科技大学 | 一种铌酸锂光波导的制备方法 |

| WO2013018604A1 (ja) | 2011-07-29 | 2013-02-07 | 株式会社村田製作所 | 圧電デバイス、および、圧電デバイスの製造方法 |

| TW201413833A (zh) | 2012-07-30 | 2014-04-01 | 住友化學股份有限公司 | 複合基板的製造方法及半導體結晶層形成基板的製造方法 |

| FR2995136B1 (fr) | 2012-09-04 | 2015-06-26 | Soitec Silicon On Insulator | Pseudo-substrat avec efficacite amelioree d'utilisation d'un materiau monocristallin |

| US9324931B2 (en) | 2013-05-14 | 2016-04-26 | Tdk Corporation | Piezoelectric device |

| FR3045677B1 (fr) * | 2015-12-22 | 2019-07-19 | Soitec | Procede de fabrication d'une couche monocristalline, notamment piezoelectrique |

-

2015

- 2015-12-22 FR FR1563055A patent/FR3045677B1/fr active Active

-

2016

- 2016-12-21 JP JP2018532582A patent/JP6816147B2/ja active Active

- 2016-12-21 US US16/064,416 patent/US11101428B2/en active Active

- 2016-12-21 KR KR1020187021267A patent/KR102681655B1/ko active Active

- 2016-12-21 EP EP16819558.4A patent/EP3394324A1/fr active Pending

- 2016-12-21 WO PCT/EP2016/082245 patent/WO2017108994A1/fr not_active Ceased

- 2016-12-21 CN CN201680080405.8A patent/CN108603305A/zh active Pending

- 2016-12-21 SG SG11201805382SA patent/SG11201805382SA/en unknown

- 2016-12-21 CN CN202411652636.4A patent/CN119553364A/zh active Pending

-

2021

- 2021-08-06 US US17/396,374 patent/US12356858B2/en active Active

-

2025

- 2025-06-05 US US19/229,438 patent/US20250301910A1/en active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6593212B1 (en) * | 2001-10-29 | 2003-07-15 | The United States Of America As Represented By The Secretary Of The Navy | Method for making electro-optical devices using a hydrogenion splitting technique |

| KR20120084295A (ko) * | 2009-10-09 | 2012-07-27 | 꼼미사리아 아 레네르지 아토미끄 에뜨 옥스 에너지스 앨터네이티브즈 | 표면파 필터 및 벌크파 필터를 포함하는 음향파 디바이스, 및 그 제조 방법 |

| KR20190061070A (ko) * | 2016-10-10 | 2019-06-04 | 소이텍 | 전면형 이미지 센서 및 그 센서를 제조하는 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2017108994A1 (fr) | 2017-06-29 |

| SG11201805382SA (en) | 2018-07-30 |

| US20210367139A1 (en) | 2021-11-25 |

| FR3045677A1 (fr) | 2017-06-23 |

| US12356858B2 (en) | 2025-07-08 |

| KR102681655B1 (ko) | 2024-07-05 |

| US20250301910A1 (en) | 2025-09-25 |

| FR3045677B1 (fr) | 2019-07-19 |

| JP6816147B2 (ja) | 2021-01-20 |

| US20180375014A1 (en) | 2018-12-27 |

| US11101428B2 (en) | 2021-08-24 |

| CN108603305A (zh) | 2018-09-28 |

| CN119553364A (zh) | 2025-03-04 |

| EP3394324A1 (fr) | 2018-10-31 |

| JP2019508924A (ja) | 2019-03-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US12356858B2 (en) | Method for the production of a single-crystal film, in particular piezoelectric | |

| US20230217832A1 (en) | Composite substrates including epitaxial monocrystalline piezoelectric layers bonded to substrates, and acoustic wave devices formed with such composite substrates | |

| US11705880B2 (en) | Process for producing a micro-electro-mechanical system from a transferred piezoelectric or ferroelectric layer | |

| KR101806578B1 (ko) | 표면파 필터 및 벌크파 필터를 포함하는 음향파 디바이스, 및 그 제조 방법 | |

| US9496847B2 (en) | Electro-acoustic transducer with periodic ferroelectric polarization produced on a micromachined vertical structure | |

| KR102750357B1 (ko) | 온도-보상된 표면 음향파 장치 또는 벌크 음향파 장치를 위한 기판 | |

| JP6129187B2 (ja) | 微細加工された垂直構造物に基づくバルク波共振器 | |

| US20130130502A1 (en) | Micromechanical membranes and related structures and methods | |

| Reinhardt et al. | Acoustic filters based on thin single crystal LiNbO 3 films: status and prospects | |

| CN205792476U (zh) | 一种采用超薄压电单晶体制作的薄膜体声波谐振器 | |

| KR20230086718A (ko) | 변형 가능한 층과 압전층을 포함하는 mems 애플리케이션용 복합 구조체 및 관련 제조 방법 | |

| KR102457258B1 (ko) | 층의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

St.27 status event code: A-0-1-A10-A15-nap-PA0105 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| A201 | Request for examination | ||

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-2-2-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-2-2-P10-P22-nap-X000 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| T11-X000 | Administrative time limit extension requested |

St.27 status event code: U-3-3-T10-T11-oth-X000 |

|

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U12-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |