KR20140028362A - 반도체 메모리 장치 - Google Patents

반도체 메모리 장치 Download PDFInfo

- Publication number

- KR20140028362A KR20140028362A KR1020120094440A KR20120094440A KR20140028362A KR 20140028362 A KR20140028362 A KR 20140028362A KR 1020120094440 A KR1020120094440 A KR 1020120094440A KR 20120094440 A KR20120094440 A KR 20120094440A KR 20140028362 A KR20140028362 A KR 20140028362A

- Authority

- KR

- South Korea

- Prior art keywords

- signal

- delay

- column

- unit

- response

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/4076—Timing circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4097—Bit-line organisation, e.g. bit-line layout, folded bit lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/06—Sense amplifiers; Associated circuits, e.g. timing or triggering circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1078—Data input circuits, e.g. write amplifiers, data input buffers, data input registers, data input level conversion circuits

- G11C7/1087—Data input latches

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/12—Bit line control circuits, e.g. drivers, boosters, pull-up circuits, pull-down circuits, precharging circuits, equalising circuits, for bit lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

- G11C7/227—Timing of memory operations based on dummy memory elements or replica circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/10—Decoders

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/005—Transfer gates, i.e. gates coupling the sense amplifier output to data lines, I/O lines or global bit lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/22—Control and timing of internal memory operations

- G11C2207/229—Timing of a write operation

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Dram (AREA)

Abstract

Description

도 2a 및 도 2b는 도 1에 도시된 반도체 장치의 동작을 설명하기 위한 타이밍도이다.

도 3은 본 발명의 실시예에 따른 반도체 장치의 블록 구성도이다.

도 4는 도 3에 도시된 컬럼 제어부의 내부 구성도이다.

도 5는 도 4에 도시된 라이트용 컬럼 소오스신호 생성부의 내부 구성도이다.

도 6은 도 5에 도시된 제1 레플리카 딜레이의 내부 구성도이다.

도 7은 도 5에 도시된 제2 레플리카 딜레이의 내부 구성도이다.

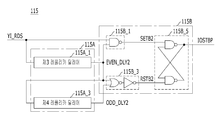

도 8은 도 4에 도시된 리드 인에이블신호 생성부의 내부 구성도이다.

도 9는 도 3에 도시된 컬럼 디코더와 복수의 매트 간의 배치 관계를 설명하기 위한 블록 구성도이다.

도 10은 본 발명의 실시예에 따른 반도체 장치의 동작을 설명하기 위한 타이밍도이다.

111 : 입력 지연부 113 : 라이트용 컬럼 소오스신호 생성부

113A : 제1 신호 생성부 113A_1 : 제1 레플리카 딜레이

113A_3 : 제2 레플리카 딜레이 113A_31 : 제1 모델링부

113A_33 : 제1 선택부 113B : 제2 신호 생성부

113B_1 : 제1 논리 연산부 113B_3 : 제2 논리 연산부

113B_5 : 제3 논리 연산부 115 : 리드용 컬럼 소오스신호 생성부

115A : 제3 신호 생성부 115A_1 : 제3 레플리카 딜레이

115A_3 : 제4 레플리카 딜레이 115A_31 : 제2 모델링부

115A_33 : 제2 선택부 115A_35 : 제1 반전부

115B : 제4 신호 생성부 115B_1 : 제4 논리 연산부

115B_3 : 제5 논리 연산부 115B_5 : 제6 논리 연산부

120 : 컬럼 디코더 130 : 라이트 드라이버

140 : 입출력 감지 증폭기 150 : 메모리 영역

Claims (30)

- 복수의 지연시간 중에서 데이터가 입출력되는 메모리 영역의 배치 위치에 따라 선택된 지연시간이 서로 다른 배수로 반영된 제1 및 제2 지연신호를 제1 컬럼 제어신호에 응답하여 순차적으로 생성하기 위한 제1 신호 생성부; 및

상기 제1 컬럼 제어신호보다 상기 지연시간만큼 지연된 제2 컬럼 제어신호를 생성하되, 상기 제1 지연신호에 응답하여 상기 제2 컬럼 제어신호의 활성화 시점을 결정하고 상기 제2 지연신호에 응답하여 상기 제2 컬럼 제어신호의 비활성화 시점을 결정하는 제2 신호 생성부

를 포함하는 반도체 메모리 장치.

- 제1항에 있어서,

상기 복수의 지연시간은 상기 데이터가 입출력되는 데이터 전송라인을 복수의 메모리 영역의 배치 위치에 대응하여 모델링한 반도체 메모리 장치.

- 제2항에 있어서,

상기 데이터 전송라인은 로컬 입출력 라인(Local Input/Output Line)을 포함하는 반도체 메모리 장치. - 제2항에 있어서,

상기 제1 신호 생성부는 상기 데이터 전송라인을 모델링하기 위한 RC 딜레이를 포함하는 반도체 메모리 장치.

- 제1항에 있어서,

상기 제1 지연신호는 상기 제1 컬럼 제어신호에 비하여 상기 선택된 지연시간의 1배수만큼 지연되고,

상기 제2 지연신호는 상기 제1 컬럼 제어신호에 비하여 상기 선택된 지연시간의 2배수만큼 지연된 반도체 메모리 장치.

- 제1항에 있어서,

상기 제1 컬럼 제어신호는 라이트 드라이버를 인에이블하기 위한 라이트 인에이블신호를 포함하고,

상기 제2 컬럼 제어신호는 컬럼 디코더가 라이트용 컬럼 선택신호를 생성할 때 소오스신호로서 이용하는 제1 컬럼 소오스신호를 포함하는 반도체 메모리 장치.

- 제6항에 있어서,

상기 선택된 지연시간은 상기 데이터가 입출력되는 메모리 영역의 배치 위치가 상기 라이트 드라이버로부터 멀수록 상기 복수의 지연시간 중에서 더 큰 값의 지연시간이 선택되는 반도체 메모리 장치.

- 제1항에 있어서,

상기 제1 컬럼 제어신호는 컬럼 디코더가 리드용 컬럼 선택신호를 생성할 때 소오스신호로서 이용하는 제2 컬럼 소오스신호를 포함하고,

상기 제2 컬럼 제어신호는 입출력 감지 증폭기(Input Output Sense Amplifier : IOSA)를 인에이블하기 위한 리드 인에이블신호를 포함하는 반도체 메모리 장치.

- 제8항에 있어서,

상기 선택된 지연시간은 상기 데이터가 입출력되는 메모리 영역의 배치 위치가 상기 입출력 감지 증폭기(IOSA)로부터 멀수록 상기 복수의 지연시간 중에서 더 큰 값의 지연시간이 선택되는 반도체 메모리 장치.

- 제1항에 있어서,

상기 제2 신호 생성부는 SR 래치를 포함하는 반도체 메모리 장치.

- 라이트 인에이블신호를 복수의 메모리 영역의 배치 위치에 대응하는 지연시간만큼 지연시켜 제1 지연신호를 생성하기 위한 제1 레플리카 지연부;

상기 제1 지연신호를 상기 지연시간만큼 지연시켜 제2 지연신호를 생성하기 위한 제2 레플리카 지연부;

상기 라이트 인에이블신호와 상기 제1 및 제2 지연신호에 응답하여 상기 라이트 인에이블신호보다 상기 지연시간만큼 지연된 제1 컬럼 소오스신호를 생성하기 위한 컬럼 소오스신호 생성부; 및

상기 제1 컬럼 소오스신호에 응답하여 라이트용 컬럼 선택신호를 생성하기 위한 컬럼 디코더

를 포함하는 반도체 메모리 장치.

- 제11항에 있어서,

글로벌 입출력 라인(Global Input/Output Line)에 실린 데이터를 상기 라이트 인에이블신호에 응답하여 로컬 입출력 라인(Local Input/Output Line)에 전달하기 위한 라이트 드라이버를 더 포함하며,

상기 지연시간은 상기 복수의 메모리 영역의 배치 위치가 상기 라이트 드라이버로부터 멀리 배치될수록 크게 반영되는 반도체 메모리 장치.

- 제12항에 있어서,

상기 제1 및 제2 레플리카 지연부는 상기 로컬 입출력 라인을 모델링한 반도체 메모리 장치.

- 제11항에 있어서,

상기 제1 레플리카 지연부는,

복수의 단위 지연 셀이 직렬로 접속되며, 상기 복수의 메모리 영역의 배치 위치에 대응하여 서로 다른 지연시간이 모델링된 복수의 지연경로를 제공하는 제1 모델링부; 및

상기 복수의 지연경로를 통해 출력되는 복수의 지연된 라이트 인에이블신호 중 어느 하나를 적어도 하나의 선택신호에 따라 선택하여 상기 제1 지연신호로서 출력하기 위한 제1 선택부를 포함하는 반도체 메모리 장치.

- 제11항에 있어서,

상기 제2 레플리카 지연부는,

복수의 단위 지연 셀이 직렬로 접속되며, 상기 복수의 메모리 영역의 배치 위치에 대응하여 서로 다른 지연시간이 모델링된 복수의 지연경로를 제공하는 제2 모델링부;

상기 복수의 지연경로를 통해 출력되는 복수의 지연된 제1 지연신호 중 어느 하나를 상기 선택신호에 따라 선택하기 위한 제2 선택부; 및

상기 제2 선택부에 의해 선택된 신호를 반전시켜 상기 제2 지연신호로서 출력하기 위한 제1 반전부를 포함하는 반도체 메모리 장치.

- 제14항 또는 제15항에 있어서,

상기 복수의 단위 지연 셀은 RC 딜레이를 포함하는 반도체 메모리 장치.

- 제16항에 있어서,

상기 복수의 메모리 영역은 뱅크에 포함된 복수의 매트 영역에 대응하고,

상기 선택신호는 상기 복수의 매트 영역 중에서 데이터가 라이트되는 매트 영역에 대응하여 인가되는 반도체 메모리 장치.

- 제11항에 있어서,

상기 컬럼 소오스신호 생성부는,

상기 라이트 인에이블신호와 상기 제1 지연신호를 논리 연산하여 제1 세트신호를 생성하기 위한 제1 논리 연산부;

상기 제1 지연신호와 제2 지연신호를 논리 연산하여 제1 리세스신호를 생성하기 위한 제2 논리 연산부; 및

상기 제1 세트신호와 상기 제1 리세트신호에 응답하여 상기 제1 컬럼 소오스신호를 생성하기 위한 제3 논리 연산부를 포함하는 반도체 메모리 장치.

- 제18항에 있어서,

상기 제3 논리 연산부는 SR 래치를 포함하는 반도체 메모리 장치.

- 제18항에 있어서,

상기 제1 지연신호는 상기 라이트 인에이블신호와 동일 위상을 가지고,

상기 제2 지연신호는 상기 라이트 인에이블신호와 반대 위상을 가지는 반도체 메모리 장치.

- 제11항에 있어서,

상기 컬럼 디코더는 제2 컬럼 소오스신호에 응답하여 리드용 컬럼 선택신호를 생성하며,

라이트/리드 구분신호와 소오스 신호에 응답하여 상기 라이트 인에이블신호 및 상기 제2 컬럼 소오스신호를 생성하기 위한 입력 지연부;

상기 제2 컬럼 소오스신호를 상기 지연시간만큼 지연시켜 제3 지연신호를 생성하기 위한 제3 레플리카 지연부;

상기 제3 지연신호를 상기 지연시간만큼 지연시켜 제4 지연신호를 생성하기 위한 제4 레플리카 지연부; 및

상기 제2 컬럼 소오스신호와 상기 제3 및 제4 지연신호에 응답하여 상기 제2 컬럼 소오스신호보다 상기 지연시간만큼 지연된 리드 인에이블신호를 생성하기 위한 리드 인에이블신호 생성부를 더 포함하는 반도체 메모리 장치.

- 제21항에 있어서,

로컬 입출력 라인에 실린 데이터를 상기 리드 인에이블신호에 응답하여 글로벌 입출력 라인에 전달하기 위한 입출력 감지 증폭기(Input Output Sense Amplifier : IOSA)를 더 포함하며,

상기 지연시간은 상기 복수의 메모리 영역의 배치 위치가 상기 입출력 감지 증폭기로부터 멀리 배치될수록 크게 반영되는 반도체 메모리 장치. - 제22항에 있어서,

상기 제3 및 제4 레플리카 지연부는 상기 로컬 입출력 라인을 모델링한 반도체 메모리 장치.

- 제21항에 있어서,

상기 제3 레플리카 지연부는,

복수의 단위 지연 셀이 직렬로 접속되며, 상기 복수의 메모리 영역의 배치 위치에 대응하여 서로 다른 지연시간이 모델링된 복수의 지연경로를 제공하는 제3 모델링부; 및

상기 복수의 지연경로를 통해 출력되는 복수의 지연된 제2 컬럼 소오스신호 중 어느 하나를 적어도 하나의 선택신호에 따라 선택하여 상기 제3 지연신호로서 출력하기 위한 제3 선택부를 포함하는 반도체 메모리 장치.

- 제21항에 있어서,

상기 제4 레플리카 지연부는,

복수의 단위 지연 셀이 직렬로 접속되며, 상기 복수의 메모리 영역의 배치 위치에 대응하여 서로 다른 지연시간이 모델링된 복수의 지연경로를 제공하는 제4 모델링부;

상기 복수의 지연경로를 통해 출력되는 복수의 지연된 제3 지연신호 중 어느 하나를 상기 선택신호에 따라 선택하기 위한 제4 선택부; 및

상기 제4 선택부에 의해 선택된 신호를 반전시켜 상기 제4 지연신호로서 출력하기 위한 제2 반전부를 포함하는 반도체 메모리 장치.

- 제24항 또는 제25항에 있어서,

상기 복수의 단위 지연 셀은 RC 딜레이를 포함하는 반도체 메모리 장치.

- 제26항에 있어서,

상기 복수의 메모리 영역은 뱅크에 포함된 복수의 매트 영역에 대응하고,

상기 선택신호는 상기 복수의 매트 영역 중에서 데이터가 리드되는 매트 영역에 대응하여 인가되는 반도체 메모리 장치.

- 제21항에 있어서,

상기 리드 인에이블신호 생성부는,

상기 제2 컬럼 소오스신호와 상기 제3 지연신호를 논리 연산하여 제2 세트신호를 생성하기 위한 제4 논리 연산부;

상기 제5 제어신호와 제4 지연신호를 논리 연산하여 제2 리세스신호를 생성하기 위한 제4 논리 연산부; 및

상기 제2 세트신호와 상기 제2 리세트신호에 응답하여 상기 리드 인에이블신호를 생성하기 위한 제6 논리 연산부를 포함하는 반도체 메모리 장치.

- 제28항에 있어서,

상기 제6 논리 연산부는 SR 래치를 포함하는 반도체 메모리 장치.

- 제28항에 있어서,

상기 제3 지연신호는 상기 제2 컬럼 소오스신호와 동일 위상을 가지고,

상기 제4 지연신호는 상기 제2 컬럼 소오스신호와 반대 위상을 가지는 반도체 메모리 장치.

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020120094440A KR102007364B1 (ko) | 2012-08-28 | 2012-08-28 | 반도체 메모리 장치 |

| US13/717,357 US9190130B2 (en) | 2012-08-28 | 2012-12-17 | Semiconductor memory device with sequentially generated delay signals |

| US14/943,639 US9520167B2 (en) | 2012-08-28 | 2015-11-17 | Semiconductor memory device using delays to control column signals for different memory regions |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020120094440A KR102007364B1 (ko) | 2012-08-28 | 2012-08-28 | 반도체 메모리 장치 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20140028362A true KR20140028362A (ko) | 2014-03-10 |

| KR102007364B1 KR102007364B1 (ko) | 2019-08-05 |

Family

ID=50187436

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020120094440A Expired - Fee Related KR102007364B1 (ko) | 2012-08-28 | 2012-08-28 | 반도체 메모리 장치 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US9190130B2 (ko) |

| KR (1) | KR102007364B1 (ko) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9552255B2 (en) | 2015-06-09 | 2017-01-24 | SK Hynix Inc. | Memory device with parallel odd and even column access and methods thereof |

| US9940982B2 (en) | 2015-06-09 | 2018-04-10 | SK Hynix Inc. | Memory device having bank interleaving access |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104900255B (zh) * | 2014-03-03 | 2018-03-09 | 台湾积体电路制造股份有限公司 | 用于双端口sram的升压系统 |

| KR102220749B1 (ko) * | 2014-03-14 | 2021-03-02 | 에스케이하이닉스 주식회사 | 반도체 장치 |

| CN104134457B (zh) * | 2014-07-17 | 2018-01-09 | 北京航空航天大学 | 一种利用非易失性元器件的电阻特性实现片上信号延时的电路 |

| US9804793B2 (en) | 2016-03-04 | 2017-10-31 | Intel Corporation | Techniques for a write zero operation |

| CN114143432A (zh) * | 2016-03-30 | 2022-03-04 | 株式会社尼康 | 拍摄元件、拍摄装置以及半导体存储器 |

| US10249351B2 (en) | 2016-11-06 | 2019-04-02 | Intel Corporation | Memory device with flexible internal data write control circuitry |

| US10490239B2 (en) | 2016-12-27 | 2019-11-26 | Intel Corporation | Programmable data pattern for repeated writes to memory |

| KR102697484B1 (ko) * | 2017-01-23 | 2024-08-21 | 에스케이하이닉스 주식회사 | 반도체장치 |

| KR102342471B1 (ko) * | 2017-08-07 | 2021-12-24 | 에스케이하이닉스 주식회사 | 반도체 기입 장치 및 반도체 장치 |

| KR102591123B1 (ko) * | 2018-07-16 | 2023-10-19 | 에스케이하이닉스 주식회사 | 반도체장치 |

| KR102730064B1 (ko) * | 2018-12-06 | 2024-11-15 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 그의 동작 방법 |

| CN112558342B (zh) * | 2020-12-23 | 2023-11-28 | 深圳市华星光电半导体显示技术有限公司 | 像素电路的仿真系统及仿真方法 |

| US12131059B2 (en) * | 2022-03-03 | 2024-10-29 | Changxin Memory Technologies, Inc. | Data writing circuit, data writing method, and memory |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20010021140A1 (en) * | 1997-06-03 | 2001-09-13 | Fujitsu Limited | Semiconductor memory device |

| KR20030084510A (ko) * | 2002-04-27 | 2003-11-01 | 삼성전자주식회사 | 동기식 반도체 메모리장치의 컬럼 디코더 인에이블 타이밍제어방법 및 장치 |

| KR100771551B1 (ko) * | 2006-10-17 | 2007-10-31 | 주식회사 하이닉스반도체 | 반도체 소자의 컬럼경로 제어신호 생성회로 및 컬럼경로제어신호 생성방법 |

| KR20090104309A (ko) * | 2008-03-31 | 2009-10-06 | 주식회사 하이닉스반도체 | 반도체 메모리 장치의 컬럼 선택 신호 회로 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5475690A (en) * | 1994-11-10 | 1995-12-12 | Digital Equipment Corporation | Delay compensated signal propagation |

| KR100388317B1 (ko) * | 1998-12-28 | 2003-10-10 | 주식회사 하이닉스반도체 | 반도체메모리소자 |

| US6622256B1 (en) * | 2000-03-30 | 2003-09-16 | Intel Corporation | System for protecting strobe glitches by separating a strobe signal into pointer path and timing path, filtering glitches from signals on pointer path thereof |

| KR100631929B1 (ko) * | 2005-02-15 | 2006-10-04 | 삼성전자주식회사 | 신호 딜레이 조절부를 갖는 반도체 메모리 장치 |

| KR100647361B1 (ko) * | 2005-03-18 | 2006-11-23 | 주식회사 하이닉스반도체 | 반도체 메모리 장치의 컬럼선택신호 발생장치 |

| KR100853468B1 (ko) * | 2007-07-12 | 2008-08-21 | 주식회사 하이닉스반도체 | 온 다이 터미네이션 장치를 구비하는 반도체메모리소자 및그의 구동방법 |

| KR100939117B1 (ko) | 2007-12-28 | 2010-01-28 | 주식회사 하이닉스반도체 | 안정적 데이터 액세스를 위한 반도체 메모리 장치 및 그방법 |

| KR100968418B1 (ko) | 2008-06-04 | 2010-07-07 | 주식회사 하이닉스반도체 | 반도체 메모리 소자와 그의 구동 방법 |

| KR101043731B1 (ko) * | 2008-12-30 | 2011-06-24 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 |

| KR101047059B1 (ko) * | 2009-10-30 | 2011-07-06 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 |

-

2012

- 2012-08-28 KR KR1020120094440A patent/KR102007364B1/ko not_active Expired - Fee Related

- 2012-12-17 US US13/717,357 patent/US9190130B2/en active Active

-

2015

- 2015-11-17 US US14/943,639 patent/US9520167B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20010021140A1 (en) * | 1997-06-03 | 2001-09-13 | Fujitsu Limited | Semiconductor memory device |

| KR20030084510A (ko) * | 2002-04-27 | 2003-11-01 | 삼성전자주식회사 | 동기식 반도체 메모리장치의 컬럼 디코더 인에이블 타이밍제어방법 및 장치 |

| KR100771551B1 (ko) * | 2006-10-17 | 2007-10-31 | 주식회사 하이닉스반도체 | 반도체 소자의 컬럼경로 제어신호 생성회로 및 컬럼경로제어신호 생성방법 |

| KR20090104309A (ko) * | 2008-03-31 | 2009-10-06 | 주식회사 하이닉스반도체 | 반도체 메모리 장치의 컬럼 선택 신호 회로 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9552255B2 (en) | 2015-06-09 | 2017-01-24 | SK Hynix Inc. | Memory device with parallel odd and even column access and methods thereof |

| US9940982B2 (en) | 2015-06-09 | 2018-04-10 | SK Hynix Inc. | Memory device having bank interleaving access |

Also Published As

| Publication number | Publication date |

|---|---|

| US9190130B2 (en) | 2015-11-17 |

| US20160071564A1 (en) | 2016-03-10 |

| KR102007364B1 (ko) | 2019-08-05 |

| US20140063977A1 (en) | 2014-03-06 |

| US9520167B2 (en) | 2016-12-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102007364B1 (ko) | 반도체 메모리 장치 | |

| CN110910928B (zh) | 存储器模块 | |

| US9761297B1 (en) | Hidden refresh control in dynamic random access memory | |

| US9767903B2 (en) | Nonvolatile memory module having dual-port DRAM | |

| US8154933B2 (en) | Mode-register reading controller and semiconductor memory device | |

| KR20210074172A (ko) | 메모리-내 포스트 패키지 리페어(ppr)를 위한 인라인 버퍼 | |

| US9805781B2 (en) | Semiconductor memory device | |

| JP7007102B2 (ja) | 不揮発性メモリモジュール、及び格納装置の動作方法 | |

| CN106055493B (zh) | 存储系统、存储模块及其操作方法 | |

| KR102548599B1 (ko) | 버퍼메모리를 포함하는 메모리 장치 및 이를 포함하는 메모리 모듈 | |

| US9070428B2 (en) | Semiconductor device | |

| KR100745369B1 (ko) | 포트상태 시그날링 기능을 갖는 멀티패쓰 억세스블 반도체메모리 장치 | |

| JP4307894B2 (ja) | 同期式半導体メモリ装置のカラムデコーダ・イネーブルタイミングの制御方法及びその装置 | |

| US10331378B2 (en) | Methods of operating mixed device type memory modules, and processors and systems configured for operating the same | |

| US9368175B2 (en) | Semiconductor memory device receiving multiple commands simultaneously and memory system including the same | |

| KR102115457B1 (ko) | 반도체 장치 및 그를 포함하는 반도체 시스템 | |

| KR20080069298A (ko) | 반도체 메모리 장치 및 그의 동작 제어방법 | |

| KR20080099945A (ko) | 억세스 권한 이양 시 프리차아지 스킵을 방지하는 동작을갖는 멀티패쓰 억세스블 반도체 메모리 장치 | |

| US9575880B2 (en) | Semiconductor memory device and memory system | |

| KR20120004825A (ko) | 반도체 메모리 장치 | |

| KR102646721B1 (ko) | 컴퓨팅 시스템, 비휘발성 메모리 모듈, 및 저장 장치의 동작 방법 | |

| KR100909800B1 (ko) | 반도체 메모리장치의 리드 제어장치 및 방법 | |

| JP2010123157A (ja) | 半導体記憶装置 | |

| KR100903387B1 (ko) | 전력 소모를 줄이는 반도체 메모리 장치 | |

| KR20110002303A (ko) | 반도체 메모리 장치 및 그 구동 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| A201 | Request for examination | ||

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20230731 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20230731 |