KR20090012136A - 반도체 장치 - Google Patents

반도체 장치 Download PDFInfo

- Publication number

- KR20090012136A KR20090012136A KR1020080072364A KR20080072364A KR20090012136A KR 20090012136 A KR20090012136 A KR 20090012136A KR 1020080072364 A KR1020080072364 A KR 1020080072364A KR 20080072364 A KR20080072364 A KR 20080072364A KR 20090012136 A KR20090012136 A KR 20090012136A

- Authority

- KR

- South Korea

- Prior art keywords

- wiring

- layer

- standard cell

- power supply

- boundary

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 73

- 239000010410 layer Substances 0.000 claims description 528

- 239000011229 interlayer Substances 0.000 claims description 44

- 238000000034 method Methods 0.000 claims description 15

- 230000002787 reinforcement Effects 0.000 claims description 10

- 230000003014 reinforcing effect Effects 0.000 claims description 9

- 230000010354 integration Effects 0.000 abstract description 35

- 229910052751 metal Inorganic materials 0.000 description 91

- 239000002184 metal Substances 0.000 description 91

- 230000015572 biosynthetic process Effects 0.000 description 40

- 239000000758 substrate Substances 0.000 description 39

- 239000000872 buffer Substances 0.000 description 30

- 230000004888 barrier function Effects 0.000 description 18

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 10

- 238000013461 design Methods 0.000 description 9

- 238000002955 isolation Methods 0.000 description 8

- 239000002356 single layer Substances 0.000 description 8

- 101100528928 Oryza sativa subsp. japonica RL9 gene Proteins 0.000 description 6

- 238000009792 diffusion process Methods 0.000 description 6

- 239000012535 impurity Substances 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- 229910018565 CuAl Inorganic materials 0.000 description 4

- 101100409457 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) CDC40 gene Proteins 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- 238000009413 insulation Methods 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 4

- 239000010936 titanium Substances 0.000 description 4

- 101100522111 Oryza sativa subsp. japonica PHT1-11 gene Proteins 0.000 description 3

- 101100522114 Oryza sativa subsp. japonica PHT1-12 gene Proteins 0.000 description 3

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 101100522115 Oryza sativa subsp. japonica PHT1-13 gene Proteins 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000000945 filler Substances 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 2

- 238000012360 testing method Methods 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 230000002596 correlated effect Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 238000007306 functionalization reaction Methods 0.000 description 1

- 125000002496 methyl group Chemical group [H]C([H])([H])* 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000008719 thickening Effects 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

CMOS 인버터 NT1, PT1이 스탠다드 셀(51a)에 포함되어 있다. 전원선은, CMOS 인버터 NT1, PT1에 전기적으로 접속되고, 또한 하층 배선(32a, 32b) 및 상층 배선(34c, 34d)을 갖고 있다. 하층 배선(32a, 32b)은 서로 인접하는 스탠다드 셀(51a)의 경계를 따라서 경계 위로 연장되어 있다. 상층 배선(34c, 34d)은 평면에서 보아 하층 배선(32a, 32b)보다도 스탠다드 셀(51a)의 내측에 위치하고 있다. CMOS 인버터 NT1, PT1은 상층 배선(34c, 34d)을 통해서 하층 배선(32a, 32b)에 전기적으로 접속되어 있다. 이에 의해, 고속화 및 고집적화의 쌍방이 양립 가능한 반도체 장치가 얻어진다.

스탠다드 셀, 상층 배선, 하층 배선, 기능 소자, 고속 셀, 고집적 셀

Description

본 발명은, 반도체 장치에 관한 것으로, 특히, 배열된 복수개의 스탠다드 셀을 갖는 반도체 장치에 관한 것이다.

근년, SOC(System On Chip)에서는 회로의 대규모화에 의해, 표준 셀 라이브러리를 사용한 레이아웃 설계가 일반적으로 행해지고 있다. 또한,SOC의 고기능화, 고성능화에 수반하여, 표준 셀 라이브러리는 고집적화, 고속화가 요구되고 있다. 한편, 고속화에 수반하여 소비 전류가 증가함으로써 IR-Drop(전류 I가 임의의 경로를 흐를 때, 그 경로의 저항값 R로 하면,I×R로 표현되는 전위차가 경로의 양단에 발생하는 것) 등의 전원 노이즈에 의한 특성 열화를 야기하는 문제가 커지고 있다.

종래, 표준 셀 라이브러리의 스탠다드 셀에, 기능 소자로서 예를 들면 CMOS(Complementary Metal 0xide Semiconductor) 인버터를 형성한 구성이 있다. 이 구성에서는, n형 웰 영역의 표면에 p채널 MOS 트랜지스터(이하, pMOS 트랜지스터라고 칭함)가 형성되고, p형 웰 영역의 표면에 n채널 MOS 트랜지스터(이하, nMOS 트랜지스터라고 칭함)가 형성되어 있다. 이들 pMOS 트랜지스터 및 nMOS 트랜지스 터의 각각에는, 전원선(VDD 배선, GND 배선)이 접속되어 있다. 이들 전원선의 각각은, 기판에 컨택트되어 기판 전위를 고정하고 있고, 각 스탠다드 셀의 기능 소자에 공통으로 형성되어 있다.

표준 셀 라이브러리의 고속화에 수반하여 스탠다드 셀의 소비 전류는 증대하므로, 전원선에 흐르는 전류도 증가해 간다. 또한, 각 스탠다드 셀에 공통의 전원선에는 복수의 스탠다드 셀의 전류가 유입된다. 이에 의해, 전원선에 흐르는 전류값이 커지기 때문에, IR-Drop의 영향을 고려할 필요가 있다. 전원선의 IR-Drop은 전원선의 저항값과 상관이 있어, 저항값이 작은수록 IR-Drop의 영향은 작아진다. 이 때문에, 전원선의 선폭을 굵게 하는 대책이 종래 행해지고 있었다.

한편, 표준 셀 라이브러리의 고집적화에 수반하여, 드레인 노드가 서로 다른 2개의 CMOS 트랜지스터를 1개의 스탠다드 셀 내에 배치하는 경우가 있다. 이 경우에는, 4개의 트랜지스터를 평면에서 보아 세로 방향으로 1열로 나열하여 배치함으로써 스탠다드 셀의 고집적화를 도모하는 방법이 종래부터 행해지고 있었다. 이 방법에서는, 트랜지스터끼리를 접속하는 배선과, 트랜지스터와 전원선을 접속하는 배선이 많아져, 배선 레이아웃이 복잡해지는 경향이 있었다.

또한 종래의 스탠다드 셀을 복수 배치한 레이아웃은, 예를 들면 일본 특개 2000-223575호 공보에 개시되어 있다. 이 공보에는, 제1층 전원선(3VDD1, 3VSS1)과, 이에 평행한 제3층 전원선(3VDD3, 3VSS3)을 형성하고, 또한 제2층에 신호선(3S2)을 지나가게 함으로써, 제2층의 배치에 제한을 발생시키지 않고, 제1층 전원선을 제3층 전원선으로 보강하는 것이 개시되어 있다.

그러나, 상기한 바와 같은 종래의 스탠다드 셀의 구성에서는, 고집적이고 또한 고속의 스탠다드 셀을 실현하기 위해서, 고속화용의 전원선을 굵게 한 구성과, 고집적화용의 복수의 트랜지스터를 세로 방향으로 배치한 구성을 양립하는 것이 곤란했다. 왜냐하면, 전원선을 굵게 함으로써, 인버터를 구성하는 pMOS 트랜지스터 및 nMOS 트랜지스터의 각 드레인을 접속하는 배선과, 전원선을 트랜지스터에 접속하는 배선 부분과의 간격을 확보하는 것이 곤란해지기 때문이다.

본 발명은, 상기의 과제를 감안하여 이루어진 것으로, 그 목적은, 고속화 및 고집적화의 쌍방이 양립 가능한 반도체 장치를 제공하는 것이다.

본 발명의 실시 형태에서의 반도체 장치는, 배열된 복수개의 스탠다드 셀을 갖는 반도체 장치로서, 기능 소자와, 전원선을 구비하고 있다. 기능 소자는, 스탠다드 셀에 포함되어 있다. 전원선은, 기능 소자에 전기적으로 접속되고, 또한 하층 배선 및 상층 배선을 갖고 있다. 하층 배선은 서로 인접하는 스탠다드 셀의 경계를 따라서 경계 위로 연장되는 부분을 갖고 있다. 상층 배선은 평면에서 보아 하층 배선보다도 스탠다드 셀의 내측에 위치하는 부분을 갖고 있다. 기능 소자는 상층 배선을 통해서 하층 배선에 전기적으로 접속되어 있다.

본 발명의 실시 형태에서의 반도체 장치에 의하면, 전원선이 하층 배선과 상층 배선으로 분리되어 있어, 전원선이 단일층인 경우보다도 전류 경로가 늘어나 있 기 때문에, 고속화를 도모할 수 있다. 또한, 전원선의 선폭을 굵게 하지 않고 전류 경로를 늘릴 수 있기 때문에, 고집적화를 도모할 수도 있다.

또한 하층 배선이 스탠다드 셀의 경계를 따라서 연장되어 있기 때문에, 인접하는 스탠다드 셀 간에서 하층 배선을 공유할 수 있다. 이에 의해 인접하는 스탠다드 셀의 각각에서 별개로 하층 배선을 형성할 필요가 없기 때문에, 고집적화를 도모할 수 있다.

또한 기능 소자는 상층 배선을 통해서 하층 배선에 접속되어 있기 때문에, 스탠다드 셀의 경계에 위치하는 하층 배선을 기능 소자가 위치하는 스탠다드 셀의 중앙부로 연장할 필요가 없어진다. 이에 의해, 하층 배선을 스탠다드 셀의 중앙부로 연장할 부분에 빈 공간이 생기기 때문에, 그 빈 공간에 다른 배선 등을 배치하는 것이 가능해져, 고집적화를 도모할 수 있다.

이상으로부터, 고속화 및 고집적화의 쌍방이 양립 가능한 반도체 장치를 얻을 수 있다.

본 발명의 상기 및 다른 목적, 특징, 국면 및 이점은, 첨부의 도면과 관련하여 이해되는 본 발명에 관한 다음의 상세한 설명으로부터 명백하게 될 것이다.

이하, 본 발명의 실시 형태에 대해서 도면에 기초하여 설명한다.

(실시 형태 1)

도 1을 참조하여, 반도체 장치(예를 들면 반도체 칩)(50)는, 그 표면에, 스탠다드 셀 영역(51)과, 그 스탠다드 셀 영역(51)의 주위에 배치된 I/O(Input/Output) 셀 영역(52)과, 외부와의 입출력에 이용되는 패드(도시하지 않음)를 주로 갖고 있다.

스탠다드 셀 영역(51)은, 매트릭스 형상(행렬 형상)으로 배치된 복수의 스탠다드 셀(51a)을 갖고 있다. 표준 셀 라이브러리를 사용한 SOC에서는, 이 스탠다드 셀 영역(51) 내에, CPU(Central Processing Unit), RAM(Random Access Memory), FIFO(First-In First-Out), SCSI(Small Computer System Interface), SOG(Sea Of Gate) 등이 형성되어 있다.

도 2를 참조하여, 스탠다드 셀(51a) 내에 형성되는 기능 소자의 회로는, 예를 들면 TriState(트라이스테이트)용 버퍼의 일부 회로로서, 출력단과 드라이버부를 갖고 있다. 출력단은, 예를 들면 pMOS 트랜지스터 PT1과 nMOS 트랜지스터 NT1로 이루어지는 CMOS 인버터로 이루어져 있다. 드라이버부는, 예를 들면 pMOS 트랜지스터 PT2 및 nMOS 트랜지스터 NT2로 이루어지는 CMOS 인버터와, pMOS 트랜지스터 PT3과 nMOS 트랜지스터 NT3으로 이루어지는 CMOS 인버터로 이루어져 있다.

pMOS 트랜지스터 PT2 및 nMOS 트랜지스터 NT2로 이루어지는 CMOS 인버터의 출력이, 출력단의 nMOS 트랜지스터 NT1에 입력되어 있다. 또한 pMOS 트랜지스터 PT3 및 nMOS 트랜지스터 NT3으로 이루어지는 CMOS 인버터의 출력이, 출력단의 pMOS 트랜지스터 PT1에 입력되어 있다.

이 회로에서는, 드라이버부의 2개의 CMOS 인버터에 "High"를 입력한 경우에는 출력단의 CMOS 인버터로부터 "High"가 출력된다. 또한 드라이버부의 2개의 CMOS 인버터에 "Low"를 입력한 경우에는 출력단의 CMOS 인버터로부터 "Low"가 출력 된다. 또한 pMOS 트랜지스터 PT3 및 nMOS 트랜지스터 NT3으로 이루어지는 CMOS 인버터에 "Low"를 입력하고, pMOS 트랜지스터 PT2 및 nMOS 트랜지스터 NT2로 이루어지는 CMOS 인버터에 "High"를 입력한 경우, 출력단의 CMOS 인버터의 출력이 플로팅 상태로 되어, 소위 "High impedance"로 된다.

도 3 및 도 4를 참조하여, 반도체 기판의 표면에 p형 웰 영역(1)이 형성되어 있고, 이 p형 웰 영역(1) 내의 표면에는 n형 웰 영역(2)이 선택적으로 형성되어 있다. 이 p형 웰 영역(1) 내의 표면에는, nMOS 트랜지스터 NT1, NT2, NT3이 형성되어 있다. n형 웰 영역(2) 내의 표면에는, pMOS 트랜지스터 PT1, PT2, PT3이 형성되어 있다.

또한 스탠다드 셀(51a)의 세로 방향(도 3 내의 Y방향)의 경계의 한쪽(도 3 내의 Y방향 하측의 경계)을 따라서, p형 웰 영역(1) 내의 표면에는 가로 방향(도 3 내의 X방향)으로 연장되도록 p+ 영역(15)이 형성되어 있다. 또한 스탠다드 셀(51a)의 세로 방향(도 3 내의 Y방향)의 경계의 다른 쪽(도 3 내의 Y방향 상측의 경계)을 따라서, n형 웰 영역(2) 내의 표면에는 가로 방향(도 3 내의 X방향)으로 연장되도록 n+ 영역(25)이 형성되어 있다.

복수의 MOS 트랜지스터의 형성 영역, p+ 영역(15) 및 n+ 영역(25)의 각각을 전기적으로 분리하기 위해서, 반도체 기판의 표면에 예를 들면 STI(Shallow Trench Isolation)로 이루어지는 소자 분리 영역(3)이 형성되어 있다. 이 STI는, 반도체 기판의 표면에 형성된 홈과, 그 홈 내를 충전하는 절연성의 충전물에 의해 구성되 어 있다.

nMOS 트랜지스터 NT1, NT2, NT3의 각각은, 드레인 영역(11a) 및 소스 영역(11b)과, 게이트 절연층(12)과, 게이트 전극층(13)을 갖고 있다. 드레인 영역(11a) 및 소스 영역(11b)은, n형의 불순물 영역으로 이루어져 있고, p형 웰 영역(1)의 표면에 서로 거리를 두고 형성되어 있다. 게이트 전극층(13)은, 드레인 영역(11a) 및 소스 영역(11b) 사이에 끼워지는 영역 위에 게이트 절연층(12)을 개재하여 형성되어 있다.

pMOS 트랜지스터 PT1, PT2, PT3의 각각은, 드레인 영역(21a) 및 소스 영역(21b)과, 게이트 절연층(22)과, 게이트 전극층(23)을 갖고 있다. 드레인 영역(21a) 및 소스 영역(21b)은, p형의 불순물 영역으로 이루어져 있고, n형 웰 영역(2)의 표면에 서로 거리를 두고 형성되어 있다. 게이트 전극층(23)은, 드레인 영역(21a) 및 소스 영역(21b) 사이에 끼워지는 영역 위에 게이트 절연층(22)을 개재하여 형성되어 있다.

nMOS 트랜지스터 NT2의 게이트 전극층(13)과 pMOS 트랜지스터 PT2의 게이트 전극층(23)은 공통의 도전층으로 이루어져 있어, 서로 전기적으로 접속되어 있다. 또한 nMOS 트랜지스터 NT3의 게이트 전극층(13)과 pMOS 트랜지스터 PT3의 게이트 전극층(23)은 공통의 도전층으로 이루어져 있어, 서로 전기적으로 접속되어 있다.

이들 각 MOS 트랜지스터 NT1∼NT3, PT1∼PT3을 덮도록 반도체 기판의 표면 위에 층간 절연층(31A, 31B)이 적층되어 형성되어 있다. 층간 절연층(31A)은 예를 들면 TEOS(Tetra-Ethyl-Ortho-Silicate) 산화막으로 이루어져 있고, 층간 절연 층(31B)은 예를 들면 SiOC, MSQ(MethylSilses-Quioxane) 등으로 이루어져 있다.

층간 절연층(31B)에는 그 상면으로부터 층간 절연층(31A)에 도달하는 배선용 홈(31b)이 형성되어 있고, 층간 절연층(31A)에는 배선용 홈(31b)의 저부로부터 반도체 기판에 도달하는 컨택트홀(31a)이 형성되어 있다. 상기의 배선용 홈(31b)의 각각의 내부에는, 예를 들면 CuAl 합금(Al 함유량이 예를 들면 0.1∼1.0% 정도)으로 이루어지는 배선층(32a∼32h)의 각각이 매립되어 형성되어 있다. 또한 상기의 컨택트홀(31a)의 각각의 내부에는, 예를 들면 텅스텐(W)으로 이루어지는 플러그층이 매립되어 형성되어 있다.

또한 컨택트홀(31a)의 측면 및 저면에는 배리어 메탈층(도시하지 않음)이 형성되어 있다. 이 배리어 메탈층은, 상기 플러그층과 층간 절연층(31A) 사이 및 상기 플러그층과 반도체 기판 사이에 위치하고 있다. 이 배리어 메탈층은, 예를 들면 티탄(Ti)과 질화 티탄(TiN)의 적층 구조를 갖고 있다.

배선용 홈(31b)의 측면 및 저면에도 배리어 메탈층(도시하지 않음)이 형성되어 있다. 이 배리어 메탈층은, 상기 배선층(32a∼32h)과 층간 절연층(31B) 사이, 상기 배선층(32a∼32h)과 상기 플러그층 사이 및 상기 배선층(32a∼32h)과 층간 절연층(31A) 사이에 위치하고 있다. 이 배리어 메탈층은, 예를 들면 탄탈(Ta)로 이루어져 있다.

또한 층간 절연층(31A)과 층간 절연층(31B) 사이에는, 예를 들면 SiCN으로 이루어지는 에칭 스토퍼층(도시하지 않음)이 형성되어 있다.

배선층(32e)에 의해, nMOS 트랜지스터 NT1의 드레인 영역(11a)과 pMOS 트랜 지스터 PT1의 드레인 영역(21a)이 서로 전기적으로 접속되어 있다. 또한 배선층(32c)에 의해, nMOS 트랜지스터 NT2의 드레인 영역(11a)과 pMOS 트랜지스터 PT2의 드레인 영역(21a)이 서로 전기적으로 접속되고, 또한 nMOS 트랜지스터 NT1의 게이트 전극층(13)에 전기적으로 접속되어 있다. 또한 배선층(32d)에 의해, nMOS 트랜지스터 NT3의 드레인 영역(11a)과 pMOS 트랜지스터 PT3의 드레인 영역(21a)이 서로 전기적으로 접속되고, 또한 pMOS 트랜지스터 PT1의 게이트 전극층(23)에 전기적으로 접속되어 있다. 이들 배선층(32c, 32d)은 드라이버부로부터 출력단에 신호를 전달하는 신호선에 해당한다.

또한 배선층(32a)은, 스탠다드 셀(51a)의 세로 방향의 경계의 한쪽(도 3 내의 Y방향 하측의 경계)을 따라서 그 경계 위를 가로 방향(도 3 내의 X방향)으로 뻗도록 연장되어 있다. 또한 배선층(32b)은, 스탠다드 셀(51a)의 세로 방향의 경계의 다른 쪽(도 3 내의 Y방향 상측의 경계)을 따라서 그 경계 위를 가로 방향(도 3 내의 X방향)으로 뻗도록 연장되어 있다. 이들 스탠다드 셀의 경계 위를 따라서 연장되는 배선층(32a, 32b)의 각각은, 전원 전위(VDD, GND)를 인가 가능하고, 전원선의 하층 배선에 대응한다.

구체적으로는, 배선층(32a)에는 GND 전위가 인가 가능하고, 배선층(32b)에는 VDD 전위가 인가 가능하다.

배선층(32a)은 p+ 영역(15)에 전기적으로 접속되어 있고, p형 웰 영역(1)의 전위를 고정하고 있다. 또한 배선층(32a)은, 세로 방향(도 3 내의 Y방향)의 경계 의 한쪽(도 3 내의 Y방향 하측의 경계)을 따라서 직선적으로 연장되는 부분으로부터 분기되어 nMOS 트랜지스터 NT2, NT3의 각각의 소스 영역(11b) 위로 연장되는 부분을 갖고, 그 부분에서 그들의 소스 영역(11b)에 전기적으로 접속되어 있다.

배선층(32b)은 n+ 영역(25)에 전기적으로 접속되어 있고, n형 웰 영역(2)의 전위를 고정하고 있다. 또한 배선층(32b)은, 세로 방향(도 3 내의 Y방향)의 경계의 다른 쪽(도 3 내의 Y방향 상측의 경계)을 따라서 직선적으로 연장되는 부분으로부터 분기되어 pMOS 트랜지스터 PT2의 소스 영역(21b) 위로 연장되는 부분을 갖고, 그 부분에서 그 소스 영역(21b)에 전기적으로 접속되어 있다.

또한 nMOS 트랜지스터 NT1의 소스 영역(11b), pMOS 트랜지스터 PT1의 소스 영역(21b) 및 pMOS 트랜지스터 PT3의 소스 영역(21b)의 각각에는, 배선층(32g, 32h, 32f)의 각각이 전기적으로 접속되어 있다.

또한 배선층(32a∼32h)의 각각과 반도체 기판의 표면에 형성된 불순물 영역의 접속은, 층간 절연층(31A)에 형성된 컨택트홀(31a) 내의 플러그층을 통해서 이루어져 있다.

배선층(32a∼32h)을 덮도록 층간 절연층(31B) 위에, 예를 들면 SiOC, MSQ로 이루어지는 층간 절연층(33)이 형성되어 있다. 이 층간 절연층(33)의 상면에는 배선용 홈(33b)이 형성되어 있고, 배선용 홈(33b)의 저부로부터 하층의 각 배선층의 각각에 도달하는 비아 홈(33a)이 형성되어 있다. 이 비아 홈(33a) 및 배선용 홈(33b) 내를 매립하도록, 예를 들면 CuAl 합금(Al 함유량이 예를 들면 0.1∼1.0% 정도)으로 이루어지는 배선층(34a∼34d)의 각각이 형성되어 있다.

또한 비아 홈(33a) 및 배선용 홈(33b)의 측면 및 저면에는 배리어 메탈층(도시하지 않음)이 형성되어 있다. 이 배리어 메탈층은, 배선층(34a∼34d)의 각각과 층간 절연층(33) 사이, 비아 홈(33a)의 각각과 층간 절연층(33) 사이 및 비아 홈(33a)의 각각과 하층의 배선층 사이에 위치하고 있다. 이 배리어 메탈층은, 예를 들면 탄탈(Ta)과 질화 탄탈(TaN)의 적층 구조를 갖고 있다.

또한 층간 절연층(33) 아래에는, 예를 들면 SiCN으로 이루어지는 스토퍼층(도시하지 않음)이 형성되어 있다.

배선층(34c)에 의해, nMOS 트랜지스터 NT1의 소스 영역(11b)(배선층(32g))과 nMOS 트랜지스터 NT3의 소스 영역(11b)이 서로 전기적으로 접속되고, 또한 GND 전위가 인가 가능한 배선층(32a)에 전기적으로 접속되어 있다. 또한 배선층(34d)에 의해, pMOS 트랜지스터 PT1의 소스 영역(21b)(배선층(32h))과 pMOS 트랜지스터 PT3의 소스 영역(21b)(배선층(32f))과 pMOS 트랜지스터 PT2의 소스 영역(21b)이 서로 전기적으로 접속되고, 또한 VDD 전위가 인가 가능한 배선층(32b)에 전기적으로 접속되어 있다.

배선층(34c)은, 도 3에 도시하는 평면에서 보아, 전원선의 하층 배선(32a)보다도 스탠다드 셀(51a)의 내측(중앙측)에 배치되어 있다. 또한 배선층(34d)은, 도 3에 도시하는 평면에서 보아, 전원선의 하층 배선(32b)보다도 스탠다드 셀(51a)의 내측(중앙측)에 배치되어 있다.

또한 배선층(34a)은, 스탠다드 셀(51a)의 세로 방향(도 3 내의 Y방향)의 경 계의 한쪽(도 3 내의 Y방향 하측의 경계)을 따라서 그 경계 위를 가로 방향(도 3 내의 X방향)으로 뻗도록 연장되어 있다. 또한 배선층(34b)은, 스탠다드 셀(51a)의 세로 방향(도 3 내의 Y방향)의 경계의 다른 쪽(도 3 내의 Y방향 상측의 경계)을 따라서 그 경계 위를 가로 방향(도 3 내의 X방향)으로 뻗도록 연장되어 있다. 배선층(34a)은 그 하층에 나란히 연장되는 배선층(32a)에 접속되어 있고, 배선층(34b)은 그 하층에 나란히 연장되는 배선층(32b)에 접속되어 있다.

또한 배선층(34a)은 그 하층에 나란히 연장되는 배선층(32a)의 선폭 W1a보다도 큰 선폭 W2a를 갖고 있다. 또한 배선층(34b)은 그 하층에 나란히 연장되는 배선층(32b)의 선폭 W1b보다도 큰 선폭 W2b를 갖고 있다.

이와 같이, 이 스탠다드 셀(51a) 내의 모든 배선층(34a, 34b, 34c, 34d)은 VDD 및 GND 중 어느 하나의 전원 전위로 되기 때문에, 전원선의 상층 배선에 해당한다.

또한 배선층(34a∼34d)의 각각과 배선층(32a, 32b, 32e∼32h)의 각각의 전기적 접속은, 배선층(34a∼34d)의 각각의 비아 홈(33a) 내를 매립하는 부분을 통해서 이루어져 있다.

상기한 바와 같이, nMOS 트랜지스터 NT1의 소스 영역(11b)은, GND 전위의 전원선의 상층 배선(34c)을 통해서 GND 전위의 전원선의 하층 배선(32a)에 전기적으로 접속되어 있다. 또한 pMOS 트랜지스터 PT1, PT3의 각각의 소스 영역(21b)은, VDD 전위의 전원선의 상층 배선(34d)을 통해서 VDD 전위의 전원선의 하층 배선(32b)에 전기적으로 접속되어 있다.

또한 신호선(32c)은, 도 3에 도시하는 평면에서 보아, 전원선의 상층 배선(34c) 및 배선층(32g)의 접속부(비아홀(33a))와, 하층 배선(32a)의 스탠다드 셀(51a)의 경계를 따라서 직선적으로 연장되는 부분 사이에 위치하도록 배치되어 있다. 신호선(32d)은, 도 3에 도시하는 평면에서 보아, 전원선의 상층 배선(34d) 및 배선층(32h)의 접속부(비아홀(33a))와, 하층 배선(32b)의 스탠다드 셀(51a)의 경계를 따라서 직선적으로 연장되는 부분 사이에 위치하도록 배치되어 있다.

본 실시 형태에 따르면, GND 전위의 전원선이 하층 배선(32a)과 상층 배선(34a)으로 분리되어 있고, 또한 VDD 전위의 전원선이 하층 배선(32b)과 상층 배선(34b)으로 분리되어 있다. 이 때문에, 전원선이 단일층인 경우보다도 전류 경로가 늘어나 있기 때문에, 고속화를 도모할 수 있다. 또한, 전원선의 선폭을 굵게 하지 않고 전류 경로를 늘릴 수 있기 때문에, 고집적화를 도모할 수도 있다.

또한 상층 배선(34a, 34b)이 하층 배선(32a, 32b)의 선폭 W1a, W1b보다도 큰 선폭 W2a, W2b를 갖고 있기 때문에, 전원선의 저항값을 저감할 수 있다.

또한 하층 배선(32a, 32b)이 상층 배선(34a, 34b)의 선폭 W2a, W2b보다도 작은 선폭 W1a, W1b를 갖고 있기 때문에, 그만큼, 배선의 배치를 위한 빈 공간이 커진다. 이 때문에 하층 배선과 동일한 층에 다른 배선(예를 들면 신호선(32c, 32d)) 등을 배치하는 것이 용이해져, 다른 배선의 평면 레이아웃의 자유도가 높아진다.

또한 하층 배선(32a, 32b)의 각각이, 스탠다드 셀(51a)의 경계를 따라서 연장되어 있다. 이 때문에, 인접하는 스탠다드 셀(51a) 간에서 하층 배선(32a, 32b) 을 공유할 수 있다. 이에 의해 인접하는 스탠다드 셀(51a)의 각각에서 별개로 하층 배선(32a, 32b)을 형성할 필요가 없기 때문에, 고집적화를 도모할 수 있다.

또한 상층 배선(34a, 34b)의 각각이, 스탠다드 셀(51a)의 경계를 따라서 연장되어 있다. 이 때문에, 상기와 마찬가지로, 인접하는 스탠다드 셀(51a)의 각각에서 별개로 상층 배선(34a, 34b)을 형성할 필요가 없기 때문에, 고집적화를 도모할 수 있다.

또한 nMOS 트랜지스터 NT1의 소스 영역(11b)은, GND 전위의 전원선의 상층 배선(34c)을 통해서 GND 전위의 전원선의 하층 배선(32a)에 전기적으로 접속되어 있다. 또한 pMOS 트랜지스터 PT1, PT3의 각각의 소스 영역(21b)은, VDD 전위의 전원선의 상층 배선(34d)을 통해서 VDD 전위의 전원선의 하층 배선(32b)에 전기적으로 접속되어 있다. 이 때문에, 스탠다드 셀(51a)의 경계에 위치하는 하층 배선(32a, 32b)의 각각을 트랜지스터가 위치하는 스탠다드 셀(51a)의 중앙부로 연장할 필요가 없어진다. 이에 의해, 하층 배선(32a, 32b)의 각각을 스탠다드 셀(51a)의 중앙부로 연장할 부분에 빈 공간이 생기기 때문에, 그 빈 공간에 신호선(32c, 32d) 등의 다른 배선을 배치하는 것이 가능해져, 고집적화를 도모할 수 있다.

이와 같이 빈 공간에 신호선(32c, 32d)을 배치한 결과, 신호선(32c)은, 도 3에 도시하는 평면에서 보아, 전원선의 상층 배선(34c) 및 배선층(32g)의 접속부와, 하층 배선(32a)의 스탠다드 셀(51a)의 경계를 따라서 연장되는 부분 사이에 위치하도록 배치될 수 있다. 또한 신호선(32d)은, 도 3에 도시하는 평면에서 보아, 전원선의 상층 배선(34d) 및 배선층(32h)의 접속부와, 하층 배선(32b)의 스탠다드 셀(51a)의 경계를 따라서 연장되는 부분 사이에 위치하도록 배치될 수 있다.

이상으로부터, 고속화 및 고집적화의 쌍방이 양립 가능한 반도체 장치를 얻을 수 있다.

(실시 형태 2)

도 5 및 도 6을 참조하여, 본 실시 형태에서는, 복수의 스탠다드 셀(51a)의 각각에, nMOS 트랜지스터 NT1 및 pMOS 트랜지스터 PT1로 이루어지는 CMOS 인버터가 형성된 구성에 대해서 설명한다.

반도체 기판의 표면에 p형 웰 영역(1)이 형성되어 있고, 이 p형 웰 영역(1) 내의 표면에는 n형 웰 영역(2)이 선택적으로 형성되어 있다. p형 웰 영역(1) 내의 표면에는, nMOS 트랜지스터 NT1이 형성되어 있다. n형 웰 영역(2) 내의 표면에는, pMOS 트랜지스터 PT1이 형성되어 있다.

스탠다드 셀(51a)의 세로 방향(도 5 내의 Y방향)의 경계의 한쪽(도 5 내의 Y방향 하측의 경계)을 따라서 가로 방향(도 5 내의 X방향)으로 연장되도록, p형 웰 영역(1) 내의 표면에는 p+ 영역(15)이 형성되어 있다. 또한 스탠다드 셀(51a)의 세로 방향(도 5 내의 Y방향)의 경계의 다른 쪽(도 5 내의 Y방향 상측의 경계)을 따라서 가로 방향(도 5 내 X방향)으로 연장되도록, n형 웰 영역(2) 내의 표면에는 n+ 영역(25)이 형성되어 있다.

복수의 MOS 트랜지스터의 형성 영역, p+ 영역(15) 및 n+ 영역(25)의 각각을 전기적으로 분리하기 위해서, 반도체 기판의 표면에 예를 들면 STI로 이루어지는 소자 분리 영역(3)이 형성되어 있다. 이 STI는, 반도체 기판의 표면에 형성된 홈과, 그 홈 내를 충전하는 절연성의 충전물에 의해 구성되어 있다.

nMOS 트랜지스터 NT1은, 드레인 영역(11a) 및 소스 영역(11b)과, 게이트 절연층(12)과, 게이트 전극층(13)을 갖고 있다. 드레인 영역(11a) 및 소스 영역(11b)은, n형의 불순물 영역으로 이루어져 있고, p형 웰 영역(1)의 표면에 서로 거리를 두고 형성되어 있다. 게이트 전극층(13)은, 드레인 영역(11a) 및 소스 영역(11b) 사이에 끼워지는 영역 위에 게이트 절연층(12)을 개재하여 형성되어 있다.

pMOS 트랜지스터 PT1은, 드레인 영역(21a) 및 소스 영역(21b)과, 게이트 절연층(22)과, 게이트 전극층(23)을 갖고 있다. 드레인 영역(21a) 및 소스 영역(21b)은, p형의 불순물 영역으로 이루어져 있고, n형 웰 영역(2)의 표면에 서로 거리를 두고 형성되어 있다. 게이트 전극층(23)은, 드레인 영역(21a) 및 소스 영역(21b) 사이에 끼워지는 영역 위에 게이트 절연층(22)을 개재하여 형성되어 있다.

nMOS 트랜지스터 NT2의 게이트 전극층(13)과 pMOS 트랜지스터 PT2의 게이트 전극층(23)은 공통의 도전층으로 이루어져 있어, 서로 전기적으로 접속되어 있다.

이들 각 MOS 트랜지스터 NT1, PT1을 덮도록 반도체 기판의 표면 위에 층간 절연층(31A, 31B)이 적층되어 형성되어 있다. 층간 절연층(31A)은 예를 들면 TEOS 산화막으로 이루어져 있고, 층간 절연층(31B)은 예를 들면 SiOC, MSQ 등으로 이루어져 있다. 층간 절연층(31B)에는 그 상면으로부터 층간 절연층(31A)에 도달하는 배선용 홈(31b)이 형성되어 있고, 층간 절연층(31A)에는 배선용 홈(31b)의 저부로부터 반도체 기판에 도달하는 컨택트홀(31a)이 형성되어 있다. 상기의 배선용 홈(31b)의 각각의 내부에는, 예를 들면 CuAl 합금(Al 함유량이 예를 들면 0.1∼1.0% 정도)으로 이루어지는 배선층(32a, 32b, 32e, 32g, 32h)의 각각이 매립되어 형성되어 있다. 또한 상기의 컨택트홀(31a)의 각각의 내부에는, 예를 들면 텅스텐(W)으로 이루어지는 플러그층이 매립되어 형성되어 있다.

또한 컨택트홀(31a)의 측면 및 저면에는 배리어 메탈층(도시하지 않음)이 형성되어 있다. 이 배리어 메탈층은, 상기 플러그층과 층간 절연층(31A) 사이 및 상기 플러그층과 반도체 기판 사이에 위치하고 있다. 이 배리어 메탈층은, 예를 들면 티탄(Ti)과 질화 티탄(TiN)의 적층 구조를 갖고 있다.

배선용 홈(31b)의 측면 및 저면에도 배리어 메탈층(도시하지 않음)이 형성되어 있다. 이 배리어 메탈층은, 상기 배선층(32a, 32b, 32e, 32g, 32h)의 각각과 층간 절연층(31B) 사이, 상기 배선층(32a, 32b, 32e, 32g, 32h)의 각각과 상기 플러그층 사이 및 상기 배선층(32a, 32b, 32e, 32g, 32h)의 각각과 층간 절연층(31A) 사이에 위치하고 있다. 이 배리어 메탈층은, 예를 들면 탄탈(Ta)로 이루어져 있다.

또한 층간 절연층(31A)과 층간 절연층(31B) 사이에는, 예를 들면 SiCN으로 이루어지는 에칭 스토퍼층(도시하지 않음)이 형성되어 있다.

배선층(32e)에 의해, nMOS 트랜지스터 NT1의 드레인 영역(11a)과 pMOS 트랜지스터 PT1의 드레인 영역(21a)이 서로 전기적으로 접속되어 있다. 또한 배선층(32a)은, 스탠다드 셀(51a)의 세로 방향(도 5 내의 Y방향)의 경계의 한쪽(도 5 내의 Y방향 하측의 경계)을 따라서 그 경계 위를 가로 방향(도 5 내의 X방향)으로 뻗도록 연장되어 있다. 또한 배선층(32b)은, 스탠다드 셀(51a)의 세로 방향(도 5 내의 Y방향)의 경계의 다른 쪽(도 5 내의 Y방향 상측의 경계)을 따라서 그 경계 위를 가로 방향(도 5 내의 X방향)으로 뻗도록 연장되어 있다. 이 배선층(32b)은, 그 하층의 n+ 영역(25)에 전기적으로 접속되어 있고, 그에 의해 n형 웰 영역(2)의 전위를 고정하고 있다. 이들 스탠다드 셀(51a)의 경계선 위를 따라서 연장되는 배선층(32a, 32b)의 각각은, VDD 및 GND 중 어느 하나의 전원 전위를 인가 가능하고, 전원선의 하층 배선에 대응한다.

구체적으로는, 배선층(32a)에는 GND 전위가 인가 가능하고, 배선층(32b)에는 VDD 전위가 인가 가능하다.

배선층(32a)은 그 하층의 p+ 영역(15)에 전기적으로 접속되어 있고, 그에 의해 p형 웰 영역(1)의 전위를 고정하고 있다. 또한 배선층(32a)은, 세로 방향(도 5 내의 Y방향)의 경계의 한쪽(도 5 내의 Y방향 하측의 경계)을 따라서 직선적으로 연장되는 부분으로부터 분기되어 CMOS 인버터 등의 기능 소자가 형성되어 있지 않은 스탠다드 셀(51a) 위로 연장되는 부분을 갖고 있다.

배선층(32b)은 n+ 영역(25)에 전기적으로 접속되어 있고, 그에 의해 n형 웰 영역(2)의 전위를 고정하고 있다. 또한 배선층(32b)은, 세로 방향(도 5 내의 Y방향)의 경계의 다른 쪽(도 5 내의 Y방향 상측의 경계)을 따라서 직선적으로 연장되는 부분으로부터 분기되어 CMOS 인버터 등의 기능 소자가 형성되어 있지 않은 스탠다드 셀(51a) 위로 연장되는 부분을 갖고 있다.

또한 nMOS 트랜지스터 NT1의 소스 영역(11b) 및 pMOS 트랜지스터 PT1의 소스 영역(21b)의 각각에는, 배선층(32g, 32h)의 각각이 전기적으로 접속되어 있다.

또한 배선층(32a, 32b, 32e, 32g, 32h)의 각각과 반도체 기판의 표면에 형성된 불순물 영역의 접속은, 층간 절연층(31A)에 형성된 컨택트홀(31a) 내의 플러그층을 통해서 이루어져 있다.

배선층(32a, 32b, 32e, 32g, 32h)을 덮도록 층간 절연층(31B) 위에, 예를 들면 SiOC, MSQ로 이루어지는 층간 절연층(33)이 형성되어 있다. 이 층간 절연층(33)의 상면에는 배선용 홈(33b)이 형성되어 있고, 배선용 홈(33b)의 저부로부터 하층의 각 배선층의 각각에 도달하는 비아 홈(33a)이 형성되어 있다. 이 비아 홈(33a) 및 배선용 홈(33b) 내를 매립하도록, 예를 들면 CuAl 합금(Al 함유량이 예를 들면 0.1∼1·0% 정도)으로 이루어지는 배선층(34c, 34d)의 각각이 형성되어 있다.

또한 비아 홈(33a) 및 배선용 홈(33b)의 측면 및 저면에는 배리어 메탈층(도시하지 않음)이 형성되어 있다. 이 배리어 메탈층은, 배선층(34c, 34d)의 각각과 층간 절연층(33) 사이, 비아 홈(33a)의 각각과 층간 절연층(33) 사이 및 비아 홈(33a)의 각각과 하층의 배선층 사이에 위치하고 있다. 이 배리어 메탈층은, 예를 들면 탄탈(Ta)과 질화 탄탈(TaN)의 적층 구조를 갖고 있다.

또한 층간 절연층(33) 아래에는, 예를 들면 SiCN으로 이루어지는 에칭 스토퍼층(도시하지 않음)이 형성되어 있다.

배선층(34c)에 의해, 각 스탠다드 셀(51a)에서의 nMOS 트랜지스터 NT1의 소 스 영역(11b)(배선층(32g))이 서로 전기적으로 접속되어 있다. 또한 배선층(34c)은, CMOS 인버터가 형성되어 있지 않은 스탠다드 셀(51a) 내에서, 전원선의 하층 배선(32a)의 분기부와 전기적으로 접속되어 있다.

배선층(34d)에 의해, 각 스탠다드 셀(51a)에서의 pMOS 트랜지스터 PT1의 소스 영역(21b)(배선층(32h))이 서로 전기적으로 접속되어 있다. 또한 배선층(34d)은, CMOS 인버터가 형성되어 있지 않은 스탠다드 셀(51a) 내에서, 전원선의 하층 배선(32b)의 분기부와 전기적으로 접속되어 있다.

배선층(34c)은, 도 5에 도시하는 평면에서 보아, 전원선의 하층 배선(32a)보다도 스탠다드 셀(51a)의 내측(중앙측)에 배치되어 있다. 또한 배선층(34d)은, 도 5에 도시하는 평면에서 보아, 전원선의 하층 배선(32b)보다도 스탠다드 셀(51a)의 내측(중앙측)에 배치되어 있다.

또한 배선층(34c, 34d)의 각각과 배선층(32a, 32b, 32g, 32h)의 각각의 전기적 접속은, 배선층(34c, 34d)의 각각의 비아 홈(33a) 내를 매립하는 부분을 통해서 이루어져 있다.

상기한 바와 같이, nMOS 트랜지스터 NT1의 소스 영역(11b)은, GND 전위의 전원선의 상층 배선(34c)을 통해서 GND 전위의 전원선의 하층 배선(32a)에 전기적으로 접속되어 있다. 또한 pMOS 트랜지스터 PT1의 소스 영역(21b)은, VDD 전위의 전원선의 상층 배선(34d)을 통해서 VDD 전위의 전원선의 하층 배선(32b)에 전기적으로 접속되어 있다.

본 실시 형태에 따르면, 하층 배선(32a, 32b)의 각각이, 스탠다드 셀(51a)의 경계를 따라서 연장되어 있다. 이 때문에, 인접하는 스탠다드 셀(51a) 간에서 하층 배선(32a, 32b)을 공유할 수 있다. 이에 따라 인접하는 스탠다드 셀(51a)의 각각에서 별개로 하층 배선(32a, 32b)을 형성할 필요가 없기 때문에, 고집적화를 도모할 수 있다.

또한 상층 배선(34a, 34b)의 각각이, 스탠다드 셀(51a)의 경계를 따라서 연장되어 있다. 이 때문에, 상기와 마찬가지로, 인접하는 스탠다드 셀(51a)의 각각에서 별개로 상층 배선(34a, 34b)을 형성할 필요가 없기 때문에, 고집적화를 도모할 수 있다.

또한 nMOS 트랜지스터 NT1의 소스 영역(11b)은, GND 전위의 전원선의 상층 배선(34c)을 통해서 GND 전위의 전원선의 하층 배선(32a)에 전기적으로 접속되어 있다. 또한 pMOS 트랜지스터 PT1의 소스 영역(21b)은, VDD 전위의 전원선의 상층 배선(34d)을 통해서 VDD 전위의 전원선의 하층 배선(32b)에 전기적으로 접속되어 있다. 이 때문에, 스탠다드 셀(51a)의 경계에 위치하는 하층 배선(32a, 32b)의 각각을 각 트랜지스터가 위치하는 스탠다드 셀(51a)의 중앙부로 연장할 필요가 없어진다. 이에 의해, 하층 배선(32a, 32b)의 각각을 스탠다드 셀(51a)의 중앙부로 연장할 부분에 빈 공간이 생기기 때문에, 그 빈 공간에 신호선(32c, 32d) 등의 다른 배선을 배치하는 것이 가능해져, 고집적화를 도모할 수 있다.

이상으로부터, 고속화 및 고집적화의 쌍방이 양립 가능한 반도체 장치를 얻을 수 있다.

또한, 실시 형태 2에서, 도 5에서 기능 소자(예를 들면 CMOS 인버터)가 형성 되어 있지 않은 스탠다드 셀(51a)에, 도 7에 도시하는 바와 같이 퓨즈(40)가 배치되어 있어도 된다. 이와 같은 퓨즈(40)가 배치된 복수의 스탠다드 셀(51a)로 이루어지는 열이 또한 반도체 장치 내에 존재하고 있어도 된다. 이 퓨즈(40)는, 예를 들면 전원선의 하층 배선(32a, 32b)의 분기 부분의 경로의 도중에 배치되어 있어도 된다.

이 이외의 도 7의 구성은, 전술한 도 5 및 도 6의 구성과 거의 동일하기 때문에, 동일한 요소에 대해서는 동일한 부호를 붙이고, 그 설명을 반복하지 않는다.

또한 도 5에서는, 기능 소자가 형성되어 있지 않은 스탠다드 셀(51a)에서 전원선의 상층 배선(34c)이 하층 배선(32a)에 전기적으로 접속되고, 또한 전원선의 상층 배선(34d)이 하층 배선(32b)에 전기적으로 접속된 구성에 대해서 설명했다. 그러나, 실시 형태 2에서, 도 8에 도시하는 바와 같이 기능 소자가 형성되어 있지 않은 스탠다드 셀(51a) 내에서 전원선의 상층 배선(34c)이 하층 배선(32a)에 전기적으로 접속되어 있지 않고, 또한 전원선의 상층 배선(34d)이 하층 배선(32b)에 전기적으로 접속되어 있지 않도록 하는 복수의 스탠다드 셀(51a)로 이루어지는 열이 또한 반도체 장치 내에 존재하고 있어도 된다.

이 이외의 도 8의 구성은, 전술한 도 5 및 도 6의 구성과는 거의 동일하기 때문에, 동일한 요소에 대해서는 동일한 부호를 붙이고, 그 설명을 반복하지 않는다.

실시 형태 2의 도 5에 도시하는 바와 같이, 기능 소자가 형성되어 있지 않은 스탠다드 셀(51a)에서, 전원선의 상층 배선(34c)이 하층 배선(32a)에 전기적으로 접속되어 있고, 또한 전원선의 상층 배선(34d)이 하층 배선(32b)에 전기적으로 접속되어 있는 형태를 A형태로 한다. 또한 도 8에 도시하는 바와 같이, 기능 소자가 형성되어 있지 않은 스탠다드 셀(51a)에서, 전원선의 상층 배선(34c)이 하층 배선(32a)에 전기적으로 접속되어 있지 않고, 또한 전원선의 상층 배선(34d)이 하층 배선(32b)에 전기적으로 접속되어 있지 않은 형태를 B형태로 한다.

이들 A형태와 B형태를 반도체 장치의 설계 단계에서 교체하는 것만으로, A형태를 갖는 복수의 스탠다드 셀(51a) 열은 고속 동작이 가능한 셀 열로서 사용할 수 있도록 설계 가능해지고,B형태를 갖는 복수의 스탠다드 셀(51a) 열은 저소비 전력 동작이 가능한 셀 열로서 사용할 수 있도록 설계 가능하게 된다.

A형태를 갖는 복수의 스탠다드 셀(51a) 열에서는, 복수층으로부터의 전원선에 의해 동작 전류가 공급되기 때문에 고속 동작이 가능하다. 또한 B형태를 갖는 복수의 스탠다드 셀(51a) 열에서는, 전위 관계가 하층 배선(32a)<상층 배선(34c)<상층 배선(34d)<하층 배선(32b)으로 된다. 이에 의해,nMOS 트랜지스터 NT1이나 pMOS 트랜지스터 PT1의 기판의 전위와 소스 전위에 서로 다른 전위의 전압을 공급하여 기판 효과에 의한 트랜지스터의 임계값(Vth)을 크게 함으로써, 스탠다드 셀(51a)을 포함하는 회로의 대기 전류를 작게 할 수 있기 때문에, 저소비 전력 동작이 가능하게 된다.

이들 A형태와 B형태는 셀의 크기가 매우 서로 비슷하기 때문에, 간단히 교체 가능하여, 간단히 고속 동작이 가능한 셀 열과 저소비 전력 동작이 가능한 셀 열을 교체할 수 있다.

또한 도 7에 도시하는 바와 같이 기능 소자가 형성되어 있지 않은 스탠다드 셀(51a)에 퓨즈(40)가 배치되도록 하는 형태를 C형태로 한다. 이 C형태를 가짐으로써, 제품의 테스트 공정에서 퓨즈의 절단 유무에 의해 전술한 바와 같은 고속 동작과 저소비 전력 동작을 교체할 수 있다. 반도체 프로세스의 미세화에 수반하여, 제품의 웨이퍼 프로세스 완료 후의 특성 변동의 문제가 커지고 있다. 그러나, 테스트 공정에서 스탠다드 셀(51a)을 고속 동작 또는 저소비 전력 동작용으로 선택함으로써, 특성 변동을 작게 하는 것이 가능하다. 예를 들면, 트랜지스터의 임계값 전압 Vth가 낮아지는 방향으로 어긋남으로써, 동작 속도는 타겟의 속도보다도 충분히 빠르지만, 소비 전력이 타겟의 소비 전력보다도 커지는 경우가 생각된다. 이 경우, 퓨즈(40)를 절단하고, B형태를 갖는 복수의 스탠다드 셀(51a) 열과 같은 전위 관계로 함으로써 기판 효과에 의한 소비 전력 삭감에 의해 소비 전력을 타겟의 소비 전력 내로 억제하는 것이 가능하게 된다.

(실시 형태 3)

본 실시 형태는, 실시 형태 2의 구성을 변형함으로써 도 2에 도시하는 회로 구성을 실현한 것이다.

도 9 및 도 10을 참조하여, 본 실시 형태의 구성에서는, 예를 들면 인버터를 갖는 3개 나열한 스탠다드 셀(51a) 중, 중앙의 스탠다드 셀(51a) 내의 nMOS 트랜지스터 NT1 및 pMOS 트랜지스터 PT1이 도 2에서의 출력단의 CMOS 인버터에 대응하고 있다.

또한, 중앙의 스탠다드 셀(51a)의 도면 내의 우측의 스탠다드 셀(51a)의 nMOS 트랜지스터 NT2 및 pMOS 트랜지스터 PT2로 이루어지는 CMOS 인버터와, 도면 내의 좌측의 스탠다드 셀(51a)의 nMOS 트랜지스터 NT3 및 pMOS 트랜지스터 PT3으로 이루어지는 CMOS 인버터가 도 2에서의 드라이버부에 대응하고 있다.

중앙의 스탠다드 셀(51a) 내의 nMOS 트랜지스터 NT1의 게이트 전극층(13)과 pMOS 트랜지스터 PT1의 게이트 전극층(23)이 전기적으로 분리되어 있다. 우측의 스탠다드 셀(51a)에서의 배선층(32e1)은, 중앙의 스탠다드 셀(51a)의 게이트 전극층(13)에 전기적으로 접속되어 있고, 실시 형태 1에서의 신호선(32c)에 대응하는 것이다. 이 배선층(32e1)은 nMOS 트랜지스터 NT2의 드레인 영역(11a)과 pMOS 트랜지스터 PT2의 드레인 영역(21a)을 전기적으로 접속하고 있다.

또한 좌측의 스탠다드 셀(51a)에서의 배선층(32e2)은, 중앙의 스탠다드 셀(51a)의 게이트 전극층(23)에 전기적으로 접속되어 있고, 실시 형태 1에서의 신호선(32d)에 대응하는 것이다. 이 배선층(32e2)은 nMOS 트랜지스터 NT3의 드레인 영역(11a)과 pMOS 트랜지스터 PT3의 드레인 영역(21a)을 전기적으로 접속하고 있다.

전원선의 상층 배선(34c)은 그 하층에 나란히 연장되는 하층 배선(32a)의 선폭 W1a보다도 큰 선폭 W2a를 갖고 있고, 상층 배선(34d)은 그 하층에 나란히 연장되는 하층 배선(32b)의 선폭 W1b보다도 큰 선폭 W2b를 갖고 있다. 이에 의해, 상층 배선(34c)은, 도 9에 도시하는 평면에서 보아, 하층 배선(32a)보다도 스탠다드 셀(51a)의 내측에 위치하는 부분을 갖고 있다. 상층 배선(34c)의 하층 배선(32a) 보다도 내측에 위치하는 부분은, 배선층(32g)에 평면적으로 중복되어 있고, 또한 비아홀(33a)을 통해서 배선층(32g)에 전기적으로 접속되어 있다.

또한 전원선의 상층 배선(34d)은, 도 9에 도시하는 평면에서 보아, 하층 배선(32b)보다도 스탠다드 셀(51a)의 내측에 위치하는 부분을 갖고 있다. 상층 배선(34d)의 하층 배선(32b)보다도 내측에 위치하는 부분은, 배선층(32h)에 평면적으로 중복되어 있고, 또한 비아홀(33a)를 통해서 배선층(32h)에 전기적으로 접속되어 있다.

전원선의 하층 배선(32a, 32b)의 각각은, 스탠다드 셀(51a)의 경계선을 따라서 직선적으로 연장되어 있고, 그 경계부로부터 스탠다드 셀(51a)의 내측으로 연장되는 분기 부분을 갖고 있지 않다.

상기한 바와 같이, nMOS 트랜지스터 NT1의 소스 영역(11b)은, GND 전위의 전원선의 상층 배선(34c)을 통해서 GND 전위의 전원선의 하층 배선(32a)에 전기적으로 접속되어 있다. 또한 pMOS 트랜지스터 PT1의 소스 영역(21b)은, VDD 전위의 전원선의 상층 배선(34d)을 통해서 VDD 전위의 전원선의 하층 배선(32b)에 전기적으로 접속되어 있다.

또한 신호선(32e1)은, 도 9에 도시하는 평면에서 보아, 전원선의 상층 배선(34c) 및 배선층(32g)의 접속부(비아홀(33a))와 하층 배선(32a) 사이에 위치하도록 배치되어 있다. 신호선(32e2)은, 도 9에 도시하는 평면에서 보아, 전원선의 상층 배선(34d) 및 배선층(32h)의 접속부(비아홀(33a))와 하층 배선(32b) 사이에 위 치하도록 배치되어 있다.

또한, 본 실시 형태의 상기 이외의 구성은, 도 5 및 도 6에 도시하는 실시 형태 2의 구성과 거의 동일하기 때문에, 동일한 요소에 대해서는 동일한 부호를 붙이고, 그 설명을 반복하지 않는다.

본 실시 형태에 따르면, GND 전위의 전원선이 하층 배선(32a)과 상층 배선(34c)으로 분리되어 있고, 또한 VDD 전위의 전원선이 하층 배선(32b)과 상층 배선(34d)으로 분리되어 있다. 이 때문에, 전원선이 단일층인 경우보다도 전류 경로가 늘어나 있기 때문에, 고속화를 도모할 수 있다. 또한, 전원선의 선폭을 굵게 하지 않고 전류 경로를 늘릴 수 있기 때문에, 고집적화를 도모할 수도 있다.

또한 상층 배선(34c, 34d)이 하층 배선(32a, 32b)의 선폭 W1a, W1b보다도 큰 선폭 W2a, W2b를 갖고 있기 때문에, 전원선의 저항값을 저감할 수 있다.

또한 하층 배선(32a, 32b)이 상층 배선(34c, 34d)의 선폭 W2a, W2b보다도 작은 선폭 W1a, W1b를 갖고 있기 때문에, 그 만큼, 배선의 배치를 위한 빈 공간이 커진다. 이 때문에 하층 배선(32a, 32b)과 동일한 층에 다른 배선(예를 들면 신호선(32e1, 32e2)) 등을 배치하는 것이 용이해져, 다른 배선의 평면 레이아웃의 자유도가 높아진다.

또한 하층 배선(32a, 32b)의 각각이, 스탠다드 셀(51a)의 경계를 따라서 연장되어 있다. 이 때문에, 인접하는 스탠다드 셀(51a) 사이에서 하층 배선(32a, 32b)을 공유할 수 있다. 이에 의해 인접하는 스탠다드 셀(51a)의 각각에서 별개로 하층 배선(32a, 32b)을 형성할 필요가 없기 때문에, 고집적화를 도모할 수 있다.

또한 상층 배선(34c, 34d)의 각각이, 스탠다드 셀(51a)의 경계를 따라서 연장되어 있기 때문에, 상기와 마찬가지로, 인접하는 스탠다드 셀(51a)의 각각에서 별개로 상층 배선(34c, 34d)을 형성할 필요가 없기 때문에, 고집적화를 도모할 수 있다.

또한 nMOS 트랜지스터 NT1∼NT3의 각각의 소스 영역(11b)은, GND 전위의 전원선의 상층 배선(34c)을 통해서 GND 전위의 전원선의 하층 배선(32a)에 전기적으로 접속되어 있다. 또한 pMOS 트랜지스터 PT1∼PT3의 각각의 소스 영역(21b)은, VDD 전위의 전원선의 상층 배선(34d)을 통해서 VDD 전위의 전원선의 하층 배선(32b)에 전기적으로 접속되어 있다. 이 때문에, 스탠다드 셀(51a)의 경계에 위치하는 하층 배선(32a, 32b)의 각각을 각 트랜지스터가 위치하는 스탠다드 셀(51a)의 중앙부로 연장할 필요가 없어진다. 이에 의해, 하층 배선(32a, 32b)의 각각을 스탠다드 셀(51a)의 중앙부로 연장할 부분에 빈 공간이 생기기 때문에, 그 빈 공간에 신호선(32e1, 32e2) 등의 다른 배선을 배치하는 것이 가능해져, 고집적화를 도모할 수 있다.

이와 같이 빈 공간에 신호선(32e1, 32e2)을 배치한 결과, 신호선(32e1)은, 도 9에 도시하는 평면에서 보아, 전원선의 상층 배선(34c) 및 배선층(32g)의 접속부와 하층 배선(32a) 사이에 위치하도록 배치될 수 있다. 또한 신호선(32e2)은, 도 9에 도시하는 평면에서 보아, 전원선의 상층 배선(34d) 및 배선층(32h)의 접속부와 하 층 배선(32b) 사이에 위치하도록 배치될 수 있다.

이상으로부터, 고속화 및 고집적화의 쌍방이 양립 가능한 반도체 장치를 얻을 수 있다.

또한 상기의 실시 형태 1∼3에서는, 기능 소자로서 CMOS 인버터를 갖는 소자에 대해서 설명했지만, 본 발명은 이에 한정되는 것이 아니라, CMOS의 NAND나 NOR 회로, 이 이외의 다른 기능 소자에 적용할 수도 있다.

(실시 형태 4)

도 11 및 도 12를 참조하여, 본 실시 형태의 회로는, 2입력의 NAND 게이트NA1, NA2와, 버퍼 BU1, BU2, BU3과, 인버터 IN을 갖고 있다.

2입력의 NAND 게이트 NA1은, 도 12에 도시하는 바와 같이 접속된 pMOS 트랜지스터 PT11, PT12와, nMOS 트랜지스터 NT11, NT12를 갖고 있다. pMOS 트랜지스터 PT11과 nMOS 트랜지스터 NT11의 각 게이트에는 단자 A가 전기적으로 접속되어 있고, pMOS 트랜지스터 PT12와 nMOS 트랜지스터 NT12의 각 게이트에는 단자 B가 전기적으로 접속되어 있다.

버퍼 BU1은, pMOS 트랜지스터 PT13 및 nMOS 트랜지스터 NT13으로 이루어지는CMOS 인버터와, pMOS 트랜지스터 PT14 및 nMOS 트랜지스터 NT14로 이루어지는 CMOS 인버터에 의해 구성되어 있다. 이 버퍼 BU1은, NAND 게이트 NA1의 출력이 입력되도록 구성되어 있다.

버퍼 BU2는, pMOS 트랜지스터 PT15 및 nMOS 트랜지스터 NT15로 이루어지는CMOS 인버터와, pMOS 트랜지스터 PT16 및 nMOS 트랜지스터 NT16으로 이루어지는 CMOS 인버터에 의해 구성되어 있다. 이 버퍼 BU2는, 버퍼 BU1의 출력이 입력되도록 구성되어 있다.

버퍼 BU3은, pMOS 트랜지스터 PT17 및 nMOS 트랜지스터 NT17로 이루어지는 CMOS 인버터와, pMOS 트랜지스터 PT18 및 nMOS 트랜지스터 NT18로 이루어지는 CMOS 인버터에 의해 구성되어 있다. pMOS 트랜지스터 PT17 및 nMOS 트랜지스터 NT17의 각 게이트에는 단자 C가 전기적으로 접속되어 있다.

2입력의 NAND 게이트 NA2는, 도 12에 도시하는 바와 같이 접속된 pMOS 트랜지스터 PT19, PT20과, nMOS 트랜지스터 NT19, NT20을 갖고 있다. pMOS 트랜지스터 PT19와 nMOS 트랜지스터 NT19의 각 게이트에는 버퍼 BU2의 출력이 전기적으로 접속되어 있다. pMOS 트랜지스터 PT20과 nMOS 트랜지스터 NT20의 각 게이트에는 버퍼 BU3의 출력이 전기적으로 접속되어 있다.

인버터 IN은, pMOS 트랜지스터 PT21 및 nMOS 트랜지스터 NT21로 이루어지는 CMOS 인버터에 의해 구성되어 있다. pMOS 트랜지스터 PT21 및 nMOS 트랜지스터 NT21의 각 게이트에는 NAND 게이트 NA2의 출력이 전기적으로 접속되어 있다. 또한 인버터 IN의 출력은 단자 Y에 전기적으로 접속되어 있다.

다음으로, 도 11 및 도 12에 도시하는 회로를 구성하는 반도체 장치의 평면 레이아웃 구성에 대해서 설명한다.

도 13은 반도체 기판에 형성된 확산 영역 및 소자 분리 영역과, 반도체 기판 위에 형성된 게이트 전극층 등의 다결정 실리콘층을 도시하고 있다. 도 14는 상기의 다결정 실리콘층과 그 위의 제1층째의 금속층을 주로 도시하고 있다. 또한 도 15는 상기의 제1층째의 금속층과 그 위의 제2층째의 금속층과 제3층째의 금속층을 도시하고 있다.

도 13을 참조하여, 반도체 기판 SUB의 표면에는, NAND 게이트의 형성 영역 NA1, NA2와, 버퍼의 형성 영역 BU1, BU2, BU3과, 인버터의 형성 영역 IN과, 회로 비구성 영역 NON이 있다. 이들 형성 영역의 각각은 스탠다드 셀이다.

버퍼의 형성 영역 BU3과, 회로 비구성 영역 NON과, 인버터의 형성 영역 IN은, 이 순으로 도면 내의 X방향으로 나열되어 배치되어 있다. 또한 NAND 게이트의 형성 영역 NA1과, 버퍼의 형성 영역 BU1과, 버퍼의 형성 영역 BU2와, NAND 게이트의 형성 영역 NA2는, 이 순으로 도면 내의 X방향으로 나열되어 배치되어 있다.

NAND 게이트의 형성 영역 NA1에는, 상기의 pMOS 트랜지스터 PT11, PT12와, nMOS 트랜지스터 NT11, NT12가 형성되어 있다. 버퍼의 형성 영역 BU1에는, 상기의 pMOS 트랜지스터 PT13, PT14와, nMOS 트랜지스터 NT13, NT14가 형성되어 있다. 버퍼의 형성 영역 BU2에는, 상기의 pMOS 트랜지스터 PT15, PT16과, nMOS 트랜지스터 NT15, NT16이 형성되어 있다. NAND 게이트의 형성 영역 NA2에는, 상기의 pMOS 트랜지스터 PT19, PT20과, nMOS 트랜지스터 NT19, NT20이 형성되어 있다.

버퍼의 형성 영역 BU3에는, 상기의 pMOS 트랜지스터 PT17, PT18과, nMOS 트랜지스터 NT17, NT18이 형성되어 있다. 인버터의 형성 영역 IN에는, 상기의 pMOS 트랜지스터 PT21 및 nMOS 트랜지스터 NT21이 형성되어 있다.

버퍼의 형성 영역 BU3, 회로 비구성 영역 NON 및 인버터의 형성 영역 IN의 도면 내의 Y방향 상측의 경계를 따라서 도면 내의 X방향으로 연장되도록 반도체 기 판 SUB 내의 표면에는 p+ 영역 PR1이 형성되어 있다. 또한 NAND 게이트의 형성 영역 NA1, 버퍼의 형성 영역 BU1, BU2 및 NAND 게이트의 형성 영역 NA2의 도면 내의 Y방향 하측의 경계를 따라서 도면 내의 X방향으로 연장되도록 반도체 기판 SUB 내의 표면에는 p+ 영역 PR2가 형성되어 있다.

또한 버퍼의 형성 영역 BU3, 회로 비구성 영역 NON 및 인버터의 형성 영역 IN의 도면 내의 Y방향 하측의 경계로서, NAND 게이트의 형성 영역 NA1, 버퍼의 형성 영역 BU1, BU2 및 NAND 게이트의 형성 영역 NA2의 도면 내의 Y방향 상측의 경계를 따라서 n+ 영역 NR이 형성되어 있다. 이 n+ 영역 NR도 그 경계를 따라서 도면 내의 X방향으로 연장되도록 반도체 기판 SUB 내의 표면에 형성되어 있다.

도 14를 참조하여, MOS 트랜지스터 위에는, 층간 절연층(도시하지 않음)을 개재하여, 패터닝된 제1층째의 금속층이 형성되어 있다. 이 제1층째의 금속층은, GND 전위의 전원선의 하층 배선 GNDL1, GNDL2와, VDD 전위의 전원선의 하층 배선 VDDL과, 그 밖의 신호선 SL1을 갖고 있다.

하층 배선 GNDL1은, 버퍼의 형성 영역 BU3, 회로 비구성 영역 NON 및 인버터의 형성 영역 IN의 도면 내의 Y방향 상측의 경계를 따라서 도면 내의 X방향으로 연장되어 있다. 이 하층 배선 GNDL1은, 하층의 p+ 영역 PR1에 복수개의 컨택트홀 CH를 통해서 전기적으로 접속되어 있다.

하층 배선 GNDL2는, NAND 게이트의 형성 영역 NA1, 버퍼의 형성 영역 BU1, BU2 및 NAND 게이트의 형성 영역 NA2의 도면 내의 Y방향 하측의 경계를 따라서 도면 내의 X방향으로 연장되어 있다. 이 하층 배선 GNDL2는, 하층의 p+ 영역 PR2에 복수개의 컨택트홀 CH를 통해서 전기적으로 접속되어 있다.

하층 배선 VDDL은, 버퍼의 형성 영역 BU3, 회로 비구성 영역 NON 및 인버터의 형성 영역 IN의 도면 내의 Y방향 하측의 경계로서, NAND 게이트의 형성 영역 NA1, 버퍼의 형성 영역 BU1, BU2 및 NAND 게이트의 형성 영역 NA2의 도면 내의 Y방향 상측의 경계를 따라서 도면 내의 X방향으로 연장되어 있다. 하층 배선 VDDL은, 하층의 n+ 영역 NR에 복수개의 컨택트홀 CH를 통해서 전기적으로 접속되어 있다.

도 15를 참조하여, 제1층째의 금속층 위에는, 층간 절연층(도시하지 않음)을 개재하여, 패터닝된 제2층째의 금속층이 형성되어 있다. 이 제2층째의 금속층은, GND 전위의 전원선의 상층 배선 GNDU1, GNDU2와, VDD 전위의 전원선의 상층 배선 VDDU와, 그 밖의 신호선 SL2를 갖고 있다.

상층 배선 GNDU1은, 버퍼의 형성 영역 BU3, 회로 비구성 영역 NON 및 인버터의 형성 영역 IN의 도면 내의 Y방향 상측의 경계를 따라서 도면 내의 X방향으로 연장되어 있다. 이 상층 배선 GNDU1은, 하층의 하층 배선 GNDL1에 복수개의 비아홀 VH1을 통해서 전기적으로 접속되어 있다. 또한 상층 배선 GNDU1은, 하층 배선 GNDL1의 선폭 W1a1보다도 큰 선폭 W2a1을 갖고 있다.

상층 배선 GNDU2는, NAND 게이트의 형성 영역 NA1, 버퍼의 형성 영역 BU1, BU2 및 NAND 게이트의 형성 영역 NA2의 도면 내의 Y방향 하측의 경계를 따라서 도 면 내의 X방향으로 연장되어 있다. 이 상층 배선 GNDU2는, 하층의 하층 배선 GNDL2에 복수개의 비아홀 VH1을 통해서 전기적으로 접속되어 있다. 또한 상층 배선 GNDU2는, 하층 배선 GNDL2의 선폭 W1a2보다도 큰 선폭 W2a2를 갖고 있다.

상층 배선 VDDU는, 버퍼의 형성 영역 BU3, 회로 비구성 영역 NON 및 인버터의 형성 영역 IN의 도면 내의 Y방향 하측의 경계로서, NAND 게이트의 형성 영역 NA1, 버퍼의 형성 영역 BU1, BU2 및 NAND 게이트의 형성 영역 NA2의 도면 내의 Y방향 상측의 경계를 따라서 도면 내의 X방향으로 연장되어 있다. 이 상층 배선 VDDU는, 하층의 하층 배선 VDDL에 복수개의 비아홀 VH1을 통해서 전기적으로 접속되어 있다. 또한 상층 배선 VDDU는, 하층 배선 VDDL의 선폭 W1b보다도 큰 선폭 W2b를 갖고 있다.

이 제2층째의 금속층 위에는, 층간 절연층(도시하지 않음)을 개재하여, 패터닝된 제3층째의 금속층이 형성되어 있다. 이 제3층째의 금속층은, GND 전위의 전원선의 전위를 보강하는 보강 배선 GNDS와, VDD 전위의 전원선의 전위를 보강하는 보강 배선 VDDS와, 그 밖의 신호선 SL3을 갖고 있다.

보강 배선 GNDS 및 보강 배선 VDDS의 각각은, 평면에서 보아 상층 배선 GNDU1, GNDU2, VDDU에 직교하는 방향(즉 도면 내의 Y방향)으로 연장되어 있다. 보강 배선 GNDS는, 평면에서 보아 상층 배선 GNDU1, GNDU2의 각각에 교차하고 있고, 1개의 교점에서 복수개(예를 들면 4개)의 비아홀 VH2에 의해 상층 배선 GNDU1, GNDU2의 각각과 전기적으로 접속되어 있다. 또한 보강 배선 VDDS는, 평면에서 보 아 상층 배선 VDDU에 교차하고 있고, 1개의 교점에서 복수개(예를 들면 4개)의 비아홀 VH2에 의해 상층 배선 VDDU와 전기적으로 접속되어 있다.

또한 각 층에서의 신호선 SL1, SL2, SL3은, MOS 트랜지스터의 각각을 도 11 및 도 12에 도시하는 회로 구성으로 되도록 전기적으로 접속하고 있다. 또한 도 13에서, 사선으로 나타내어진 부위는 반도체 기판 위에 형성된 게이트 전극층 등의 다결정 실리콘층이며, 물방울 모양으로 나타내어진 부위는 반도체 기판에 형성된 확산 영역이다. 이들 다결정 실리콘층이나 확산 영역은 MOS 트랜지스터의 각각을 도 11 및 도 12에 도시하는 회로 구성으로 되도록 전기적으로 접속되어 있다.

또한 도 15에 도시하는 하층 배선 GNDL1과 상층 배선 GNDU1을 접속하는 복수개의 비아홀 VH1의 배치 피치 Pv는, 도 13에 도시하는 트랜지스터의 배치 피치 PT와 동일 피치이다. 또한 하층 배선 GNDL2와 상층 배선 GNDU2를 접속하는 복수개의 비아홀 VH1의 배치 피치 Pv 및 하층 배선 VDDL과 상층 배선 VDDU를 접속하는 복수개의 비아홀 VH1의 배치 피치 Pv도, 도 13에 도시하는 트랜지스터의 배치 피치 PT와 동일 피치이다. 이에 의해, 전원선의 저항값을 저감할 수 있음과 함께, 하층 배선과 상층 배선의 전위를 강화할 수 있다.

도 16을 참조하여, 복수개의 보강 배선 GNDS, VDDS와 복수개의 상층 배선 GNDU, VDDU는 평면에서 보아 격자를 구성하도록 배치되어 있다.

복수개의 보강 배선 GNDS의 각각은, 복수개의 상층 배선 GNDU(GNDU1, GNDU2를 포함함)에 비아홀 VH2를 통해서 전기적으로 접속되어 있다. 또한 복수개의 보 강 배선 VDDS의 각각은, 복수개의 상층 배선 VDDU에 비아홀 VH2를 통해서 전기적으로 접속되어 있다.

본 실시 형태에 따르면, GND 전위의 전원선이 하층 배선 GNDL1, GNDL2와 상층 배선 GNDU1, GNDU2로 분리되어 있고, 또한 VDD 전위의 전원선이 하층 배선 VDDL과 상층 배선 VDDU로 분리되어 있다. 이 때문에, 전원선이 단일층인 경우보다도 전류 경로가 늘어나 있기 때문에, 고속화를 도모할 수 있다. 또한, 전원선의 선폭을 굵게 하지 않고 전류 경로를 늘릴 수 있기 때문에, 고집적화를 도모할 수도 있다.

또한 상층 배선 GNDU1, GNDU2, VDDU의 선폭 W2a1, W2a2, W2b의 각각이, 하층 배선 GNDL1, GNDL2, VDDL의 선폭 W1a1, W1a2, W1b보다도 크기 때문에, 전원선의 저항값을 저감할 수 있다.

또한 하층 배선 GNDL1, GNDL2, VDDL의 선폭 W1a1, W1a2, W1b의 각각이, 상층 배선 GNDU1, GNDU2, VDDU의 선폭 W2a1, W2a2, W2b보다도 작기 때문에, 그 만큼, 배선의 배치를 위한 빈 공간이 커진다. 이 때문에 하층 배선 GNDL1, GNDL2, VDDL과 동일한 층에 다른 배선 등을 배치하는 것이 용이해져, 다른 배선의 평면 레이아웃의 자유도가 높아진다.

또한 하층 배선 GNDL1, GNDL2, VDDL 및 상층 배선 GNDU1, GNDU2, VDDU가, 각각 스탠다드 셀의 경계를 따라서 연장되어 있다. 이 때문에, 인접하는 스탠다드 셀의 각각에서 이들 전원선을 공유할 수 있다. 이에 의해, 각 스탠다드 셀마다 별 개로 이들 전원선을 형성할 필요가 없기 때문에, 고집적화를 도모할 수 있다.

또한 제1층째의 금속층의 신호선 SL1은 스탠다드 셀 내 배선으로서 이용되고 있다. 제2층째의 금속층의 신호선 SL2는 도면 내의 X방향을 따라서 연장되고, 하층 배선 GNDL1, GNDL2, VDDL과 같은 전원계의 배선 사이에 끼워지도록 배치된 스탠다드 셀 사이를 접속하는 배선으로서 이용되고 있다. 또한 제3층째의 금속층의 신호선 SL3은 도면 내의 Y방향을 따라서 연장되고, 하층 배선 GNDL1, GNDL2, VDDL과 같은 전원계의 배선을 걸치는 스탠다드 셀 사이를 접속하는 배선으로서 이용되고 있다. 이에 의해, P&R(Place and Route: 자동 배선 배치)에서의 배선 설계가 용이해진다.

이상으로부터, 고속화 및 고집적화의 쌍방이 양립 가능한 반도체 장치를 얻을 수 있다.

(실시 형태 5)

본 실시 형태에서는, 고속 셀과 고집적 셀을 갖는 반도체 장치에 대해서 설명한다.

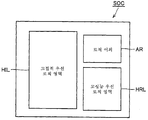

도 17을 참조하여, SOC 칩 SOC는, 예를 들면 고집적 우선의 로직 영역 HIL과, 고성능 우선의 로직 영역 HRL과, 로직 이외의 영역 AR을 갖고 있다. 고집적 우선의 로직 영역 HIL에는, 고속 동작에 알맞은 고속 셀이 형성되어 있다. 또한 고성능 우선의 로직 영역 HRL에는, 고집적화에 알맞은 고집적 셀이 형성되어 있다.

도 18은 반도체 기판에 형성된 확산 영역 및 소자 분리 영역과, 반도체 기판 위에 형성된 게이트 전극층 등의 다결정 실리콘층을 도시하고 있다. 도 19는 상기 의 다결정 실리콘층과 그 위의 제1층째의 금속층을 주로 도시하고 있다. 또한 도 20은 상기의 제1층째의 금속층과 그 위의 제2층째의 금속층을 주로 도시하고 있다.

도 18을 참조하여, 고속 셀 및 고집적 셀의 쌍방 모두, pMOS 트랜지스터 PT와 nMOS 트랜지스터 NT로 이루어지는 CMOS 인버터로 이루어져 있다.

고속 셀 및 고집적 셀 중 어느 것에서도, pMOS 트랜지스터 PT는, 1쌍의 p형 소스/드레인 영역 SD와, 게이트 절연막(도시하지 않음)과, 게이트 전극층 GE를 갖고 있다. 1쌍의 p형 소스/드레인 영역 SD의 각각은, 반도체 기판 SUB의 표면에 형성되어 있다. 게이트 전극층 GE는, 1쌍의 p형 소스/드레인 영역 SD 사이에 끼워지는 반도체 기판 SUB의 표면 위에 게이트 절연막을 개재하여 형성되어 있다.

고속 셀 및 고집적 셀 중 어느 것에서도, nMOS 트랜지스터 NT는, 1쌍의 n형 소스/드레인 영역 SD와, 게이트 절연막(도시하지 않음)과, 게이트 전극층 GE를 갖고 있다. 1쌍의 n형 소스/드레인 영역 SD의 각각은, 반도체 기판 SUB의 표면에 형성되어 있다. 게이트 전극층 GE는, 1쌍의 n형 소스/드레인 영역 SD 사이에 끼워지는 반도체 기판 SUB의 표면 위에 게이트 절연막을 개재하여 형성되어 있다.

고속 셀 및 고집적 셀 중 어느 것에서도, pMOS 트랜지스터 PT의 게이트 전극층 GE와 nMOS 트랜지스터 NT의 게이트 전극층 GE는 일체화되어 서로 전기적으로 접속되어 있다.

고속 셀 및 고집적 셀 중 어느 것에서도, 스탠다드 셀 영역의 도면 내의 Y방향 상측의 경계를 따라서 도면 내의 X방향으로 연장되도록 반도체 기판 SUB 내의 표면에는 n+ 영역 NIR이 형성되어 있다. 또한 스탠다드 셀 영역의 도면 내의 Y방향 하측의 경계를 따라서 도면 내의 X방향으로 연장되도록 반도체 기판 SUB 내의 표면에는 p+ 영역 PIR이 형성되어 있다.

여기서, 고속 셀에서의 CMOS 인버터의 평면 레이아웃과 고집적 셀에서의 CMOS 인버터의 평면 레이아웃은 동일하다. 또한 고속 셀에서의 n+ 영역 NIR 및 p+ 영역 PIR의 각각의 평면 레이아웃과 고집적 셀에서의 n+ 영역 NIR 및 p+ 영역 PIR의 각각의 평면 레이아웃은 동일하다.

도 19를 참조하여, MOS 트랜지스터 PT, NT 위에는, 층간 절연층(도시하지 않음)을 개재하여, 패터닝된 제1층째의 금속층이 형성되어 있다. 이 제1층째의 금속층은, GND 전위의 전원선의 하층 배선 GND, GNDL과, VDD 전위의 전원선의 하층 배선 VDD, VDDL과, 그 밖의 신호선 SLL1, SLL2를 갖고 있다.

하층 배선 GNDL은, 고속 셀에서의 스탠다드 셀 영역의 도면 내의 Y방향 하측의 경계를 따라서 도면 내의 X방향으로 연장되어 있다. 이 하층 배선 GNDL은, 하층의 p+ 영역 PIR에 복수개의 컨택트홀 CH를 통해서 전기적으로 접속되어 있다. 또한 하층 배선 GNDL은, nMOS 트랜지스터 NT의 소스/드레인 영역 SD의 한쪽에 복수개의 컨택트홀 CH를 통해서 전기적으로 접속되어 있다.

하층 배선 VDDL은, 고속 셀에서의 스탠다드 셀 영역의 도면 내의 Y방향 상측의 경계를 따라서 도면 내의 X방향으로 연장되어 있다. 이 하층 배선 VDDL은, 하 층의 n+ 영역 NIR에 복수개의 컨택트홀 CH를 통해서 전기적으로 접속되어 있다. 또한 하층 배선 VDDL은, pMOS 트랜지스터 PT의 소스/드레인 영역 SD의 한쪽에 복수개의 컨택트홀 CH를 통해서 전기적으로 접속되어 있다.

신호선 SLL1은, nMOS 트랜지스터 NT의 소스/드레인 영역 SD의 다른 쪽과 pMOS 트랜지스터 PT의 소스/드레인 영역 SD의 다른 쪽의 각각에 컨택트홀 CH를 통해서 전기적으로 접속되어 있다. 신호선 SLL2는, 게이트 전극층 GE에 컨택트홀 CH를 통해서 전기적으로 접속되어 있다.

여기서, 고속 셀에서의 하층 배선 GNDL 및 하층 배선 VDDL의 각각의 평면 레이아웃과 고집적 셀에서의 하층 배선 GND 및 하층 배선 VDD의 각각의 평면 레이아웃은 동일하다. 또한 고속 셀에서의 신호선 SLL1 및 신호선 SLL2의 평면 레이아웃과 고집적 셀에서의 신호선 SLL1 및 신호선 SLL2의 평면 레이아웃은 동일하다.

도 20을 참조하여, 제1층째의 금속층 위에는, 층간 절연층(도시하지 않음)을 개재하여, 패터닝된 제2층째의 금속층이 형성되어 있다. 이 제2층째의 금속층은, GND 전위의 전원선의 상층 배선 GNDU와, VDD 전위의 전원선의 상층 배선 VDDU와, 그 밖의 신호선 SLU1~SLU4를 갖고 있다.

상층 배선 GNDU는, 고속 셀에서의 스탠다드 셀 영역의 도면 내의 Y방향 하측의 경계를 따라서 도면 내의 X방향으로 연장되어 있다. 이 상층 배선 GNDU는, 하층의 하층 배선 GNDL에 복수개의 비아홀 VH1을 통해서 전기적으로 접속되어 있다. 또한 상층 배선 GNDU는, 하층 배선 GNDL의 선폭 W1a보다도 큰 선폭 W2a를 갖고 있 다.

상층 배선 VDDU는, 고속 셀에서의 스탠다드 셀 영역의 도면 내의 Y방향 상측의 경계를 따라서 도면 내의 X방향으로 연장되어 있다. 이 상층 배선 VDDU는, 하층의 하층 배선 VDDL에 복수개의 비아홀 VH1을 통해서 전기적으로 접속되어 있다. 또한 상층 배선 VDDU는, 하층 배선 VDDL의 선폭 W1b보다도 큰 선폭 W2b를 갖고 있다.

또한 신호선 SLU3, SLU4의 각각은, 고속 셀에서의 스탠다드 셀 내에 형성되어 있다. 이들 신호선 SLU3, SLU4의 각각은, 도면 내의 X방향(즉 평면에서 보아 상층 배선 GNDU, VDDU가 연장되는 방향과 동일한 방향)으로 연장되어 고속 셀에서의 스탠다드 셀 영역의 경계를 횡단하고 있다. 신호선 SLU3은 비아홀 VH1을 통해서 신호선 SLL1에 전기적으로 접속되어 있다. 또한 신호선 SLU4는 비아홀 VH1을 통해서 신호선 SLL2에 전기적으로 접속되어 있다.

또한 고집적 셀의 스탠다드 셀 내에서는, 신호선 SLU1, SLU2의 각각은, 도면 내의 Y방향(즉 평면에서 보아 하층 배선 GND, VDD가 연장되는 방향과 직교하는 방향)으로 연장되어 있다. 신호선 SLU1은 비아홀 VH1을 통해서 신호선 SLL1에 전기적으로 접속되어 있다. 또한 신호선 SLU2는 비아홀 VH1을 통해서 신호선 SLL2에 전기적으로 접속되어 있다.

또한 신호선 SLU1, SLU2의 각각은, 도면 내의 Y방향으로 연장되어 고집적 셀에서의 스탠다드 셀 영역의 경계를 횡단하여도 된다.

다음으로, 고집적 우선의 로직 영역 HIL과 고성능 우선의 로직 영역 HRL의 각각에서의 복수의 스탠다드 셀에 관해서 설명한다.

도 21은 제1층째의 금속층을 도시하고 있다. 도 22는 제1층째의 금속층과, 그 위의 제2층째의 금속층을 도시하고 있다. 도 23은 제1층째 및 제2층째의 금속층과, 그 위의 제3층째의 금속층과, 또한 그 위의 제4 금속층을 도시하고 있다.

도 21을 참조하여, 복수의 스탠다드 셀의 경우라도 단일의 스탠다드 셀의 경우와 마찬가지로, 제1층째의 금속층과 그보다 아래의 층의 각각의 평면 레이아웃 구조는, 고속 셀과 고집적 셀에서 동일하다.

도 22 및 도 23을 참조하여, 복수의 스탠다드 셀의 경우라도 단일의 스탠다드 셀의 경우와 마찬가지로, 제2층째의 금속층과 그보다 위의 층(예를 들면 제3 및 제4 금속층)의 각각의 평면 레이아웃 구조는, 고속 셀과 고집적 셀에서 서로 다르다.

고속 셀에서는, 제2층째의 금속층으로 이루어지는 상층 배선 GNDU, VDDU가, 하층 배선 GNDL, VDDL의 선폭보다도 작은 선폭으로 스탠다드 셀의 경계를 따라서 연장되도록 형성되어 있다. 또한 제2층째의 금속층으로 이루어지는 신호선 SLU는, 하층 배선 GNDL, VDDL이 연장되는 방향과 동일한 방향으로 연장되어 있다.

한편, 고집적 셀에서는, 제2층째의 금속층으로 이루어지는 상층 배선 GNDU, VDDU는 형성되어 있지 않다. 또한 제2층째의 금속층으로 이루어지는 신호선 SLU는, 하층 배선 GNDL, VDDL이 연장되는 방향과 직교하는 방향으로 연장되어 있다.

고속 셀에서는, 도 22에 도시하는 바와 같이, 제2층째의 금속층으로 이루어지는 상층 배선 GNDU, VDDU가 형성되어 있다. 이 때문에, 제2층째의 금속층으로 이루어지는 신호선 SLU를, 도면 내의 Y방향 상측의 스탠다드 셀과 하측의 스탠다드 셀의 경계를 걸치도록 연장할 수 없다. 따라서, 고속 셀에서는, 도 23에 도시하는 바와 같이, 제3층째의 금속층과 제4층째의 금속층을 이용하지 않으면, 도면 내의 Y방향으로 인접하는 스탠다드 셀 내의 소자끼리와, 도면 내의 X방향으로 인접하는 스탠다드 셀 내의 소자끼리를 전기적으로 접속할 수 없다.

즉, 제3층째의 금속층으로 이루어지는 신호선 SL3을 도면 내의 Y방향의 상하의 스탠다드 셀 간의 경계를 걸치도록 배치함으로써, 도면 내의 Y방향으로 인접하는 스탠다드 셀 내의 소자끼리를 전기적으로 접속하는 것이 가능해진다. 또한 제4층째의 금속층으로 이루어지는 신호선 SL4를 도면 내의 X방향의 좌우의 스탠다드 셀 간의 경계를 걸치도록 배치함으로써, 도면 내의 X방향에 인접하는 스탠다드 셀 내의 소자끼리를 전기적으로 접속하는 것이 가능해진다.

한편, 고집적 셀에서는, 도 22에 도시하는 바와 같이, 제2층째의 금속층으로 이루어지는 상층 배선 GNDU, VDDU가 형성되어 있지 않다. 이 때문에, 제2층째의 금속층으로 이루어지는 신호선 SLU를, 도면 내의 Y방향 상하에 인접하는 스탠다드 셀 간의 경계를 걸치도록 연장하는 것이 가능하다. 따라서, 고집적 셀에서는, 도 23에 도시하는 바와 같이, 제4층째의 금속층을 이용하지 않더라도, 제2층째의 금속층과 제3층째의 금속층을 이용하여, 도면 내의 Y방향으로 인접하는 스탠다드 셀 내의 소자끼리와, 도면 내의 X방향으로 인접하는 스탠다드 셀 내의 소자끼리를 전기적으로 접속할 수 있다.

즉, 제2층째의 금속층으로 이루어지는 신호선 SLU를 도면 내의 Y방향의 상하 의 스탠다드 셀 간의 경계를 걸치도록 배치함으로써, 도면 내의 Y방향으로 인접하는 스탠다드 셀 내의 소자끼리를 전기적으로 접속하는 것이 가능해진다. 또한 제3층째의 금속층으로 이루어지는 신호선 SL3을 도면 내의 X방향의 좌우의 스탠다드 셀 간의 경계를 걸치도록 배치함으로써, 도면 내의 X방향으로 인접하는 스탠다드 셀 내의 소자끼리를 전기적으로 접속하는 것이 가능해진다.

본 실시 형태에 따르면, 고속 셀의 스탠다드 셀 내에서, GND 전위의 전원선이 하층 배선 GNDL과 상층 배선 GNDU로 분리되어 있고, 또한 VDD 전위의 전원선이 하층 배선 VDDL과 상층 배선 VDDU로 분리되어 있다. 이 때문에, 전원선이 단일층인 경우보다도 전류 경로가 늘어나 있기 때문에, 고속화를 도모할 수 있다. 또한, 전원선의 선폭을 굵게 하지 않고 전류 경로를 늘릴 수 있기 때문에, 고집적화를 도모할 수도 있다.

또한 상층 배선 GNDU, VDDU의 선폭 W2a, W2b의 각각이, 하층 배선 GNDL, VDDL의 선폭 W1a, W1b보다도 크기 때문에, 전원선의 저항값을 저감할 수 있다.

또한 하층 배선 GNDL, VDDL의 선폭 W1a, W1b의 각각이, 상층 배선 GNDU, VDDU의 선폭 W2a, W2b보다도 작기 때문에, 그 만큼, 배선의 배치를 위한 빈 공간이 커진다. 이 때문에 하층 배선과 동일한 층에 다른 배선 등을 배치하는 것이 용이해져, 다른 배선의 평면 레이아웃의 자유도가 높아진다.

또한 하층 배선 GNDL, VDDL 및 상층 배선 GNDU, VDDU의 각각이, 스탠다드 셀의 경계를 따라서 연장되어 있다. 이 때문에, 인접하는 스탠다드 셀의 각각에서 이들 전원선을 공유할 수 있다. 이에 의해, 각 스탠다드 셀마다 별개로 이들 전원 선을 형성할 필요가 없기 때문에, 고집적화를 도모할 수 있다.

이상으로부터, 고속화 및 고집적화의 쌍방이 양립 가능한 반도체 장치를 얻을 수 있다.

또한 본 실시 형태에 따르면, 제1층째의 금속층과 그보다 하층의 평면 레이아웃이, 고속 셀과 고집적 셀에서 공통화되어 있다. 이 때문에, 평면 레이아웃의 설계가 용이해진다. 이 설계에서의 P&R(Place and Route: 자동 배선 배치) 플로우는 이하와 같다.

우선, 제1층째의 금속층과 그보다 하층의 평면 레이아웃이 고속 셀과 고집적 셀의 공통 레이아웃으로서 표준 셀 라이브러리에 등록된다. 한편, 고속 셀의 단자 액세스에 사용하는 비아홀과 고집적 셀의 단자 액세스에 사용하는 비아홀을 등록한 테크놀로지 파일이 준비된다.

P&R 플로우에서는, 표준 셀 라이브러리에 등록된 공통의 레이아웃으로부터 P&R 테크놀로지 파일의 등록 데이터를 추가함으로써, 고속 셀과 고집적 셀을 설계할 수 있다.

이와 같이 제1층째의 금속층과 그보다 하층의 평면 레이아웃이 고속 셀과 고집적 셀에서 공통화되어 있기 때문에, 고속 셀과 고집적 셀에서 셀 구조가 서로 다른 복수의 라이브러리를 준비할 필요가 없어져, 설계가 용이해진다.

또한 제2층째의 금속층과 그보다 상층의 패턴을 변경하는 것만으로, 고집적 우선의 로직 영역 HIL에는 고속 셀이 형성되고, 또한 고성능 우선의 로직 영역 HRL에는 고집적 셀이 형성되어 있다. 이에 의해, 고속 셀과 고집적 셀에서 제2층째의 금속층과 그보다 하층의 평면 패턴을 동일하게 할 수 있기 때문에, 고속화 및 고집적화의 쌍방이 양립 가능한 반도체 장치의 패턴 설계를 용이하게 할 수 있다.

또한 본 실시 형태에서는, 고집적 우선의 로직 영역 HIL에는 고속 셀이 형성되고, 또한 고성능 우선의 로직 영역 HRL에는 고집적 셀이 형성되어 있다. 이 고속 셀에서는, 전원선(VDD 배선, GND 배선)이 하층 배선 GNDL, VDDL과 상층 배선 GNDU, VDDU로 분배되어 있다. 이 때문에, 전원선이 단일층인 경우보다도 전류 경로가 늘어나 있기 때문에, 고속화를 도모할 수 있다.

또한 고집적 셀에서는, 전원선(VDD 배선, GND 배선)이 단일층으로 이루어져 있기 때문에, 적층 방향의 고집적화를 도모할 수 있다. 또한, 전원선(VDD 배선, GND 배선)이 단일층으로 이루어져 있기 때문에, 제2층째의 금속층으로 이루어지는 신호선을 고속 셀보다도 자유롭게 배치할 수 있다. 예를 들면 도 20에 도시하는 바와 같이, 제2층째의 금속층으로 이루어지는 신호선을, 하층 배선 GND, VDD에 대하여 평면에서 보아 직교하는 방향으로 연장하여 스탠다드 셀의 경계를 횡단시키는 것도 가능해진다. 이에 의해, 제2층째의 금속층으로 이루어지는 신호선의 평면 레이아웃의 자유도가 높아진다.

(실시 형태 6)

도 24를 참조하여, 본 실시 형태의 구성은, 도 21∼도 23에 도시하는 실시 형태 5의 구성과 비교하여, 고속 셀의 평면 레이아웃에 대하여 고집적 셀의 평면 레이아웃을 상대적으로 90°회전시킨 구성을 갖는 점에서 상이하다.

이에 의해, 제3층째의 금속층으로 이루어지는 신호선 SL3이 연장되는 방향이 고속 셀 및 고집적 셀의 쌍방에서 동일한 방향으로 할 수 있다.

또한, 본 실시 형태의 상기 이외의 구성은, 도 21∼도 23에 도시하는 실시 형태 5의 구성과 거의 동일하기 때문에, 동일한 요소에 대해서는 동일한 부호를 붙이고, 그 설명을 반복하지 않는다.

본 실시 형태에 따르면, 제3층째의 금속층으로 이루어지는 신호선 SL3이 연장되는 방향을 고속 셀과 고집적 셀에서 동일한 방향으로 할 수 있기 때문에, 배선 설계가 용이해진다. 이에 의해, 집적도의 향상 및 자동 배선의 수속 시간의 단축 등을 도모할 수 있다.

또한 상기의 실시 형태 1∼6에서는, 대향하여 서로 인접하는 스탠다드 셀 내의 기능 소자 및 배선의 평면 레이아웃 구성이, 그들의 스탠다드 셀의 경계선에 대하여 선대칭의 구성을 갖고 있어도 된다. 특히 복수 종류의 스탠다드 셀 간에서, 스탠다드 셀 경계에 형성된 그라운드 배선이나 전원 배선은, 셀 경계에서 선대칭의 구조로 되어 있다. 이에 따라 이 셀 경계 상하에 존재하는 스탠다드 셀에서 그라운드 배선이나 전원 배선을 공통화할 수 있어, 레이아웃의 축소나 P&R(Place and Route: 자동 배선 배치)에서의 셀 배치 설계가 용이해진다.

또한 상기의 실시 형태 4∼6에서는, 기능 소자로서 CMOS 인버터, NAND 등을 갖는 소자에 대해서 설명했지만, 본 발명은 이에 한정되는 것이 아니라, CMOS의 NAND나 NOR 회로, 플립플롭 회로, 트라이스테이트 버퍼 회로, 이 이외의 다른 기능 소자에 적용할 수도 있다.

본 발명은, 배열된 복수개의 스탠다드 셀을 갖는 반도체 장치에 특히 유리하 게 적용될 수 있다.

금회 개시된 실시 형태는 모든 점에서 예시이며 제한적인 것은 아니라고 생각되어야 한다. 본 발명의 범위는 상기한 설명이 아니라 특허 청구 범위에 의해 나타내어지고, 특허 청구의 범위와 균등한 의미 및 범위 내에서의 모든 변경이 포함되는 것이 의도된다.

도 1은 본 발명의 실시 형태 1에서의 반도체 장치의 구성을 개략적으로 도시 하는 평면도.

도 2는 도 1에 도시하는 1개의 스탠다드 셀(51a) 내에 형성되는 기능 소자의 회로 구성의 일례를 도시하는 회로도.

도 3은 도 2에 도시하는 회로가 형성된 1개의 스탠다드 셀의 구성을 개략적으로 도시하는 평면도.

도 4는 도 3의 Ⅳ-Ⅳ선을 따라 취한 개략 단면도.

도 5는 본 발명의 실시 형태 2에서의 반도체 장치의 복수개의 스탠다드 셀이 나열된 모습을 개략적으로 도시하는 평면도.

도 6은 도 5의 Ⅵ-Ⅵ선을 따라 취한 개략 단면도.

도 7은 도 5의 구성에서 기능 소자가 형성되지 않은 스탠다드 셀에 퓨즈를 형성한 구성을 개략적으로 도시하는 평면도.

도 8은 도 5의 구성에서 기능 소자가 형성되지 않은 스탠다드 셀에서 전원선의 상층 배선과 하층 배선을 접속하지 않은 구성을 개략적으로 도시하는 평면도.

도 9는 본 발명의 실시 형태 3에서의 반도체 장치의 복수개의 스탠다드 셀이 나열된 모습을 개략적으로 도시하는 평면도.

도 10은 도 9의 X-X선을 따라 취한 개략 단면도.

도 11은 본 발명의 실시 형태 4에서의 반도체 장치의 회로 구성을 도시하는 회로도.

도 12는 도 11에 도시하는 회로도를 트랜지스터 레벨로 도시하는 회로도.

도 13은 도 11 및 도 12에 도시하는 회로를 구성하는 반도체 장치의 평면 레 이아웃 구성을 도시하는 개략 평면도로서, 반도체 기판에 형성된 확산 영역 및 소자 분리 영역과, 반도체 기판 위에 형성된 게이트 전극층 등의 다결정 실리콘층을 도시하는 도면.

도 14는 도 11 및 도 12에 도시하는 회로를 구성하는 반도체 장치의 평면 레이아웃 구성을 도시하는 개략 평면도로서, 다결정 실리콘층과 그 위의 제1층째의 금속층을 주로 도시하는 도면.

도 15는 도 11 및 도 12에 도시하는 회로를 구성하는 반도체 장치의 평면 레이아웃 구성을 도시하는 개략 평면도로서, 제1층째의 금속층과 그 위의 제2층째의 금속층과 제3층째의 금속층을 도시하는 도면.

도 16은 도 15에 도시하는 보강 배선 GNDS 및 보강 배선 VDDS의 배치의 모습을 도시하는 개략 평면도.

도 17은 본 발명의 실시 형태 5에서의 반도체 장치로서 SOC 칩의 구성을 개략적으로 도시하는 평면도.

도 18은 고집적 우선의 로직 영역 HIL에 형성된 고속 셀과 고성능 우선의 로직 영역 HRL에 형성된 고집적 셀과의 평면 레이아웃 구성을 도시하는 개략 평면도로서, 반도체 기판에 형성된 확산 영역 및 소자 분리 영역과, 반도체 기판 위에 형성된 게이트 전극층 등의 다결정 실리콘층을 도시하는 도면.

도 19는 고집적 우선의 로직 영역 HIL에 형성된 고속 셀과 고성능 우선의 로직 영역 HRL에 형성된 고집적 셀의 평면 레이아웃 구성을 도시하는 개략 평면도로서, 다결정 실리콘층과 그 위의 제1층째의 금속층을 주로 도시하는 도면.

도 20은 고집적 우선의 로직 영역 HIL에 형성된 고속 셀과 고성능 우선의 로직 영역 HRL에 형성된 고집적 셀의 평면 레이아웃 구성을 도시하는 개략 평면도로서, 제1층째의 금속층과 그 위의 제2층째의 금속층을 도시하는 도면.

도 21은 고집적 우선의 로직 영역 HIL에서의 복수의 스탠다드 셀이 고속 셀로 형성되고, 또한 고성능 우선의 로직 영역 HRL에서의 복수의 스탠다드 셀이 고집적 셀로 형성된 경우의 평면 레이아웃 구성을 도시하는 개략 평면도로서, 제1층째의 금속층을 도시하는 도면.

도 22는 고집적 우선의 로직 영역 HIL에서의 복수의 스탠다드 셀이 고속 셀로 형성되고, 또한 고성능 우선의 로직 영역 HRL에서의 복수의 스탠다드 셀이 고집적 셀로 형성된 경우의 평면 레이아웃 구성을 하층으로부터 순서대로 도시하는 개략 평면도로서, 제1층째의 금속층과, 그 위의 제2층째의 금속층을 도시하는 도면.

도 23은 고집적 우선의 로직 영역 HIL에서의 복수의 스탠다드 셀이 고속 셀로 형성되고, 또한 고성능 우선의 로직 영역 HRL에서의 복수의 스탠다드 셀이 고집적 셀로 형성된 경우의 평면 레이아웃 구성을 하층으로부터 순서대로 도시하는 개략 평면도로서, 제1층째 및 제2층째의 금속층과, 그 위의 제3층째의 금속층과, 또한 그 위의 제4 금속층을 도시하는 도면.

도 24는 발명의 실시 형태 6에서의 반도체 장치로서 고속 셀 및 고집적 셀의 쌍방을 갖는 장치의 구성을 개략적으로 도시하는 평면도.

<도면의 주요 부분에 대한 부호의 설명>

1 : p형 웰 영역

2 : n형 웰 영역

3 : 소자 분리 영역

11a, 21a : 드레인 영역

11b, 21b : 소스 영역

12, 22 : 게이트 절연층

13, 23 : 게이트 전극층

15 : p+ 영역

25 : n+ 영역

31A, 31B : 층간 절연층

31a : 컨택트홀

Claims (11)

- 배열된 복수개의 스탠다드 셀을 갖는 반도체 장치로서,상기 스탠다드 셀에 포함되는 기능 소자와,상기 기능 소자에 전기적으로 접속되고, 또한 하층 배선 및 상층 배선을 갖는 전원선을 구비하고,상기 하층 배선은 서로 인접하는 상기 스탠다드 셀의 경계를 따라서 상기 경 계 위로 연장되는 부분을 갖고,상기 상층 배선이 평면에서 보아 상기 하층 배선보다도 상기 스탠다드 셀의 내측에 위치하는 부분을 갖고,상기 기능 소자는 상기 상층 배선을 통해서 상기 하층 배선에 전기적으로 접속되어 있는 반도체 장치.

- 제1항에 있어서,상기 기능 소자에 전기적으로 접속된 신호선을 더 구비하고,상기 신호선은, 평면에서 보아, 상기 기능 소자 및 상기 상층 배선의 접속부와 상기 하층 배선의 상기 경계 위를 연장하는 부분 사이에 위치하도록 배치되어 있는 반도체 장치.

- 제1항에 있어서,상기 기능 소자가 배치되는 상기 스탠다드 셀 내에서 상기 상층 배선과 상기 하층 배선이 접속되어 있는 반도체 장치.

- 제1항에 있어서,상기 기능 소자를 포함하지 않는 상기 스탠다드 셀 내에서 상기 상층 배선과 상기 하층 배선이 접속되어 있는 반도체 장치.

- 제4항에 있어서,상기 기능 소자를 포함하지 않는 상기 스탠다드 셀 내에 배치되고, 또한 상기 하층 배선에 전기적으로 접속된 퓨즈를 더 구비한 반도체 장치.

- 제1항에 있어서,상기 상층 배선은 상기 스탠다드 셀의 경계를 따라서 상기 경계 위로 연장되는 부분을 갖고,상기 상층 배선의 상기 경계 위로 연장되는 부분의 선폭은, 상기 하층 배선의 상기 경계 위로 연장되는 부분의 선폭보다도 큰 반도체 장치.

- 배열된 복수개의 스탠다드 셀을 갖는 반도체 장치로서,상기 스탠다드 셀에 포함되는 기능 소자와,상기 기능 소자에 전기적으로 접속되고, 또한 하층 배선 및 상층 배선을 갖 는 제1 전원선을 구비하고,상기 하층 배선 및 상기 상층 배선의 각각은, 서로 전기적으로 접속되고, 또한 서로 인접하는 상기 스탠다드 셀의 경계를 따라서 상기 경계 위로 연장되는 부분을 갖고,상기 상층 배선이 평면에서 보아 상기 하층 배선보다도 굵은 선폭을 갖고 있는 반도체 장치.

- 제7항에 있어서,상기 하층 배선과 상기 상층 배선은 복수개의 제1 비아홀에 의해 전기적으로 접속되어 있고,상기 복수개의 제1 비아홀은, 상기 기능 소자를 구성하는 트랜지스터의 배치 피치와 동일 피치로 배치되어 있는 반도체 장치.

- 제7항에 있어서,상기 제1 전원선은, 상기 상층 배선보다도 위의 층에 형성된 보강 배선을 갖고,상기 보강 배선은 평면에서 보아 상기 상층 배선과 직교하는 방향으로 연장되어 있는 반도체 장치.

- 제9항에 있어서,상기 상층 배선과 상기 보강 배선 사이에 형성된 층간 절연층을 더 구비하고,상기 층간 절연층은, 평면에서 보아 상기 상층 배선과 상기 보강 배선이 교차하는 1개의 교차부에서, 상기 상층 배선과 상기 보강 배선을 전기적으로 접속하기 위한 복수개의 제2 비아홀을 갖고 있는 반도체 장치.

- 제7항에 있어서,상기 복수개의 스탠다드 셀은, 제1 스탠다드 셀과 제2 스탠다드 셀을 포함하고,상기 제1 스탠다드 셀은,상기 하층 배선 및 상기 상층 배선을 갖는 상기 제1 전원선과,상기 상층 배선과 동일한 층 위로 연장되고, 또한 평면에서 보아 상기 하층 배선 및 상기 상층 배선과 동일한 방향으로 연장되는 제1 신호선을 포함하고,상기 제2 스탠다드 셀은,상기 하층 배선과 동일한 층 위로 연장되는 배선층만으로 이루어지는 제2 전원선과,상기 상층 배선과 동일한 층 위로 연장되고, 또한 평면에서 보아 상기 배선층과 직교하는 방향으로 연장되는 제2 신호선을 포함하는 반도체 장치.

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JPJP-P-2007-00193580 | 2007-07-25 | ||

| JP2007193580 | 2007-07-25 | ||

| JP2008137063A JP5293939B2 (ja) | 2007-07-25 | 2008-05-26 | 半導体装置 |

| JPJP-P-2008-00137063 | 2008-05-26 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20090012136A true KR20090012136A (ko) | 2009-02-02 |

Family

ID=40477685

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020080072364A KR20090012136A (ko) | 2007-07-25 | 2008-07-24 | 반도체 장치 |

Country Status (4)

| Country | Link |

|---|---|

| JP (1) | JP5293939B2 (ko) |

| KR (1) | KR20090012136A (ko) |

| CN (1) | CN101388391B (ko) |

| TW (1) | TWI437665B (ko) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101429396B1 (ko) * | 2013-01-28 | 2014-08-11 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 표준 셀 디자인 레이아웃 |

| KR20150145181A (ko) * | 2014-06-18 | 2015-12-29 | 에이알엠 리미티드 | 집적회로 내부의 비아 배치 |

| KR20150145178A (ko) * | 2014-06-18 | 2015-12-29 | 에이알엠 리미티드 | 집적회로 내부의 전력망 도체 배치 |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5552775B2 (ja) | 2009-08-28 | 2014-07-16 | ソニー株式会社 | 半導体集積回路 |

| JP5685457B2 (ja) * | 2010-04-02 | 2015-03-18 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置 |

| WO2013018589A1 (ja) * | 2011-08-01 | 2013-02-07 | 国立大学法人電気通信大学 | 半導体集積回路装置 |

| CN103546146B (zh) * | 2013-09-24 | 2016-03-02 | 中国科学院微电子研究所 | 抗单粒子瞬态脉冲cmos电路 |

| JP5776802B2 (ja) * | 2014-02-14 | 2015-09-09 | ソニー株式会社 | 半導体集積回路 |

| US11120190B2 (en) * | 2017-11-21 | 2021-09-14 | Advanced Micro Devices, Inc. | Metal zero power ground stub route to reduce cell area and improve cell placement at the chip level |

| WO2020044438A1 (ja) | 2018-08-28 | 2020-03-05 | 株式会社ソシオネクスト | 半導体集積回路装置 |

| WO2020066797A1 (ja) * | 2018-09-28 | 2020-04-02 | 株式会社ソシオネクスト | 半導体集積回路装置および半導体パッケージ構造 |

| JPWO2021192265A1 (ko) * | 2020-03-27 | 2021-09-30 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5923060A (en) * | 1996-09-27 | 1999-07-13 | In-Chip Systems, Inc. | Reduced area gate array cell design based on shifted placement of alternate rows of cells |

| JP3672788B2 (ja) * | 2000-02-24 | 2005-07-20 | 松下電器産業株式会社 | 半導体装置のセルレイアウト構造およびレイアウト設計方法 |

| JP3718687B2 (ja) * | 2002-07-09 | 2005-11-24 | 独立行政法人 宇宙航空研究開発機構 | インバータ、半導体論理回路、スタティックランダムアクセスメモリ、及びデータラッチ回路 |

| JP4820542B2 (ja) * | 2004-09-30 | 2011-11-24 | パナソニック株式会社 | 半導体集積回路 |

-

2008

- 2008-05-26 JP JP2008137063A patent/JP5293939B2/ja not_active Expired - Fee Related

- 2008-07-14 TW TW097126596A patent/TWI437665B/zh not_active IP Right Cessation

- 2008-07-24 KR KR1020080072364A patent/KR20090012136A/ko not_active Application Discontinuation

- 2008-07-25 CN CN2008101769097A patent/CN101388391B/zh active Active

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101429396B1 (ko) * | 2013-01-28 | 2014-08-11 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 표준 셀 디자인 레이아웃 |

| US8813016B1 (en) | 2013-01-28 | 2014-08-19 | Taiwan Semiconductor Manufacturing Company Limited | Multiple via connections using connectivity rings |

| US9213795B2 (en) | 2013-01-28 | 2015-12-15 | Taiwan Semiconductor Manufacturing Company Limited | Multiple via connections using connectivity rings |

| KR20150145181A (ko) * | 2014-06-18 | 2015-12-29 | 에이알엠 리미티드 | 집적회로 내부의 비아 배치 |

| KR20150145178A (ko) * | 2014-06-18 | 2015-12-29 | 에이알엠 리미티드 | 집적회로 내부의 전력망 도체 배치 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101388391B (zh) | 2012-07-11 |

| JP5293939B2 (ja) | 2013-09-18 |

| TW200915488A (en) | 2009-04-01 |

| CN101388391A (zh) | 2009-03-18 |

| JP2009049370A (ja) | 2009-03-05 |

| TWI437665B (zh) | 2014-05-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5293939B2 (ja) | 半導体装置 | |

| US8063415B2 (en) | Semiconductor device | |

| USRE49821E1 (en) | Semiconductor integrated circuit | |

| US10163495B2 (en) | Two-port SRAM connection structure | |

| JP4781040B2 (ja) | 半導体集積回路装置 | |

| US11205645B2 (en) | Semiconductor device | |

| EP3375009B1 (en) | Power rail inbound middle of line (mol) routing | |

| TW201804347A (zh) | 標準胞元佈局及設置多個標準胞元的方法 | |

| US20220231054A1 (en) | Semiconductor device | |

| US9484424B2 (en) | Semiconductor device with a NAND circuit having four transistors | |

| KR20210099994A (ko) | 라우팅 와이어를 포함하는 적층 집적 회로 장치 | |

| US9768179B1 (en) | Connection structures for routing misaligned metal lines between TCAM cells and periphery circuits | |

| KR20160074434A (ko) | 스페어 회로 셀들을 구비한 집적회로 | |

| US9627496B2 (en) | Semiconductor with a two-input NOR circuit | |

| US8178904B2 (en) | Gate array | |

| KR100229859B1 (ko) | 반도체 장치 | |

| KR20180015399A (ko) | 반도체 장치 및 이의 제조 방법 | |

| JP2017069513A (ja) | 半導体装置およびその製造方法 | |

| US6979870B2 (en) | Semiconductor integrated circuit including CMOS logic gate | |

| CN110634860B (zh) | 半导体装置 | |

| KR102650199B1 (ko) | 반도체 소자 | |

| JP2023110556A (ja) | 半導体集積回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| N231 | Notification of change of applicant | ||

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |