KR20080006316A - 유기 박막 트랜지스터와 그의 제조 방법 - Google Patents

유기 박막 트랜지스터와 그의 제조 방법 Download PDFInfo

- Publication number

- KR20080006316A KR20080006316A KR1020060065343A KR20060065343A KR20080006316A KR 20080006316 A KR20080006316 A KR 20080006316A KR 1020060065343 A KR1020060065343 A KR 1020060065343A KR 20060065343 A KR20060065343 A KR 20060065343A KR 20080006316 A KR20080006316 A KR 20080006316A

- Authority

- KR

- South Korea

- Prior art keywords

- gate

- thin film

- film transistor

- electrode

- conductive layer

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/125—Active-matrix OLED [AMOLED] displays including organic TFTs [OTFT]

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having a potential-jump barrier or a surface barrier

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/466—Lateral bottom-gate IGFETs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having a potential-jump barrier or a surface barrier

- H10K10/80—Constructional details

- H10K10/82—Electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

Abstract

본 발명은 박막 트랜지스터의 턴/온 동작을 제어하기 용이해지는 유기 박막트랜지스터 기판 및 그 제조방법을 제공하는 것이다.

본 발명에 따른 유기 박막 트랜지스터 기판은 하부 기판 상에 형성되는 게이트 라인과; 상기 게이트 라인과 교차되어 서브 화소 영역을 정의하는 데이터 라인과; 상기 게이트 라인 및 데이터 라인과 교차되어 접속된 유기 박막 트랜지스터와: 상기 서브 화소 영역에 형성되며 상기 유기 박막트랜지스터와 접속되는 화소 전극과; 상기 게이트 라인 및 데이터 라인 사이에 형성됨과 아울러, 상기 유기 박막 트랜지스터의 게이트 전극 및 상기 유기 반도체층 사이에 무기 절연막으로 형성되는 게이트 절연막을 구비하 것을 특징으로 한다.

유기 박막 트랜지스터 기판, 게이트 절연막

Description

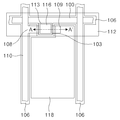

도 1 및 도 2는 본 발명에 따른 유기 박막 트랜지스터 기판의 평면도 및 단면도이다.

도 3a 및 도 3b는 종래 유기 절연막과 본 발명에 따른 무기 절연막으로 게이트 절연막을 사용한 유기 박막 트랜지스터를 비교하기 위한 그래프이다.

도 4 및 도 5는 본 발명에 따른 유기 박막 트랜지스터 기판 제조 방법 중 게이트 금속 패턴의 제조 방법을 설명하기 위한 평면도 및 단면도를 도시한 것이다.

도 6 및 도 7은 본 발명에 따른 유기 박막 트랜지스터 기판의 제조 방법 중 게이트 절연막의 제조 방법을 설명하기 위한 단면도이다.

도 10a 내지 도 10g는 도 8 및 도 9에 도시된 본 발명에 따른 유기 박막 트랜지스터 기판의 제조 방법 중 소스 및 드레인 금속 패턴, 화소 전극의 제조 방법을 설명하기 위한 단면도이다.

도 13a 내지 도 13d는 도 11 및 도 12에 도시된 본 발명에 따른 박막 트랜지스터 기판 제조 방법 중 뱅크 절연막, 유기 반도체층, 보호층의 제조 방법을 설명하기 위한 단면도이다.

<도면의 주요 부분에 대한 부호의 설명>

101 : 기판 103 : 게이트 전극

106 : 게이트 절연막 108,109 : 소스 및 드레인 전극

110 : 데이터 라인 112 : 뱅크 절연막

114 : 유기 반도체층 116 : 유기 보호층

118 : 화소 전극 140,150 : 마스크

본 발명은 유기 박막 트랜지스터 기판과 그 제조 방법에 관한 것으로, 박막 트랜지스터의 턴/온 동작을 제어하기 용이해지는 유기 박막트랜지스터 기판 및 그 제조방법에 관한 것이다.

액정 표시 장치는 전계를 이용하여 유전 이방성을 갖는 액정의 광투과율을 조절함으로써 화상을 표시하게 된다. 이를 위하여, 액정 표시 장치는 액정셀 매트릭스를 통해 화상을 표시하는 액정 표시 패널(이하, 액정 패널)과, 그 액정 패널을 구동하는 구동 회로를 구비한다.

통상, 액정 표시 장치(Liquid Crystal Display; LCD)는 액정 패널에 매트릭스 형태로 배열된 액정셀들 각각이 비디오 신호에 따라 광투과율을 조절하게 함으로써 화상을 표시하게 된다.

액정셀들 각각에는 비디오 신호를 독립적으로 공급하기 위한 스위치 소자로 박막 트랜지스터(Thin Film Transistor; TFT)가 이용된다. 이러한 박막트랜지스터의 액티브층으로는 아몰퍼스-실리콘(Amorphous-Si) 또는 폴리-실리콘(Poly-Si)이 이용된다.

그러나, 아몰퍼스-실리콘 또는 폴리-실리콘 액티브층은 박막 증착(코팅) 공정, 포토리소그래피 공정 및 식각 공정을 통해 패터닝되어 형성됨으로써 공정이 복잡함과 아울러 제조비용이 상승하는 문제점이 있다.

따라서, 최근에는 프린팅 공정을 통해 형성가능한 유기 반도체층을 액티브층으로 이용한 유기 박막 트랜지스터에 대한 연구가 활발히 진행되고 있다. 이러한 유기 박막 트랜지스터의 게이트 절연막을 유기 절연막으로 사용한 박막 트랜지스터 가 오프 동작을 할 경우 누설 전류가 흐르게 된다.

따라서, 본 발명이 이루고자 하는 기술적 과제는 박막 트랜지스터의 턴/온 동작을 제어하기 용이해지는 유기 박막트랜지스터 기판 및 그 제조방법을 제공하는 것이다.

상기 기술적 과제를 달성하기 위하여, 본 발명의 유기 박막 트랜지스터 기판은 하부 기판 상에 형성되는 게이트 라인과; 상기 게이트 라인과 교차되어 서브 화 소 영역을 정의하는 데이터 라인과; 상기 게이트 라인 및 데이터 라인과 교차되어 접속된 유기 박막 트랜지스터와; 상기 서브 화소 영역에 형성되며 상기 유기 박막트랜지스터와 접속되는 화소 전극과; 상기 게이트 라인 및 데이터 라인 사이에 형성됨과 아울러, 상기 유기 박막 트랜지스터의 게이트 전극 및 상기 유기 반도체층 사이에 무기 절연막으로 형성되는 게이트 절연막을 구비하 것을 특징으로 한다.

여기서, 상기 게이트 절연막은 산화 실리콘(SiNx)으로 형성되는 것을 특징으로 한다.

또한, 상기 게이트 전극은 제1 도전층과 제2 도전층으로 적층된 복층 구조로 형성되며, 상기 화소 전극은 상기 제1 도전층과 동일 평면 상에 동일 재질로 형성되는 것을 특징으로 한다.

상기 기술적 과제를 달성하기 위하여, 본 발명의 유기 박막 트랜지스터 기판의 제조 방법은 기판 상에 게이트 전극 및 게이트 라인을 형성하는 단계와; 상기 게이트 전극 및 게이트 라인 상에 무기 절연막으로 게이트 절연막을 형성하는 단계와; 상기 게이트 절연막 상에 데이터 라인과, 상기 데이터 라인이 연장되어 형성된 소스 전극과 드레인 전극을 형성하는 단계와; 상기 소스 전극 및 드레인 전극 사이에 유기 반도체층을 형성하는 단계를 포함하는 것을 특징으로 한다.

여기서, 상기 게이트 절연막으로 산화 실리콘(SiNx)을 이용하는 것을 특징으로 한다.

한편, 본 발명에 따른 유기 박막 트랜지스터 기판의 제조 방법은 상기 유기 반도체층을 형성하기 전에 내부에 상기 유기 반도체층이 충진되는 홀을 마련한 뱅 크 절연막을 형성하는 단계와; 상기 유기 반도체층이 형성된 홀 내에 유기 보호막을 형성하는 단계를 추가로 포함하는 것을 특징으로 한다.

그리고 상기 드레인 전극과 접속되는 화소 전극을 형성하는 단계를 추가로 포함하며, 상기 게이트 전극은 제1 도전층과 제2 도전층으로 적층된 복층 구조로 형성되며, 상기 화소 전극은 상기 제1 도전층과 동일 평면 상에 동일 재질로 형성되는 것을 특징으로 한다.

상기 기술적 과제 외에 본 발명의 기술적 과제 및 특징들은 첨부한 도면들을 참조한 실시 예에 대한 설명을 통하여 명백하게 드러나게 될 것이다. 이하, 첨부한 도면들을 참조하여 바람직한 실시 예에 대하여 설명한다.

도 1 및 도 2는 본 발명에 따른 유기 박막 트랜지스터 기판의 평면도 및 단면도이다.

유기 박막 트랜지스터 기판은 하부 기판(102) 위에 게이트 절연막(106)을 사이에 두고 교차하게 형성된 게이트 라인 및 데이터 라인(110)과, 그 교차 구조와 접속된 유기 박막 트랜지스터(130)와, 그 교차 구조로 마련된 서브 화소 영역에 형성되어 유기 박막 트랜지스터(130)와 접속된 화소 전극(118)을 구비한다.

게이트 라인(100)은 게이트 드라이버(미도시)로부터의 스캔 신호를, 데이터 라인(110)은 데이터 드라이버(미도시)로부터의 화소 신호를 공급한다. 게이트 라인(100)과 게이트 전극(103)은 하부 기판(101) 위에 제1 도전층(102)과 제2 도전층(104)이 적층된 복층 구조를 갖는다. 예를 들면, 게이트 라인(100)과 게이트 전극(103)의 제1 도전층(102)은 투명 도전층을 이용하고, 제2 도전층(104)은 불투명한 금속층으로 형성된다. 제1 도전층(102)으로는 ITO, TO, IZO, ITZO 등이, 제2 도전층(104)으로는 Cu, Mo, Al, Cu 합금, Mo 합금, Al 합금 등이 이용된다.

이러한 게이트 라인(100) 및 데이터 라인(110)은 게이트 절연막(106)을 사이에 두고 교차하여 각 서브 화소 영역을 정의한다. 여기서, 게이트 절연막(106)은 화소 전극(118)을 제외하고 형성된다. 게이트 라인(100)과 연결된 게이트 패드 상의 게이트 절연막(106)은 포토리소그래피공정과 식각 공정에 의해 패터닝됨으로써 게이트 패드가 노출된다.

데이터 라인(110)은 게이트 절연막(106) 위에 투명 도전층을 포함한 적어도 이중 이상의 복층 구조로 형성된다. 예를 들면, 데이터 라인(110)은 투명 도전층을 이용한 제3 도전층(105)과, 불투명한 금속을 이용한 제4 도전층(107)이 적층된 복층 구조로 형성된다. 제3 도전층(105)으로는 ITO, TO, IZO, ITZO 등이, 제4 도전층(107)으로는 Cu, Mo, Al, Cu 합금, Mo 합금, Al 합금 등이 이용된다.

게이트 절연막(106)은 유기 박막 트랜지스터(130)가 턴-온 및 턴-오프 동작되었을때 유기 박막 트랜지스터(130)의 온-전류(Ion) 및 오프-전류(Ioff)의 특성을 좋게하기 위하여 무기 절연막, 예를 들어 SiNx(산화 실리콘)을 이용하여 형성된다.

게이트 절연막(106)은 게이트 전극(103)과 소스 및 드레인 전극(108,109) 사이에 형성되어 이들을 절연시킨다. 또한, 게이트 라인(100) 및 데이터 라인(110)은 게이트 절연막(106)을 사이에 두고 교차하여 각 서브 화소 영역을 정의시킨다.

유기 박막 트랜지스터(130)는 게이트 라인(100)에 공급되는 스캔 신호에 응답하여 데이터 라인(110)에 공급되는 화소 신호가 반사 전극(118)에 충전되어 유지 되게 한다. 이를 위하여, 유기 박막 트랜지스터(130)는 게이트 라인(100)과 접속된 게이트 전극(103), 데이터 라인(110)과 접속된 소스 전극(108), 소스 전극(108)과 마주하며 화소 전극(118)과 접속된 드레인 전극(109), 게이트 절연막(106)을 사이에 두고 게이트 전극(106)과 중첩되어 소스 전극(108)과 드레인 전극(110) 사이에 채널을 형성하는 유기 반도체층(114)을 구비한다.

여기서, 게이트 전극(103)은 게이트 절연막(106)을 사이에 두고 유기 반도체층(116)과 중첩된다. 소스 및 드레인 전극(108,109)은 데이터 라인(110)을 이루는 제1 도전층(105)인 ITO, TO, IZO, ITZO 등으로 형성된다. 유기 반도체층(114)은 게이트 전극(106)과 중첩되는 영역에서 소스 및 드레인 전극(108,110)과 뱅크 절연막(112)에 의해 마련된 홀(113) 내에 형성된다. 이러한 유기 반도체층(114)은 펜타센(pentacene), 테트라센(tetracene), 안트라센(anthracene), 나프탈렌(naphthalene), α-6T, α-4T, 페릴렌(perylene) 및 그 유도체, 루브렌(rubrene) 및 그 유도체, 코로넨(coronene) 및 그 유도체, 페릴렌 테트라카르복실릭 디이미드(perylene tetracarboxylic diimide) 및 그 유도체, 페릴렌 테트라카르복실 디안하이드라이드(perylenetetracarboxylic dianhydride) 및 그 유도체, 프탈로시아닌(phthalocyanine) 및 그 유도체, 나프탈렌 테트라카르복실릭 디이미드(naphthalene tetracarboxylic diimide) 및 그 유도체, 나프탈렌 테트라카르복실릭 디안하이드라이드(naphthalene tetracarboxylic dianhydride) 및 그 유도체, 치환된 또는 비치환된 티오펜(thiophene)을 포함하는 공액계 고분자 유도체, 치환된 플루오렌(fluorene)을 포함하는 공액계 고분자 유도체 등과 같은 유기 반도체 물질로 이루 어진다.

이 유기 반도체층(114)은 자가 분자 조립체(Self Assembled Monolayer : SAM)처리 공정을 통해 소스 및 드레인 전극(108,109) 각각과 오믹 접촉된다. 구체적으로, SAM처리 공정을 통해 소스 및 드레인 전극(108,109) 각각과 유기 반도체층(114) 간의 일함수 차이가 줄어든다. 이에 따라, 소스 및 드레인 전극(108,109)에서 유기 반도체층(114)으로의 홀주입이 용이해짐과 아울러 소스 및 드레인 전극(108,109) 각각과 유기 반도체층(114) 간의 접촉 저항이 줄어든다.

이러한 유기 박막 트랜지스터(130)는 유기 보호막(116)에 의해 보호된다. 유기 보호막(116)은 뱅크 절연막(112)에 의해 마련된 홀(113) 내에 형성된다.

뱅크 절연막(112)은 홀(113)을 마련하도록 형성된다. 뱅크 절연막(112)에 의해 마련된 홀(113)은 소스 및 드레인 전극(108,109)을 노출시킨다. 뱅크 절연막(112)에 의해 노출된 소스 및 드레인 전극(108,109)의 일부는 유기 반도체층(116)과 중첩된다.

화소 전극(118)은 하부 기판(101) 위에 게이트 전극(103)과 동일하게 제 ㄷ도전층(102)과 제2 도전층(104)으로 형성된다. 여기서, 화소 전극(118)은 연장된 드레인 전극(109)과 접속된다. 제2 도전층(104)은 서브 화소 영역에서 드레인 전극(109) 하부에 형성되고, 제1 도전층(102)은 드레인 전극(109) 하부뿐만 아니라 서브 화소 전 영역에 형성된다.

여기서 드레인 전극(109)의 제3 도전층(105)으로 사용된 투명 도전층과 화소 전극(118)의 제1 도전층(102)으로 사용된 투명 도전층(102) 사이의 전도성을 높이 기 위해 화소 전극(118)의 제2 도전층(104)은 불투명한 금속층으로 형성된다.

이러한 화소 전극(118)은 유기 박막 트랜지스터(130)를 통해 비디오 신호가 공급되면, 공통 전압이 공급된 공통 전극과 전계를 형성하여 유기 박막 트랜지스터 기판과 칼라 필터 기판 사이에 배열된 액정 분자들이 유전율 이방성에 의해 회전하게 된다. 그리고, 액정 분자들의 회전 정도에 따라 화소 영역을 투과하는 광 투과율이 달라지게 됨으로써 계조를 구현하게 된다.

도 3a 및 도 3b는 종래 유기 절연막과 본 발명에 따른 무기 절연막으로 게이트 절연막을 사용한 유기 박막 트랜지스터를 비교하기 위한 그래프이다.

게이트 절연막(106)을 유기 절연막으로 사용하게 될 경우 유기 박막 트랜지스터(130) 턴-오프 동작에서 높게 나타날 수 있는 오프 전류(Ioff)를 무기 게이트 절연막 사용할 시 오프 전류(Ioff)가 상대적으로 낮게 나타난다. 구체적으로 유기 절연막으로 형성된 게이트 절연막(106)의 유기 박막 트랜지스터(130) 턴-온 및 턴-오프 동작에서 온-전류(Ion) 및 오프-전류(Ioff) 측정이 불가능하다. 도 3a 및 도3b에 도시된 그래프는 박막 트랜지스터(130)의 게이트 온/오프 전압(Von,Voff)을 인가하여 온/오프 전류(Ion/Ioff)를 나타낸 유기 박막 트랜지스터(130) 동작에 대한 유기 박막 트랜지스터(130)의 전압-전류 (V-I)특성곡선을 나타내는 그래프이다. 여기서, 유기 박막 트랜지스터(130)의 전압-전류(V-I) 특성곡선은 X축 방향으로 박막 트랜지스터(130)의 게이트 온/오프 전압(Von,Voff)을 나타내고, 그 전압에 따른 유기 박막 트랜지스터(130)의 온/오프 전류(Ion/Ioff)는 Y축 방향으로 나타낸다. 도 3a를 참조하면, 게이트 절연막(106)으로 유기 절연막을 사용한 유기 박막 트랜 지스터(130)는 게이트 온/오프 전압(Von,Voff)을 인가하여도 온/오프 전류(Ion/Ioff)를 측정 불가능할 정도로 일정하게 드레인 전류(Id)가 흐르고 있다. 이에 따라, 게이트 오프 전압일 경우에도 박막 트랜지스터(130)가 턴-오프되지 않고 오프 전류(Ioff)인 누설 전류가 많이 흐르게 된다. 반면에 게이트 절연막(106)으로 무기 절연막을 사용한 본 발명에 유기 박막 트랜지스터(130)에 게이트 온/오프 전압(Von,Voff)을 인가하면 유기 박막 트랜지스터(130)의 드레인 전극(109)에 흐르는 온/오프 전류(Ion/Ioff)를 정확히 구분할 수 있다. 여기서 무기 절연막은 예를 들어 SiNx(산화 실리콘)으로 이용한다. 도 3b에 도시된 바와 같이 게이트 절연막(106)으로 무기 절연막을 사용한 유기 박막 트랜지스터(130)의 전압-전류(V-I) 특성곡선을 나타내는 그래프이다. 무기 절연막을 게이트 절연막(106)으로 사용한 유기 박막 트랜지스터(130)는 게이트 온 전압(Von)을 인가하면 유기 박막 트랜지스터(130)가 턴-온되어 일정한 드레인 전류(Id)가 흐른다. 또한, 게이트 오프 전압(Voff)을 인가하면 유기 박막 트랜지스터(130)는 턴-오프되어 드레인 전류(Id)가 거의 흐르지 않는다. 게이트 온 전압(Von)에 의해 턴-온된 유기 박막 트랜지스터(130)의 드레인 전극(109)에는 상대적으로 높은 드레인 전류(Id)가 흐르고 있다가 게이트 오프 전압(Voff)을 인가하자 드레인 전류(Id)가 급격히 거의 흐르지 않는다. 다시 말하여, 게이트 오프 전압(Voff)을 인가할 경우 유기 박막 트랜지스터(130)가 턴-오프되어 오프 전류(Ioff)인 누설 전류가 많이 흐르는 것을 방지할 수 있다. 이에 따라, 유기 박막 트랜지스터(130)를 상대적으로 낮은 게이트 오프 전압(Voff)에서 오프시킬 수 있으므로 소비 전력을 감소시킬 수 있다. 한편, 무기 절연막을 사용한 유기 박막 트랜지스터(130)의 게이트 온 전압(Von)을 공급할 경우 온 된 유기 박막 트랜지스터(130)의 온-전류(Ion)가 흐르고, 게이트 오프 전압(Voff)을 공급할 경우 오프된 유기 박막 트랜지스터(130)의 오프 전류(Ioff)가 거의 흐르지 않게 된다. 이에 따라, 유기 박막 트랜지스터(130)의 턴-온 및 턴-오프 동작을 정확히 스위칭할 수 있게 된다.

도 4 및 도 5는 본 발명에 따른 유기 박막 트랜지스터 기판 제조 방법 중 게이트 금속 패턴의 제조 방법을 설명하기 위한 평면도 및 단면도를 도시한 것이다.

도 4 및 도 5에 도시된 바와 같이 제1 마스크 공정으로 하부 기판(102) 상에 제1 도전층(102)과 제2 도전층(104)이 적층된 게이트 라인(100) 및 게이트 전극(104)과 화소 전극(118)을 포함하는 게이트 금속 패턴이 형성된다.

구체적으로, 하부 기판(102) 상에 스퍼터링 방법 등의 증착 방법을 통해 제1 도전층(102)과 제2 도전층(104)이 차례로 적층된다. 제1 도전층(102)과 제2 도전층(104)을 적층한 후 그 제1 도전층(102)과 제2 도전층(104)이 포토리소그래피공정과 식각 공정에 의해 패터닝됨으로써 게이트 라인(100) 및 게이트 전극(104)과 화소 전극(118)을 포함하는 제1 마스크 패턴이 형성된다. 여기서, 제1 도전층(102)은 아모퍼스 인듐 틴 옥사이드(Amorpho Indium-Tin Oxide; 이하 a-ITO)을 이용하고, 제2 도전층(104)으로는 알루미늄(AL), 몰리브덴(MO), 크롬(Cr), 구리(Cu) 등 이들의 복수층 구조로 형성된다.

도 6 및 도 7은 본 발명에 따른 유기 박막 트랜지스터 기판의 제조 방법 중 게이트 절연막의 제조 방법을 설명하기 위한 단면도이다.

도 6에 도시된 바와 같이 게이트 금속 패턴이 형성된 하부 기판(101) 상에 게이트 절연막(106)이 형성된다. 구체적으로, 게이트 금속 패턴이 형성된 하부 기판 상(101)에 무기 절연 물질이 전면 증착됨으로써 게이트 절연막(106)이 형성된다. 게이트 절연막(106)으로는 PECVD(Plasma Enhanced Chemical Vapor Deposion)등의 증착 방법을 통해 예를 들어 산화 실리콘(SiNx) 등과 같은 무기 절연 물질이 이용된다. 여기서, 게이트 라인(100)과 연결된 게이트 패드 상의 게이트 절연막(106)은 포토리소그래피공정과 식각 공정에 의해 패터닝됨으로써 게이트 패드를 노출시키고, 화소 전극(118)이 형성될 영역의 하부 기판도 노출시킨다.

도 10a 내지 도 10g는 도 8 및 도 9에 도시된 본 발명에 따른 유기 박막 트랜지스터 기판의 제조 방법 중 소스 및 드레인 금속 패턴의 제조 방법을 설명하기 위한 단면도이다.

도 10a에 도시된 바와 같이 게이트 절연막(106) 상에 스퍼터링등의 증착 방법으로 제3 도전층(105), 제4 도전층(107)으로 적층된다. 제3 도전층(105)으로는 ITO, TO, IZO, ITZO 등이, 제4 도전층(107)으로는 Cu, Mo, Al, Cu 합금, Mo 합금, Al 합금 등이 이용된다.

이어서, 제4 도전층(107) 위에 포토레지스트가 도포된 다음, 반투과 마스크 또는 슬릿 마스크(140)를 이용한 포토리소그래피 공정으로 포토레지스트가 노광 및 현상됨으로써 도 10b에 도시된 바와 같이 서로 다른 두께를 갖는 제1 및 제2 포토레지스트 패턴(212a,212b)이 형성된다.

구체적으로, 슬릿 마스크(140)는 석영 기판(142) 상에 차단층(144)이 형성된 차단 영역(S11)과, 석영 기판(152) 상에 다수개의 슬릿들(146)이 형성된 슬릿 영역(S12)과, 석영 기판(142)만 존재하는 투과 영역(S13)을 구비한다. 차단 영역(S11)은 데이터 라인(110)이 형성되어질 영역에 위치하여 노광 공정시 자외선을 차단함으로써 현상 공정 후 도 4b에 도시된 바와 같이 제2 포토레지스트 패턴(212b)이 남게 된다. 슬릿 영역(S12)은 소스 및 드레인 전극(108,109)이 형성될 영역에 위치하여 노광 공정시 자외선을 회절시킴으로써 현상 공정 후 도 4b에 도시된 바와 같이 제2 포토레지스트 패턴(212b)보다 두께가 얇은 제1 포토레지스트 패턴(212a)이 남게 된다. 그리고, 투과영역(S13)은 자외선을 모두 투과시킴으로써 현상 후 도 4b에 도시된 바와 같이 포토레지스트가 제거된다.

제1 및 제2 포토레지스트 패턴을 마스크로 이용한 제1 식각 공정으로 제2 도전층(107)이 도 10c에 도시된 바와 같이 패터닝됨으로써 제3 도전층(105)이 노출된다. 이어서, 도 10d에 도시된 바와 같이 산소(O2) 플라즈마를 이용한 애싱 공정으로 제1 포토레지스트 패턴(212a)의 두께는 얇아지게 되고, 제2 포토레지스트 패턴(212b)은 제거된다. 그리고, 도 10e에 도시된 바와 같이 애싱된 제1 포토레지스트 패턴(212a)을 마스크로 이용한 제2 식각 공정으로 노출된 제3 도전층(105)이 제거된다. 제3 및 제4 도전층(107,107)으로 이루어진 데이터 라인(110), 소스 및 드레인 전극과(108,109)이 형성한다.

도 10f에 도시된 바와 같이 제1 포토레지스트 패턴(212a)을 마스크로 이용한 제3 식각 공정으로 노출된 제4 도전층(107)과 제2 도전층(104) 제거된다. 다시 말 하여 화소 전극(118)의 제2 도전층(104)은 드레인 전극(109)과 연결된 일부를 제외하고 제거된다. 제4 도전층(107)이 제거된 곳에 소스 및 드레인 전극(108,109)이 서로 마주보며 형성된다. 이후, 도 9에 도시된 바와 같이 데이터 라인(107) 상에 형성된 제1 포토레지스트 패턴(212a)이 스트립 공정으로 제거된다.

도 13a 내지 도 13d는 도 11 및 도 12에 도시된 본 발명에 따른 박막 트랜지스터 기판 제조 방법 중 뱅크 절연막, 유기 반도체층, 보호층의 제조 방법을 설명하기 위한 단면도이다.

도 13a에 도시된 바와 같이 소스 및 데이터 전극(108,109) 과 데이터 라인(110) 및 반사 전극(118)이 형성된 하부 기판(102) 상에 스핀리스 또는 스핀 코팅 등의 코팅 방법을 통해 감광성 유기 절연 물질(116)이 전면 도포된다. 이어서, 마스크(150)가 하부 기판(102) 상에 정렬된다. 마스크(150)는 석영 기판 상에 차단층(154)이 형성된 차단 영역(S21)과, 석영 기판(152)만 존재하는 투과 영역(S22)을 구비한다. 차단 영역(S21)은 노광 공정시 자외선을 차단함으로써 현상 공정 후 차단 영역(S21)과 대응되는 영역의 하부 기판(101) 상에는 도 13b에 도시된 바와 같이 뱅크 절연막(112)이 형성된다. 투과영역(S22)은 노광 공정시 자외선을 모두 투과시킴으로써 현상 공정 후 투과 영역(S22)과 대응되는 영역의 하부 기판(101) 상에는 홀(113)이 형성된다. 여기서, 홀(113)은 게이트 절연막(106)과 소스 및 드레인 전극(108,109)이 노출된다. 이후, 잉크젯 분사 장치(160)를 이용하여 소스 및 드레인 전극(108,110)과 뱅크 절연막(112)에 의해 마련된 홀(113) 내에 액체 상태의 유기 반도체(162)를 분사한다. 이후, 액체 상태의 유기 반도체(162)가 경화됨 으로써 도 13c에 도시된 바와 같이 고체 상태의 유기 반도체층(114)이 형성된다. 유기 반도체층(114)이 형성된 후 그 유기 반도체층(114)은 자가 분자 조립체(SAM) 처리된다. 이에 따라, 유기 반도체층(114)은 소스 및 드레인 전극(108,109) 각각과 오믹 접촉된다. 그런 다음, 뱅크 절연막(112)에 의해 마련된 홀(113) 내에 폴리 비닐 알콜(Poly Vinyl Alcohol : PVA) 등과 같은 유기 절연액이 잉크젯 분사 장치를 통해 분사된 후 경화된다. 이에 따라, 뱅크 절연막(112)에 의해 마련된 홀(113) 내에 도 13d에 도시된 바와 같이 유기 보호막(116)이 형성된다.

상술한 바와 같이, 본 발명에 따른 유기 박막 트랜지스터 기판 및 그 제조 방법은 게이트 절연막으로 무기 절연막인 산화 실리콘을 사용한다. 이에 따라, 박막 트랜지스터 온 전압을 인가할 경우 오프 전류가 거의 흐르지 않게 된다. 또한, 무기 절연막으로 게이트 절연막을 형성할 경우 소스 및 드레인 전극과 게이트 절연막 사이의 들뜸 현상을 방지할 수 있다.

이상에서 설명한 본 발명의 상세한 설명에서는 본 발명의 바람직한 실시 예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자 또는 해당 기술 분야에 통상의 지식을 갖는 자라면, 후술된 특허청구범위에 기재된 본 발명의 사상 및 기술 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해 할 수 있을 것이다.

따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구 범위에 의해 정하여져야만 할 것이다.

Claims (7)

- 하부 기판 상에 형성되는 게이트 라인과;상기 게이트 라인과 교차되어 서브 화소 영역을 정의하는 데이터 라인과;상기 게이트 라인 및 데이터 라인과 교차되어 접속된 유기 박막 트랜지스터와;상기 서브 화소 영역에 형성되며 상기 유기 박막트랜지스터와 접속되는 화소 전극과;상기 게이트 라인 및 데이터 라인 사이에 형성됨과 아울러, 상기 유기 박막 트랜지스터의 게이트 전극 및 상기 유기 반도체층 사이에 무기 절연막으로 형성되는 게이트 절연막을 구비하 것을 특징으로 하는 유기 박막 트랜지스터 기판.

- 제1항에 있어서,상기 게이트 절연막은 산화 실리콘(SiNx)으로 형성되는 것을 특징으로 하는 유기 박막 트랜지스터 기판.

- 제1항에 있어서,상기 게이트 전극은 제1 도전층과 제2 도전층으로 적층된 복층 구조로 형성되며, 상기 화소 전극은 상기 제1 도전층과 동일 평면 상에 동일 재질로 형성되는 것을 특징으로 하는 유기 박막 트랜지스터 기판.

- 기판 상에 게이트 전극 및 게이트 라인을 형성하는 단계와;상기 게이트 전극 및 게이트 라인 상에 무기 절연막으로 게이트 절연막을 형성하는 단계와;상기 게이트 절연막 상에 데이터 라인과, 상기 데이터 라인이 연장되어 형성된 소스 전극과 드레인 전극을 형성하는 단계와;상기 소스 전극 및 드레인 전극 사이에 유기 반도체층을 형성하는 단계를 포함하는 것을 특징으로 하는 유기 박막트랜지스터 기판의 제조방법.

- 제4항에 있어서,상기 게이트 절연막으로 산화 실리콘(SiNx)을 이용하는 것을 특징으로 하는 유기 박막 트랜지스터 기판의 제조 방법.

- 제4항에 있어서,상기 유기 반도체층을 형성하기 전에 내부에 상기 유기 반도체층이 충진되는 홀을 마련한 뱅크 절연막을 형성하는 단계와;상기 유기 반도체층이 형성된 홀 내에 유기 보호막을 형성하는 단계를 추가로 포함하는 것을 특징으로 하는 유기 박막 트랜지스터 기판의 제조 방법.

- 제4항에 있어서,상기 드레인 전극과 접속되는 화소 전극을 형성하는 단계를 추가로 포함하며,상기 게이트 전극은 제1 도전층과 제2 도전층으로 적층된 복층 구조로 형성되며, 상기 화소 전극은 상기 제1 도전층과 동일 평면 상에 동일 재질로 형성되는 것을 특징으로 하는 유기 박막 트랜지스터 기판의 제조방법.

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060065343A KR20080006316A (ko) | 2006-07-12 | 2006-07-12 | 유기 박막 트랜지스터와 그의 제조 방법 |

| EP07013459A EP1879233A1 (en) | 2006-07-12 | 2007-07-10 | Organic thin film transistor substrate and fabrication thereof |

| JP2007182465A JP2008022008A (ja) | 2006-07-12 | 2007-07-11 | 有機薄膜トランジスタ基板とその製造方法 |

| TW096125450A TW200814386A (en) | 2006-07-12 | 2007-07-12 | Organic thin film transistor substrate and fabrication thereof |

| CNA2007101494189A CN101114667A (zh) | 2006-07-12 | 2007-07-12 | 有机薄膜晶体管基板及其制造方法 |

| US11/777,174 US7858971B2 (en) | 2006-07-12 | 2007-07-12 | Organic thin film transistor substrate and method of fabricating the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060065343A KR20080006316A (ko) | 2006-07-12 | 2006-07-12 | 유기 박막 트랜지스터와 그의 제조 방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20080006316A true KR20080006316A (ko) | 2008-01-16 |

Family

ID=38668787

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020060065343A KR20080006316A (ko) | 2006-07-12 | 2006-07-12 | 유기 박막 트랜지스터와 그의 제조 방법 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7858971B2 (ko) |

| EP (1) | EP1879233A1 (ko) |

| JP (1) | JP2008022008A (ko) |

| KR (1) | KR20080006316A (ko) |

| CN (1) | CN101114667A (ko) |

| TW (1) | TW200814386A (ko) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100923423B1 (ko) * | 2008-03-28 | 2009-10-27 | 전자부품연구원 | 유기 박막 트랜지스터 및 그의 제조 방법 |

| KR101427707B1 (ko) * | 2008-02-21 | 2014-08-11 | 삼성디스플레이 주식회사 | 유기 박막 트랜지스터 기판 및 그의 제조 방법 |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9041202B2 (en) | 2008-05-16 | 2015-05-26 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method of the same |

| JP2010080896A (ja) * | 2008-09-29 | 2010-04-08 | Toppan Printing Co Ltd | 電界効果型トランジスタ及びその製造方法並びに画像表示装置 |

| US8191936B2 (en) | 2008-11-12 | 2012-06-05 | Cole Kepro International, Llc | Gaming machine door latch |

| KR101895561B1 (ko) | 2009-11-13 | 2018-09-07 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| US9299941B2 (en) | 2011-01-13 | 2016-03-29 | Samsung Electronics Co., Ltd. | Organic semiconductor device and method of manufacturing the same |

| WO2013018137A1 (ja) | 2011-08-03 | 2013-02-07 | パナソニック株式会社 | 表示パネル装置及びその製造方法 |

| WO2013046547A1 (ja) | 2011-09-26 | 2013-04-04 | パナソニック株式会社 | 有機薄膜トランジスタ |

| US8766244B2 (en) * | 2012-07-27 | 2014-07-01 | Creator Technology B.V. | Pixel control structure, array, backplane, display, and method of manufacturing |

| US20160216584A1 (en) * | 2015-01-26 | 2016-07-28 | Samsung Display Co., Ltd. | Liquid crystal display and manufacturing method thereof |

| TWI647870B (zh) * | 2017-11-29 | 2019-01-11 | 友達光電股份有限公司 | 有機薄膜電晶體及畫素結構 |

| JP7168497B2 (ja) * | 2019-03-20 | 2022-11-09 | スタンレー電気株式会社 | 液晶表示素子 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5167569B2 (ja) * | 1999-06-21 | 2013-03-21 | ケンブリッジ・エンタープライズ・リミテッド | トランジスタの製造方法 |

| JP2002215065A (ja) * | 2000-11-02 | 2002-07-31 | Seiko Epson Corp | 有機エレクトロルミネッセンス装置及びその製造方法、並びに電子機器 |

| US6821811B2 (en) * | 2002-08-02 | 2004-11-23 | Semiconductor Energy Laboratory Co., Ltd. | Organic thin film transistor and method of manufacturing the same, and semiconductor device having the organic thin film transistor |

| KR100925460B1 (ko) | 2002-12-05 | 2009-11-06 | 삼성전자주식회사 | 유기 박막 트랜지스터 기판 및 그 제조 방법 |

| KR100973811B1 (ko) | 2003-08-28 | 2010-08-03 | 삼성전자주식회사 | 유기 반도체를 사용한 박막 트랜지스터 표시판 및 그 제조방법 |

| KR100583252B1 (ko) | 2003-12-29 | 2006-05-24 | 엘지.필립스 엘시디 주식회사 | 유기전계 발광소자와 그 제조방법 |

| KR100736008B1 (ko) * | 2004-06-07 | 2007-07-06 | 가시오게산키 가부시키가이샤 | 표시장치 및 그 제조방법 |

| JP4672319B2 (ja) | 2004-09-22 | 2011-04-20 | 株式会社東芝 | 有機半導体装置およびその製造方法 |

| KR101078360B1 (ko) * | 2004-11-12 | 2011-10-31 | 엘지디스플레이 주식회사 | 폴리형 액정 표시 패널 및 그 제조 방법 |

| KR100603836B1 (ko) * | 2004-11-30 | 2006-07-24 | 엘지.필립스 엘시디 주식회사 | 유기전계발광 소자 및 그의 제조방법 |

-

2006

- 2006-07-12 KR KR1020060065343A patent/KR20080006316A/ko not_active Application Discontinuation

-

2007

- 2007-07-10 EP EP07013459A patent/EP1879233A1/en not_active Withdrawn

- 2007-07-11 JP JP2007182465A patent/JP2008022008A/ja active Pending

- 2007-07-12 US US11/777,174 patent/US7858971B2/en not_active Expired - Fee Related

- 2007-07-12 TW TW096125450A patent/TW200814386A/zh unknown

- 2007-07-12 CN CNA2007101494189A patent/CN101114667A/zh active Pending

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101427707B1 (ko) * | 2008-02-21 | 2014-08-11 | 삼성디스플레이 주식회사 | 유기 박막 트랜지스터 기판 및 그의 제조 방법 |

| KR100923423B1 (ko) * | 2008-03-28 | 2009-10-27 | 전자부품연구원 | 유기 박막 트랜지스터 및 그의 제조 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW200814386A (en) | 2008-03-16 |

| US20080012024A1 (en) | 2008-01-17 |

| JP2008022008A (ja) | 2008-01-31 |

| EP1879233A1 (en) | 2008-01-16 |

| US7858971B2 (en) | 2010-12-28 |

| CN101114667A (zh) | 2008-01-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20080006316A (ko) | 유기 박막 트랜지스터와 그의 제조 방법 | |

| JP4988322B2 (ja) | 表示装置とその製造方法 | |

| US7045816B2 (en) | Liquid crystal display apparatus | |

| KR101328628B1 (ko) | 유기 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR101244898B1 (ko) | 유기 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR101198907B1 (ko) | 유기 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR20030082651A (ko) | 박막 트랜지스터 어레이 기판 및 그 제조 방법 | |

| KR101427707B1 (ko) | 유기 박막 트랜지스터 기판 및 그의 제조 방법 | |

| KR101265217B1 (ko) | 유기 박막트랜지스터 기판 및 그 제조방법 | |

| JP2008078655A (ja) | 薄膜トランジスタ表示板の製造方法 | |

| KR20080011826A (ko) | 유기 박막 트랜지스터 기판 및 이의 제조방법 | |

| US20090180044A1 (en) | Thin film transistor substrate, liquid crystal display having the same, and method of manufacturing the same | |

| KR20080041448A (ko) | 유기 박막 트랜지스터 기판의 제조 방법 | |

| KR101438038B1 (ko) | 유기 박막트랜지스터 및 그 제조방법 | |

| KR20090124546A (ko) | 유기 박막 트랜지스터 기판의 제조 방법 | |

| KR20080006315A (ko) | 전기 영동 장치 및 그의 제조 방법 | |

| KR101380225B1 (ko) | 액정표시장치용 어레이 기판 | |

| KR20080040158A (ko) | 유기 박막 트랜지스터 기판 및 이의 제조방법 | |

| KR20080056388A (ko) | 액정표시장치용 어레이 기판 및 그 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |