KR20070019458A - 배선 및 그 형성 방법과 박막 트랜지스터 기판 및 그 제조방법 - Google Patents

배선 및 그 형성 방법과 박막 트랜지스터 기판 및 그 제조방법 Download PDFInfo

- Publication number

- KR20070019458A KR20070019458A KR1020050074455A KR20050074455A KR20070019458A KR 20070019458 A KR20070019458 A KR 20070019458A KR 1020050074455 A KR1020050074455 A KR 1020050074455A KR 20050074455 A KR20050074455 A KR 20050074455A KR 20070019458 A KR20070019458 A KR 20070019458A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- reactive metal

- metal

- silicided

- silver

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

Abstract

접착성이 향상되고, 전도성이 우수한 배선, 그 형성 방법과 이를 이용하여 형성된 박막 트랜지스터 기판 및 그 제조 방법을 제공한다. 배선은 산화 반응성 금속 또는 실리사이드화 반응성 금속 및 은을 포함하는 접착층, 접착층 상에 형성된 은 도전층 및 은 도전층 상에 형성되고, 산화 반응성 금속을 포함하는 보호층을 포함한다.

박막 트랜지스터, 저저항 금속, 은(Ag), 실리사이드화, 산화

Description

도 1 내지 도 3은 본 발명의 실시예들에 따른 배선의 단면도들이다.

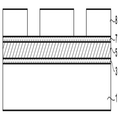

도 4 내지 도 6은 본 발명의 일 실시예에 따른 배선 형성 방법의 공정 단계별 단면도들이다.

도 7 내지 도 9는 본 발명의 다른 실시예에 따른 배선 형성 방법의 공정 단계별 단면도들이다.

도 10a는 본 발명의 다른 실시예에 따른 제조 방법에 의해 제조된 박막 트랜지스터 기판의 레이아웃도이다.

도 10b는 도 10a 및 도 10b의 B - B'선을 따라 절단한 단면도들이다.

도 11a, 도 13a 및 도 19a는 본 발명의 다른 실시예에 따른 박막 트랜지스터 기판의 제조 방법을 순차적으로 나타낸 레이아웃도들이다.

도 11b, 도 12는 도 11a의 B - B'선을 따라 절단한 공정 단계별 단면도들이다.

도 13b 내지 도 18은 도 13a의 B - B'선을 따라 절단한 공정 단계별 단면도들이다.

도 19b는 도 19a의 B - B'선을 따라 절단한 공정 단계별 단면도이다.

<도면의 주요부분에 대한 부호의 설명>

3, 3', 3": 접착층 5: 은 도전층

7: 보호층

본 발명은 배선, 그 형성 방법, 박막 트랜지스터 기판 및 그 제조 방법에 관한 것으로, 보다 상세하게는 접착성이 향상되고, 전도성이 우수한 배선, 그 형성 방법과 이를 이용하여 형성된 박막 트랜지스터 기판 및 그 제조 방법에 관한 것이다.

액정 표시 장치(Liquid Crystal Display; LCD)는 현재 가장 널리 사용되고 있는 평판 표시 장치(flat panel display) 중 하나로서, 전극이 형성되어 있는 두 장의 기판과 그 사이에 삽입되어 있는 액정층으로 이루어져, 전극에 전압을 인가하여 액정층의 액정 분자들을 재배열시킴으로써 투과되는 빛의 양을 조절하는 표시 장치이다.

액정 표시 장치 중에서도 현재 주로 사용되는 것은 전계 생성 전극이 두 개의 기판에 각각 구비되어 있는 형태이다. 이 중에서도, 하나의 기판에는 복수의 화소 전극이 매트릭스(matrix) 형태로 배열되어 있고 다른 기판에는 하나의 공통 전극이 기판 전면을 덮고 있다. 이러한 액정 표시 장치에서 화상의 표시는 각 화소 전극에 별도의 전압을 인가함으로써 이루어진다. 이를 위해서 화소 전극에 인가되는 전압을 스위칭하기 위한 삼단자소자인 박막 트랜지스터를 각 화소 전극에 연결하고 이 박막 트랜지스터를 제어하기 위한 신호를 전달하는 게이트선(gate line)을 포함하는 게이트 배선과 화소 전극에 인가될 전압을 전달하는 데이터선(data line)을 포함하는 데이터 배선을 기판 상에 형성한다.

한편, 액정 표시 장치의 표시 면적이 점점 대형화됨에 따라, 상기 박막 트랜지스터와 연결되는 게이트선 및 데이터선 또한 길어지고, 그에 따라 배선의 저항 또한 증가한다. 따라서, 이러한 저항 증가에 의한 신호 지연 등의 문제를 해결하기 위해서는, 상기 게이트선 및 데이터선을 최대한 낮은 비저항을 가지는 재료로 형성할 필요가 있다.

배선 재료 중 가장 낮은 비저항을 갖는 물질은 은(Ag)이다. 은(Ag)은 비저항이 약 1.59μΩ㎝인 것으로 알려져 있다. 따라서, 실제 공정에서 은(Ag)으로 이루어진 게이트 배선 및 데이터 배선을 사용함으로써, 신호 지연 등의 문제를 해결할 수 있다. 그러나, 은(Ag)은 유리 등의 기판 또는 진성 비정질 규소나 도핑된 비정질 규소 등으로 이루어진 반도체 기판 등의 하부 기판에 대해 접착성(adhesion)이 극히 불량하여 증착이 용이하지 않고, 배선의 들뜸(lifting) 또는 벗겨짐(peeling)이 쉽게 유발된다. 또한 은은 내열성 및 내화학성이 취약하여, 고온의 열에 의해 뭉침 현상이 발생하고 식각액 등에 의해 부식되기 쉽다.

본 발명이 이루고자 하는 기술적 과제는 접착성과 전도도가 우수한 배선 및 그 형성 방법을 제공하고자 하는 것이다.

본 발명이 이루고자 하는 다른 기술적 과제는 접착성과 전도도가 우수한 배선을 포함하는 박막 트랜지스터 기판 및 그 제조 방법을 제공하고자 하는 것이다.

본 발명의 기술적 과제들은 이상에서 언급한 기술적 과제들로 제한되지 않으며, 언급되지 않은 또 다른 기술적 과제들은 아래의 기재로부터 당업자에게 명확하게 이해될 수 있을 것이다.

상기 기술적 과제를 달성하기 위한 본 발명의 일 실시예에 따른 배선은 산화 반응성 금속 또는 실리사이드화 반응성 금속 및 은을 포함하는 접착층, 상기 접착층 상에 형성된 은 도전층 및 상기 은 도전층 상에 형성되고 상기 산화 반응성 금속 및 상기 은을 포함하는 보호층을 포함한다.

상기 다른 기술적 과제를 달성하기 위한 본 발명의 일 실시예에 따른 배선 형성 방법은 실리사이드화 반응성 금속 또는 산화 반응성 금속을 포함하는 제 1 은 합금층, 은 도전층 및 산화 반응성 금속을 포함하는 제 2 은 합금층을 차례로 적층하는 단계 및 상기 적층 결과물에 열처리하여 상기 제 1 은 합금층 중의 상기 실리사이드화 반응성 금속을 실리사이드화하거나 또는 상기 산화 반응성 금속을 산화하여 접착층을 형성하고, 상기 제 2 은 합금층 중의 산화 반응성 금속을 산화하여 보호층을 형성하는 단계를 포함한다.

상기 또 다른 기술적 과제를 달성하기 위한 본 발명의 일 실시예에 따른 박막 트랜지스터 기판은 제 1 방향으로 연장되는 게이트선을 포함하는 게이트 배선 및 상기 게이트선과 절연되어 교차하는 제 2 방향으로 연장되는 데이터선을 포함하는 데이터 배선을 포함하되, 상기 게이트 배선 또는 상기 데이터 배선 중 적어도 하나는 산화 반응성 금속 또는 실리사이드화 반응성 금속 및 은을 포함하는 접착층, 은 도전층 및 산화 반응성 금속 및 은을 포함하는 보호층의 순서로 적층된 배선을 포함한다.

상기 또 다른 기술적 과제를 달성하기 위한 본 발명의 일 실시예에 따른 박막 트랜지스터 기판의 제조 방법은 제 1 방향으로 연장되는 게이트선을 포함하는 게이트 배선을 형성하는 단계 및 상기 게이트선과 절연되어 교차하는 제 2 방향으로 연장되는 데이터선을 포함하는 데이터 배선을 형성하는 단계를 포함하되, 상기 게이트 배선 또는 상기 데이터 배선을 형성하는 단계 중 적어도 하나는 실리사이드화 반응성 금속 또는 산화 반응성 금속을 포함하는 제 1 은 합금층, 은 도전층 및 산화 반응성 금속을 포함하는 제 2 은 합금층을 차례로 적층하는 단계 및 상기 적층 결과물에 열처리하여 상기 제 1 은 합금층 중의 실리사이드 반응성 금속을 실리사이드화하거나 또는 상기 산화 반응성 금속을 산화하여 접착층을 형성하고, 상기 제 2 은 합금층 중의 산화 반응성 금속을 산화하여 보호층을 형성하는 단계를 포함한다.

기타 실시예들의 구체적인 사항들은 상세한 설명 및 도면들에 포함되어 있다.

본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시예들을 참조하면 명확해질 것이다. 그러나 본 발 명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

이하, 첨부된 도면을 참조하여 본 발명에 따른 실시예들을 설명한다.

본 발명의 실시예들에 따른 배선에 대해 설명한다. 도 1 내지 도 3은 본 발명의 실시예들에 따른 배선을 도시한 단면도들이다.

도 1에 도시한 바와 같이, 본 발명의 일 실시예에 따른 배선은 기판(1) 상에 산소와의 반응성이 큰 금속인 산화 반응성 금속 및 은을 포함하는 접착층(3), 은 도전층(5) 및 접착층(3)에 포함되는 산화 반응성 금속과 동일한 산화 반응성 금속 및 은을 포함하는 보호층(7)으로 구성된다.

접착층(3)은 산화 반응성 금속이 산소와 반응하여 형성된 산화 금속과 은을 포함하는 합금층으로서 하부에 위치하는 기판(1)과 우수한 접착성을 갖는다. 산화 반응성 금속으로는 산소와 반응하는 것이라면 특별히 한정되지 않지만, 예를 들어 Mg, Al, Li, Zn, In 및 Sn으로부터 선택된 적어도 하나의 금속을 포함할 수 있다. 산화 반응성 금속은 접착층(3) 중에 약 0.1 내지 50원자% 포함될 수 있다. 이때, 접착층(3) 중의 산화 반응성 금속의 농도는 일정하지 않고, 즉 접착층(3)과 은 도전층(5)의 계면에서 기판(1)과의 계면으로 갈수록 산화 반응성 금속의 농도가 증가하는 농도 구배가 형성되어 있다.

접착층(3) 상에 적층된 은 도전층(5)은 배선의 본래 기능인 전기 신호의 통로 역할을 하는 층으로서 낮은 비저항을 갖는다.

은 도전층(5) 상에 형성된 보호층(7)은 접착층(3)에 포함된 산화 반응성 금속과 동일한 산화 반응성 금속이 산소와 반응하여 형성된 산화 금속과 은을 포함하는 합금층으로서 후속의 열처리 공정 또는 식각 공정 등에서 내열성 및 내화학성이 취약한 은 도전층(5)을 보호하는 역할을 한다. 산화 반응성 금속은 보호층(7) 중에 약 0.1 내지 50원자% 포함될 수 있다. 이때, 보호층(7) 중의 산화 반응성 금속의 농도는 일정하지 않고, 즉 보호층(7)과 은 도전층(5)의 계면에서 표면으로 갈수록 산화 반응성 금속의 농도가 증가하는 농도 구배가 형성되어 있다.

도 2에 도시한 바와 같이, 본 발명의 다른 실시예에 따른 배선은 기판(1) 상에 산화 반응성 금속을 포함하는 접착층(3'), 은 도전층(5) 및 산화 반응성 금속을 포함하는 보호층(7)을 포함하고, 접착층(3') 및 보호층(7)에 포함되는 산화 반응성 금속이 서로 다른 금속이라는 것을 제외하고는 본 발명의 일 실시예에 따른 배선과 동일하다. 본 발명의 일 실시예에 따른 배선과 마찬가지로, 접착층(3')은 하부 기판(1)과 우수한 접착성을 갖고, 은 도전층(5)은 전기 신호의 통로 역할을 하며, 보호층(7)은 은 도전층(5)을 보호한다.

도 3에 도시한 바와 같이, 본 발명의 다른 실시예에 따른 배선은 기판(1) 상에 규소와의 반응성이 큰 금속인 실리사이드화 반응성 금속을 포함하는 접착층(3"), 은 도전층(5) 및 산화 반응성 금속을 포함하는 보호층(7)으로 구성된다. 이때, 배선 하부에 존재하는 기판(1)은 규소를 포함하여야 한다.

보호층(3")은 실리사이드화 반응성 금속이 기판(1)에 포함된 규소와 반응하여 형성된 실리사이드 금속과 은을 포함하는 합금층으로서, 하부에 위치하는 기판(1)과 우수한 접착성을 갖는다. 이때, 실리사이드화 반응성 금속은 규소와 반응하는 것이라면 특별히 한정되지 않지만, 예를 들어 Ca, Th, Zr, Co, Ni, Ti, V, Nb, Mo, Ta, W 및 Cr으로부터 선택된 적어도 하나의 금속을 포함할 수 있다. 접착층(3") 중의 실리사이드화 반응성 금속은 약 0.1 내지 50원자% 포함될 수 있다. 이때, 접착층(3") 중의 실리사이드화 반응성 금속의 농도는 일정하지 않고, 즉 접착층(3")과 은 도전층(5)의 계면에서 기판(1)과의 계면으로 갈수록 산화 반응성 금속의 농도가 증가하는 농도 구배가 형성되어 있다.

제 1 은 합금층(3") 상에 적층된 은 도전층(5)은 본 발명의 일 실시예에서와 마찬가지로 전기 신호의 통로 역할을 하고, 은 도전층(5) 상에 형성된 보호층(7)은 산화 반응성 금속이 산소와 반응하여 형성된 산화 금속과 은을 포함하는 합금층으로서, 은 도전층(5)을 보호하는 역할을 한다.

계속해서, 본 발명의 일 실시예에 따른 배선 형성 방법을 도 1 및 도 4 내지 6을 참조하여 설명한다. 도 4 내지 도 6은 본 발명의 일 실시예에 따른 배선 형성 방법의 공정 단계별 단면도들이다.

도 4에 도시한 바와 같이, 예를 들어 SiO2로 이루어진 유리 등으로 이루어진 기판(1)에 은을 기본으로 하고 0.1 내지 50원자%(atomic%)의 산화 반응성 금속을 포함하는 은 합금의 타겟(target)을 스퍼터링하여 제 1 은 합금층(2)을 형성한다. 이러한 산화 반응성 금속으로는 산소와 반응하여 산화 반응을 일으키는 것이라면 특별히 한정되지 않지만, 예를 들어 Mg, Al, Li, Zn, In 및 Sn으로부터 적어도 하나 선택될 수 있다. 이때, 제 1 은 합금층(2)의 두께는 특별히 한정되지는 않지만, 너무 두껍게 형성되는 경우에는 배선의 비저항이 증가될 수 있으므로 예를 들어 100Å내지 2000Å 일 수 있다.

다음, 제 1 은 합금층(2) 상에 은 타겟을 스퍼터링하여 은 도전층(5)을 형성한다. 은 도전층(5)은 배선의 본래 기능인 전기 신호의 통로 역할을 하는 층으로 예를 들어 약 1000 내지 3000Å 일 수 있다.

이어, 은 도전층(5) 상에 은을 기본으로 하고 0.1 내지 50원자%의 산화 반응성 금속을 포함하는 은 합금의 타겟을 스퍼터링하여 제 2 은 합금층(6)을 형성한다. 이러한 산화 반응성 금속은 제 1 은 합금층(2)에 포함되어 있는 산화 반응성 금속과 동일한 금속을 포함할 수도 있고, 다른 금속을 포함할 수도 있다. 본 실시예에서는 제 1 및 제 2 은 합금층(2, 6) 중에 포함된 산화 반응성 금속이 서로 동일한 경우를 예시하여 설명하지만, 산화 반응성 금속이 서로 다른 경우에도 본 발명의 일 실시예에 따른 배선 형성 방법이 적용가능함은 물론이다.

제 2 은 합금층(6)에 포함되는 산화 반응성 금속은 제 1 은 합금층(2)에 포함되는 산화 반응성 금속과 마찬가지로 예를 들어 Mg, Al, Li, Zn, In 및 Sn으로부터 적어도 하나 선택될 수 있다. 이때, 은 합금층의 두께는 특별히 한정되지는 않지만, 너무 두껍게 형성되는 경우에는 배선의 저항이 증가될 수 있으므로, 예를 들어 500 내지 2000Å 일 수 있다.

계속해서, 도 5에 도시한 바와 같이 기판(1) 상에 형성된 제 1 은 합금층(도 4의 2), 은 도전층(5) 및 제 2 은 합금층(도 4의 6)으로 이루어진 적층 결과물에 열처리 공정인 어닐링을 실시한다. 어닐링 공정은 진공, 질소 또는 소량의 산소를 포함하는 분위기 하에서 실시되며, 처리 온도 및 시간은 약 200 내지 300℃에서 약 30 분 내지 2 시간 범위이다.

열처리 결과 제 1 및 제 2 은 합금층(도 4의 2, 6) 중에 포함된 산화 반응성 금속은 은보다 더 빠른 확산 속도를 갖고, 각각 기판(1)과의 계면 및 제 2 은 합금층(도 4의 6)의 표면으로 이동한다. 기판(1)과의 계면으로 이동한 산화 반응성 금속은 기판 중에 포함되는 SiO2와 반응하여, 산화 금속을 형성한다. 제 2 은 합금층(도 4의 6)의 표면으로 이동한 산화 반응성 금속은 대기 중의 산소와 반응하여 산화 금속을 형성한다. 예를 들어 산화 반응성 금속이 Mg 또는 Al 인 경우, 열처리에 의해 산소와 반응하여 MgO 또는 Al2O3의 산화 금속을 형성한다.

이러한 산화 금속을 포함하는 층은 각각 기판과의 접착성을 향상시키는 접착층(3)과 내열성 및 내화학성이 취약한 은 도전층(5)을 보호하는 보호층(7)이 된다. 접착층(3) 및 보호층(7) 중의 산화 반응성 금속의 농도는 일정하지 않고, 즉 접착층(3)에서는 도전층(5)과의 계면에서 기판(1)과의 계면으로 갈수록 산화 반응성 금속의 농도가 높아지는 농도 구배가 형성되고, 보호층(3)에서는 도전층(5)과의 계면에서 보호층(7)의 표면으로 갈수록 산화 반응성 금속의 농도가 높아지는 농도 구배가 형성된다. 이러한 접착층(3) 및 보호층의 두께는 열처리 공정을 수행하기 전의 제 1 은 합금층(도 4의 2) 및 제 2 은 합금층(도 4의 6)의 두께에 따라 달라지지만, 예를 들어 열처리 공정을 수행하기 전의 제 1 은 합금층 및 제 2 은 합금층(도 4의 2, 6)의 두께가 각각 약 500Å, 1000Å인 경우 접착층(3) 및 보호층(7)의 두께는 각각 약 200Å, 150Å일 수 있다.

계속해서, 도 6에 도시한 바와 같이 접착층(3), 은 도전층(5) 및 보호층(7)을 포함하는 열처리 결과물 상에 감광막을 형성하고, 이를 목적하는 형상으로 감광막 패턴(8)을 형성한다.

마지막으로 도 1에 도시한 바와 같이, 감광막 패턴(8)을 식각 마스크로 하여 접착층(3), 은 도전층(5) 및 보호층(7)을 포함하는 열처리 결과물을 패터닝하여 배선을 완성하게 된다.

계속해서 도 3, 도 7 내지 도 9를 참조하여, 본 발명의 다른 실시예에 따른 배선 형성 방법을 설명한다. 도 7 내지 도 9는 본 발명의 다른 실시예에 따른 배선 형성 방법의 공정 단계별 단면도들이다.

도 7에 도시한 바와 같이 기판(1) 예를 들어 진성 비정질 규소나 도핑된 비정질 규소 등을 포함하는 기판(1)에 은을 기본으로 하고 0.1 내지 50원자%(atomic%)의 실리사이드화 반응성 금속을 포함하는 은 합금의 타겟(target)을 스퍼터링하여 실리사이드화 반응성 금속을 포함하는 제 1 은 합금층(2")을 형성한다. 이러한 실리사이드화 반응성 금속으로는 규소와 실리사이드 반응을 일으키는 것이라면 특별히 한정되지 않지만, 예를 들어 Ca, Th, Zr, Co, Ni, Ti, V, Nb, Mo, Ta, W 및 Cr으로부터 적어도 하나 선택될 수 있다. 이때, 제 1 은 합금층(2")의 두께는 특별히 한정되지는 않지만, 너무 두껍게 형성되는 경우에는 배선의 비저항이 증가될 수 있으므로 예를 들어 100 내지 2000Å 일 수 있다.

다음, 제 1 은 합금층(2") 상에 은 타겟을 스퍼터링하여 은 도전층(5)을 형성한다. 은 도전층(5)은 배선의 본래 기능인 전기 신호의 통로 역할을 하는 층으로 예를 들어 약 1000 내지 3000Å 일 수 있다.

이어, 은 도전층(5) 상에 은을 기본으로 하고 0.1 내지 50원자%의 산화 반응성 금속을 포함하는 은 합금의 타겟을 스퍼터링하여 제 2 은 합금층(6)을 형성한다. 이러한 산화 반응성 금속으로는 산소와의 반응성이 좋은 금속이라면 특별히 한정되지는 않지만, 예를 들어 Mg, Al, Li, Zn, In 및 Sn으로부터 적어도 하나 선택될 수 있다. 이때, 은 합금층의 두께는 특별히 한정되지는 않지만, 너무 두껍게 형성되는 경우에는 배선의 저항이 증가될 수 있으므로, 예를 들어 500 내지 2000Å 일 수 있다.

계속해서, 도 8에 도시한 바와 같이 기판(1) 상에 형성된 제 1 은 합금층(도 4의 2"), 은 도전층(5) 및 제 2 은 합금층(도 4의 6)으로 이루어진 적층 결과물에 열처리 공정인 어닐링을 실시한다. 어닐링 공정은 진공, 질소 또는 소량의 산소를 포함하는 분위기 하에서 실시되며, 처리 온도 및 시간은 약 200 내지 300℃에서 약 30 분 내지 2 시간 범위이다.

열처리 결과 제 1 은 합금층(도 4의 2") 중에 포함된 실리사이드화 반응성 금속은 은보다 더 빠른 확산 속도를 갖고, 기판(1)과의 계면으로 이동하여 기판(1)에 포함되어 있는 규소와 반응하여 실리사이드화 금속을 형성한다. 예를 들어 실리 사이드화 반응성 금속이 Ti 또는 Co인 경우, 열처리에 의해 규소와 반응하여 TiSi2 또는 CoSi2의 실리사이드화 금속이 형성된다. 이러한 실리사이드화 금속을 포함하는 층은 기판과의 접착성을 향상시키고, 접촉 저항을 낮출 뿐만 아니라, 은이 기판(1)으로 확산되는 것을 억제하는 접착층(3")이 된다. 접착층(3")에서의 실리사이드화 반응성 금속의 농도는 일정하지 않고, 즉 은 도전층(5)과의 계면에서 기판(1)과의 계면으로 갈수록 실리사이드화 반응성 금속의 농도가 높아지는 농도 구배가 형성된다. 접착층(3")의 두께는 열처리 공정을 수행하기 전의 제 1 은 합금층(도 4의 2")의 두께에 따라 달라지지만, 예를 들어 열처리 공정을 수행하기 전의 제 1 은 합금층(도 4의 2")의 두께가 약 500Å인 경우 접착층(3")의 두께는 약 100Å일 수 있다.

또한, 열처리 결과 제 2 은 합금층(도 4의 6) 중에 포함된 산화 반응성 금속은 은 보다 더 빠른 확산 속도를 갖고, 제 2 은 합금층(도 4의 6)의 표면으로 이동하여 대기 중의 산소와 반응하여 산화 금속을 형성한다. 예를 들어 산화 반응성 금속이 Mg 또는 Al인 경우, 열처리에 의해 산소와 반응하여 MgO 또는 Al2O3의 산화 금속을 형성한다. 이러한 산화 금속을 포함하는 층은 내열성 및 내화학성이 취약한 은 도전층(5)을 보호하는 보호층(7)이 된다. 보호층(7)에서의 산화 반응성 금속의 농도는 일정하지 않고, 즉 은 도전층(5)과의 계면에서 보호층(7)의 표면으로 갈수록 산화 반응성 금속의 농도가 높아지는 농도 구배가 형성된다. 보호층(7)의 두께는 열처리 공정을 수행하기 전의 제 2 은 합금층(도 4의 6)의 두께에 따라 달라지 지만, 예를 들어 열처리 공정을 수행하기 전의 제 2 은 합금층(도 4의 6)의 두께가 약 1000Å인 경우 보호층(7)의 두께가 약 150Å 일 수 있다.

계속해서, 도 9에 도시한 바와 같이 접착층(3"), 은 도전층(5) 및 보호층(7)을 포함하는 열처리 결과물 상에 감광막을 형성하고, 이를 목적하는 형상으로 감광막 패턴(8)을 형성한 후, 도 3에 도시한 바와 같이, 감광막 패턴(8)을 식각 마스크로 하여 접착층(3"), 은 도전층(5) 및 보호층(7)을 포함하는 열처리 결과물을 패터닝하여 배선을 완성하게 된다.

상기한 바와 같은 배선 및 배선의 형성 방법은 박막 트랜지스터 기판 및 그 제조 방법에도 적용될 수 있다.

이하, 첨부된 도면을 참조하여 본 발명의 일 실시예에 따른 박막 트랜지스터 기판 및 그 제조 방법에 대해 설명한다.

먼저 도 10a 내지 도 10c를 참조하여 본 발명의 일 실시예에 따른 제조 방법에 의해 제조된 박막 트랜지스터 기판의 구조에 대해 설명한다. 도 10a는 본 발명의 일 실시예에 따른 제조 방법에 의해 제조된 박막 트랜지스터 기판의 레이아웃도이고, 도 10b 및 도 10c는 도 10a의 B - B' 선을 따라 절단한 단면도들이다.

도 10 a 내지 도 10c에 도시한 바와 같이, 기판(10) 위에 게이트 신호를 전달하는 복수의 게이트 배선(22, 24, 26, 27, 28)이 형성되어 있다. 게이트 배선(22, 24, 26, 27, 28)은 가로 방향으로 뻗어 있는 게이트선(22), 게이트선(22)의 끝에 연결되어 있어 외부로부터의 게이트 신호를 인가받아 게이트선(22)으로 전달하는 게이트 패드(24), 게이트선(22)에 연결되어 돌기 형태로 형성된 박막 트랜지 스터의 게이트 전극(26), 게이트선(22)과 평행하게 형성되어 있는 유지 전극(27) 및 유지 전극선(28)을 포함한다. 유지 전극선(28)은 화소 영역을 가로질러 가로 방향으로 뻗어 있으며, 유지 전극선(28)에 비해 너비가 넓게 형성되어 있는 유지 전극(27)이 연결된다.

유지 전극(27)은 후술할 화소 전극(82)과 연결된 드레인 전극 확장부(67)와 중첩되어 화소의 전하 보존 능력을 향상시키는 유지 축전기를 이룬다. 이와 같은 유지 전극(27) 및 유지 전극선(28)의 모양 및 배치 등은 다양한 형태로 변형될 수 있으며, 화소 전극(82)과 게이트선(22)의 중첩으로 발생하는 유지 용량이 충분할 경우 형성되지 않을 수도 있다.

게이트 배선(22, 24, 26, 27)은 기판(10)과 우수한 접착성을 갖는 산화 반응성 금속을 포함하는 접착층(221, 241, 261, 271), 전기 신호의 통로 역할을 하는 은 도전층(222, 242, 262, 272) 및 내열성과 내화학성이 취약한 은 도전층(222, 242, 262, 272)을 보호하는 산화 반응성 금속을 포함하는 보호층(223, 243, 263, 273)의 삼중층을 포함할 수 있다. 이때, 산화 반응성 금속은 접착층(221, 241, 261, 271) 및 보호층(223, 243, 263, 273)에서 산화 금속의 형태로 포함된다.

이러한 접착층(221, 241, 261, 271) 및 보호층(223, 243, 263, 273)은 도 10b의 G1에 도시한 바와 같이 동일한 산화 반응성 금속을 포함하여 형성될 수도 있고, 도 10c의 G2에 도시한 바와 같이 서로 다른 산화 반응성 금속을 포함하여 형성될 수 도 있다. 또한 도면에 직접 도시되지는 않았지만, 유지 전극선(28)도 다른 게이트 배선(22, 24, 26, 27)과 동일한 구조를 갖는다. 이하에서 설명되는 구성의 게이트 배선에는 유지 전극선(28)도 포함된다.

기판(10), 게이트 배선(22, 24, 26, 27, 28)의 위에는 질화 규소(SiNx) 등으로 이루어진 게이트 절연막(30)이 형성되어 있다.

게이트 절연막(30) 상부에는 수소화 비정질 규소 또는 다결정 규소 등의 반도체로 이루어진 반도체층(42, 44, 48)이 형성되어 있으며, 반도체층(42, 44, 28)의 상부에는 실리사이드 또는 n형 불순물이 고농도로 도핑된 n+ 수소화 비정질 규소 등의 물질로 이루어진 저항성 접촉층(52, 55, 56, 58)이 각각 형성되어 있다.

저항성 접촉층(52, 55, 56, 58)은 그 하부의 반도체층(42, 44, 48)과 그 상부의 데이터 배선(62, 65, 66, 67, 68)의 접촉 저항을 낮추어 주는 역할을 하며, 데이터 배선(62, 65, 66, 67, 68)과 완전히 동일한 형태를 갖는다. 한편, 반도체층(42, 44, 48)은 박막 트랜지스터의 채널부를 제외하면 후술하는 데이터 배선(62, 65, 66, 67, 68) 및 저항성 접촉층(52, 55, 56, 58)과 동일한 모양을 하고 있다.

저항성 접촉층(55, 56) 및 게이트 절연막(30) 위에는 데이터 배선(62, 65, 66, 67, 68)이 형성되어 있다. 데이터 배선(62, 65, 66, 67, 68)은 세로 방향으로 형성되어 게이트선(22)과 교차하여 화소를 정의하는 데이터선(62), 데이터선(62)의 분지이며 저항성 접촉층(55)의 상부까지 연장되어 있는 소오스 전극(65), 데이터선(62)의 한쪽 끝에 연결되어 외부로부터의 화상 신호를 인가받는 데이터 패드(68), 소오스 전극(65)과 분리되어 있으며 게이트 전극(26) 또는 박막 트랜지스터의 채널부에 대하여 소오스 전극(65)의 반대쪽 저항성 접촉층(56) 상부에 형성되어 있는 드레인 전극(66) 및 드레인 전극(66)으로부터 연장되어 유지 전극(27)과 중첩하는 넓은 면적의 드레인 전극 확장부(67)를 포함한다.

소오스 전극(65)은 반도체층(40)과 적어도 일부분이 중첩되고, 드레인 전극(66)은 게이트 전극(26)을 중심으로 소오스 전극(65)과 대향하며 반도체층(40)과 적어도 일부분이 중첩된다.

드레인 전극 확장부(67)는 유지 전극(27)과 중첩되도록 형성되어, 유지 전극(27)과 게이트 절연막(30)을 사이에 두고 유지 용량이 형성된다. 유지 전극(27)을 형성하지 않을 경우 드레인 전극 확장부(27) 또한 형성하지 않는다.

이러한 데이터 배선(62, 65, 66, 67, 68)은 도 10b의 D1에 도시한 바와 같이, 하부층과의 접착성이 우수하고 접촉 저항을 낮출 수 있는 실리사이드 반응성 금속을 포함하는 접착층(621, 651, 661, 671, 681), 전기 신호의 통로 역할을 하는 은 도전층(622, 652, 662, 672, 682) 및 내열성과 내화학성이 취약한 은 도전층(622, 652, 662, 672, 682)을 보호하는 산화 반응성 금속을 포함하는 보호층(623, 653, 663, 673, 683)의 삼중의 금속층을 포함한다. 이때, 실라사이드화 반응성 금속은 저항성 접촉층(55, 56)의 상부의 접착층(621, 651, 661, 671, 681)에서 실리사이드화 금속의 형태로 포함되고, 산화 반응성 금속은 보호층(623, 653, 663, 673, 683)에서 산화 금속의 형태로 포함된다.

데이터 배선(62, 65, 66, 67, 68) 및 이들이 가리지 않는 반도체층(40) 상부에는 보호막(70)이 형성되어 있다. 보호막(70)은 예를 들어 평탄화 특성이 우수하며 감광성(photosensitivity)을 가지는 유기 물질, 플라즈마 화학기상증착(Plasma Enhanced Chemical Vapor Deposition; PECVD)으로 형성되는 a-Si:C:O, a-Si:O:F 등의 저유전율 절연 물질, 또는 무기 물질인 질화 규소(SiNx) 등으로 형성될 수 있다.

또한, 보호막(70)을 유기 물질로 형성하는 경우에는 소오스 전극(65)과 드레인 전극(66) 사이의 반도체층(40)이 드러난 부분에 보호막(70)의 유기 물질이 접촉하는 것을 방지하기 위하여, 유기막의 하부에 질화 규소(SiNx) 또는 산화 규소(SiO2)로 이루어진 절연막(도시하지 않음)이 추가로 형성될 수도 있다.

보호막(70)에는 드레인 전극 확장부(67) 및 데이터선 패드(68)를 각각 드러내는 컨택홀(77, 78)이 형성되어 있으며, 보호막(70)과 게이트 절연막(30)에는 게이트선 패드(24)을 드러내는 컨택홀(74)이 형성되어 있다. 보호막(70) 위에는 컨택홀(77)을 통하여 드레인 전극(66)과 전기적으로 연결되며 화소에 위치하는 화소 전극(82)이 형성되어 있다. 데이터 전압이 인가된 화소 전극(82)은 상부 기판의 공통 전극과 함께 전기장을 생성함으로써 화소 전극(82)과 공통 전극 사이의 액정층의 액정 분자들의 배열을 결정한다.

또한, 보호막(70) 위에는 컨택홀(74, 78)을 통하여 각각 게이트 패드(24) 및 데이터 패드(68)와 연결되어 있는 보조 게이트 패드(84) 및 보조 데이터 패드(88)가 형성되어 있다. 화소 전극(82)과 보조 게이트 및 데이터 패드(86, 88)는 투명 도전성 물질, 예를 들어 인듐 틴 옥사이드 또는 인듐 징크 옥사이드로 이루어져 있다.

이하, 본 발명의 일 실시예에 따른 배선 형성 방법을 이용한 박막 트랜지스터 기판의 제조 방법에 대하여 도 10a 내지 도 10c와, 도 11a 내지 도 19b를 참조하여 상세히 설명한다.

먼저 도 11a 및 도 11b에 도시된 바와 같이, SiO2로 이루어진 유리 기판(10) 위에 은을 기본으로 하고 0.1 내지 50원자%의 산화 반응성 금속을 포함하는 은 합금의 타겟을 스퍼터링하여 제 1 은 합금층을 형성하고, 이어 은 타겟을 스퍼터링 하여 은 도전층을 형성한 후, 0.1 내지 50원자%의 산화 반응성 금속을 포함하는 은 합금 타겟을 스퍼터링하여 제 2 은 합금층을 형성한다.

이때, 제 1 및 제 2 은 합금층 중에 포함되는 산화 반응성 금속은 서로 동일하거나 다를 수 있다. 이러한 산화 반응성 금속으로는 산소와 반응하여 산화 반응을 일으키는 것이라면 특별히 한정되지 않지만, 예를 들어 Mg, Al, Li, Zn, In 및 Sn으로부터 선택된 적어도 하나 선택될 수 있다. 제 1 은 합금층, 은 도전층 및 제 2 은 합금층의 두께는 특별히 한정되지 않지만, 배선의 비저항이 증가되지 않도록 예를 들어 각각, 100 내지 2000Å, 1000 내지 3000Å 및 500 내지 2000Å 일 수 있다.

삼중의 금속층을 예를 들어 진공, 질소 또는 소량의 산소를 포함하는 분위기 하에서 약 200 내지 300℃에서 약 30 분 내지 2 시간 동안 어닐링한다. 그 결과, 제 1 은 합금층 중의 산화 반응성 금속은 기판(10)과의 계면으로 확산되어 기판(10)의 SiO2와 반응하여 산화 금속을 형성한다. 또한, 제 2 은 합금층 중의 산화 반 응성 금속은 표면으로 확산되어 대기 중의 산소와 반응하여 산화 금속을 형성한다. 따라서, 제 1 은 합금층, 은 도전층 및 제 2 은 합금층은 열처리에 의해 기판(10)과의 접착성이 우수한 접착층(221, 241, 261, 271), 전기 신호의 통로 역할을 하는 은 도전층(222, 242, 262, 272) 및 내열성 및 내화학성이 취약한 은 도전층(223, 243, 263, 273)을 보호하는 보호층(223, 243, 263, 273)으로 된다. 이때, 접착층(221, 241, 261, 271) 및 보호층(223, 243, 263, 273)은 은 도전층(222, 242, 262, 272)과의 계면에서 각각 기판(10)과의 계면 및 표면으로 갈수록 산화 반응성 금속의 농도가 높아지는 농도 구배가 형성된다.

이러한 열처리 결과물을 패터닝하여 게이트선(22), 게이트 전극(26), 게이트 패드(24), 유지 전극(27) 및 유지 전극선(28)을 포함하는 게이트 배선(22, 24, 26, 27, 28)을 형성한다.

이어, 도 12에 도시된 바와 같이, 질화 규소로 이루어진 게이트 절연막(30), 진성 비정질 규소층 및 도핑된 비정질 규소층을 예컨대, 화학 기상 증착법을 이용하여 각각 1,500Å 내지 5,000Å, 500Å 내지 2,000Å, 300Å 내지 600Å의 두께로 연속 증착한다.

다음, 도핑된 비정질 규소층(50) 위에 예를 들어 은을 기본으로 하고 0.1 내지 50원자%의 실리사이드화 반응성 금속을 포함하는 은 합금의 타겟을 스퍼터링하여 제 3 은 합금층을 형성하고, 이어 은 타겟을 스퍼터링 하여 은 도전층을 형성한 후, 0.1 내지 50원자%의 산화 반응성 금속을 포함하는 은 합금 타겟을 스퍼터링하여 제 4 은 합금층을 형성한다.

이때, 제 3 은 합금층 중에 포함되는 실리사이드화 반응성 금속으로는 규소와 반응하여 실리사이드화 반응을 일으키는 것이라면 특별히 한정되지 않지만, 예를 들어 Ca, Th, Zr, Co, Ni, Ti, V, Nb, Mo, Ta, W 및 Cr으로부터 적어도 하나 선택될 수 있다. 또한, 제 4 은 합금층 중에 포함되는 산화 반응성 금속은 산소와 반응하여 산화 반응을 일으키는 것이라면 특별히 한정되지 않지만, 예를 들어 예를 들어 Mg, Al, Li, Zn, In 및 Sn으로부터 적어도 하나 선택될 수 있다. 제 3 은 합금층, 은 도전층 및 제 4 은 합금층의 두께는 특별히 한정되지 않지만, 배선의 비저항이 증가되지 않도록 예를 들어 각각, 100 내지 2000 Å, 1000 내지 3000Å 및 500 내지 2000Å 일 수 있다.

삼중의 금속층을 예를 들어 진공, 질소 또는 소량의 산소를 포함하는 분위기 하에서 약 200 내지 300℃에서 약 30분 내지 2시간 동안 어닐링한다. 그 결과, 제 3 은 합금층 중의 실리사이드와 반응성 금속은 진성 비정질 규소층 및 도핑된 비정질 규소층과의 계면으로 확산되어 진성 비정질 규소층 및 도핑된 비정질 규소층의 규소와 반응하여 실리사이드화 금속을 형성한다. 또한, 제 4 은 합금층 중의 산화 반응성 금속은 표면으로 확산되어 대기 중의 산소와 반응하여 산화 금속을 형성한다. 따라서, 제 3 은 합금층, 은 도전층 및 제 4 은 합금층은 열처리에 의해 하부막과의 접착성이 우수한 접착층(601), 전기 신호의 통로 역할을 하는 은 도전층(602) 및 내열성 및 내화학성이 취약한 은 도전층(602)을 보호하는 보호층(603)으로 된다. 이때, 접착층(601) 및 보호층(603)은 은 도전층(602)과의 계면에서 각각 진성 비정질 규소층 및 도핑된 비정질 규소층의 계면 및 표면으로 갈수록 실리사이 드화 반응성 금속의 농도 및 산화 반응성 금속의 농도가 높아지는 농도 구배가 형성된다.

이어, 열처리된 결과물 상에 감광막(110)을 도포한다.

다음, 도 13a 및 도 13b에 도시된 바와 같이, 마스크(도시하지 않음)를 통하여 감광막(110)에 광을 조사한 후 현상하여, 감광막 패턴(112, 114)을 형성한다. 이때, 감광막 패턴(112, 114) 중에서 박막 트랜지스터의 채널부, 즉 소오스 전극(도 10b 및 도 10c의 65)과 드레인 전극(도 10b 및 도 10c의 66) 사이에 위치한 제 1 부분(114)은 데이터 배선부, 즉 데이터 배선이 형성될 부분에 위치한 제 2 부분(112)보다 두께가 작게 되도록 하며, 채널부와 데이터 배선부를 제외한 기타 부분의 감광막은 모두 제거한다. 이때, 채널부에 남아 있는 감광막(114)의 두께와 데이터 배선부에 남아 있는 감광막(112)의 두께의 비는 후술할 식각 공정에서의 공정 조건에 따라 다르게 하여야 하되, 제 1 부분(114)의 두께를 제 2 부분(112)의 두께의 1/2 이하로 할 수 있으며, 예를 들면, 4,000Å 이하로 할 수 있다.

다음, 감광막 패턴(112, 114)을 식각 마스크로 하여 그 하부의 보호층(603), 은 도전층(602) 및 접착층(601)으로 이루어진 열처리 결과물을 패터닝한다. 그 결과, 도 14에 도시한 바와 같이 채널부 및 데이터 배선부의 삼중층 패턴만이 남고, 채널부 및 데이터 배선부를 제외한 기타 부분의 삼중층(60)은 모두 제거되어 그 하부의 도핑된 비정질 규소층(50)이 드러난다. 이때 남은 삼중층 패턴은 소오스 및 드레인 전극((도 10b 및 도 10c의 65, 66)이 분리되지 않고 연결되어 있는 점을 제외하면 최종적인 데이터 배선의 형태와 동일하다.

이어, 도 15에 도시한 바와 같이 이어서, 채널부와 데이터 배선부를 제외한 기타 부분의 노출된 도핑된 비정질 규소층(50) 및 그 하부의 진성 비정질 규소층(40)을 감광막의 제 1 부분(114)과 함께 건식 식각 방법으로 동시에 제거하고, 애싱(ashing)을 통하여 채널부의 소오스/드레인용 삼중층 패턴(64)의 표면에 남아 있는 감광막 찌꺼기를 제거한다.

다음, 도 16에 도시된 바와 같이 채널부의 보호층(643), 은 도전층(642) 및 접착층(641)으로 이루어진 삼중층 패턴을 식각하여 제거한 후, 도핑된 비정질 규소로 이루어진 저항성 접촉층(52, 55, 56, 58)을 형성한다. 이때 건식 식각이 사용될 수 있다. 반도체층(44)의 일부가 제거되어 두께가 작아질 수도 있으며 감광막 패턴의 제 2 부분(112)도 어느 정도의 두께로 식각될 수 있다. 그 결과, 소오스 전극(65)과 드레인 전극(66)이 분리되면서 데이터 배선(65, 66)과 그 하부의 저항성 접촉층(55, 56)이 완성된다.

이어, 도 17에 도시한 바와 같이 데이터 배선부에 남아 있는 감광막 제 2 부분(도 16의 112)를 제거한다.

다음, 도 18에 도시한 바와 같이 평탄화 특성이 우수하며 감광성을 가지는 유기 물질, 플라즈마 화학 기상 증착(Plasma Enhanced Chemical Vapor Deposition; PECVD)으로 형성되는 a-Si:C:O, a-Si:O:F 등의 저유전율 절연 물질, 또는 무기 물질인 질화 규소(SiNx) 등을 단일층 또는 복수층으로 형성하여 보호막(passivation layer)(70)을 형성한다.

이어, 도 19a 및 도 19b에 도시한 바와 같이, 사진 식각 공정으로 게이트 절 연막(30)과 함께 보호막(70)을 패터닝하여, 게이트 패드(24), 드레인 전극 확장부(67) 및 데이터 패드(68)를 드러내는 컨택홀(74, 77, 78)을 형성한다. 이때 감광성을 가지는 유기막일 경우에는 사진 공정만으로 컨택홀을 형성할 수 있으며, 게이트 절연막(30)과 보호막(70)에 대하여 실질적으로 동일한 식각비를 갖는 식각 조건으로 실시하는 것이 바람직하다.

이어, 마지막으로 도 10a 내지 도 10c에 도시된 바와 같이, 투명 도전성 물질, 예를 들어 인듐 틴 옥사이드 또는 인듐 징크 옥사이드를 증착하고 사진 식각하여 컨택홀(77)을 통하여 드레인 전극(66)과 연결되는 화소 전극(82)과 컨택홀(74, 78)을 통하여 게이트 패드(24) 및 데이터 패드(68)과 각각 연결되는 보조 게이트 패드(84) 및 보조 데이터 패드(88)를 형성한다.

본 명세서에서는 반도체층과 데이터 배선을 하나의 감광막 패턴을 이용한 사진 식각 공정으로 형성하는 박막 트랜지스터 기판의 제조 방법을 설명하였으나, 서로 다른 마스크를 이용한 사진 식각 공정으로 형성하는 박막 트랜지스터 기판의 제조 방법에 대해서도 적용 가능하다.

또한, 본 명세서에서는 박막 트랜지스터 기판의 데이터 배선을 실리사이드화 반응성 금속을 포함하는 접착층을 포함하는 경우에 대해서만 설명하였지만, 이는 예시적인 것에 불과하고 산화 반응성 금속을 포함하는 접착층을 포함하여도 무방하다.

이상 첨부된 도면을 참조하여 본 발명의 실시예를 설명하였지만, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자는 본 발명이 그 기술적 사상이나 필수 적인 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해해야만 한다.

상술한 바와 같이, 본 발명의 일 실시예에 따른 배선의 형성 방법을 이용하여 형성된 박막 트랜지스터 기판의 게이트 배선 또는 데이터 배선은 은 도전층 하부에는 접착층을 개재하여 하부층과의 접착성을 향상시키고, 상부에는 보호층을 형성하여 은 도전층을 보호한다. 따라서, 게이트 배선 또는 데이터 배선의 들뜸 또는 벗겨짐 현상이 방지되어 결국 액정 표시 장치의 신호 특성이 좋아지고, 화질이 개선된다.

Claims (36)

- 산화 반응성 금속 또는 실리사이드화 반응성 금속 및 은을 포함하는 접착층;상기 접착층 상에 형성된 은 도전층; 및상기 은 도전층 상에 형성되고 상기 산화 반응성 금속 및 상기 은을 포함하는 보호층을 포함하는 배선.

- 제 1 항에 있어서,상기 접착층 및 상기 보호층 중의 상기 각 산화 반응성 금속은 서로 동일하거나 다른 금속인 배선.

- 제 1 항에 있어서,상기 산화 반응성 금속은 Mg, Al, Li, Zn, In 및 Sn으로부터 선택된 적어도 하나의 금속을 포함하는 배선.

- 제 1 항에 있어서,상기 접착층 또는 상기 보호층은 산화 반응성 금속을 0.1 내지 50원자% 포함하는 배선.

- 제 1 항에 있어서,상기 실리사이드화 반응성 금속을 포함하는 상기 접착층은 하부에 규소층을 더 포함하는 배선.

- 제 1 항에 있어서,상기 실리사이드화 반응성 금속은 Ca, Th, Zr, Co, Ni, Ti, V, Nb, Mo, Ta, W 및 Cr로부터 선택된 적어도 하나의 금속을 포함하는 배선.

- 제 1 항에 있어서,상기 접착층은 상기 실리사이드화 반응성 금속을 0.1 내지 50원자% 포함하는 배선.

- 제 1 항에 있어서,상기 접착층 중의 상기 실리사이드화 반응성 금속은 규소와 반응하여 실리사이드화된 금속으로 포함되거나, 상기 접착층 중의 상기 산화 반응성 금속은 산소와 반응하여 산화된 금속으로 포함되는 배선.

- 제 1 항에 있어서,상기 보호층 중의 상기 산화 반응성 금속은 산소와 반응하여 산화된 금속으로 포함되는 배선.

- 실리사이드화 반응성 금속 또는 산화 반응성 금속을 포함하는 제 1 은 합금층, 은 도전층 및 산화 반응성 금속을 포함하는 제 2 은 합금층을 차례로 적층하는 단계; 및상기 적층 결과물에 열처리하여 상기 제 1 은 합금층 중의 상기 실리사이드화 반응성 금속을 실리사이드화하거나 또는 상기 산화 반응성 금속을 산화하여 접착층을 형성하고, 상기 제 2 은 합금층 중의 산화 반응성 금속을 산화하여 보호층을 형성하는 단계를 포함하는 배선 형성 방법.

- 제 10 항에 있어서,상기 제 1 및 제 2 은 합금층 중의 상기 각 산화 반응성 금속은 서로 동일하거나 다른 금속인 배선 형성 방법.

- 제 10 항에 있어서,상기 산화 반응성 금속은 Ca, Th, Zr, Co, Ni, Ti, V, Nb, Mo, Ta, W 및 Cr로부터 선택된 적어도 하나의 금속을 포함하는 배선 형성 방법.

- 제 10 항에 있어서,상기 제 1 은 합금층 또는 상기 제 2 은 합금층은 상기 산화 반응성 금속을 0.1 내지 50원자% 포함하는 배선 형성 방법.

- 제 10 항에 있어서,상기 실리사이드화 반응성 금속을 포함하는 상기 제 1 은 합금층의 하부에 규소층을 더 포함하는 배선 형성 방법.

- 제 10 항에 있어서,상기 실리사이드화 반응성 금속은 Ca, Th, Zr, Co, Ni, Ti, V, Nb, Mo, Ta, W 및 Cr로부터 선택된 적어도 하나의 금속을 포함하는 배선 형성 방법.

- 제 10 항에 있어서,상기 제 1 은 합금층은 상기 실리사이드화 반응성 금속을 0.1 내지 50원자% 포함하는 배선 형성 방법.

- 제 10 항에 있어서,상기 열처리 온도는 200 내지 300℃인 배선 형성 방법.

- 제 1 방향으로 연장되는 게이트선을 포함하는 게이트 배선; 및상기 게이트선과 절연되어 교차하는 제 2 방향으로 연장되는 데이터선을 포함하는 데이터 배선을 포함하되, 상기 게이트 배선 또는 상기 데이터 배선 중 적어도 하나는 산화 반응성 금속 또는 실리사이드화 반응성 금속 및 은을 포함하는 접착층, 은 도전층 및 산화 반응성 금속 및 은을 포함하는 보호층의 순서로 적층된 배선을 포함하는 박막 트랜지스터 기판.

- 제 18 항에 있어서,상기 접착층 및 상기 보호층 중의 상기 각 산화 반응성 금속은 서로 동일하거나 다른 금속인 박막 트랜지스터 기판.

- 제 18 항에 있어서,상기 산화 반응성 금속은 Mg, Al, Li, Zn, In 및 Sn으로부터 선택된 적어도 하나의 금속을 포함하는 박막 트랜지스터 기판.

- 제 18 항에 있어서,상기 접착층 또는 상기 보호층은 상기 산화 반응성 금속을 0.1 내지 50원자% 포함하는 박막 트랜지스터 기판.

- 제 18 항에 있어서,상기 실리사이드화 반응성 금속을 포함하는 상기 접착층 하부에 규소층을 더 포함하는 박막 트랜지스터 기판.

- 제 22 항에 있어서,상기 규소층은 반도체층 또는 저항성 접촉층인 박막 트랜지스터 기판.

- 제 18 항에 있어서,상기 실리사이드화 반응성 금속은 Ca, Th, Zr, Co, Ni, Ti, V, Nb, Mo, Ta, W 및 Cr로부터 선택된 적어도 하나의 금속을 포함하는 박막 트랜지스터 기판.

- 제 18 항에 있어서,상기 접착층은 상기 실리사이드화 반응성 금속을 0.1 내지 50원자% 포함하는 박막 트랜지스터 기판.

- 제 18 항에 있어서,상기 접착층 중의 상기 실리사이드화 반응성 금속은 규소와 반응하여 실리사이드화된 금속으로 포함되거나, 상기 접착층 중의 상기 산화 반응성 금속은 산소와 반응하여 산화된 금속으로 포함되는 박막 트랜지스터 기판.

- 제 18 항에 있어서,상기 보호층 중의 상기 산화 반응성 금속은 산소와 반응하여 산화된 금속으로 포함되는 박막 트랜지스터 기판.

- 제 1 방향으로 연장되는 게이트선을 포함하는 게이트 배선을 형성하는 단계; 및상기 게이트선과 절연되어 교차하는 제 2 방향으로 연장되는 데이터선을 포함하는 데이터 배선을 형성하는 단계를 포함하되,상기 게이트 배선 또는 상기 데이터 배선을 형성하는 단계 중 적어도 하나는 실리사이드화 반응성 또는 산화 반응성 금속을 포함하는 제 1 은 합금층, 은 도전층 및 산화 반응성 금속을 포함하는 제 2 은 합금층을 차례로 적층하는 단계 및 상기 적층 결과물에 열처리하여 상기 제 1 은 합금층 중의 실리사이드화 반응성 금속을 실리사이드화하거나 또는 상기 산화 반응성 금속을 산화하여 접착층을 형성하고, 상기 제 2 은 합금층 중의 산화 반응성 금속을 산화하여 보호층을 형성하는 단계를 포함하는 박막 트랜지스터 기판의 제조 방법.

- 제 28 항에 있어서,상기 제 1 및 제 2 은 합금층 중의 상기 산화 반응성 금속은 서로 동일하거나 다른 금속인 박막 트랜지스터 기판의 제조 방법.

- 제 28 항에 있어서,상기 산화 반응성 금속은 Ca, Th, Zr, Co, Ni, Ti, V, Nb, Mo, Ta, W 및 Cr로부터 선택된 적어도 하나의 금속을 포함하는 박막 트랜지스터 기판의 제조 방법.

- 제 28 항에 있어서,상기 제 1 은 합금층은 상기 산화 반응성 금속을 0.1 내지 50원자% 포함하는 박막 트랜지스터 기판의 제조 방법.

- 제 28 항에 있어서,상기 실리사이드화 반응성 금속을 포함하는 상기 제 1 은 합금층의 하부에 규소층을 더 포함하는 박막 트랜지스터 기판의 제조 방법.

- 제 32 항에 있어서,상기 규소층은 반도체층 또는 저항성 접촉층인 박막 트랜지스터 기판의 제조 방법.

- 제 28 항에 있어서,상기 실리사이드화 반응성 금속은 Ca, Th, Zr, Co, Ni, Ti, V, Nb, Mo, Ta, W 및 Cr로부터 선택된 적어도 하나의 금속을 포함하는 박막 트랜지스터 기판의 제조 방법.

- 제 28 항에 있어서,상기 제 1 은 합금층은 상기 실리사이드화 반응성 금속을 0.1 내지 50원자% 포함하는 박막 트랜지스터 기판의 제조 방법.

- 제 28 항에 있어서,상기 열처리 온도는 200 내지 300℃인 박막 트랜지스터 기판의 제조 방법.

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020050074455A KR20070019458A (ko) | 2005-08-12 | 2005-08-12 | 배선 및 그 형성 방법과 박막 트랜지스터 기판 및 그 제조방법 |

| JP2006218156A JP5215543B2 (ja) | 2005-08-12 | 2006-08-10 | 薄膜トランジスタ基板 |

| US11/502,918 US7808108B2 (en) | 2005-08-12 | 2006-08-11 | Thin film conductor and method of fabrication |

| TW095129564A TWI423445B (zh) | 2005-08-12 | 2006-08-11 | 薄膜導體及製造方法 |

| CN200610112109XA CN1913146B (zh) | 2005-08-12 | 2006-08-11 | 薄膜导体及其制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020050074455A KR20070019458A (ko) | 2005-08-12 | 2005-08-12 | 배선 및 그 형성 방법과 박막 트랜지스터 기판 및 그 제조방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20070019458A true KR20070019458A (ko) | 2007-02-15 |

Family

ID=37722015

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020050074455A KR20070019458A (ko) | 2005-08-12 | 2005-08-12 | 배선 및 그 형성 방법과 박막 트랜지스터 기판 및 그 제조방법 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7808108B2 (ko) |

| JP (1) | JP5215543B2 (ko) |

| KR (1) | KR20070019458A (ko) |

| CN (1) | CN1913146B (ko) |

| TW (1) | TWI423445B (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20190033674A (ko) * | 2017-09-21 | 2019-04-01 | 삼성디스플레이 주식회사 | 표시 장치 |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8334537B2 (en) * | 2007-07-06 | 2012-12-18 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device |

| US8373948B2 (en) * | 2008-04-28 | 2013-02-12 | Hitachi Global Storage Technologies Netherlands B.V. | Tunnel magnetoresistance (TMR) structures with MGO barrier and methods of making same |

| US20100224878A1 (en) * | 2009-03-05 | 2010-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| TWI419328B (zh) * | 2009-06-12 | 2013-12-11 | Ind Tech Res Inst | 主動層堆疊結構及其製造方法及其應用 |

| KR101857405B1 (ko) | 2009-07-10 | 2018-05-11 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| EP2312633A1 (en) * | 2009-10-15 | 2011-04-20 | Applied Materials, Inc. | Method and installation for producing a semiconductor device, and semiconductor device |

| KR101969291B1 (ko) | 2010-02-26 | 2019-04-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR20130055607A (ko) | 2010-04-23 | 2013-05-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치의 제작 방법 |

| CN102955308B (zh) * | 2011-08-19 | 2015-06-10 | 乐金显示有限公司 | 用于显示装置的阵列基板及其制造方法 |

| KR101976057B1 (ko) * | 2011-08-19 | 2019-05-07 | 엘지디스플레이 주식회사 | 표시장치용 어레이 기판 및 그의 제조방법 |

| KR101881895B1 (ko) * | 2011-11-30 | 2018-07-26 | 삼성디스플레이 주식회사 | 박막트랜지스터 어레이 기판, 이를 포함하는 유기 발광 표시 장치 및 박막트랜지스터 어레이 기판의 제조 방법 |

| KR102066592B1 (ko) * | 2013-09-27 | 2020-02-11 | 엘지디스플레이 주식회사 | 디스플레이 장치 및 그 제조방법 |

| KR102240456B1 (ko) * | 2014-07-30 | 2021-04-15 | 에스케이하이닉스 주식회사 | 광학적 관통 비아를 가지는 반도체 소자 |

| US9941376B2 (en) * | 2015-04-30 | 2018-04-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | Metal gate scheme for device and methods of forming |

| CN107275342B (zh) * | 2017-06-12 | 2019-11-08 | 京东方科技集团股份有限公司 | 一种显示装置及其制备方法 |

| US10901543B1 (en) * | 2017-09-29 | 2021-01-26 | Apple Inc. | Touch screen with transparent electrode structure |

| GB2590427A (en) * | 2019-12-17 | 2021-06-30 | Flexanable Ltd | Semiconductor devices |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2917616B2 (ja) | 1991-10-25 | 1999-07-12 | 三菱マテリアル株式会社 | 保護膜付銀合金導体箔及びその製造方法 |

| KR100307385B1 (ko) * | 1997-03-05 | 2001-12-15 | 구본준, 론 위라하디락사 | 액정표시장치의구조및그제조방법 |

| US6297519B1 (en) * | 1998-08-28 | 2001-10-02 | Fujitsu Limited | TFT substrate with low contact resistance and damage resistant terminals |

| KR100750922B1 (ko) * | 2001-04-13 | 2007-08-22 | 삼성전자주식회사 | 배선 및 그 제조 방법과 그 배선을 포함하는 박막트랜지스터 기판 및 그 제조 방법 |

| JP4620298B2 (ja) * | 2001-07-23 | 2011-01-26 | パイオニア株式会社 | 銀若しくは銀合金配線及びその形成方法並びに表示パネル基板 |

| KR100980008B1 (ko) * | 2002-01-02 | 2010-09-03 | 삼성전자주식회사 | 배선 구조, 이를 이용하는 박막 트랜지스터 기판 및 그제조 방법 |

| KR100825102B1 (ko) * | 2002-01-08 | 2008-04-25 | 삼성전자주식회사 | 박막 트랜지스터 기판 및 그 제조 방법 |

| JP4496518B2 (ja) | 2002-08-19 | 2010-07-07 | 日立金属株式会社 | 薄膜配線 |

| JP2004131747A (ja) | 2002-10-08 | 2004-04-30 | Sumitomo Metal Mining Co Ltd | 表示デバイス用銀合金及びこの銀合金を用いて形成した電極膜または反射膜を使用する表示デバイス |

| JP4278034B2 (ja) * | 2003-03-10 | 2009-06-10 | シャープ株式会社 | 表示装置用基板及びその製造方法及びそれを備えた表示装置 |

| JP2004277780A (ja) * | 2003-03-13 | 2004-10-07 | Furuya Kinzoku:Kk | 銀系合金の積層構造並びにそれを用いた電極、配線、反射膜及び反射電極 |

| TWI319776B (en) * | 2003-07-23 | 2010-01-21 | Silver alloy material, circuit substrate, electronic device, and method for manufacturing circuit substrate |

-

2005

- 2005-08-12 KR KR1020050074455A patent/KR20070019458A/ko not_active Application Discontinuation

-

2006

- 2006-08-10 JP JP2006218156A patent/JP5215543B2/ja active Active

- 2006-08-11 CN CN200610112109XA patent/CN1913146B/zh active Active

- 2006-08-11 TW TW095129564A patent/TWI423445B/zh active

- 2006-08-11 US US11/502,918 patent/US7808108B2/en not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20190033674A (ko) * | 2017-09-21 | 2019-04-01 | 삼성디스플레이 주식회사 | 표시 장치 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1913146A (zh) | 2007-02-14 |

| CN1913146B (zh) | 2012-06-20 |

| US7808108B2 (en) | 2010-10-05 |

| TW200713597A (en) | 2007-04-01 |

| JP5215543B2 (ja) | 2013-06-19 |

| TWI423445B (zh) | 2014-01-11 |

| JP2007053363A (ja) | 2007-03-01 |

| US20070034954A1 (en) | 2007-02-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20070019458A (ko) | 배선 및 그 형성 방법과 박막 트랜지스터 기판 및 그 제조방법 | |

| JP4368200B2 (ja) | 薄膜トランジスタ基板及びその製造方法 | |

| JP2007053363A5 (ko) | ||

| KR20070049278A (ko) | 배선, 이를 포함하는 박막 트랜지스터 기판과 그 제조 방법 | |

| KR20080108223A (ko) | Tft 기판, 반사형 tft 기판 및 이들의 제조 방법 | |

| KR20080106900A (ko) | 반사형 tft 기판 및 반사형 tft 기판의 제조 방법 | |

| JP2002055362A (ja) | 液晶表示装置用薄膜トランジスタ基板の製造方法 | |

| KR20070009329A (ko) | 컨택홀 형성 방법 및 이를 이용한 박막 트랜지스터 기판의제조 방법 | |

| CN113345837A (zh) | 一种显示面板的制作方法及显示面板 | |

| CN212010934U (zh) | 阵列基板及显示面板 | |

| KR20030016051A (ko) | 액정 표시 장치용 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR20020080559A (ko) | 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR100623988B1 (ko) | 배선의 접촉 구조 및 그의 제조 방법과 이를 포함하는박막 트랜지스터 기판 및 그 제조 방법 | |

| KR100672623B1 (ko) | 액정표시장치 제조방법 | |

| KR100750913B1 (ko) | 배선의 제조 방법 및 그 배선을 포함하는 액정 표시장치용 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR20020037845A (ko) | 액정 표시 장치용 박막 트랜지스터 기판의 제조 방법 | |

| KR100709707B1 (ko) | 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR100709706B1 (ko) | 배선의 접촉 구조 및 그의 제조 방법과 이를 포함하는박막 트랜지스터 기판 및 그 제조 방법 | |

| KR100375497B1 (ko) | 배선의 접촉부 및 그의 제조 방법과 이를 포함하는 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR100750919B1 (ko) | 액정 표시 장치용 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR100656917B1 (ko) | 배선의 접촉 구조 및 그의 제조 방법과 이를 포함하는박막 트랜지스터 기판 및 그 제조 방법 | |

| KR20080030798A (ko) | 박막 트랜지스터 표시판의 제조 방법 | |

| KR20010017529A (ko) | 액정 표시 장치용 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR100783696B1 (ko) | 액정 표시 장치용 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR20070008257A (ko) | 배선 및 그 형성 방법과 박막 트랜지스터 기판 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| N231 | Notification of change of applicant | ||

| E601 | Decision to refuse application |