KR100262434B1 - 쌍방향 전송형 기억장치 및 메모리의 입출력 제어방법 - Google Patents

쌍방향 전송형 기억장치 및 메모리의 입출력 제어방법 Download PDFInfo

- Publication number

- KR100262434B1 KR100262434B1 KR1019970043250A KR19970043250A KR100262434B1 KR 100262434 B1 KR100262434 B1 KR 100262434B1 KR 1019970043250 A KR1019970043250 A KR 1019970043250A KR 19970043250 A KR19970043250 A KR 19970043250A KR 100262434 B1 KR100262434 B1 KR 100262434B1

- Authority

- KR

- South Korea

- Prior art keywords

- memory

- mode

- data

- address

- filo

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/76—Arrangements for rearranging, permuting or selecting data according to predetermined rules, independently of the content of the data

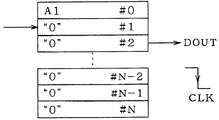

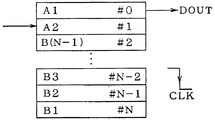

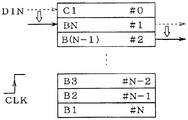

- G06F7/78—Arrangements for rearranging, permuting or selecting data according to predetermined rules, independently of the content of the data for changing the order of data flow, e.g. matrix transposition or LIFO buffers; Overflow or underflow handling therefor

- G06F7/785—Arrangements for rearranging, permuting or selecting data according to predetermined rules, independently of the content of the data for changing the order of data flow, e.g. matrix transposition or LIFO buffers; Overflow or underflow handling therefor having a sequence of storage locations each being individually accessible for both enqueue and dequeue operations, e.g. using a RAM

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Mathematical Physics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Dram (AREA)

- Shift Register Type Memory (AREA)

- Memory System (AREA)

- Image Input (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP97-037683 | 1997-02-21 | ||

| JP9037683A JPH10241354A (ja) | 1997-02-21 | 1997-02-21 | 双方向転送型記憶装置及びメモリの入出力制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19980069917A KR19980069917A (ko) | 1998-10-26 |

| KR100262434B1 true KR100262434B1 (ko) | 2000-08-01 |

Family

ID=12504406

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970043250A Expired - Fee Related KR100262434B1 (ko) | 1997-02-21 | 1997-08-29 | 쌍방향 전송형 기억장치 및 메모리의 입출력 제어방법 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6067605A (enExample) |

| JP (1) | JPH10241354A (enExample) |

| KR (1) | KR100262434B1 (enExample) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4627823B2 (ja) * | 1999-06-25 | 2011-02-09 | 三洋電機株式会社 | 表示装置の制御回路 |

| CN1860520B (zh) * | 2003-05-20 | 2011-07-06 | 辛迪安特公司 | 数字底板 |

| US10690072B2 (en) | 2016-10-19 | 2020-06-23 | Ford Global Technologies, Llc | Method and system for catalytic conversion |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5958689A (ja) * | 1982-09-28 | 1984-04-04 | Fujitsu Ltd | 半導体記憶装置 |

| US4665482A (en) * | 1983-06-13 | 1987-05-12 | Honeywell Information Systems Inc. | Data multiplex control facility |

| JPH04248729A (ja) * | 1991-02-05 | 1992-09-04 | Fujitsu Ltd | Atm交換機 |

| KR0134177B1 (ko) * | 1992-03-24 | 1998-04-22 | Toshiba Kk | 가변장 부호의 기록 재생 장치 |

| US5442282A (en) * | 1992-07-02 | 1995-08-15 | Lsi Logic Corporation | Testing and exercising individual, unsingulated dies on a wafer |

| JPH06224933A (ja) * | 1993-01-22 | 1994-08-12 | Toshiba Corp | バッファメモリ装置 |

-

1997

- 1997-02-21 JP JP9037683A patent/JPH10241354A/ja active Pending

- 1997-06-13 US US08/876,048 patent/US6067605A/en not_active Expired - Lifetime

- 1997-08-29 KR KR1019970043250A patent/KR100262434B1/ko not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US6067605A (en) | 2000-05-23 |

| JPH10241354A (ja) | 1998-09-11 |

| KR19980069917A (ko) | 1998-10-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100915554B1 (ko) | 반도체기억장치 | |

| US5416749A (en) | Data retrieval from sequential-access memory device | |

| US4521874A (en) | Random access memory device | |

| KR100307056B1 (ko) | 양방향 시프트 레지스터, 상기 양방향 시프트 레지스터를 구비하는 어드레스 선택 회로 및 상기 어드레스 선택 회로를 구비하는 fifo/lifo 회로 | |

| KR100262434B1 (ko) | 쌍방향 전송형 기억장치 및 메모리의 입출력 제어방법 | |

| US7051153B1 (en) | Memory array operating as a shift register | |

| US6738792B1 (en) | Parallel mask generator | |

| KR100840030B1 (ko) | 프로그래머블 논리 회로 | |

| EP1311945A1 (en) | A configurable register file with multi-range shift register support | |

| KR100257060B1 (ko) | 파이프라인 동작형 메모리 시스템 | |

| US5621337A (en) | Iterative logic circuit | |

| JP3710586B2 (ja) | 誤り訂正装置 | |

| KR19980071812A (ko) | N개의 세트들의 비트들 중 m개의 세트들의 비트들을 교체하기 위한 인터페이싱 장치, 제어부 및 논리 셀 | |

| KR100489356B1 (ko) | 단일 스테이지의 멀티플렉서를 가진 메모리 장치의 데이터경로 회로 | |

| JPH04168699A (ja) | 半導体集積回路 | |

| EP0862348A1 (en) | Interfacing device to extract M sets of bits out of N sets of bits, control unit and logical cell | |

| JP3837136B2 (ja) | プログラマブル論理回路 | |

| KR20010078351A (ko) | 입력 회로 및 그 입력 회로를 이용하는 반도체 장치 | |

| KR0164819B1 (ko) | 반도체 메모리장치의 블럭라이트 제어회로 및 블럭라이트 제어방법 | |

| JPH07146815A (ja) | メモリ回路およびデータ演算処理装置ならびに記憶制御装置 | |

| KR100557933B1 (ko) | 버스 효율 향상을 위한 라이트 버퍼의 구조 | |

| JP3455828B2 (ja) | ビットシフト回路 | |

| JP2791763B2 (ja) | 演算装置 | |

| JP2005057451A (ja) | プログラマブル論理回路 | |

| JP2005092412A (ja) | Fifo回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 6 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 7 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| FPAY | Annual fee payment |

Payment date: 20070424 Year of fee payment: 8 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 8 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20080503 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20080503 |