JP7548232B2 - 炭化珪素半導体装置の製造方法及び炭化珪素半導体装置 - Google Patents

炭化珪素半導体装置の製造方法及び炭化珪素半導体装置 Download PDFInfo

- Publication number

- JP7548232B2 JP7548232B2 JP2021533082A JP2021533082A JP7548232B2 JP 7548232 B2 JP7548232 B2 JP 7548232B2 JP 2021533082 A JP2021533082 A JP 2021533082A JP 2021533082 A JP2021533082 A JP 2021533082A JP 7548232 B2 JP7548232 B2 JP 7548232B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- silicon carbide

- contact hole

- semiconductor device

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02373—Group 14 semiconducting materials

- H01L21/02378—Silicon carbide

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

- H01L21/31116—Etching inorganic layers by chemical means by dry-etching

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0291—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/83—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge

- H10D62/832—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge being Group IV materials comprising two or more elements, e.g. SiGe

- H10D62/8325—Silicon carbide

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

-

- H10D64/0115—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/23—Electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. sources, drains, anodes or cathodes

- H10D64/251—Source or drain electrodes for field-effect devices

- H10D64/252—Source or drain electrodes for field-effect devices for vertical or pseudo-vertical devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/62—Electrodes ohmically coupled to a semiconductor

-

- H10P50/667—

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Inorganic Chemistry (AREA)

- General Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Materials Engineering (AREA)

- Electrodes Of Semiconductors (AREA)

Description

炭化珪素基板は、Siの他にC(炭素)が含まれているため、炭化珪素に含まれるSiがNiとの合金化に用いられると、未反応のCが生じ、この未反応のCが合金化されたオーミック電極の表面等に析出する場合がある。このように、オーミック電極の表面にCが析出すると、オーミック電極の上に、金属配線層を形成した際に、信頼性の低下等を招くおそれがある。

本開示によれば、炭化珪素基板の表面にオーミック電極を形成する際に、炭素がオーミック電極の表面に析出することを抑制できる。

最初に本開示の実施態様を列記して説明する。以下の説明では、同一または対応する要素には同一の符号を付し、それらについて同じ説明は繰り返さない。

以下、本開示の一実施形態について詳細に説明するが、本実施形態はこれらに限定されるものではない。

最初に、炭化珪素半導体装置の製造方法において、炭化珪素基板の表面にオーミック電極を形成する工程について説明する。炭化珪素基板の表面に、オーミック電極を形成する際には、炭化珪素基板の表面に、スパッタリングによりNi膜を形成した後、ウェットエッチング等により、不要なNi膜を除去する。この後、加熱することにより、炭化珪素基板に含まれるSiとNiとを合金化させて、オーミック電極となるニッケルシリサイド膜を形成する。この際、Niとの合金化のために炭化珪素基板の表面のSiが奪われるため、未反応のCがニッケルシリサイド膜の表面に析出する。この後、スパッタリングによりAl膜を形成し配線層を形成した場合、オーミック電極となるニッケルシリサイド膜の表面にCが析出していると、Al膜が剥がれやすいため、信頼性の低下を招く。

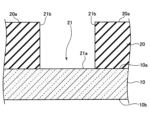

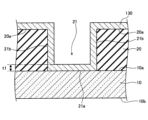

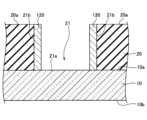

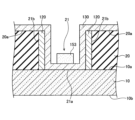

次に、第1の実施形態における半導体装置の製造方法について、図6から図14に基づき説明する。図6は、本開示の第1の実施形態の半導体装置の製造方法のフローチャートである。図7~図14は、本開示の第1の実施形態の半導体装置の製造方法の工程図である。

次に、本実施形態の変形例について説明する。

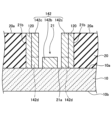

次に、第1の実施形態における半導体装置の一例について説明する。本実施形態における半導体装置は、図20に示されるように、例えば、縦型MOSFET(Metal Oxide Semiconductor Field Effect Transistor)である。具体的には、本実施形態における半導体装置は、炭化珪素基板10と、電極層142と、配線層70と、ゲート絶縁膜25と、ゲート電極71とを有し、ゲート電極71は、層間絶縁膜となる絶縁膜20に覆われている。炭化珪素基板10は、第1のn層11、第2のn層12、pボディ層13、nソース領域14、p領域18を有する。第1のn層11及びnソース領域14は、第2のn層12よりも多く不純物元素がドープされている。p領域18は、pボディ層13よりも多くの不純物元素がドープされている。

次に、第2の実施形態における半導体装置の製造方法について、図21から図27に基づき説明する。

本変形例では、上記の図21に示す工程において、図28に示すように、TiN膜120をコンタクトホール21の側面21bにのみに形成してもよい。この後、図29に示すように、TiN膜120、コンタクトホール21の底面21a及び絶縁膜20を覆うSi膜130をスパッタリングにより形成する。この後、図30に示すように、コンタクトホール21の底面21aよりも狭い領域のSi膜130の上に、レジストパターン153を形成し、レジストパターン153の形成されていない領域のSi膜130を除去する。この後、上記と同様の工程(ステップS5~S9)を行うことにより、図31に示されるように、コンタクトホール21の底面21aにおいて、第1の電極142bと第2の電極142cとが互いから離れて形成される。

10a 一方の主面

10b 他方の主面

11 第1のn層

12 第2のn層

13 pボディ層

14 nソース領域

18 p領域

20 絶縁膜

20a 上面

21 コンタクトホール

21a 底面

21b 側面

25 ゲート絶縁膜

30 TiN膜

30a 開口部

40 Ni膜

41 反応前駆体層

41a オーミック電極

70 配線層

71 ゲート電極

72 ドレイン電極

120 TiN膜

130 Si膜

140 Ni膜

141 反応前駆体層

142 電極層

142a オーミック領域

142b 第1の電極

142c 第2の電極

142d オーミック領域

151、152、153 レジストパターン

Claims (10)

- 炭化珪素基板を準備する工程と、

前記炭化珪素基板の一方の主面に絶縁膜を形成する工程と、

前記絶縁膜にコンタクトホールを形成し、前記コンタクトホールの底面において、前記炭化珪素基板の一方の主面を露出させる工程と、

前記コンタクトホールの底面の上にSi膜を形成する工程と、

前記Si膜の上にNi膜を形成する工程と、

前記Ni膜を形成する工程の後、NiとSiとが反応する第1の温度で第1の熱処理を行う工程と、

前記第1の熱処理の後、ウェットエッチングにより、前記Ni膜のうち前記Si膜と反応していない未反応部を除去する工程と、

前記未反応部を除去する工程の後、前記第1の温度よりも高い第2の温度で第2の熱処理を行う工程と、

を有する炭化珪素半導体装置の製造方法。 - 前記コンタクトホールの底面の上にSi膜を形成する工程は、

前記コンタクトホールの底面及び側面と、前記絶縁膜の上面とに第1Si膜を形成する工程と、

前記第1Si膜を形成する工程の後、少なくとも前記絶縁膜の上面の前記第1Si膜をドライエッチングにより除去する工程と、

を有する請求項1に記載の炭化珪素半導体装置の製造方法。 - 前記第1の温度は、200℃以上、400℃以下である請求項1または請求項2に記載の炭化珪素半導体装置の製造方法。

- 前記第2の温度は、800℃以上、1100℃以下である請求項1から請求項3のいずれか一項に記載の炭化珪素半導体装置の製造方法。

- 前記コンタクトホールの底面における前記Si膜の膜厚は、5nm以上、100nm以下である請求項1から請求項4のいずれか一項に記載の炭化珪素半導体装置の製造方法。

- 前記コンタクトホールの底面における前記Ni膜の膜厚は、5nm以上、100nm以下である請求項1から請求項5のいずれか一項に記載の炭化珪素半導体装置の製造方法。

- 前記Si膜は、前記コンタクトホールの側面にも形成されている請求項1から請求項6のいずれか一項に記載の炭化珪素半導体装置の製造方法。

- 前記Si膜の上に前記Ni膜が形成された状態の前記コンタクトホールの底面において、前記Si膜に含まれる厚さ方向に積算される単位面積当たりのSi原子の数をNSi、前記Ni膜に含まれる厚さ方向に積算される単位面積当たりのNi原子の数をNNiとしたとき、NNi≧NSi/2の関係が成り立つ請求項1から請求項7のいずれか一項に記載の炭化珪素半導体装置の製造方法。

- 主面を有する炭化珪素基板と、

前記炭化珪素基板の主面上に設けられた絶縁膜と、

前記絶縁膜に設けられたコンタクトホールと、

前記コンタクトホールの底面の一部に設けられ、前記炭化珪素基板と接触している第1の電極と、

前記コンタクトホールの側面に、前記第1の電極から離れて設けられた第2の電極と、

を有し、

前記第1の電極は、SiとNiとを含み、前記炭化珪素基板とオーミックコンタクトしている炭化珪素半導体装置。 - 前記コンタクトホールの底面において、前記第1の電極と前記第2の電極との間の距離は、0.1μm以上、1μm以下である請求項9に記載の炭化珪素半導体装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019131803 | 2019-07-17 | ||

| JP2019131803 | 2019-07-17 | ||

| PCT/JP2020/027413 WO2021010405A1 (ja) | 2019-07-17 | 2020-07-14 | 炭化珪素半導体装置の製造方法及び炭化珪素半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2021010405A1 JPWO2021010405A1 (ja) | 2021-01-21 |

| JP7548232B2 true JP7548232B2 (ja) | 2024-09-10 |

Family

ID=74210901

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021533082A Active JP7548232B2 (ja) | 2019-07-17 | 2020-07-14 | 炭化珪素半導体装置の製造方法及び炭化珪素半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US12100739B2 (ja) |

| JP (1) | JP7548232B2 (ja) |

| WO (1) | WO2021010405A1 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7647216B2 (ja) * | 2021-03-22 | 2025-03-18 | 住友電気工業株式会社 | 炭化珪素半導体装置の製造方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005276978A (ja) | 2004-03-24 | 2005-10-06 | Nissan Motor Co Ltd | オーミック電極構造体の製造方法、オーミック電極構造体、半導体装置の製造方法および半導体装置 |

| JP2010103229A (ja) | 2008-10-22 | 2010-05-06 | Sumitomo Electric Ind Ltd | 炭化珪素半導体装置およびその製造方法 |

| JP2013058587A (ja) | 2011-09-08 | 2013-03-28 | Seiko Epson Corp | 半導体素子の製造方法 |

| JP2018050008A (ja) | 2016-09-23 | 2018-03-29 | トヨタ自動車株式会社 | 半導体装置の製造方法 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3953696B2 (ja) | 1999-12-24 | 2007-08-08 | 新日本無線株式会社 | 半導体装置の製造方法 |

| JP2003158259A (ja) | 2001-09-07 | 2003-05-30 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP5418466B2 (ja) | 2010-11-01 | 2014-02-19 | 住友電気工業株式会社 | 半導体装置およびその製造方法 |

| JP7047250B2 (ja) | 2016-03-16 | 2022-04-05 | 富士電機株式会社 | 炭化珪素半導体素子の製造方法 |

| JP6705231B2 (ja) | 2016-03-16 | 2020-06-03 | 富士電機株式会社 | 炭化珪素半導体装置および炭化珪素半導体装置の製造方法 |

| JP7006118B2 (ja) | 2017-10-17 | 2022-01-24 | 富士電機株式会社 | 半導体装置及びその製造方法 |

| WO2021010382A1 (ja) * | 2019-07-17 | 2021-01-21 | 住友電気工業株式会社 | 炭化珪素半導体装置の製造方法及び炭化珪素半導体装置 |

-

2020

- 2020-07-14 JP JP2021533082A patent/JP7548232B2/ja active Active

- 2020-07-14 US US17/595,007 patent/US12100739B2/en active Active

- 2020-07-14 WO PCT/JP2020/027413 patent/WO2021010405A1/ja not_active Ceased

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005276978A (ja) | 2004-03-24 | 2005-10-06 | Nissan Motor Co Ltd | オーミック電極構造体の製造方法、オーミック電極構造体、半導体装置の製造方法および半導体装置 |

| JP2010103229A (ja) | 2008-10-22 | 2010-05-06 | Sumitomo Electric Ind Ltd | 炭化珪素半導体装置およびその製造方法 |

| JP2013058587A (ja) | 2011-09-08 | 2013-03-28 | Seiko Epson Corp | 半導体素子の製造方法 |

| JP2018050008A (ja) | 2016-09-23 | 2018-03-29 | トヨタ自動車株式会社 | 半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US12100739B2 (en) | 2024-09-24 |

| US20220208971A1 (en) | 2022-06-30 |

| WO2021010405A1 (ja) | 2021-01-21 |

| JPWO2021010405A1 (ja) | 2021-01-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5525940B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| US7829416B2 (en) | Silicon carbide semiconductor device and method for producing the same | |

| JPS584924A (ja) | 半導体装置の電極形成方法 | |

| JP2003324197A (ja) | 半導体装置およびその製造方法 | |

| JP6178106B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| US9704743B2 (en) | Method for manufacturing silicon carbide semiconductor device | |

| US20170271486A1 (en) | Silicon carbide semiconductor device and method of manufacturing silicon carbide semiconductor device | |

| JP7548232B2 (ja) | 炭化珪素半導体装置の製造方法及び炭化珪素半導体装置 | |

| WO2015045627A1 (ja) | 炭化珪素半導体装置の製造方法 | |

| JP7459875B2 (ja) | 炭化珪素半導体装置の製造方法及び炭化珪素半導体装置 | |

| JPWO2008117430A1 (ja) | 半導体装置の製造方法、半導体装置 | |

| WO2016169162A1 (zh) | 一种制作阵列基板的方法及其阵列基板和显示装置 | |

| JP6395299B2 (ja) | 炭化珪素半導体素子及び炭化珪素半導体素子の製造方法 | |

| JP5561343B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| JP7647216B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| JP5014749B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| JP2000252472A (ja) | 薄膜半導体素子及びその製造方法 | |

| US20230009078A1 (en) | Method of manufacturing silicon carbide semiconductor device | |

| JPH0126172B2 (ja) | ||

| WO2020004067A1 (ja) | 炭化珪素半導体装置 | |

| CN118173587B (zh) | 一种半导体器件及其制作方法 | |

| JP5037095B2 (ja) | 炭化珪素半導体装置及び炭化珪素半導体装置の製造方法 | |

| JPS5961147A (ja) | 半導体装置の製造方法 | |

| JPH09162392A (ja) | 半導体装置 | |

| KR100659116B1 (ko) | 박막트랜지스터의 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230322 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240416 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20240730 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20240812 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7548232 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |