JP7307662B2 - 半導体発光素子および半導体発光素子の製造方法 - Google Patents

半導体発光素子および半導体発光素子の製造方法 Download PDFInfo

- Publication number

- JP7307662B2 JP7307662B2 JP2019198541A JP2019198541A JP7307662B2 JP 7307662 B2 JP7307662 B2 JP 7307662B2 JP 2019198541 A JP2019198541 A JP 2019198541A JP 2019198541 A JP2019198541 A JP 2019198541A JP 7307662 B2 JP7307662 B2 JP 7307662B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- electrode

- protective layer

- type semiconductor

- opening

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

- H10H20/011—Manufacture or treatment of bodies, e.g. forming semiconductor layers

- H10H20/013—Manufacture or treatment of bodies, e.g. forming semiconductor layers having light-emitting regions comprising only Group III-V materials

- H10H20/0137—Manufacture or treatment of bodies, e.g. forming semiconductor layers having light-emitting regions comprising only Group III-V materials the light-emitting regions comprising nitride materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/822—Materials of the light-emitting regions

- H10H20/824—Materials of the light-emitting regions comprising only Group III-V materials, e.g. GaP

- H10H20/825—Materials of the light-emitting regions comprising only Group III-V materials, e.g. GaP containing nitrogen, e.g. GaN

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/831—Electrodes characterised by their shape

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/832—Electrodes characterised by their material

- H10H20/835—Reflective materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/84—Coatings, e.g. passivation layers or antireflective coatings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

- H10H20/032—Manufacture or treatment of electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

- H10H20/034—Manufacture or treatment of coatings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/816—Bodies having carrier transport control structures, e.g. highly-doped semiconductor layers or current-blocking structures

- H10H20/8162—Current-blocking structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/819—Bodies characterised by their shape, e.g. curved or truncated substrates

- H10H20/82—Roughened surfaces, e.g. at the interface between epitaxial layers

Landscapes

- Led Devices (AREA)

- Led Device Packages (AREA)

Description

Claims (9)

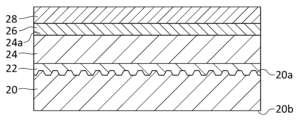

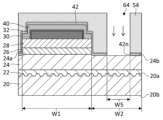

- n型AlGaN系半導体材料から構成されるn型半導体層と、

前記n型半導体層の第1上面に設けられ、AlGaN系半導体材料から構成される活性層と、

前記n型半導体層の第2上面と接触して設けられるn側コンタクト電極と、

前記活性層上に設けられるp型半導体層と、

前記p型半導体層の上面と接触し、Rhから構成されるp側コンタクト電極と、

前記p側コンタクト電極の上面および側面を被覆し、TiNから構成されるp側電極被覆層と、

前記p側電極被覆層の上面の一部に設けられる第1p側パッド開口を有し、前記第1p側パッド開口とは異なる箇所において前記p側電極被覆層の上面および側面を被覆し、SiO2またはSiONから構成される第1保護層と、

前記第1p側パッド開口と連通する第2p側パッド開口を有し、前記第2p側パッド開口とは異なる箇所において前記第1保護層、前記p型半導体層の側面および前記活性層の側面を被覆し、Al2O3から構成される第2保護層と、

前記第1p側パッド開口および前記第2p側パッド開口において前記p側電極被覆層と接触するp側パッド電極と、を備えることを特徴とする半導体発光素子。 - 前記第2保護層は、前記n型半導体層の前記第2上面の一部に設けられるn側コンタクト開口を有し、前記n側コンタクト開口とは異なる箇所にて前記n型半導体層の前記第2上面をさらに被覆し、

前記n側コンタクト電極は、前記n側コンタクト開口において前記n型半導体層の前記第2上面と接触し、前記n側コンタクト開口の外縁において前記第2保護層の上に重なることを特徴とする請求項1に記載の半導体発光素子。 - 前記p側電極被覆層は、前記p型半導体層と接触するように設けられ、

前記第1保護層は、前記p側コンタクト電極および前記p側電極被覆層が設けられる箇所とは異なる箇所において前記p型半導体層の前記上面をさらに被覆することを特徴とする請求項1または2に記載の半導体発光素子。 - 前記p側コンタクト電極上に設けられる第3p側パッド開口および前記n側コンタクト電極上に設けられるn側パッド開口を有し、前記第3p側パッド開口とは異なる箇所において前記第2保護層を被覆するとともに、前記n側パッド開口とは異なる箇所において前記n側コンタクト電極を被覆し、SiO2から構成される第3保護層と、

前記n側パッド開口に設けられるn側パッド電極と、をさらに備え、

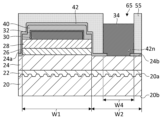

前記p側パッド電極および前記n側パッド電極は、前記第3保護層の上に重なることを特徴とする請求項1から3のいずれか一項に記載の半導体発光素子。 - 前記n側コンタクト電極の上面および側面を被覆し、前記第2保護層と接触するTiNで構成されるn側電極被覆層をさらに備え、

前記第3保護層は、前記n側パッド開口とは異なる箇所において前記n側電極被覆層を被覆し、

前記n側パッド電極は、前記n側パッド開口において前記n側電極被覆層と接触することを特徴とする請求項4に記載の半導体発光素子。 - 前記第1保護層は、前記活性層および前記n型半導体層と接触しない、請求項1から5のいずれか一項に記載の半導体発光素子。

- n型AlGaN系半導体材料から構成されるn型半導体層の第1上面にAlGaN系半導体材料から構成される活性層を形成する工程と、

前記活性層上にp型半導体層を形成する工程と、

前記p型半導体層の上面と接触し、Rhから構成されるp側コンタクト電極を形成する工程と、

前記p側コンタクト電極を被覆し、TiNから構成されるp側電極被覆層を形成する工程と、

前記p型半導体層の上面を被覆するとともに、前記p側電極被覆層の上面および側面を被覆し、SiO2またはSiONから構成される第1保護層を形成する工程と、

前記p側コンタクト電極が形成された領域とは異なる領域において前記第1保護層、前記p型半導体層および前記活性層を除去し、前記n型半導体層の第2上面を露出させる工程と、

前記第1保護層、前記p型半導体層の側面および前記活性層の側面を被覆し、Al2O3から構成される第2保護層を形成する工程と、

前記n型半導体層の前記第2上面と接触するn側コンタクト電極を形成する工程と、

前記p側コンタクト電極上の前記第2保護層を貫通する第2p側パッド開口を形成する工程と、

前記p側コンタクト電極上の前記第1保護層を貫通し、前記第2p側パッド開口と連通する第1p側パッド開口を形成する工程と、

前記第1p側パッド開口にて露出する前記p側電極被覆層に接触するp側パッド電極を形成する工程と、を備えることを特徴とする半導体発光素子の製造方法。 - 前記第2保護層は、前記n型半導体層の前記第2上面をさらに被覆するよう形成され、

前記n型半導体層の前記第2上面の一部に設けられる前記第2保護層を貫通するn側コンタクト開口を形成する工程をさらに備え、

前記n側コンタクト電極は、前記n側コンタクト開口の外縁において前記第2保護層の上に重なるように形成されることを特徴とする請求項7に記載の半導体発光素子の製造方法。 - 前記第1p側パッド開口の形成後、前記第1p側パッド開口において露出する前記p側電極被覆層、前記第2保護層および前記n側コンタクト電極を被覆し、SiO2で構成される第3保護層を形成する工程と、

前記p側コンタクト電極上の前記第3保護層を貫通する第3p側パッド開口を形成するとともに、前記n側コンタクト電極上の前記第3保護層を貫通するn側パッド開口を形成する工程と、

前記n側パッド開口にn側パッド電極を形成する工程と、をさらに備え、

前記p側パッド電極は、前記第3p側パッド開口の形成後に形成され、

前記p側パッド電極および前記n側パッド電極は、前記第3保護層の上に重なることを特徴とする請求項7または8に記載の半導体発光素子の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019198541A JP7307662B2 (ja) | 2019-10-31 | 2019-10-31 | 半導体発光素子および半導体発光素子の製造方法 |

| US17/012,973 US11626540B2 (en) | 2019-10-31 | 2020-09-04 | Semiconductor light-emitting element and method of manufacturing semiconductor light-emitting element |

| TW109131211A TW202133463A (zh) | 2019-10-31 | 2020-09-11 | 半導體發光元件以及半導體發光元件的製造方法 |

| US18/118,497 US12278312B2 (en) | 2019-10-31 | 2023-03-07 | Semiconductor light-emitting element and method of manufacturing semiconductor light-emitting element |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019198541A JP7307662B2 (ja) | 2019-10-31 | 2019-10-31 | 半導体発光素子および半導体発光素子の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2021072376A JP2021072376A (ja) | 2021-05-06 |

| JP7307662B2 true JP7307662B2 (ja) | 2023-07-12 |

Family

ID=75687767

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019198541A Active JP7307662B2 (ja) | 2019-10-31 | 2019-10-31 | 半導体発光素子および半導体発光素子の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US11626540B2 (ja) |

| JP (1) | JP7307662B2 (ja) |

| TW (1) | TW202133463A (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6839320B1 (ja) | 2020-05-13 | 2021-03-03 | 日機装株式会社 | 半導体発光素子および半導体発光素子の製造方法 |

| JP6892538B1 (ja) * | 2020-05-13 | 2021-06-23 | 日機装株式会社 | 半導体発光素子および半導体発光素子の製造方法 |

| WO2022050510A1 (ko) * | 2020-09-04 | 2022-03-10 | 주식회사 포톤웨이브 | 자외선 발광소자 및 이를 포함하는 발광소자 패키지 |

| JP2022172792A (ja) * | 2021-05-07 | 2022-11-17 | 日機装株式会社 | 窒化物半導体発光素子 |

| JP7345524B2 (ja) * | 2021-07-30 | 2023-09-15 | 日機装株式会社 | 半導体発光素子および半導体発光素子の製造方法 |

| JP7344936B2 (ja) | 2021-07-30 | 2023-09-14 | 日機装株式会社 | 半導体発光素子および半導体発光素子の製造方法 |

| JP7339994B2 (ja) * | 2021-11-12 | 2023-09-06 | 日機装株式会社 | 半導体発光素子および半導体発光素子の製造方法 |

| CN114725262A (zh) * | 2021-11-26 | 2022-07-08 | 泉州三安半导体科技有限公司 | 一种发光二极管芯片、发光装置 |

| CN114141922A (zh) * | 2021-12-01 | 2022-03-04 | 聚灿光电科技(宿迁)有限公司 | 一种led芯片及其制造方法 |

| JP7296513B1 (ja) | 2021-12-07 | 2023-06-22 | Dowaエレクトロニクス株式会社 | 紫外発光素子及びその製造方法 |

| WO2023106268A1 (ja) * | 2021-12-07 | 2023-06-15 | Dowaエレクトロニクス株式会社 | 紫外発光素子及びその製造方法 |

| JP7269414B1 (ja) | 2022-04-28 | 2023-05-08 | 日機装株式会社 | 半導体発光素子および半導体発光素子の製造方法 |

| CN119029106A (zh) * | 2024-10-28 | 2024-11-26 | 江西科技师范大学 | 一种led芯片制备方法及led芯片 |

Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004274042A (ja) | 2003-02-19 | 2004-09-30 | Nichia Chem Ind Ltd | 窒化物半導体素子 |

| JP2005302747A (ja) | 2004-03-29 | 2005-10-27 | Stanley Electric Co Ltd | 半導体発光素子 |

| JP2009194367A (ja) | 2008-01-16 | 2009-08-27 | Rohm Co Ltd | 半導体発光素子およびその製造方法 |

| JP2011138820A (ja) | 2009-12-25 | 2011-07-14 | Nichia Corp | 発光素子 |

| JP2012151261A (ja) | 2011-01-19 | 2012-08-09 | Mitsubishi Heavy Ind Ltd | 半導体発光素子、半導体発光素子の保護膜及びその作製方法 |

| US20140291714A1 (en) | 2012-07-18 | 2014-10-02 | Semicon Light Co., Ltd. | Semiconductor Light Emitting Device |

| JP2016208012A (ja) | 2015-04-27 | 2016-12-08 | 日亜化学工業株式会社 | 発光装置 |

| JP2017208400A (ja) | 2016-05-17 | 2017-11-24 | ローム株式会社 | 半導体発光素子 |

| CN108123018A (zh) | 2017-12-18 | 2018-06-05 | 湘能华磊光电股份有限公司 | 一种氮化镓基倒装结构发光器件及其制备方法 |

| US20190058088A1 (en) | 2015-09-30 | 2019-02-21 | Lg Innotek Co., Ltd. | Light emitting device |

| JP6570702B1 (ja) | 2018-05-29 | 2019-09-04 | 日機装株式会社 | 半導体発光素子および半導体発光素子の製造方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100671924B1 (ko) * | 2003-02-19 | 2007-01-24 | 니치아 카가쿠 고교 가부시키가이샤 | 질화물 반도체 소자 |

| CN102124574B (zh) | 2008-06-16 | 2013-07-17 | 丰田合成株式会社 | 半导体发光元件、其电极及制造方法以及灯 |

| TW201331066A (zh) | 2011-10-10 | 2013-08-01 | 普羅泰拉公司 | 在固定路線應用程式下用於電池壽命最大化的系統及方法 |

| JP5857786B2 (ja) | 2012-02-21 | 2016-02-10 | 日亜化学工業株式会社 | 半導体発光素子の製造方法 |

-

2019

- 2019-10-31 JP JP2019198541A patent/JP7307662B2/ja active Active

-

2020

- 2020-09-04 US US17/012,973 patent/US11626540B2/en active Active

- 2020-09-11 TW TW109131211A patent/TW202133463A/zh unknown

-

2023

- 2023-03-07 US US18/118,497 patent/US12278312B2/en active Active

Patent Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004274042A (ja) | 2003-02-19 | 2004-09-30 | Nichia Chem Ind Ltd | 窒化物半導体素子 |

| JP2005302747A (ja) | 2004-03-29 | 2005-10-27 | Stanley Electric Co Ltd | 半導体発光素子 |

| JP2009194367A (ja) | 2008-01-16 | 2009-08-27 | Rohm Co Ltd | 半導体発光素子およびその製造方法 |

| JP2011138820A (ja) | 2009-12-25 | 2011-07-14 | Nichia Corp | 発光素子 |

| JP2012151261A (ja) | 2011-01-19 | 2012-08-09 | Mitsubishi Heavy Ind Ltd | 半導体発光素子、半導体発光素子の保護膜及びその作製方法 |

| US20140291714A1 (en) | 2012-07-18 | 2014-10-02 | Semicon Light Co., Ltd. | Semiconductor Light Emitting Device |

| JP2016208012A (ja) | 2015-04-27 | 2016-12-08 | 日亜化学工業株式会社 | 発光装置 |

| US20190058088A1 (en) | 2015-09-30 | 2019-02-21 | Lg Innotek Co., Ltd. | Light emitting device |

| JP2017208400A (ja) | 2016-05-17 | 2017-11-24 | ローム株式会社 | 半導体発光素子 |

| CN108123018A (zh) | 2017-12-18 | 2018-06-05 | 湘能华磊光电股份有限公司 | 一种氮化镓基倒装结构发光器件及其制备方法 |

| JP6570702B1 (ja) | 2018-05-29 | 2019-09-04 | 日機装株式会社 | 半導体発光素子および半導体発光素子の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20230223499A1 (en) | 2023-07-13 |

| JP2021072376A (ja) | 2021-05-06 |

| TW202133463A (zh) | 2021-09-01 |

| US12278312B2 (en) | 2025-04-15 |

| US20210135058A1 (en) | 2021-05-06 |

| US11626540B2 (en) | 2023-04-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7307662B2 (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| TWI753536B (zh) | 半導體發光元件以及半導體發光元件的製造方法 | |

| CN113675309B (zh) | 半导体发光元件及半导体发光元件的制造方法 | |

| CN113675310B (zh) | 半导体发光元件及半导体发光元件的制造方法 | |

| JP6995227B1 (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| JP2020205401A (ja) | 半導体発光素子 | |

| JP7146562B2 (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| JP7146589B2 (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| TW202005110A (zh) | 半導體發光元件以及半導體發光元件的製造方法 | |

| JP2023020627A (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| JP7217819B1 (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| JP7344937B2 (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| JP6837593B1 (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| TW202315159A (zh) | 半導體發光元件以及半導體發光元件的製造方法 | |

| TWI832544B (zh) | 半導體發光元件以及半導體發光元件的製造方法 | |

| JP7296001B2 (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| JP7295924B2 (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| JP2024054528A (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| JP7296002B2 (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| JP2025169601A (ja) | 半導体発光素子および半導体発光素子の製造方法 | |

| JP2024054527A (ja) | 半導体発光素子および半導体発光素子の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20220517 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20221216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20230124 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230324 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230620 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230630 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7307662 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |