JP6685884B2 - 半導体モジュール - Google Patents

半導体モジュール Download PDFInfo

- Publication number

- JP6685884B2 JP6685884B2 JP2016231244A JP2016231244A JP6685884B2 JP 6685884 B2 JP6685884 B2 JP 6685884B2 JP 2016231244 A JP2016231244 A JP 2016231244A JP 2016231244 A JP2016231244 A JP 2016231244A JP 6685884 B2 JP6685884 B2 JP 6685884B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor package

- semiconductor

- wiring

- side conductor

- igbt

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/36—Selection of materials, or shaping, to facilitate cooling or heating, e.g. heatsinks

- H01L23/373—Cooling facilitated by selection of materials for the device or materials for thermal expansion adaptation, e.g. carbon

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/42—Fillings or auxiliary members in containers or encapsulations selected or arranged to facilitate heating or cooling

- H01L23/433—Auxiliary members in containers characterised by their shape, e.g. pistons

- H01L23/4334—Auxiliary members in encapsulations

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49541—Geometry of the lead-frame

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49568—Lead-frames or other flat leads specifically adapted to facilitate heat dissipation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

- H01L23/49844—Geometry or layout for devices being provided for in H01L29/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5226—Via connections in a multilevel interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53228—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being copper

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5386—Geometry or layout of the interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/34—Strap connectors, e.g. copper straps for grounding power devices; Manufacturing methods related thereto

- H01L24/39—Structure, shape, material or disposition of the strap connectors after the connecting process

- H01L24/40—Structure, shape, material or disposition of the strap connectors after the connecting process of an individual strap connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/07—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L29/00

- H01L25/074—Stacked arrangements of non-apertured devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/10—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers

- H01L25/11—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers the devices being of a type provided for in group H01L29/00

- H01L25/115—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers the devices being of a type provided for in group H01L29/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/2612—Auxiliary members for layer connectors, e.g. spacers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/291—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/29101—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of less than 400°C

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/29198—Material with a principal constituent of the material being a combination of two or more materials in the form of a matrix with a filler, i.e. being a hybrid material, e.g. segmented structures, foams

- H01L2224/29298—Fillers

- H01L2224/29299—Base material

- H01L2224/293—Base material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/29338—Base material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/29339—Silver [Ag] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/33—Structure, shape, material or disposition of the layer connectors after the connecting process of a plurality of layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/33—Structure, shape, material or disposition of the layer connectors after the connecting process of a plurality of layer connectors

- H01L2224/331—Disposition

- H01L2224/3318—Disposition being disposed on at least two different sides of the body, e.g. dual array

- H01L2224/33181—On opposite sides of the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/34—Strap connectors, e.g. copper straps for grounding power devices; Manufacturing methods related thereto

- H01L2224/36—Structure, shape, material or disposition of the strap connectors prior to the connecting process

- H01L2224/37—Structure, shape, material or disposition of the strap connectors prior to the connecting process of an individual strap connector

- H01L2224/3754—Coating

- H01L2224/37599—Material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/34—Strap connectors, e.g. copper straps for grounding power devices; Manufacturing methods related thereto

- H01L2224/39—Structure, shape, material or disposition of the strap connectors after the connecting process

- H01L2224/40—Structure, shape, material or disposition of the strap connectors after the connecting process of an individual strap connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/34—Strap connectors, e.g. copper straps for grounding power devices; Manufacturing methods related thereto

- H01L2224/39—Structure, shape, material or disposition of the strap connectors after the connecting process

- H01L2224/40—Structure, shape, material or disposition of the strap connectors after the connecting process of an individual strap connector

- H01L2224/401—Disposition

- H01L2224/40135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/40137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

- H01L2224/40139—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate with an intermediate bond, e.g. continuous strap daisy chain

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73215—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73221—Strap and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/838—Bonding techniques

- H01L2224/83801—Soldering or alloying

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/84—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a strap connector

- H01L2224/848—Bonding techniques

- H01L2224/84801—Soldering or alloying

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/36—Selection of materials, or shaping, to facilitate cooling or heating, e.g. heatsinks

- H01L23/373—Cooling facilitated by selection of materials for the device or materials for thermal expansion adaptation, e.g. carbon

- H01L23/3735—Laminates or multilayers, e.g. direct bond copper ceramic substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49541—Geometry of the lead-frame

- H01L23/49548—Cross section geometry

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49541—Geometry of the lead-frame

- H01L23/49562—Geometry of the lead-frame for devices being provided for in H01L29/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49861—Lead-frames fixed on or encapsulated in insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L24/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/33—Structure, shape, material or disposition of the layer connectors after the connecting process of a plurality of layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/84—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a strap connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/1026—Compound semiconductors

- H01L2924/1027—IV

- H01L2924/10272—Silicon Carbide [SiC]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/1026—Compound semiconductors

- H01L2924/1032—III-V

- H01L2924/1033—Gallium nitride [GaN]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1203—Rectifying Diode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13055—Insulated gate bipolar transistor [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Geometry (AREA)

- Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

Description

ラミック板に半田を介して半導体チップが実装されており、半導体チップを実装したセラ

ミック板は、半田を介して金属ベース基板に実装されていた。このような半導体パワーモ

ジュールは、例えば、セラミック板の線膨張係数を半導体チップの線膨張係数に近付ける

ことで温度サイクル耐量およびパワーサイクル耐量を向上させている。

を半導体チップの下面から金属ベース板へ放熱するのみであった。

る絶縁層と、を有する基板と、前記基板上に設けられた第6配線と、前記第6配線上に設

けられ、上部および下部において放熱する第1半導体パッケージと、前記第6配線上に、

前記第1半導体パッケージに対して上下反転して設けられ、上部および下部において放熱

する第2半導体パッケージと、前記第1半導体パッケージ上に設けられた第4配線と、前

記第2半導体パッケージ上に設けられた第5配線と、を備え、前記第1半導体パッケージ

と前記第2半導体パッケージは前記第6配線を介して、直列接続される半導体モジュール

。

モジュールの特徴的な構成および動作を中心に説明するが、半導体モジュールには以下の

説明で省略した構成および動作が存在しうる。これらの省略した構成および動作も本実施

形態の範囲に含まれるものである。

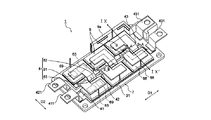

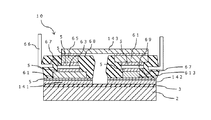

図1は、第1の実施形態を示す半導体モジュール1の斜視図である。図2Aは、第1の

実施形態の半導体モジュール1を示す図1の模式的なII_A−II_A断面図である。

図2Bは、図1の模式的なII_B−II_B断面図である。半導体モジュール1は、例

えば、風力発電システム、太陽光発電システムおよび電車において、インバータ等の電力

変換装置として用いることができるものである。

層から順に、金属層2と絶縁層3とからなる基板7と、正極側、負極側および出力側の導

体41〜43と、導体41あるいは導体43上に半田層5を介して設けられた半導体パッ

ケージ6と、半導体パッケージ6上に半田層5を介して設けられた第3配線8とを備える

。なお、正極側導体41は、第1配線の一例であり、この場合出力側導体43は第2配線

である。あるいは出力側導体43を第1配線の一例とすると、負極側導体42は第2配線

である。

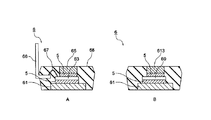

パッケージ6のIV_A−IV_A断面を示している。図4Aに示すように、半導体パッ

ケージ6は、第1の部材61と、半田層5を介して第1の部材61上に設けられたIGB

T(Insulated gate bipolar transistor)63と、半田層5を介してIGBT63上に

設けられた第2の部材65とを備える。半導体パッケージ6は、表面実装型であり、第1

の部材61と第2の部材65はそれぞれ電極を構成する。なお、IGBT63は、第1の

半導体チップの一例であるが、第1の半導体チップとしてMOSFETやダイオード等の

他の半導体チップを用いてもよい。半導体パッケージ6は、リードフレーム66と、半導

体パッケージ63とリードフレーム66とを接続するボンディングワイヤ67と、封止部

材の一例である封止樹脂68とを備える。

体的には、半導体パッケージ6は、第1の部材61と、半田層5を介して第1の部材61

上に設けられたダイオード69と、半田層5を介してダイオード69上に設けられた第4

の部材613とを備える。なお、ダイオード69は、第2の半導体チップの一例であるが

、第2の半導体チップとしてMOSFETやIGBT等の他の半導体チップを用いてもよ

い。

半導体パッケージ63から露出した部分を有している。この露出した部分は、導体41、

43あるいは第3配線8に半田層5を介して接続している。

った枠状のケース9を備える。ケース9は、基板7を支持し、基板7の側部を覆うように

設けられている。なお、図1には、ケース9の一部が図示されている。ケース9の上端9

aは、第3配線8よりも上方に位置する。基板7上のケース9で囲まれた領域は、不図示

の樹脂で封止されている。ケース9の上部は、蓋で覆われていてもよい。

図1に示すように、基板7は、略矩形状を有する。基板7は、方向D1において長く、

方向D1に略垂直な方向D2において短い。以下、D1を、半導体モジュール1の全長方

向と定義し、D2を、半導体モジュール1の幅方向と定義する。

図1の例では、基板7上に、全長方向D1に沿って3列、幅方向D2に沿って2列の計6

つの半導体パッケージ6を配置できる。

ナを含有する場合と比較してコストを削減できる。なお、金属層2は、主成分としてアル

ミニウムを含有してもよい。また、金属層2は、主成分として金属およびセラミック(例

えば、アルミ炭化ケイ素複合材)を含有してもよい。

ている。絶縁層3は、樹脂を含有する。

ルミナ、窒化アルミ、窒化ケイ素および炭化ケイ素などであってもよい。

熱抵抗を低減できる。絶縁層3は、17kV/mm以上の絶縁耐圧を有していてもよい。

金属層2と絶縁層3とで構成された基板7を用いることで、セラミック板を用いる従来の

場合と比較してコストを削減できる。また基板7は放熱の機能を有し、かつ半導体モジュ

ールの支持基板としての役割を果たす。つまり従来の金属ベース基板の機能を兼ね備える

。よって、本実施形態においては、従来用いていた金属ベース基板は不要となる。

図2Aおよび図2Bに示すように、導体41〜43は、いずれも絶縁層3の上面31に

接して設けられており、配線として用いられる。

一端には、正極端子411が接続されている。正極側導体41の幅方向D2の寸法は、半

導体パッケージ6の幅方向D2の寸法と程同一である。正極側導体41上には、全長方向

D1に間隔を空けて3つの半導体パッケージ6が配置されている。

延びている。出力側導体43の一端には、2つの出力端子431が接続されている。出力

側導体43上には、全長方向D1に間隔を空けて3つの半導体パッケージ6が配置されて

いる。出力側導体43上の半導体パッケージ6は、正極側導体41上の半導体パッケージ

6に対向している。

に延びている。負極側導体42の一端には、負極端子421が接続されている。負極側導

体42の幅方向D2の寸法は、正極側導体41および出力側導体43の幅方向D2の寸法

よりも小さい。負極側導体42には、第3配線8が接続されている。

を含有する。よって導体41〜43は、導電性を確保しつつ熱抵抗を低減できる。

(第1の部材61)

正極側導体41上の半導体パッケージ6の第1の部材61と、出力側導体43上の半導

体パッケージ6の第1の部材61とは、ともに基板7に平行な略矩形の板形状を有する。

第1の部材61は、導電性および熱伝導性を有し、例えば、主成分として金属を含有し、

好ましくは、主成分として銅を含有する。

電気的かつ機械的に接続されている。半田層5は、導電性および熱伝導性を有する。なお

、正極側の第1の部材61は、金属を主成分とする材料を介して正極側導体41と電気的

かつ機械的に接続されていてもよい。

電気的かつ機械的に接続されている。なお、出力側の第1の部材61は、金属を主成分と

する材料を介して出力側導体43と電気的かつ機械的に接続されていてもよい。

図2Aおよび図2Bに示すように、IGBT63は、半田層5を介して第1の部材61

と電気的かつ機械的に接続されている。より具体的には、IGBT63の下面には図示し

ないコレクタ電極が設けられており、コレクタ電極は第1の部材61と接続されている。

また、IGBT63の上面には、図示しないエミッタ電極およびゲート電極が設けられて

いる。図4Aに示すように、ボンディングワイヤ67の一端はゲート電極に接続され、他

端は、リードフレーム66に接続されている。

図2A、図2Bおよび図3に示すように、第2の部材65は、基板7に平行な略矩形の

板形状を有する。第2の部材65は、導電性および熱伝導性を有し、主成分として金属を

含有し、好ましくは、主成分として銅を含有する。

。より具体的には、第2の部材65は、IGBT63のエミッタ電極と接続されている。

図2Aおよび図2Bに示すように、ダイオード69は、半田層5で第1の部材61と電

気的かつ機械的に接続されている。ダイオード69の下面には図示しないアノード電極が

設けられており、ダイオード69は、アノード電極において第1の部材61と接続されて

いる。

の板形状を有し、例えば、主成分として金属を含有し、好ましくは、主成分として銅を含

有する。第4の部材613は、半田層5でダイオード69と電気的かつ機械的に接続され

ている。より具体的には、ダイオード69の上面には図示しないカソード電極が設けられ

ており、カソード電極は第4の部材613と接続されている。

する。第1の部材61の少なくとも一部、例えば下面は封止樹脂68から露出し、また、

IGBT63の上部に設けられた第2の部材65の少なくとも一部、例えば上面は封止樹

脂68から露出している。これにより、半導体パッケージ6は、上面および下面において

放熱できる。同様に、第4の部材613の少なくとも一部、例えば上面は封止樹脂68か

ら露出している。なお、封止樹脂68は、トランスファーモールド成形で形成している。

ード69よりも正極端子411側に位置するように金属層2上に配置されている。一方、

出力側導体43上の半導体パッケージ6は、ダイオード69がIGBT63よりも負極端

子421側に位置するように金属層2上に配置されている。すなわち、正極側導体41上

の半導体パッケージ6のIGBT63は、出力側導体43上の半導体パッケージ6のダイ

オード69に対向するように設けられている。

されない。半導体パッケージ6は、IGBT63以外の半導体チップを備えていてもよい

。例えば、SiCチップやGaNチップを備えていてもよい。また、半導体パッケージ6

において、ダイオード69を削除することもできる。

図1に示すように、第3配線8は、平面視において略L字形状であり、半導体パッケー

ジ6の上面に露出した第2の部材65と第4の部材613とに接続する第1の部分81と

、負極側導体42に接続する第2の部分82と、第1の部分81と第2の部分82とを接

続する第3の部分83を有する。なお、パッケージ6中にダイオード69を設けない場合

、第3配線8は、略L字形状でなくてもよい。

第4の部材613の上面から第2の部材65の上面に亘るように全長方向D1に延びてい

る。また、第2の部材65上から導体42の方向、すなわち幅方向D2の内方に延びてL

字形状を有している。第1の部分81は、半田層5を介して第2の部材65および第4の

部材613と電気的かつ機械的に接続されている。より具体的には、第1の部分81は、

第2の部材65の上面と第4の部材613の上面の全範囲に接続されており、幅方向D2

において第2の部材65および第4の部材613の幅より大きい幅を有する。なお、第1

の部分81は、金属を主成分とする材料を介して第2の部材65および第4の部材613

と電気的かつ機械的に接続されていてもよい。

延びている。すなわち、第3の部分83は、第1の部分81に対して下方に傾斜している

。

83(以下、正極側の第3の部分83ともいう)は、その下端部が出力側導体43の近傍

に至る。

83(以下、出力側の第3の部分83ともいう)は、その下端部が負極側導体42の近傍

に至る。

3配線8の第2の部分82(以下、正極側の第2の部分82ともいう)は、正極側の第3

の部分83の下端部に繋がっている。正極側の第2の部分82は、半田層5で出力側導体

43と電気的かつ機械的に接続されている。より具体的には、正極側の第2の部分82は

、その底面の全範囲において出力側導体43と接続されている。なお、正極側の第2の部

分82は、金属を主成分とする材料を介して出力側導体43と電気的かつ機械的に接続さ

れていてもよい。

分82ともいう)は、出力側の第3の部分83の下端部に繋がっている。出力側の第2の

部分82は、半田層5で負極側導体42と電気的かつ機械的に接続されている。より具体

的には、出力側の第2の部分82は、その底面の全範囲において負極側導体42と接続さ

れている。なお、出力側の第2の部分82は、金属を主成分とする材料を介して負極側導

体42と電気的かつ機械的に接続されていてもよい。

おいて出力側導体43と接続されていることで、正極側の第3配線8は、第2の部材65

に伝達されたIGBT63の熱を、出力側導体43及び金属層2に効率的に逃がすことが

できる。

範囲において負極側導体42と接続されていることで、出力側の第3配線8は、第2の部

材65に伝達されたIGBT63の熱を、負極側導体42に効率的に逃がすことができる

。

図5は、第1の実施形態を示す半導体モジュール1の等価回路図である。図5に示すよ

うに、各半導体パッケージ6において、IGBT63とダイオード69とは逆並列に接続

されている。正極端子411に接続されるIGBT63同士は並列接続され、ダイオード

69同士も並列接続されている。また負極端子421に接続されるIGBT63同士は並

列接続され、ダイオード69同士も並列接続されている。正極側導体41上の半導体パッ

ケージ6のIGBT63およびダイオード69と、出力側導体43上の半導体パッケージ

6のIGBT63およびダイオード69とは、正極側の第3配線8を通じて直列接続され

ている。

ることができる。出力側導体43上の半導体パッケージ6は、例えば、インバータの下ア

ームとして用いることができる。

以上のように構成された半導体モジュール1は、以下のようにしてIGBT63に発生

した熱を放熱できる。

子421を直流電源の正極および負極にそれぞれ接続する。また、出力端子431を、例

えば、三相電動機のU端子、V端子、W端子に接続する。また、リードフレーム66を、

ゲートへの入力信号を制御する制御装置に接続する。そして、直流電源で正極端子411

と負極端子421との間に直流電力を印加し、ゲートへの入力信号でIGBT63をスイ

ッチング制御することで、直流電力を三相交流電力に変換する。変換された三相交流電力

は、出力端子431から三相電動機に出力する。

制御されることで発熱する。

は、順に、半田層5、第1の部材61、半田層5、正極側導体41および絶縁層3を経由

して金属層2に通じる放熱経路が形成されている。また、図2Bに示すように、出力側導

体43上の半導体パッケージ6のIGBT63の下方には、順に、半田層5、第1の部材

61、半田層5、出力側導体43および絶縁層3を経由して金属層2に通じる放熱経路が

形成されている。したがって、IGBT63の下方の放熱経路を通じてIGBT63で発

生した熱を下方に放熱できる。

の上方には、順に、半田層5、第2の部材65、半田層5、第3配線8、半田層5、出力

側導体43および絶縁層3を経由して金属層2に通じる放熱経路が形成されている。また

、図2Bに示すように、出力側導体43上の半導体パッケージ6のIGBT63の上方に

は、順に、半田層5、第2の部材65、半田層5、第3配線8、半田層5、負極側導体4

2および絶縁層3を経由して金属層2に通じる放熱経路が形成されている。したがって、

IGBT63の上方の放熱経路を通じてIGBT63で発生した熱を上方にも放熱できる

。

次に、第1の実施形態の実験例について説明する。図6Aは、第1の実施形態の半導体

モジュール1を模擬したシミュレーション用の積層構造100(以下、第1の実施形態の

積層構造ともいう)の断面図である。図6Bは、比較例の半導体モジュールを模擬したシ

ミュレーション用の積層構造200(以下、比較例の積層構造ともいう)の断面図である

。

と、比較例の積層構造200とを作成し、両積層構造100、200に対して、以下の条

件で熱伝達シミュレーションを行った。

ク101と、シリコングリス102と、シリコングリス上に設けられ、Cuからなる金属

層103及び樹脂からなる絶縁層104で構成された基板と、Cuからなる導体105と

、半田層106と、Cuからなる部材107と、半田層108と、半導体チップ109と

、半田層110と、Cuからなる部材111と、半田層112と、Cuからなる部材11

3とを備える。Cuからなる金属層103は、金属層2を模擬している。Cuからなる導

体105は、導体41〜43を模擬している。Cuからなる部材107は、第1の部材6

1を模擬している。半導体チップ109は、IGBT63を模擬している。Cuからなる

部材プレート111は、第2の部材65を模擬している。Cuからなる部材113は、第

3配線8を模擬している。

と、シリコングリス102と、Cuベース基板103と、半田層201と、Cu層202

と、アルミナ絶縁層203と、Cu配線105と、半田層204と、半導体チップ109

とを備える。

値とを示す図である。積層構造100、200の各層は、図7に示すような構成材料、成

分および物性値(密度、比熱、熱伝達率)を有する。

熱量で発熱することを条件とした。また、シミュレーションでは、ヒートシンク101が

400W/m2・Kの冷却能力で半導体チップ109を冷却することを条件とした。

第1の実施形態の積層構造100は、熱抵抗を約22%低減できることが確認された。第

1の実施形態の積層構造100は、比較例の積層構造200と異なり、半導体チップ10

9の下層側への放熱経路だけでなく、半導体チップ109の上層側への放熱経路も有して

いるため、熱抵抗を改善できたと推測される。

上層に第2の部材65と第3配線8とを備えることで、IGBT63の下方への放熱経路

だけでなく、IGBT63の上方への放熱経路も確保できる。これにより、放熱効率を向

上できる。

及び第2の部材65は、封止樹脂68によって安定的に封止されている。従ってIGBT

63に対し線膨張係数の異なる第1の部材61および第2の部材65は熱変形を生じず、

部材の熱変形に起因したIGBT63の破壊も抑制できる。また、従来構造においてセラ

ミック基板の上面に設けられたCu配線105はエッチングで形成されるため、その厚み

には上限がある。これに対し、本実施形態の第1の部材61および第2の部材65はプレ

ス部品である。従って第1の部材61と第2の部材65の厚みを従来よりも厚くすること

ができる。これにより、IGBT63で発生した過渡熱を、第2および第2の部材61、

65によって迅速に放熱できるので、放熱効率を更に向上できる。

の幅が太い第3配線8を用いることで、インダクタンスを低減できる。

よりも第2の部分82の近くに設けられる。従ってIGBT63から第1の部分81乃至

第3の部分83を介して基板7へ向かう熱の伝達距離をダイオード69より短くしている

。これにより、IGBT63からの熱に対する第3配線8の熱抵抗を抑え、放熱効率を向

上できる。また、第3の部分83は、第2の部分82に向かって直進するように傾斜して

いる。これにより、第3配線8中のIGBT63の熱の伝達距離を更に短くすることがで

き、放熱効率を更に向上できる。

41上の半導体パッケージ6と出力側導体43上の半導体パッケージ6との間で、IGB

T63とダイオード69との相対的な位置関係を互いに逆転させることができる。つまり

、正極側導体41上の半導体パッケージのIGBT63と、出力側導体43上の半導体パ

ッケージ6のダイオード69とが対向して設けられる。これにより、金属層2上のスペー

スにおいて、正極側の第3配線8を出力側の第3配線8に対して180度向きを変えて効

率よく配置する事ができる。

したセラミック基板を、金属ベース基板に実装した状態で行う必要があった。これに対し

第1の実施形態の半導体モジュール1は、半導体チップ109がパッケージとして封止さ

れているために、半導体パッケージ6の単位でスイッチングテストを行うことができる。

従って利便性を向上できる。また、信号端子であるリードフレーム66を半導体パッケー

ジ6から直接取り出すことができるので、基板7の金属層2に信号端子を設けることを要

しない。更に半導体パッケージ6はIGBT63を挟んで上下両面に設けられた第1の部

材61と第2の部材65に、厚みが1mm以上のCuからなるプレス部品を用いている。

このような厚みの大きい部材を有する半導体パッケージ6を半導体モジュール1に組み込

むことができるため、IGBT63から効率的に放熱を行うことができる。つまり、半導

体パッケージ6を組み込むことで半導体モジュール1は従来に比べ効率的に放熱を行うこ

とが可能になる。

次に、第2の実施形態について、第1の実施形態との相違点を中心に説明する。図8は

、第2の実施形態を示す半導体モジュール1の断面図である。図8は、図4Aに対応する

断面図であり、正極側導体41上の半導体パッケージ6およびその周辺の構成を示してい

る。

分81とは、半田層を介さず超音波接合により直接接続されている。

により直接接続されている。

65と第1の部分81とを超音波接続で直接繋げ、第2の部分82と負極側導体42とを

超音波接続で直接繋げてもよい。また、正極側の第1の部材61は、半田層を介さず超音

波接合により直接、正極側導体41と電気的かつ機械的に接続されていてもよい。また、

出力側の第1の部材61も、半田層を介さず超音波接合により直接、出力側導体43と電

気的かつ機械的に接続されていてもよい。

ュール1の放熱効率を向上できる。

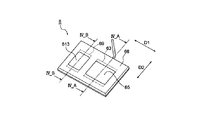

次に、第3の実施形態について、第1の実施形態との相違点を中心に説明する。図9は

、図1に示す第1の実施形態の半導体モジュール1のIX−IX’断面を示している。図

10は、第3の実施形態の半導体モジュール10断面図である。図10は、図9に対応す

る断面図であり、半導体パッケージ6と導体141、142、143との構成を示してい

る。なお、正極側導体141は、第4配線、負極側導体142は第5配線、出力側導体1

43は第6配線である。

上アームと下アームは異なるタイミングでオンとオフのスイッチングを行う。第1の実施

形態の図1に示す構造において、IGBT63のオンからオフへのスイッチング直後に、

サージ電圧が発生する。このサージ電圧が各素子の許容値を超えると素子が破壊される。

サージ電圧ΔVは、インダクタンスL、電流iを用いて以下の式のように表せる。

に、インダクタンスLを低減することが重要であり、サージ電圧の発生に関係する電流経

路が短いほどインダクタンスは低減する。このとき、サージ電圧の発生に関係する電流は

、オンからオフへのスイッチング直後にIGBT63に暫く減少しながら流れる電流とダ

イオード69に流れる電流とを合わせて考えたときの電流である。

1、正極側導体41、正極側導体41に搭載されている半導体パッケージ6、第3配線8

、出力側導体43、出力側導体43に搭載されている半導体パッケージ6、第3配線8、

負極側導体42、負極端子421である。

る。これにより、サージ電圧の発生に関係する電流経路が短縮される。図10に示すよう

に、半導体モジュール10には、金属層2上に絶縁層3を介して正極側導体141と負極

側導体142が設けられている。正極側導体141と負極側導体142上にはそれぞれ半

導体パッケージ6が設けられている。この一組の半導体パッケージ6上に、すなわち、半

導体パッケージ6の正極側導体141および負極側導体142に接する面と反対側の面に

、出力側導体143が設けられている。出力側導体143は、一組の半導体パッケージ6

の上面全体を覆うように設けられている。正極側導体141上に設けられた半導体パッケ

ージ6において、内部に設けられたIGBTのエミッタ電極は、出力側導体143に向か

い合うよう設けられている。一方、負極側導体142上に設けられた半導体パッケージ6

において、内部に設けられたIGBTのコレクタ電極は、出力側導体143に向かい合う

よう設けられている。つまり、負極側導体142上の半導体パッケージ6は、正極側導体

141上の半導体パッケージに対して上下反転して設置されている。以上より、半導体モ

ジュール10は、第3の配線8を不要とする。

411、正極側導体141、正極側導体141に搭載されている半導体パッケージ6、出

力側導体143、負極側導体142に搭載されている半導体パッケージ6、負極側導体1

42、負極端子421である。つまり、第1の実施形態の半導体モジュール1に対して、

第3の実施形態の半導体モジュール10は、第3の配線8を経由する必要がなくなり、サ

ージ電圧の発生に関係する電流経路を短くすることができる。よって、IGBT63の両

面で放熱する構造を有しながら、インダクタンスの低減を図ることが出来る。

0%低減することが確認された。

オードを有している。半導体パッケージ6を形成する場合、IGBTとダイオードを互い

に上下反転させることなく設けることができる。また、このように形成された半導体パッ

ケージ6を用いて半導体モジュール10を形成する場合、上述したとおり、一組の半導体

パッケージ6のうち、一方を他方に対して上下反転させるのみでよく、組み立て性や信頼

性が向上する。また、パッケージサイズも小さくできる。一方、半導体チップ単体を用い

て半導体モジュールを形成する比較例の場合、すなわち、IGBTとダイオードの2つの

半導体チップを他のIGBTとダイオードの2つの半導体チップに対して上下反転して設

ける場合、計4個の半導体チップを半導体モジュール10に設けることになり、第3の実

施形態に比べ組み立て性や信頼性が下がる。また半導体モジュールも大きくなってしまう

。

体142を設けているが、代わりに出力側導体143を設けても良い。この場合、一組の

半導体パッケージの上面に正極側導体141と負極側導体142がそれぞれ設けられる。

また、上面に負極側導体142を有する半導体パッケージ6は、上面に正極側導体141

を有する半導体パッケージ6に対して上下反転して設置される。この場合も同様に、サー

ジ電圧の発生に関係する電流経路が短縮化される。

てもよい。

のであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様

々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、

置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に

含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるもので

ある。

2 金属層

3 絶縁層

41 正極側導体

42 負極側導体

43 出力側導体

5 半田層

6 半導体パッケージ

61 第1の部材

63 IGBT

65 第2の部材

66 リードフレーム

68 封止樹脂

69 ダイオード

7 基板

8 第3配線

81 第1の部分

82 第2の部分

83 第3の部分

9 ケース

10 半導体モジュール

141 正極側導体

142 負極側導体

143 出力側導体

Claims (6)

- 金属層と、前記金属層上に設けられ樹脂を含有する絶縁層と、を有する基板と、

前記基板上に設けられた第6配線と、

前記第6配線上に設けられ、上部および下部において放熱する第1半導体パッケージと

、

前記第6配線上に、前記第1半導体パッケージに対して上下反転して設けられ、上部お

よび下部において放熱する第2半導体パッケージと、

前記第1半導体パッケージ上に設けられた第4配線と、

前記第2半導体パッケージ上に設けられた第5配線と、を備え、

前記第1半導体パッケージと前記第2半導体パッケージは前記第6配線を介して、直列

接続される半導体モジュール。 - 前記第2半導体パッケージは、

前記下部に設けられ、導電性および熱伝導性を有する第3の部材と、

前記上部に設けられ、導電性および熱伝導性を有する第4の部材と、

前記第3の部材と前記第4の部材との間に設けられた第2の半導体チップと、

前記第3の部材と前記第4の部材と前記第2の半導体チップとを封止する封止部材と、

を備える請求項1に記載の半導体モジュール。 - 前記第1半導体パッケージは、

前記第1半導体パッケージの前記下部に設けられ、導電性および熱伝導性を有する第1

の部材と、

前記第1半導体パッケージの前記上部に設けられ、導電性および熱伝導性を有する第2

の部材と、

前記第1の部材と前記第2の部材との間に設けられた第1の半導体チップと、

前記第1の部材と前記第2の部材と前記第1の半導体チップとを封止する封止部材と、

を備える請求項1から2のいずれかに記載の半導体モジュール。 - 前記第1の部材は半田あるいは金属を主成分とする材料を介して前記第4配線に接続し

、前記第2の部材は半田あるいは金属を主成分とする材料を介して前記第6配線に接続す

る請求項3に記載の半導体モジュール。 - 前記第1の部材は前記第4配線に直接接続し、前記第2の部材は前記第6配線に直接接

続する請求項3に記載の半導体モジュール。 - 前記第2の部材は、前記封止部材から露出した露出面を有し、前記第6配線は前記露出

面全体に接して設けられる請求項3に記載の半導体モジュール。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015233751 | 2015-11-30 | ||

| JP2015233751 | 2015-11-30 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017108130A JP2017108130A (ja) | 2017-06-15 |

| JP2017108130A5 JP2017108130A5 (ja) | 2019-03-22 |

| JP6685884B2 true JP6685884B2 (ja) | 2020-04-22 |

Family

ID=58777338

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016231244A Active JP6685884B2 (ja) | 2015-11-30 | 2016-11-29 | 半導体モジュール |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US10217690B2 (ja) |

| JP (1) | JP6685884B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE112017003455B4 (de) * | 2016-07-08 | 2024-06-06 | Mitsubishi Electric Corporation | Halbleitervorrichtung und Leistungsumwandlungsvorrichtung |

| US10937731B2 (en) * | 2016-07-27 | 2021-03-02 | Hitachi, Ltd. | Semiconductor module and method for manufacturing semiconductor module |

| JP6891904B2 (ja) * | 2017-02-06 | 2021-06-18 | 富士電機株式会社 | 半導体モジュール、電気自動車およびパワーコントロールユニット |

| JP6470328B2 (ja) * | 2017-02-09 | 2019-02-13 | 株式会社東芝 | 半導体モジュール |

| JP6685470B2 (ja) * | 2017-03-30 | 2020-04-22 | 三菱電機株式会社 | 半導体装置およびその製造方法、ならびに電力変換装置 |

| TWI675441B (zh) * | 2018-05-14 | 2019-10-21 | 欣興電子股份有限公司 | 封裝載板結構及其製造方法 |

| JP7301805B2 (ja) * | 2020-09-24 | 2023-07-03 | 株式会社東芝 | 半導体モジュール |

| JP7354076B2 (ja) | 2020-09-24 | 2023-10-02 | 株式会社東芝 | 半導体モジュール |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0874399A1 (en) * | 1996-08-20 | 1998-10-28 | Kabushiki Kaisha Toshiba | Silicon nitride circuit board and semiconductor module |

| WO2004057662A2 (en) * | 2002-12-20 | 2004-07-08 | Koninklijke Philips Electronics N.V. | Electronic device and method of manufacturing same |

| JP2004241734A (ja) * | 2003-02-10 | 2004-08-26 | Toyota Industries Corp | 半導体モジュール |

| JP2005109100A (ja) * | 2003-09-30 | 2005-04-21 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2006080153A (ja) * | 2004-09-07 | 2006-03-23 | Toshiba Corp | 半導体装置 |

| JP4770533B2 (ja) | 2005-05-16 | 2011-09-14 | 富士電機株式会社 | 半導体装置の製造方法および半導体装置 |

| JP4775327B2 (ja) * | 2007-06-06 | 2011-09-21 | 富士電機株式会社 | 半導体装置の製造方法 |

| US8138587B2 (en) * | 2008-09-30 | 2012-03-20 | Infineon Technologies Ag | Device including two mounting surfaces |

| JP2011086889A (ja) * | 2009-10-19 | 2011-04-28 | Renesas Electronics Corp | 半導体装置およびその製造方法 |

| US8120158B2 (en) * | 2009-11-10 | 2012-02-21 | Infineon Technologies Ag | Laminate electronic device |

| JP5253455B2 (ja) * | 2010-06-01 | 2013-07-31 | 三菱電機株式会社 | パワー半導体装置 |

| JP5520889B2 (ja) * | 2011-06-24 | 2014-06-11 | 日立オートモティブシステムズ株式会社 | パワー半導体モジュール及びそれを用いた電力変換装置 |

| JP5706251B2 (ja) * | 2011-06-30 | 2015-04-22 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP5863602B2 (ja) | 2011-08-31 | 2016-02-16 | 三菱電機株式会社 | 電力用半導体装置 |

| JP2013097560A (ja) | 2011-10-31 | 2013-05-20 | Mitsubishi Heavy Ind Ltd | 建設工事の工程最適化システム及び建設工事の工程最適化方法 |

| JP5965687B2 (ja) | 2012-03-23 | 2016-08-10 | 株式会社 日立パワーデバイス | パワー半導体モジュール |

| JP2014157927A (ja) * | 2013-02-15 | 2014-08-28 | Denso Corp | 半導体装置及びその製造方法 |

| JP2015095560A (ja) * | 2013-11-12 | 2015-05-18 | 株式会社デンソー | パワーモジュール |

| JP2015144188A (ja) * | 2014-01-31 | 2015-08-06 | 株式会社東芝 | 半導体装置及びその製造方法 |

-

2016

- 2016-08-04 US US15/228,086 patent/US10217690B2/en active Active

- 2016-11-29 JP JP2016231244A patent/JP6685884B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US10217690B2 (en) | 2019-02-26 |

| US20170154834A1 (en) | 2017-06-01 |

| JP2017108130A (ja) | 2017-06-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6685884B2 (ja) | 半導体モジュール | |

| EP3107120B1 (en) | Power semiconductor module | |

| US8987777B2 (en) | Stacked half-bridge power module | |

| JP4803241B2 (ja) | 半導体モジュール | |

| KR101388737B1 (ko) | 반도체 패키지, 반도체 모듈, 및 그 실장 구조 | |

| US10084389B2 (en) | Power module | |

| JP6786416B2 (ja) | 半導体装置 | |

| JP6852011B2 (ja) | 半導体装置 | |

| JP2015095560A (ja) | パワーモジュール | |

| JP2021141222A (ja) | 半導体モジュール | |

| US8823153B2 (en) | Semiconductor package | |

| US10896864B2 (en) | Power semiconductor chip module | |

| US11081412B2 (en) | Semiconductor device | |

| JP2013125889A (ja) | 半導体装置 | |

| JP4375299B2 (ja) | パワー半導体装置 | |

| JP6156131B2 (ja) | 半導体装置 | |

| JP2009117701A (ja) | パワーモジュール | |

| JP6305362B2 (ja) | 電力用半導体モジュール | |

| US10658344B2 (en) | Semiconductor device | |

| JP2017069351A (ja) | 半導体装置 | |

| JP2017069352A (ja) | 半導体装置 | |

| JP2013098343A (ja) | 半導体装置とその製造方法 | |

| JP5444486B2 (ja) | インバータ装置 | |

| JP6884723B2 (ja) | 半導体装置 | |

| JP2010171463A (ja) | 電力用半導体素子及びそのインバータ装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20170929 Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20170929 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20180831 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190204 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190204 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20191030 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20191206 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200204 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200306 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200401 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6685884 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |