JP6439552B2 - 半導体モジュール及び半導体装置 - Google Patents

半導体モジュール及び半導体装置 Download PDFInfo

- Publication number

- JP6439552B2 JP6439552B2 JP2015075251A JP2015075251A JP6439552B2 JP 6439552 B2 JP6439552 B2 JP 6439552B2 JP 2015075251 A JP2015075251 A JP 2015075251A JP 2015075251 A JP2015075251 A JP 2015075251A JP 6439552 B2 JP6439552 B2 JP 6439552B2

- Authority

- JP

- Japan

- Prior art keywords

- plate

- semiconductor

- semiconductor module

- gate

- guide groove

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H10W40/47—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/27—Electrodes not carrying the current to be rectified, amplified, oscillated or switched, e.g. gates

- H10D64/311—Gate electrodes for field-effect devices

- H10D64/411—Gate electrodes for field-effect devices for FETs

- H10D64/511—Gate electrodes for field-effect devices for FETs for IGFETs

- H10D64/512—Disposition of the gate electrodes, e.g. buried gates

-

- H10W72/00—

-

- H10W72/50—

-

- H10W76/136—

-

- H10W90/00—

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Inverter Devices (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Power Conversion In General (AREA)

Description

[第1の実施の形態]

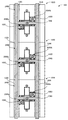

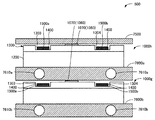

第1の実施の形態の半導体モジュールについて、図1〜図10を用いて説明する。

なお、図1(A)は、半導体モジュールの平面図を、図1(B)は、図1(A)の一点鎖線X1−X1の断面図をそれぞれ示している。

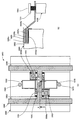

図2(A)は、ドレイン板1010の平面図を、図2(B)は、図2(A)の一点鎖線X−Xにおける断面図をそれぞれ示している。

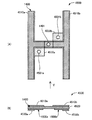

ゲート板1400は、ガイド溝1303,1304に配置され、ゲート端子1040と電気的に接続され、ガイド溝1303,1304に沿って外周部に延伸されている。なお、ゲート端子1040は、ガイド溝1303,1304の中間点を直交する線上に位置している。

まず、図2に示されるように、ドレイン板1010の中央部に積層基板1030と、積層基板1030の両側に複数の半導体素子1020とがそれぞれ配置されている。

次いで、枠1200に被せる蓋1300は、図8(A)に示されるように、開口1301と、ボルト孔1305,1306とがそれぞれ形成されている。さらに、蓋1300は、図中上下方向に直線状のガイド溝1303,1304が開口1301に接して、外周部まで延伸されて形成されている。

なお、第1の実施の形態では、ガイド溝1303,1304に補助ソース板1500a,1500bを先に配置して、ゲート板1400を配置する場合を例に挙げて説明した。この場合に限らず、ゲート板1400を先に配置して、補助ソース板1500a,1500bを配置することも可能である。

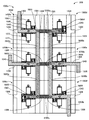

第2の実施の形態では、第1の実施の形態で示した半導体モジュールを複数組み合わせた半導体装置について、図11及び図12を用いて説明する。

また、図12は、第2の実施の形態の半導体装置の配線板を示す図である。

図12(A)はゲート板の平面図、図12(B)は補助ソース板の平面図をそれぞれ示している。

このようにガイド溝同士を連結した複数の半導体モジュールに対して、図12に示されるような、一体化したゲート板2400と、一体化した補助ソース板2500a,2500bとを用意する。

さらに、連結したガイド溝1303,1304の絶縁層を介して、一体化したゲート板2400を配置する。配置の際には、ゲート板2400のボルト孔2401を、ゲート端子1040のボルト孔1041に位置合わせする。

第3の実施の形態では、補助ソース端子を設けずに、補助ソース電流を得ることができる半導体モジュールについて、図13を用いて説明する。

図13(A)は、蓋2300の平面図を、図13(B)は、第3の実施の形態の半導体モジュール2000の平面図をそれぞれ示している。

[第4の実施の形態]

第4の実施の形態では、半導体モジュールのガイド溝の深さをゲート端子並びに補助ソース端子よりも浅くする場合について、図14を用いて説明する。

図14(A)は、第4の実施の形態の半導体モジュール3000の平面図、図14(B)は、図14(A)の一点鎖線X−Xにおける断面拡大図をそれぞれ示している。

これにより、ゲート板3400と補助ソース板3500a,3500bとが配置されるガイド溝3303,3304の隙間(空間)を小さくすることができる。このために、半導体モジュール3000の低インダクタンス化を図ることができる。したがって、ガイド溝3303,3304の深さは、隙間が最も少ない、ゲート板3400と、補助ソース板3500a,3500bと、絶縁層とを合わせた厚さ程度とすることが望ましい。

第5の実施の形態では、第1の実施の形態のゲート板1400と補助ソース板1500a,1500bとをプリント基板にして一体化した場合について、図15を用いて説明する。

図15(A)は、ゲート板1400と補助ソース板1500a,1500bとを含むプリント基板の平面図を、図15(B)は、図15(A)の矢視Yから見た側面図をそれぞれ示している。

なお、複数の半導体モジュールを組み合わせる場合には、例えば、第4の実施の形態に示したゲート板2400と、補助ソース板2500a,2500bとを、プリント基板として一体化することが可能である。

第6の実施の形態では半導体モジュールを6つ組み合わせた場合について、図16を用いて説明する。

半導体モジュール1000a〜1000fは、半導体モジュール1000と同様の構成をなしている。但し、半導体モジュール1000a〜1000fの蓋4300には、ガイド溝1303,1304の中心部から外周部に通じるガイド溝1308,1309がさらに形成されている。なお、図16では、半導体モジュール1000aにのみ符号を付しており、半導体モジュール1000b〜1000fに対する符号は省略している。

そして、ゲート板5400aが半導体モジュール1000aのガイド溝1303に配置され、半導体モジュール1000aのゲート端子1040にボルト1043で固定されている。

接続板5700aが、半導体モジュール1000aのガイド溝1309と半導体モジュール1000dのガイド溝1308とに配置されている。接続板5700aと、ゲート板5400a,5500aとが、ボルト5801で固定され、接続板5700aと、ゲート板5600bとが、ボルト5804で固定されている。

第7の実施の形態では、第1の実施の形態の半導体モジュール1000において、補助ソース板が配置されるガイド溝を新たに設けた場合について説明する。

半導体モジュール5000では、蓋5300以外については、半導体モジュール1000と同様の構成がなされている。

図18は、第7の実施の形態の半導体モジュールを複数組み合わせた半導体装置を示す図である。

連結したガイド溝5303に絶縁層を介して、ゲート板5400を配置して、ゲート板5400をゲート端子1040にボルト1043で固定する。

第8の実施の形態では、第7の実施の形態の半導体モジュール5000において、補助ソース板が配置されるガイド溝を別の箇所に設けた場合について説明する。

図19(A)は、蓋6300が設置された半導体モジュール6000の平面図、図19(B)は、半導体モジュール6000の内部平面図をそれぞれ示している。

蓋6300は、ゲート端子1040と隣接し、開口6301に接して形成されたガイド溝6303を備える。さらに、開口6301の図中左側に、ガイド溝6303と平行に配置され、ボルト孔6305aを備える補助ガイド溝6304が形成されている。

また、このような半導体モジュール6000を複数組み合わせた半導体装置400について、図20を用いて説明する。

複数(第8の実施の形態では3つ)の半導体モジュール6000を用意して、ガイド溝6303と補助ガイド溝6304が連結するように配置する。

同様にして、連結した補助ガイド溝6304に絶縁層を介して、補助ソース板6500を配置して、補助ソース板6500を補助ガイド溝6304のボルト孔6305aに、ボルト6503でねじ止めして固定する。

第9の実施の形態では、半導体モジュール1000を直列に組み合わせた場合について図21及び図22を用いて説明する。

なお、図21では、複数の半導体モジュールを縦方向に配列して、図22は、複数の半導体モジュールを横方向に配列して、それぞれ直列に組み合わせた半導体装置を示す側面図である。

次いで、複数の半導体モジュール1000を直列に接続するに当たって、半導体モジュール1000を横方向に配置する場合について、図22を用いて説明する。

1000 半導体モジュール

1010 ドレイン板

1020 半導体素子

1030 積層基板

1031a 第1回路板

1031b 第2回路板

1032 絶縁板

1033 金属板

1040 ゲート端子

1041,1051,1061,1071,1081,1305,1306,1401,1501a,1501b ボルト孔

1043,1053,1063,1073,1083 ボルト

1050,1060 補助ソース端子

1070,1080 ソース端子

1072,1082 段差面

1090,1100 プリント基板

1091,1101 ゲート配線層

1093,1103 ソース配線層

1092a,1092b,1102a,1102b 導電ポスト

1094,1104 貫通孔

1095,1105 ゲート接続部

1096,1106 ソース接続部

1200 枠

1300 蓋

1301 開口

1303,1304 ガイド溝

1400 ゲート板

1500a,1500b 補助ソース板

1600a,1600b,1600c 絶縁層

1700 ソース導体

1800 ドレイン導体

Claims (14)

- ドレイン板と、

おもて面にゲート電極とソース電極とを備え、裏面にドレイン電極を備え、前記ドレイン板のおもて面に配置され、前記ドレイン電極と前記ドレイン板とが電気的に接続される、半導体素子と、

絶縁板と、前記絶縁板のおもて面に設けられた第1回路板及び第2回路板とを備え、前記ドレイン板のおもて面に配置され、前記第1回路板は前記ゲート電極と電気的に接続され、前記第2回路板は前記ソース電極と電気的に接続された、積層基板と、

前記第1回路板上に配置されたゲート端子と、

前記第2回路板上に配置されたソース端子と、

開口及びガイド溝を備え、前記ドレイン板のおもて面と対向して配置され、前記ゲート端子及び前記ソース端子が前記開口に位置し、前記ガイド溝は前記開口に接して外周部まで延伸されている、蓋と、

を備える半導体モジュール。 - 前記ゲート端子と電気的に接続され、前記ガイド溝に沿って外周部に延伸されたゲート板、

をさらに有する請求項1記載の半導体モジュール。 - 前記第2回路板上に配置され、前記開口に位置する補助ソース端子と、

前記補助ソース端子と電気的に接続され、前記ガイド溝に沿って前記ゲート板とは電気的に絶縁されて外周部に延伸された補助ソース板と、

をさらに有する請求項2記載の半導体モジュール。 - 前記蓋に設けられた補助ガイド溝と、

前記補助ガイド溝に沿って外周部に延伸された補助ソース板と、

をさらに有し、

前記ガイド溝は前記開口の一方に接して形成され、

前記補助ガイド溝は前記開口の他方に接して形成され、

前記第2回路板と前記補助ソース板との間が、前記ソース端子及び前記蓋を経由して電気的に接続されている、

請求項2記載の半導体モジュール。 - 前記第2回路板は、前記第1回路板を取り囲んで前記絶縁板のおもて面に配置されている請求項1乃至4のいずれかに記載の半導体モジュール。

- 前記ゲート端子は、前記ガイド溝の中間点を直交する線上に位置するように前記第1回路板上に設けられている請求項5記載の半導体モジュール。

- 前記ソース端子は、前記第2回路板上に一対設けられ、

前記ゲート端子と、一対の前記ソース端子とは前記ガイド溝と平行に直線状に配置されている請求項6記載の半導体モジュール。 - 前記ガイド溝の底部が、前記ゲート端子の上端部より上方に位置している、

請求項1から4のいずれか1項に記載の半導体モジュール。 - 請求項2記載の前記半導体モジュールを複数備え、

複数の前記半導体モジュールは、前記ガイド溝同士が連結されるように配置され、

当該連結された前記ガイド溝に沿って、一体化された前記ゲート板が配置されている、

半導体装置。 - 請求項3記載の前記半導体モジュールを複数備え、

複数の前記半導体モジュールは、前記ガイド溝同士が連結されるように配置され、

当該連結された前記ガイド溝に沿って、一体化された前記ゲート板及び一体化された前記補助ソース板が配置されている、

半導体装置。 - 請求項4記載の前記半導体モジュールを複数備え、

複数の前記半導体モジュールは、前記ガイド溝同士が連結されるように配置され、前記補助ガイド溝同士が連結されるように配置され、

当該連結された前記ガイド溝に沿って一体化された前記ゲート板が配置され、

当該連結された前記補助ガイド溝に沿って一体化された前記補助ソース板が配置されている、

半導体装置。 - 請求項1記載の前記半導体モジュールを複数備え、

複数の前記半導体モジュールは、前記半導体モジュールの前記ソース端子と、別の前記半導体モジュールの前記ドレイン板とが電気的に接続されている、

半導体装置。 - 複数の前記半導体モジュールが積層して配置され、

前記半導体モジュールの前記ソース端子と、隣接する前記半導体モジュールの前記ドレイン板が電気的に接続されている、

請求項12記載の半導体装置。 - 複数の前記半導体モジュールが並んで配置され、

前記半導体モジュールの前記ソース端子と、隣接する前記半導体モジュールの前記ドレイン板が導電部材を経由して電気的に接続されている、

請求項12記載の半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015075251A JP6439552B2 (ja) | 2015-04-01 | 2015-04-01 | 半導体モジュール及び半導体装置 |

| CN201610130201.2A CN106057740B (zh) | 2015-04-01 | 2016-03-08 | 半导体模块及半导体装置 |

| DE102016203819.2A DE102016203819B4 (de) | 2015-04-01 | 2016-03-09 | Halbleitermodul und Halbleitervorrichtung |

| US15/069,404 US9524919B2 (en) | 2015-04-01 | 2016-03-14 | Semiconductor module and semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015075251A JP6439552B2 (ja) | 2015-04-01 | 2015-04-01 | 半導体モジュール及び半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016195216A JP2016195216A (ja) | 2016-11-17 |

| JP6439552B2 true JP6439552B2 (ja) | 2018-12-19 |

Family

ID=56937228

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015075251A Expired - Fee Related JP6439552B2 (ja) | 2015-04-01 | 2015-04-01 | 半導体モジュール及び半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9524919B2 (ja) |

| JP (1) | JP6439552B2 (ja) |

| CN (1) | CN106057740B (ja) |

| DE (1) | DE102016203819B4 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7545298B2 (ja) * | 2020-11-13 | 2024-09-04 | 株式会社日立製作所 | 電力変換装置 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB930704A (en) * | 1960-09-05 | 1963-07-10 | Sony Corp | A balanced esaki diode pair |

| JPS62142856U (ja) * | 1986-02-28 | 1987-09-09 | ||

| JPH0666411B2 (ja) * | 1987-11-06 | 1994-08-24 | 富士電機株式会社 | 平形半導体装置 |

| JPH0734457B2 (ja) * | 1988-04-05 | 1995-04-12 | 株式会社東芝 | 半導体装置 |

| JPH0312410A (ja) | 1989-06-08 | 1991-01-21 | Mitsui Petrochem Ind Ltd | フツ素含有共重合体及びそれよりなるコンタクトレンズ |

| JP2882143B2 (ja) * | 1991-12-10 | 1999-04-12 | 富士電機株式会社 | 半導体装置の内部配線構造 |

| DE69509428T2 (de) * | 1994-03-24 | 1999-09-30 | Fuji Electric Co Ltd | Struktur einer Parallelschaltverbindung für flache Halbleiterschalter |

| JP3228043B2 (ja) | 1994-03-24 | 2001-11-12 | 富士電機株式会社 | 平形半導体スイッチの並列接続構造 |

| JP3228021B2 (ja) | 1994-09-13 | 2001-11-12 | 富士電機株式会社 | インバータユニット及びインバータ装置 |

| DE102004044619B4 (de) * | 2004-09-13 | 2009-07-16 | Infineon Technologies Ag | Kondensatorstruktur in Grabenstrukturen von Halbleiterbauteilen und Halbleiterbauteile mit derartigen Kondensatorstrukturen und Verfahren zur Herstellung derselben |

| JP5338830B2 (ja) * | 2011-03-15 | 2013-11-13 | 株式会社豊田自動織機 | 半導体装置 |

| JP6330436B2 (ja) * | 2014-04-01 | 2018-05-30 | 富士電機株式会社 | パワー半導体モジュール |

-

2015

- 2015-04-01 JP JP2015075251A patent/JP6439552B2/ja not_active Expired - Fee Related

-

2016

- 2016-03-08 CN CN201610130201.2A patent/CN106057740B/zh active Active

- 2016-03-09 DE DE102016203819.2A patent/DE102016203819B4/de not_active Expired - Fee Related

- 2016-03-14 US US15/069,404 patent/US9524919B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| DE102016203819B4 (de) | 2021-03-18 |

| US9524919B2 (en) | 2016-12-20 |

| CN106057740A (zh) | 2016-10-26 |

| US20160293517A1 (en) | 2016-10-06 |

| DE102016203819A1 (de) | 2016-10-06 |

| CN106057740B (zh) | 2019-12-10 |

| JP2016195216A (ja) | 2016-11-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5289348B2 (ja) | 車載用電力変換装置 | |

| JP5434986B2 (ja) | 半導体モジュールおよびそれを備えた半導体装置 | |

| US11538794B2 (en) | Power converter with an upper arm and a lower arm and at least first and second semiconductor devices connected by a bridging member | |

| JP7519356B2 (ja) | 半導体装置 | |

| CN108400716B (zh) | 低电感的半桥装置 | |

| US9780684B2 (en) | Power converter | |

| TWI716075B (zh) | 功率模組 | |

| WO2016129097A1 (ja) | ハーフブリッジパワー半導体モジュール及びその製造方法 | |

| JP4660214B2 (ja) | 電力用半導体装置 | |

| JPWO2015053142A1 (ja) | ドライバ基板および電力変換装置 | |

| CN104218829A (zh) | 逆变器单元 | |

| KR20150036347A (ko) | 반도체장치 | |

| CN110875265A (zh) | 半导体装置以及电力转换器 | |

| CN109994441B (zh) | 具有增强的高功率密度的电子组件 | |

| JP4356434B2 (ja) | 3レベルインバータ回路 | |

| JP2015053410A (ja) | 半導体モジュール | |

| JP6439552B2 (ja) | 半導体モジュール及び半導体装置 | |

| JP6922450B2 (ja) | 半導体モジュール | |

| JP4349364B2 (ja) | 半導体装置 | |

| JP3741002B2 (ja) | 半導体装置の実装構造 | |

| JP6979997B2 (ja) | 電力用半導体装置 | |

| JP2017184376A (ja) | 電力変換装置 | |

| CN112652612A (zh) | 一种堆叠型压接式功率模块及其制造方法 | |

| JP7533740B2 (ja) | 電力変換装置 | |

| JP7215402B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180214 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20181004 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20181023 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20181105 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6439552 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |