JP6115407B2 - 表示パネル、その駆動方法、および電子機器 - Google Patents

表示パネル、その駆動方法、および電子機器 Download PDFInfo

- Publication number

- JP6115407B2 JP6115407B2 JP2013177535A JP2013177535A JP6115407B2 JP 6115407 B2 JP6115407 B2 JP 6115407B2 JP 2013177535 A JP2013177535 A JP 2013177535A JP 2013177535 A JP2013177535 A JP 2013177535A JP 6115407 B2 JP6115407 B2 JP 6115407B2

- Authority

- JP

- Japan

- Prior art keywords

- unit

- clock

- signal

- pixel

- display

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 13

- 230000008859 change Effects 0.000 claims description 5

- 230000007704 transition Effects 0.000 description 38

- 230000004048 modification Effects 0.000 description 33

- 238000012986 modification Methods 0.000 description 33

- 101100042610 Arabidopsis thaliana SIGB gene Proteins 0.000 description 29

- 239000000872 buffer Substances 0.000 description 27

- 238000010586 diagram Methods 0.000 description 26

- 101100294408 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) MOT2 gene Proteins 0.000 description 21

- 101150117326 sigA gene Proteins 0.000 description 21

- 230000007257 malfunction Effects 0.000 description 12

- 230000003111 delayed effect Effects 0.000 description 11

- 238000006243 chemical reaction Methods 0.000 description 10

- 101100421503 Arabidopsis thaliana SIGA gene Proteins 0.000 description 8

- 238000004519 manufacturing process Methods 0.000 description 8

- 230000001360 synchronised effect Effects 0.000 description 8

- 230000001934 delay Effects 0.000 description 7

- 238000005401 electroluminescence Methods 0.000 description 7

- 230000006870 function Effects 0.000 description 7

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 7

- 239000011159 matrix material Substances 0.000 description 7

- 238000007493 shaping process Methods 0.000 description 7

- 230000004044 response Effects 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 4

- 230000005855 radiation Effects 0.000 description 4

- 230000000630 rising effect Effects 0.000 description 4

- 230000005236 sound signal Effects 0.000 description 4

- 230000006866 deterioration Effects 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- 238000005070 sampling Methods 0.000 description 3

- 230000009471 action Effects 0.000 description 2

- 230000002238 attenuated effect Effects 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- VZSRBBMJRBPUNF-UHFFFAOYSA-N 2-(2,3-dihydro-1H-inden-2-ylamino)-N-[3-oxo-3-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)propyl]pyrimidine-5-carboxamide Chemical class C1C(CC2=CC=CC=C12)NC1=NC=C(C=N1)C(=O)NCCC(N1CC2=C(CC1)NN=N2)=O VZSRBBMJRBPUNF-UHFFFAOYSA-N 0.000 description 1

- 101001072191 Homo sapiens Protein disulfide-isomerase A2 Proteins 0.000 description 1

- 101150107050 PSA2 gene Proteins 0.000 description 1

- 102100036351 Protein disulfide-isomerase A2 Human genes 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 208000030825 patent ductus arteriosus 2 Diseases 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2085—Special arrangements for addressing the individual elements of the matrix, other than by driving respective rows and columns in combination

- G09G3/2088—Special arrangements for addressing the individual elements of the matrix, other than by driving respective rows and columns in combination with use of a plurality of processors, each processor controlling a number of individual elements of the matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0828—Several active elements per pixel in active matrix panels forming a digital to analog [D/A] conversion circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0857—Static memory circuit, e.g. flip-flop

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Electroluminescent Light Sources (AREA)

- Transforming Electric Information Into Light Information (AREA)

- Control Of El Displays (AREA)

- Led Devices (AREA)

Description

本開示の第2の表示パネルは、表示部と、表示駆動部とを備えている。表示部は、複数の単位画素を有するものである。表示駆動部は、互いに異なる位相を有する2以上のクロック信号を含む複数のクロック信号を生成し、表示部に供給するものである。上記単位画素は、複数のクロック信号のそれぞれに対応して所定数ずつ設けられている。各単位画素は、クロック入力端子を有している。所定数の単位画素のそれぞれのクロック入力端子には、所定数の単位画素に対応するクロック信号が供給される。

本開示の第2の駆動方法は、互いに異なる位相を有する2以上のクロック信号を含む複数のクロック信号を生成し、複数のクロック信号のそれぞれに対応して所定数ずつ設けられ、それぞれがクロック入力端子を含む複数の単位画素を有する表示部に供給するものである。上記複数のクロック信号を表示部に供給する際、所定数の単位画素のそれぞれのクロック入力端子に、その所定数の単位画素に対応するクロック信号を供給する。

1.第1の実施の形態

2.第2の実施の形態

[構成例]

図1は、第1の実施の形態に係る表示装置の一構成例を表すものである。表示装置1は、LED(Light Emitting Diode)を表示素子として用いた表示パネルを有するテレビジョン装置である。なお、本開示の実施の形態に係る表示パネルおよびその駆動方法は、本実施の形態により具現化されるので、併せて説明する。

続いて、本実施の形態の表示装置1の動作および作用について説明する。

まず、図1などを参照して、表示装置1の全体動作概要を説明する。RF部11は、アンテナ19において受信された放送波(RF信号)に対して、ダウンコンバート等の処理を行う。復調部12は、RF部11から供給された信号に対して復調処理を行う。デマルチプレクサ部13は、復調部12から供給された信号(ストリーム)に多重化されたビデオ信号およびオーディオ信号から、これらの信号を分離する。デコーダ部14は、デマルチプレクサ部13から供給された信号(ビデオ信号およびオーディオ信号)をデコードする。信号変換部15は、信号のフォーマット変換を行い、映像信号Sdispとして出力する。

画素Pでは、制御部41がステートマシーンとして機能し、画素Pの動作を制御する。以下に、まず、制御部41の動作について、詳細に説明する。

表示装置1では、表示駆動部20が、表示部30における画素Pの各画素列に対して、信号S(1,1)〜S(M,1)を供給する。その際、表示駆動部20では、出力回路23(1)〜23(M)が4相のクロック信号CKA〜CKDに基づいてそれぞれ動作する。これにより、表示装置1では、各画素Pが誤動作するおそれを低減することができるため、画質の低下を抑えることができる。以下に、その詳細を説明する。

以上のように本実施の形態では、表示駆動部が、多相のクロック信号に基づいて信号を生成するようにしたので、画素が誤動作するおそれを低減することができ、表示装置の画質が低下するおそれを低減することができるとともに、部品のレイアウトなどの設計自由度を高めることができる。

上記実施の形態では、クロック生成部22は4相のクロック信号CKA〜CKDを生成したが、これに限定するものではなく、これに代えて、例えば、2相、3相、または5相以上のクロック信号を生成してもよい。以下に、2相のクロック信号CKA,CKCを生成する表示駆動部20Aを有する表示装置1Aについて、詳細に説明する。

上記実施の形態では、クロック信号CKA〜CKD(クロック信号CK(1,1)〜CK(4,1))のうちの隣り合うクロック信号間の位相差を90度にしたが、これに限定するものではなく、例えば、図11に示すように、90度以外の位相差にしてもよい。同様に、例えば、変形例1−1の表示装置1Aにおいて、クロック信号CKA,CKC(クロック信号CK(1,1),CK(2,1))の間の位相差を180度にしたが、これに限定するものではなく、例えば、図12に示すように、180度以外の位相差にしてもよい。

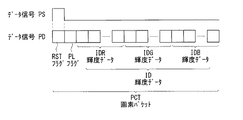

上記実施の形態では、クロック信号CKの周期を、データ信号PS,PDにおける1ビット分のパルス幅と同じにしたが、これに限定されるものではなく、これに代えて、図13に示すように、例えば、クロック信号CKの周期を、データ信号PS,PDにおける2ビット分のパルス幅と同じにしてもよい。この場合には、例えば、各画素Pのフリップフロップ42,44は、立ち上がりエッジと立ち下がりエッジの両方で動作する回路を用いることができる。

上記実施の形態では、クロック信号CKを各画素Pに供給したが、これに限定されるものではなく、これに代えて、例えば、差動のクロック信号を各画素に供給してもよい。以下に、本変形例に係る表示装置1Bについて詳細に説明する。

上記実施の形態では、DAC52R,52G,52Bを用いて駆動部50を構成したが、これに限定されるものではなく、これに代えて、例えば、カウンタを用いて駆動部を構成してもよい。以下に、本変形例に係る画素PCについて詳細に説明する。

次に、第2の実施の形態に係る表示装置2について説明する。本実施の形態は、各画素における遅延量を調整できるように構成されたものである。なお、上記第1の実施の形態に係る表示装置1と実質的に同一の構成部分には同一の符号を付し、適宜説明を省略する。

上記実施の形態では、フリップフロップ42とフリップフロップ44との間に遅延回路81を設け、フリップフロップ42とセレクタ部43との間に遅延回路82を設け、入力端子CKINとバッファ45との間に遅延回路83を設けたが、これに限定されるものではない。これに代えて、例えば図23に示す画素QAのように、フリップフロップ44と出力端子PSOUTとの間に遅延回路81Aを設け、フリップフロップ44と出力端子PDOUTとの間に遅延回路82Aを設け、バッファ45と出力端子CKOUTとの間に遅延回路83Aを設けてもよい。

上記実施の形態では、位相比較部90を設け、位相比較部90がクロック信号CKO(1)〜CKO(M)の位相を比較し、その比較結果に基づいて遅延データDDを設定するようにしたが、これに限定するものではなく、位相比較部90を設けなくてもよい。以下に、本変形例に係る表示装置2Bについて詳細に説明する。

上記実施の形態では、メモリ部86が輝度データIDに加えて遅延データDDをも記憶したが、これに限定されるものではない。以下に、本変形例に係る表示装置2Cについて詳細に説明する。

上記実施の形態では、各画素Qに遅延回路81〜83を設けたが、これに限定されるものではなく、これに代えて、全ての画素に遅延回路81〜83を設けなくてもよい。具体的には、例えば、各画素列において、遅延回路81〜83を設けた画素Qと、遅延回路81〜83を設けない画素Pとを交互に設けてもよい。

上記実施の形態に係る表示装置2に、上記第1の実施の形態に係る表示装置1の各変形例1−1〜1−5を適用してもよい。

互いに異なる位相を有する2以上のクロック信号を含む複数のクロック信号を生成し、前記表示部に供給する表示駆動部と

を備えた表示パネル。

前記複数のクロック信号のそれぞれは、前記2以上の基準クロック信号のうちのいずれかに対応する

前記(1)に記載の表示パネル。

各単位画素は、表示素子と、クロック入力端子と、クロック出力端子とを有し、

前記所定数の単位画素のうちの第1の単位画素のクロック入力端子には、前記表示駆動部から、前記複数のクロック信号のうちの1つが供給され、

前記所定数の単位画素のうちの前記第1の単位画素以外の一の単位画素のクロック入力端子は、前記所定数の単位画素のうちの他の単位画素のいずれかのクロック出力端子に接続されている

前記(1)または(2)に記載の表示パネル。

前記(3)に記載の表示パネル。

各単位画素は、データ入力端子と、データ出力端子とをさらに有し、

前記第1の単位画素のデータ入力端子には、前記表示駆動部から、前記複数のデータ信号のうちの1つが供給され、

前記所定数の単位画素のうちの前記第1の単位画素以外の一の単位画素の前記データ入力端子は、前記所定数の単位画素のうちの他の単位画素のいずれかのデータ出力端子に接続されている

前記(4)に記載の表示パネル。

前記(5)に記載の表示パネル。

前記(6)に記載の表示パネル。

前記(7)に記載の表示パネル。

前記(6)に記載の表示パネル。

前記(9)に記載の表示パネル。

各単位画素は、クロック入力端子を有し、

前記所定数の単位画素のそれぞれのクロック入力端子には、前記所定数の単位画素に対応するクロック信号が供給される

前記(1)または(2)に記載の表示パネル。

前記クロック入力端子は、差動信号の一方に対応する第1のクロック入力端子と、差動信号の他方に対応する第2のクロック入力端子からなり、

前記クロック出力端子は、差動信号の一方に対応する第1のクロック出力端子と、差動信号の他方に対応する第2のクロック出力端子からなる

前記(3)から(11)のいずれかに記載の表示パネル。

前記(1)から(12)のいずれかに記載の表示パネル。

前記(1)から(13)のいずれかに記載の表示パネル。

前記(1)に記載の表示パネル。

駆動方法。

前記表示パネルに対して動作制御を行う制御部と

を備え、

前記表示パネルは、

複数の単位画素を有する表示部と、

互いに異なる位相を有する2以上のクロック信号を含む複数のクロック信号を生成し、前記表示部に供給する表示駆動部と

を有する

電子機器。

Claims (17)

- 複数の単位画素を有する表示部と、

互いに異なる位相を有する2以上のクロック信号を含む複数のクロック信号を生成し、前記表示部に供給する表示駆動部と

を備え、

前記単位画素は、前記複数のクロック信号のそれぞれに対応して所定数ずつ設けられ、

各単位画素は、表示素子と、クロック入力端子と、クロック出力端子とを有し、

前記所定数の単位画素のうちの第1の単位画素のクロック入力端子には、前記表示駆動部から、前記複数のクロック信号のうちの1つが供給され、

前記所定数の単位画素のうちの前記第1の単位画素以外の一の単位画素のクロック入力端子は、前記所定数の単位画素のうちの他の単位画素のいずれかのクロック出力端子に接続されている

表示パネル。 - 前記表示駆動部は、互いに位相が異なる2以上の基準クロック信号を生成する多相クロック生成部を有し、

前記複数のクロック信号のそれぞれは、前記2以上の基準クロック信号のうちのいずれかに対応する

請求項1に記載の表示パネル。 - 前記所定数の単位画素のうちの少なくとも1つは、クロック入力端子からクロック出力端子への信号経路上に設けられた、遅延量を変更可能に構成された遅延回路を有する

請求項1または請求項2に記載の表示パネル。 - 前記表示駆動部は、前記複数のクロック信号に対応する複数のデータ信号をも生成し、

各単位画素は、データ入力端子と、データ出力端子とをさらに有し、

前記第1の単位画素のデータ入力端子には、前記表示駆動部から、前記複数のデータ信号のうちの1つが供給され、

前記所定数の単位画素のうちの前記第1の単位画素以外の一の単位画素の前記データ入力端子は、前記所定数の単位画素のうちの他の単位画素のいずれかのデータ出力端子に接続されている

請求項3に記載の表示パネル。 - 各データ信号は、前記表示素子の輝度を画定する輝度データと、前記遅延回路の遅延量を画定する遅延データとを含む

請求項4に記載の表示パネル。 - 前記所定数の単位画素のうちの最終段である第2の単位画素のクロック出力端子から出力されるクロック信号の位相を比較する位相比較部をさらに備えた

請求項5に記載の表示パネル。 - 前記位相比較部は、比較結果に基づいて、前記遅延データを決定する

請求項6に記載の表示パネル。 - 前記所定数の単位画素のうちの最終段である第2の単位画素のクロック出力端子から出力されるクロック信号を外部から検出するための外部端子をさらに備えた

請求項7に記載の表示パネル。 - 前記表示駆動部は、前記遅延データを記憶するメモリを有する

請求項8に記載の表示パネル。 - 各データ信号は、デジタル信号である

請求項4から請求項9のいずれか一項に記載の表示パネル。 - 各クロック信号は、差動信号であり、

前記クロック入力端子は、差動信号の一方に対応する第1のクロック入力端子と、差動信号の他方に対応する第2のクロック入力端子からなり、

前記クロック出力端子は、差動信号の一方に対応する第1のクロック出力端子と、差動信号の他方に対応する第2のクロック出力端子からなる

請求項1から請求項10のいずれか一項に記載の表示パネル。 - 前記表示素子は、LED表示素子である

請求項1から請求項11のいずれか一項に記載の表示パネル。 - 前記表示駆動部は、前記2以上のクロック信号の位相差をそれぞれ画定する1または複数の遅延回路を有する

請求項1に記載の表示パネル。 - 複数の単位画素を有する表示部と、

互いに異なる位相を有する2以上のクロック信号を含む複数のクロック信号を生成し、前記表示部に供給する表示駆動部と

を備え、

前記単位画素は、前記複数のクロック信号のそれぞれに対応して所定数ずつ設けられ、

各単位画素は、クロック入力端子を有し、

前記所定数の単位画素のそれぞれのクロック入力端子には、前記所定数の単位画素に対応するクロック信号が供給される

表示パネル。 - 互いに異なる位相を有する2以上のクロック信号を含む複数のクロック信号を生成し、

前記複数のクロック信号のそれぞれに対応して所定数ずつ設けられ、それぞれが表示素子と、クロック入力端子と、クロック出力端子とを含む複数の単位画素を有する表示部に供給し、

前記複数のクロック信号を前記表示部に供給する際、

前記所定数の単位画素のうちの第1の単位画素のクロック入力端子に、前記複数のクロック信号のうちの1つを供給し、

前記所定数の単位画素のうちの前記第1の単位画素以外の一の単位画素のクロック入力端子に、前記所定数の単位画素のうちの他の単位画素のいずれかのクロック出力端子から出力されたクロック信号を供給する

駆動方法。 - 互いに異なる位相を有する2以上のクロック信号を含む複数のクロック信号を生成し、

前記複数のクロック信号のそれぞれに対応して所定数ずつ設けられ、それぞれがクロック入力端子を含む複数の単位画素を有する表示部に供給し、

前記複数のクロック信号を前記表示部に供給する際、前記所定数の単位画素のそれぞれのクロック入力端子に、前記所定数の単位画素に対応するクロック信号を供給する

駆動方法。 - 表示パネルと

前記表示パネルに対して動作制御を行う制御部と

を備え、

前記表示パネルは、

複数の単位画素を有する表示部と、

互いに異なる位相を有する2以上のクロック信号を含む複数のクロック信号を生成し、

前記表示部に供給する表示駆動部と

を有し、

前記単位画素は、前記複数のクロック信号のそれぞれに対応して所定数ずつ設けられ、

各単位画素は、表示素子と、クロック入力端子と、クロック出力端子とを有し、

前記所定数の単位画素のうちの第1の単位画素のクロック入力端子には、前記表示駆動部から、前記複数のクロック信号のうちの1つが供給され、

前記所定数の単位画素のうちの前記第1の単位画素以外の一の単位画素のクロック入力端子は、前記所定数の単位画素のうちの他の単位画素のいずれかのクロック出力端子に接続されている

電子機器。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013177535A JP6115407B2 (ja) | 2013-08-29 | 2013-08-29 | 表示パネル、その駆動方法、および電子機器 |

| US14/457,192 US20150061979A1 (en) | 2013-08-29 | 2014-08-12 | Display panel, method of driving the same, and electronic apparatus |

| CN201410419677.9A CN104424888B (zh) | 2013-08-29 | 2014-08-22 | 显示面板及其驱动方法、以及电子设备 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013177535A JP6115407B2 (ja) | 2013-08-29 | 2013-08-29 | 表示パネル、その駆動方法、および電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015045777A JP2015045777A (ja) | 2015-03-12 |

| JP2015045777A5 JP2015045777A5 (ja) | 2016-03-03 |

| JP6115407B2 true JP6115407B2 (ja) | 2017-04-19 |

Family

ID=52582471

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013177535A Expired - Fee Related JP6115407B2 (ja) | 2013-08-29 | 2013-08-29 | 表示パネル、その駆動方法、および電子機器 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20150061979A1 (ja) |

| JP (1) | JP6115407B2 (ja) |

| CN (1) | CN104424888B (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6070524B2 (ja) * | 2013-12-04 | 2017-02-01 | ソニー株式会社 | 表示パネル、駆動方法、および電子機器 |

| WO2016084544A1 (ja) * | 2014-11-25 | 2016-06-02 | ソニー株式会社 | 画素ユニット、表示パネル、および信号伝送方法 |

| KR102542853B1 (ko) | 2016-04-25 | 2023-06-14 | 삼성전자주식회사 | Led 디스플레이 모듈, 디스플레이 장치 및 제어 방법 |

| TWI678923B (zh) * | 2018-05-25 | 2019-12-01 | 友達光電股份有限公司 | 具雜訊抑制設計的顯示面板 |

| KR102544520B1 (ko) * | 2018-07-12 | 2023-06-16 | 엘지디스플레이 주식회사 | 표시장치와 그 구동 방법 |

| US11468821B2 (en) * | 2020-08-17 | 2022-10-11 | Novatek Microelectronics Corp. | Source driving circuit and operating method thereof |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6288699B1 (en) * | 1998-07-10 | 2001-09-11 | Sharp Kabushiki Kaisha | Image display device |

| JP2004226684A (ja) * | 2003-01-23 | 2004-08-12 | Sony Corp | 画像表示パネルおよび画像表示装置 |

| JP2007518066A (ja) * | 2003-11-11 | 2007-07-05 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 電子ユニットをアドレッシングするための回路 |

| JP2005351920A (ja) * | 2004-06-08 | 2005-12-22 | Semiconductor Energy Lab Co Ltd | 表示装置の制御回路及びそれを内蔵した表示装置・電子機器並びにその駆動方法 |

| JP2006330138A (ja) * | 2005-05-24 | 2006-12-07 | Casio Comput Co Ltd | 表示装置及びその表示駆動方法 |

| JP5051776B2 (ja) * | 2008-04-10 | 2012-10-17 | シャープ株式会社 | 表示装置の駆動回路 |

| TWI482143B (zh) * | 2008-08-19 | 2015-04-21 | Au Optronics Corp | 液晶顯示器的驅動裝置 |

| KR100986041B1 (ko) * | 2008-10-20 | 2010-10-07 | 주식회사 실리콘웍스 | 클럭 신호가 임베딩된 단일 레벨 신호 전송을 이용한 디스플레이 구동 시스템 |

| KR101502834B1 (ko) * | 2008-11-04 | 2015-03-17 | 삼성디스플레이 주식회사 | 광원 모듈의 구동 장치, 이 구동 장치를 갖는 광원 장치, 광원 모듈의 구동 방법 및 이 구동 장치를 갖는 표시 장치 |

| JP2010170104A (ja) * | 2008-12-26 | 2010-08-05 | Rohm Co Ltd | タイミングコントロール回路およびそれを用いたディスプレイ装置 |

| JP2010217568A (ja) * | 2009-03-17 | 2010-09-30 | Sharp Corp | 表示装置 |

| US8305368B2 (en) * | 2009-08-19 | 2012-11-06 | Himax Technologies Limited | Method for determining an optimum skew and adjusting a clock phase of a pixel clock signal and data driver utilizing the same |

| KR20110037339A (ko) * | 2009-10-06 | 2011-04-13 | 삼성전자주식회사 | 전자 장치, 디스플레이 장치 그리고 디스플레이 장치의 제어 방법 |

| JP5796944B2 (ja) * | 2010-10-04 | 2015-10-21 | ラピスセミコンダクタ株式会社 | 表示パネル駆動装置 |

-

2013

- 2013-08-29 JP JP2013177535A patent/JP6115407B2/ja not_active Expired - Fee Related

-

2014

- 2014-08-12 US US14/457,192 patent/US20150061979A1/en not_active Abandoned

- 2014-08-22 CN CN201410419677.9A patent/CN104424888B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015045777A (ja) | 2015-03-12 |

| CN104424888A (zh) | 2015-03-18 |

| CN104424888B (zh) | 2019-03-08 |

| US20150061979A1 (en) | 2015-03-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9905151B2 (en) | Display panel having daisy-chain-connected pixels, pixel chip, and electronic apparatus | |

| USRE48358E1 (en) | Emission control driver and organic light emitting display device having the same | |

| JP6115407B2 (ja) | 表示パネル、その駆動方法、および電子機器 | |

| US10217395B2 (en) | Display device, source drive integrated circuit, timing controller and driving method thereof | |

| US9747854B2 (en) | Shift register, gate driving circuit, method for driving display panel and display device | |

| US9734757B2 (en) | Gate driver integrated circuit, and image display apparatus including the same | |

| JP7482936B2 (ja) | ゲート駆動部およびこれを用いた電界発光表示装置 | |

| CN104900192A (zh) | 移位寄存器单元及其驱动方法、栅极驱动电路、显示装置 | |

| WO2016084544A1 (ja) | 画素ユニット、表示パネル、および信号伝送方法 | |

| US20070146290A1 (en) | Device for driving a display panel | |

| KR100740476B1 (ko) | 디스플레이 장치, 디스플레이 드라이버 및 데이터 전송방법 | |

| JP2022510053A (ja) | シフトレジスタユニット、走査駆動回路及びその駆動方法、並びに表示装置 | |

| US10607563B2 (en) | Display device and method of driving the same | |

| KR100836437B1 (ko) | 데이터구동부 및 그를 이용한 유기전계발광표시장치 | |

| CN112532236A (zh) | 时钟数据恢复电路 | |

| US9424773B2 (en) | Display panel, method of driving the same, and electronic apparatus | |

| US8390559B2 (en) | Display driving apparatus, display module package, display panel module, and television set | |

| JP2003036054A (ja) | 表示装置 | |

| JP2008262132A (ja) | 表示駆動装置および表示装置 | |

| KR102706505B1 (ko) | 발광표시장치 및 이의 구동방법 | |

| JPH1049102A (ja) | 信号線選択回路およびマトリクス型表示装置 | |

| KR20110093371A (ko) | 디스플레이 장치 및 디스플레이 장치의 동작 방법 | |

| KR20060093239A (ko) | 평판표시장치의 스캔 드라이버용 양방향 시프트 레지스터 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160114 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160114 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160928 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161004 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161107 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170221 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170306 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6115407 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |