JP6070524B2 - 表示パネル、駆動方法、および電子機器 - Google Patents

表示パネル、駆動方法、および電子機器 Download PDFInfo

- Publication number

- JP6070524B2 JP6070524B2 JP2013250779A JP2013250779A JP6070524B2 JP 6070524 B2 JP6070524 B2 JP 6070524B2 JP 2013250779 A JP2013250779 A JP 2013250779A JP 2013250779 A JP2013250779 A JP 2013250779A JP 6070524 B2 JP6070524 B2 JP 6070524B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- data

- unit

- display panel

- detection

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims description 10

- 238000001514 detection method Methods 0.000 claims description 247

- 101100194363 Schizosaccharomyces pombe (strain 972 / ATCC 24843) res2 gene Proteins 0.000 description 77

- 101150037117 pct-1 gene Proteins 0.000 description 77

- 238000012937 correction Methods 0.000 description 29

- 238000010586 diagram Methods 0.000 description 21

- 230000004048 modification Effects 0.000 description 19

- 238000012986 modification Methods 0.000 description 19

- 238000012546 transfer Methods 0.000 description 18

- 238000006243 chemical reaction Methods 0.000 description 17

- 101000685663 Homo sapiens Sodium/nucleoside cotransporter 1 Proteins 0.000 description 14

- 102100023116 Sodium/nucleoside cotransporter 1 Human genes 0.000 description 14

- 230000006870 function Effects 0.000 description 12

- 238000005401 electroluminescence Methods 0.000 description 7

- 230000008859 change Effects 0.000 description 6

- 239000011159 matrix material Substances 0.000 description 5

- 230000003287 optical effect Effects 0.000 description 5

- 230000005540 biological transmission Effects 0.000 description 4

- 239000000872 buffer Substances 0.000 description 4

- 238000012545 processing Methods 0.000 description 4

- 230000005855 radiation Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 3

- 230000001151 other effect Effects 0.000 description 3

- 230000009471 action Effects 0.000 description 2

- 230000002238 attenuated effect Effects 0.000 description 2

- 230000003111 delayed effect Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 206010047571 Visual impairment Diseases 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 238000007493 shaping process Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/14—Digital output to display device ; Cooperation and interconnection of the display device with other functional units

- G06F3/1423—Digital output to display device ; Cooperation and interconnection of the display device with other functional units controlling a plurality of local displays, e.g. CRT and flat panel display

- G06F3/1446—Digital output to display device ; Cooperation and interconnection of the display device with other functional units controlling a plurality of local displays, e.g. CRT and flat panel display display composed of modules, e.g. video walls

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/02—Composition of display devices

- G09G2300/026—Video wall, i.e. juxtaposition of a plurality of screens to create a display screen of bigger dimensions

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/0452—Details of colour pixel setup, e.g. pixel composed of a red, a blue and two green components

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0283—Arrangement of drivers for different directions of scanning

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/08—Details of timing specific for flat panels, other than clock recovery

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/06—Adjustment of display parameters

- G09G2320/0626—Adjustment of display parameters for control of overall brightness

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2360/00—Aspects of the architecture of display systems

- G09G2360/14—Detecting light within display terminals, e.g. using a single or a plurality of photosensors

- G09G2360/141—Detecting light within display terminals, e.g. using a single or a plurality of photosensors the light conveying information used for selecting or modulating the light emitting or modulating element

- G09G2360/142—Detecting light within display terminals, e.g. using a single or a plurality of photosensors the light conveying information used for selecting or modulating the light emitting or modulating element the light being detected by light detection means within each pixel

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2370/00—Aspects of data communication

- G09G2370/10—Use of a protocol of communication by packets in interfaces along the display data pipeline

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2370/00—Aspects of data communication

- G09G2370/18—Use of optical transmission of display information

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Control Of El Displays (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Electroluminescent Light Sources (AREA)

- Transforming Electric Information Into Light Information (AREA)

Description

1.第1の実施の形態

2.第2の実施の形態

3.第3の実施の形態

4.第4の実施の形態

5.適用例

[構成例]

(全体構成例)

図1は、第1の実施の形態に係る表示パネルの一構成例を表すものである。表示パネル1は、画像を表示するとともに光を検出することができる表示パネルである。なお、本開示の実施の形態に係る駆動方法および電子機器は、本実施の形態により具現化されるので、併せて説明する。表示パネル1は、制御部10と、ドライバ部12と、表示部20と、レシーバ部13とを備えている。

図5は、画素Pの一構成例を表すものである。画素Pは、クロックバッファ25,26と、制御部21と、発光制御部22と、発光部23と、光検出部24とを有している。なお、以下では、説明の便宜上、デイジーチェーン接続されたN個の画素Pのうちの初段の画素P(0)を用いて説明するが、その他の画素P(1)〜P(N−1)においても同様である。

続いて、本実施の形態の表示パネル1の動作および作用について説明する。

まず、図1などを参照して、表示パネル1の全体動作概要を説明する。制御部10は、映像信号Sdisp0に基づいて、ドライバ部12の動作に必要な様々な信号を生成し、これらの信号を輝度データIDとともに映像信号Sdispとしてドライバ部12に供給する。その際、制御部10の輝度データ生成部11は、レシーバ部13から供給される検出信号Sdetに基づいて、光を検出した位置に配置された画素Pの輝度データIDを生成し、映像信号Sdisp0により供給された1フレーム画像分の輝度データIDのうちの、この画素Pに対応する輝度データIDを、この生成した輝度データIDに置き換える。ドライバ部12は、映像信号Sdispに基づいて、表示部20の画素Pの各画素列に対して、データ信号PS、PDおよびクロック信号CKを供給する。各画素Pは、データ信号PS,PDおよびクロック信号CKを用いて画素パケットPCT1,PCT2を転送する。その際、各画素Pは、スタートフラグSFが“0”である画素パケットPCT1,PCT2が供給された場合には、その画素パケットPCT1,PCT2をそのまま後段の画素Pに供給する。また、各画素Pは、スタートフラグSFが“1”である画素パケットPCT1が供給された場合には、その画素パケットPCT1における輝度データIDおよび制御データCDを読み出す。その際、各画素Pは、その画素パケットPCT1のうちのスタートフラグSFを“0”に変更するとともに輝度データIDおよび制御データCDを検出データSDに置き換えることにより、画素パケットPCT2を生成し、後段の画素Pに供給する。さらに、各画素Pは、次の画素パケットPCT1におけるスタートフラグSFを“1”に設定する。各画素Pは、読み出した輝度データIDおよび制御データCD(発光タイミングデータETD)に基づいて表示動作を行うとともに、読み出した制御データCD(検出タイミングデータSTD)に基づいて光検出動作を行い、検出データSDを生成する。レシーバ部13は、最後段の画素Pから供給されたデータ信号PS(N),PD(N)およびクロック信号CK(N)に基づいて、画素パケットPCT2に含まれる検出データSDを取得し、表示部20の全画素P分の検出データSDを、検出信号Sdetとして制御部10に供給する。

次に、画素Pの動作について詳細に説明する。まず最初に、画素パケットPCT1,PCT2の転送動作について説明する。

図9は、画素Pの一動作例を示すフローチャートを表すものである。図10は、画素Pの一動作例を表すタイミング図を表すものである。図10(D)〜(F)において、“ON”は発光素子23R,23G,23Bが発光していることを示し、“OFF”は発光素子23R,23G,23Bが消光していることを示す。また、図10(G)において、“ON”は光検出部24が光を検出していることを示し、“OFF”は光検出部24が光を検出していないことを示す。画素Pは、1フレーム期間において、表示動作と光検出動作とを時分割的に行う。以下に、その詳細を説明する。

以上のように本実施の形態では、発光素子が発光動作を行わない期間に光検出動作を行うようにしたので、時間を有効活用して光検出動作を行うことができる。

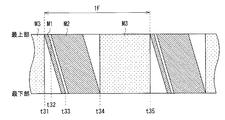

上記実施の形態では、ドライバ部12を表示部20の下側に配置したが、これに限定されるものではなく、これに代えて、例えば、図12に示す表示パネル1Aのように、表示部20の上側に配置してもよい。この場合には、表示パネル1Aは、図13に示すように、表示部20の最上部から最下部に向かって画素パケットPCT1,PCT2を順次転送するとともに、最上部から最下部に向かって表示動作M2を順次開始する。具体的には、表示部20は、タイミングt31〜t33の期間において転送動作M1を行い、タイミングt33より前のタイミングt32から、タイミングt34までの期間において表示動作M2を行う。これにより、表示パネル1Aでは、表示パネル1の場合に比べて、例えば、光検出動作M3を行う期間(タイミングt34〜t35)を長く設定することができる。

上記実施の形態に係る表示パネル1を複数枚並べて、大きな表示装置を構成してもよい。以下に、いくつかの例を挙げて本変形例について説明する。

上記実施の形態では、各画素Pは、発光素子23R,23G,23Bの発光時間の長さによって輝度の階調を表現したが、これに限定されるものではなく、これに代えて、例えば、発光素子23R,23G,23Bが発する光の強度によって輝度の階調を表現してもよい。

上記実施の形態では、デイジーチェーン接続されたN個の画素Pのすべてが光検出動作を行うようにしたが、これに限定されるものではなく、これに代えて、例えば、N個の画素Pのうちの一部が光検出動作を行うようにしてもよい。また、上記実施の形態では、光検出部24を有するN個の画素Pをデイジーチェーン接続したが、これに限定されるものではなく、これに代えて、例えば、光検出部24を有しない複数の画素と、光検出部24を有する複数の画素Pとをデイジーチェーン接続してもよい。具体的には、例えば、光検出部24を有しない画素と、検出部24を有する画素Pとを交互に配置することができる。

上記実施の形態では、光検出動作M3を表示部20の全面にわたり同じ期間に行うようにしたが、これに限定されるものではなく、これに代えて、例えば、表示動作M2と同様に、表示画面の最上部から順に行うようにしてもよい。

次に、第2の実施の形態に係る表示パネル2について説明する。本実施の形態は、画像を表示するとともに、いわゆるイメージスキャナとしても機能する表示部を用いたものである。なお、上記第1の実施の形態に係る表示パネル1と実質的に同一の構成部分には同一の符号を付し、適宜説明を省略する。

上記実施の形態に係る表示パネル2に、上記第1の実施の形態の各変形例を適用してもよい。

次に、第3の実施の形態に係る表示パネル3について説明する。本実施の形態は、表示部における輝度の経時変化を補正する機能を有するものである。なお、上記第1の実施の形態に係る表示パネル1などと実質的に同一の構成部分には同一の符号を付し、適宜説明を省略する。

上記実施の形態に係る表示パネル3に、上記第1の実施の形態の各変形例を適用してもよい。

次に、第4の実施の形態に係る表示パネル4について説明する。本実施の形態は、表示部における輝度の温度依存性を補正する機能を有するものである。なお、上記第1の実施の形態に係る表示パネル1などと実質的に同一の構成部分には同一の符号を付し、適宜説明を省略する。

上記実施の形態に係る表示パネル4に、上記第1の実施の形態の各変形例を適用してもよい。

次に、上記実施の形態および変形例で説明した表示パネルの適用例について説明する。

順次接続され、それぞれが、前記第1の画素パケットの前記デジタル輝度データに基づいて表示動作を行うとともに、少なくとも1つが、自画素における物理量の検出動作を行い、その検出動作により得られたデジタル検出データを含む第2の画素パケットを生成して次段に出力する複数の単位画素と、

前記第2の画素パケットを受け取るレシーバ部と

を備えた表示パネル。

各単位画素は、前記フラグデータの値に基づいて、入力された第1の画素パケットに含まれるデジタル輝度データを読み込むか否かを判断する

前記(1)に記載の表示パネル。

各単位画素は、

入力された第1の画素パケットの前記フラグデータが前記第1のフラグ値を示す場合には、その第1の画素パケットをそのまま出力し、

入力された第1の画素パケットの前記フラグデータが前記第2のフラグ値を示す場合には、その第1の画素パケットに含まれるデジタル輝度データを読み出すとともに、前記第2の画素パケットを生成する

前記(3)に記載の表示パネル。

各単位画素は、第2の画素パケットを生成し出力した後の最初の第1の画素パケットにおけるフラグデータを前記第2のフラグ値に設定する

前記(3)に記載の表示パネル。

前記(1)から(4)のいずれかに記載の表示パネル。

前記(1)から(5)のいずれかに記載の表示パネル。

各単位画素は、前記フラグデータに基づいてカウント値が初期化される基準カウンタを有し、その基準カウンタのカウント値に基づいて表示動作および検出動作を行う

前記(1)から(6)のいずれかに記載の表示パネル。

前記(1)から(7)のいずれかに記載の表示パネル。

前記(8)に記載の表示パネル。

前記(8)に記載の表示パネル。

前記光検出素子は、その光検出素子を有する単位画素が前記所定光を発しているときに光を検出する

前記(8)に記載の表示パネル。

前記(1)から(7)のいずれかに記載の表示パネル。

前記レシーバ部は、前記第2の画素パケットにおける前記デジタル検出データを前記輝度データ生成部に供給し、

前記輝度データ生成部は、前記デジタル検出データに基づいて、前記複数の単位画素のうちの1または複数の単位画素のデジタル輝度データを生成して前記ドライバ部に供給する

前記(8)から(12)のいずれかに記載の表示パネル。

前記(13)に記載の表示パネル。

順次接続された複数の単位画素のそれぞれが、前記第1の画素パケットの前記デジタル輝度データに基づいて表示動作を行うとともに、前記複数の単位画素のうちの少なくとも1つが、自画素における物理量の検出動作を行い、その検出動作により得られたデジタル検出データを含む第2の画素パケットを生成して次段に出力する

駆動方法。

前記表示パネルに対して動作制御を行う制御部と

を備え、

前記表示パネルは、

デジタル輝度データを含む第1の画素パケットを生成するドライバ部と、

順次接続され、それぞれが、前記第1の画素パケットの前記デジタル輝度データに基づいて表示動作を行うとともに、少なくとも1つが、自画素における物理量の検出動作を行い、その検出動作により得られたデジタル検出データを含む第2の画素パケットを生成して次段に出力する複数の単位画素と、

前記第2の画素パケットを受け取るレシーバ部と

を有する

電子機器。

Claims (16)

- デジタル輝度データを含む第1の画素パケットを生成するドライバ部と、

順次接続され、それぞれが、前記第1の画素パケットの前記デジタル輝度データに基づいて表示動作を行うとともに、少なくとも1つが、自画素における物理量の検出動作を行い、その検出動作により得られたデジタル検出データを含む第2の画素パケットを生成して次段に出力する複数の単位画素と、

前記第2の画素パケットを受け取るレシーバ部と

を備えた表示パネル。 - 前記第1の画素パケットは、フラグデータをさらに含み、

各単位画素は、前記フラグデータの値に基づいて、入力された第1の画素パケットに含まれるデジタル輝度データを読み込むか否かを判断する

請求項1に記載の表示パネル。 - 前記フラグデータは、第1のフラグ値または第2のフラグ値を示し、

各単位画素は、

入力された第1の画素パケットの前記フラグデータが前記第1のフラグ値を示す場合には、その第1の画素パケットをそのまま出力し、

入力された第1の画素パケットの前記フラグデータが前記第2のフラグ値を示す場合には、その第1の画素パケットに含まれるデジタル輝度データを読み出すとともに、前記第2の画素パケットを生成する

請求項2に記載の表示パネル。 - 前記第2の画素パケットは、前記第1のフラグ値を示すフラグデータをさらに含み、

各単位画素は、第2の画素パケットを生成し出力した後の最初の第1の画素パケットにおけるフラグデータを前記第2のフラグ値に設定する

請求項3に記載の表示パネル。 - 前記第1の画素パケットは、単位画素における表示動作の開始タイミングを示す第1の制御データをさらに含む

請求項1に記載の表示パネル。 - 前記第1の画素パケットは、単位画素における検出動作の開始タイミングを示す第2の制御データをさらに含む

請求項1に記載の表示パネル。 - 前記第1の画素パケットは、フラグデータをさらに含み、

各単位画素は、前記フラグデータに基づいてカウント値が初期化される基準カウンタを有し、その基準カウンタのカウント値に基づいて表示動作および検出動作を行う

請求項1に記載の表示パネル。 - 各単位画素は、光検出素子を有し、その光検出素子による検出値に基づいて前記デジタル検出データを生成する

請求項1に記載の表示パネル。 - 前記光検出素子は、その光検出素子を有する単位画素が表示動作を行っていないときに光を検出する

請求項8に記載の表示パネル。 - 前記光検出素子は、その光検出素子を有する単位画素が表示動作を行っているときに光を検出する

請求項8に記載の表示パネル。 - 各単位画素は、所定光を発し、

前記光検出素子は、その光検出素子を有する単位画素が前記所定光を発しているときに光を検出する

請求項8に記載の表示パネル。 - 各単位画素は、温度検出素子を有し、その温度検出素子による検出値に基づいて前記デジタル検出データを生成する

請求項1に記載の表示パネル。 - 輝度データ生成部をさらに備え、

前記レシーバ部は、前記第2の画素パケットにおける前記デジタル検出データを前記輝度データ生成部に供給し、

前記輝度データ生成部は、前記デジタル検出データに基づいて、前記複数の単位画素のうちの1または複数の単位画素のデジタル輝度データを生成して前記ドライバ部に供給する

請求項8に記載の表示パネル。 - 前記輝度データ生成部は、前記デジタル検出データに基づいて、そのデジタル検出データを生成した単位画素におけるデジタル輝度データを生成する

請求項13に記載の表示パネル。 - デジタル輝度データを含む第1の画素パケットを生成し、

順次接続された複数の単位画素のそれぞれが、前記第1の画素パケットの前記デジタル輝度データに基づいて表示動作を行うとともに、前記複数の単位画素のうちの少なくとも1つが、自画素における物理量の検出動作を行い、その検出動作により得られたデジタル検出データを含む第2の画素パケットを生成して次段に出力する

駆動方法。 - 表示パネルと

前記表示パネルに対して動作制御を行う制御部と

を備え、

前記表示パネルは、

デジタル輝度データを含む第1の画素パケットを生成するドライバ部と、

順次接続され、それぞれが、前記第1の画素パケットの前記デジタル輝度データに基づいて表示動作を行うとともに、少なくとも1つが、自画素における物理量の検出動作を行い、その検出動作により得られたデジタル検出データを含む第2の画素パケットを生成して次段に出力する複数の単位画素と、

前記第2の画素パケットを受け取るレシーバ部と

を有する

電子機器。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013250779A JP6070524B2 (ja) | 2013-12-04 | 2013-12-04 | 表示パネル、駆動方法、および電子機器 |

| US14/533,532 US9495911B2 (en) | 2013-12-04 | 2014-11-05 | Display panel, driving method, and electronic apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013250779A JP6070524B2 (ja) | 2013-12-04 | 2013-12-04 | 表示パネル、駆動方法、および電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015108695A JP2015108695A (ja) | 2015-06-11 |

| JP2015108695A5 JP2015108695A5 (ja) | 2016-03-03 |

| JP6070524B2 true JP6070524B2 (ja) | 2017-02-01 |

Family

ID=53265810

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013250779A Active JP6070524B2 (ja) | 2013-12-04 | 2013-12-04 | 表示パネル、駆動方法、および電子機器 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9495911B2 (ja) |

| JP (1) | JP6070524B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20170330508A1 (en) * | 2014-11-25 | 2017-11-16 | Sony Corporation | Pixel unit, display panel, and method of transmitting signal |

| JP2019012106A (ja) * | 2017-06-29 | 2019-01-24 | 株式会社ジャパンディスプレイ | 画像処理装置、画像処理装置の画像処理方法、及びそれらを実装した表示システム |

| KR102555144B1 (ko) * | 2017-12-29 | 2023-07-12 | 엘지디스플레이 주식회사 | 디스플레이 장치 |

| KR102573291B1 (ko) * | 2017-12-29 | 2023-08-30 | 엘지디스플레이 주식회사 | 발광 표시 장치 |

| WO2019217242A1 (en) * | 2018-05-08 | 2019-11-14 | Apple Inc. | Memory-in-pixel display |

| US10909926B2 (en) | 2018-05-08 | 2021-02-02 | Apple Inc. | Pixel circuitry and operation for memory-containing electronic display |

| CN109151538B (zh) * | 2018-09-17 | 2021-02-05 | 深圳Tcl新技术有限公司 | 图像显示方法、装置、智能电视及可读存储介质 |

| EP3706109A1 (de) | 2019-03-08 | 2020-09-09 | Continental Automotive GmbH | Hintergrund-beleuchtungsmatrix für eine anzeigevorrichtung zum anzeigen von bildern, anzeigevorrichtung sowie fahrzeug |

| KR20210053629A (ko) | 2019-11-04 | 2021-05-12 | 삼성전자주식회사 | 디스플레이 장치 및 그 제어 방법 |

| KR20220016346A (ko) * | 2020-07-30 | 2022-02-09 | 삼성디스플레이 주식회사 | 표시 장치 |

| FR3123493B1 (fr) * | 2021-05-26 | 2023-05-26 | Commissariat Energie Atomique | Dispositif d’affichage a adressage par groupes de pixels |

Family Cites Families (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1994018809A1 (en) * | 1993-02-11 | 1994-08-18 | Phares Louis A | Controlled lighting system |

| JPH08298649A (ja) * | 1995-04-27 | 1996-11-12 | Oki Electric Ind Co Ltd | 映像符号化・復号化システム、映像符号化装置及び映像復号化装置 |

| JP3854790B2 (ja) * | 2000-08-22 | 2006-12-06 | キヤノン株式会社 | 画像処理装置及び方法及び記憶媒体 |

| US7865306B2 (en) * | 2000-09-28 | 2011-01-04 | Michael Mays | Devices, methods, and systems for managing route-related information |

| JP4284390B2 (ja) * | 2002-06-27 | 2009-06-24 | ソニー株式会社 | アクティブマトリクス表示装置及び画像信号処理装置 |

| US7405719B2 (en) * | 2003-05-01 | 2008-07-29 | Genesis Microchip Inc. | Using packet transfer for driving LCD panel driver electronics |

| US7391898B2 (en) * | 2003-10-10 | 2008-06-24 | Nova Packaging Systems, Inc. | Method and apparatus for programmable zoned array counter |

| WO2005069639A1 (en) * | 2004-01-05 | 2005-07-28 | Koninklijke Philips Electronics, N.V. | Ambient light derived by subsampling video content and mapped through unrendered color space |

| JP5370454B2 (ja) | 2004-04-12 | 2013-12-18 | 三洋電機株式会社 | 有機el画素回路およびその駆動方法 |

| US7280112B1 (en) * | 2004-05-14 | 2007-10-09 | Nvidia Corporation | Arithmetic logic unit temporary registers |

| US7375701B2 (en) * | 2004-07-01 | 2008-05-20 | Carestream Health, Inc. | Scanless virtual retinal display system |

| WO2006098246A1 (ja) * | 2005-03-15 | 2006-09-21 | Sharp Kabushiki Kaisha | 液晶表示装置の駆動方法、液晶表示装置の駆動装置、そのプログラムおよび記録媒体、並びに、液晶表示装置 |

| US7348988B2 (en) * | 2005-05-06 | 2008-03-25 | Via Technologies, Inc. | Texture cache control using an adaptive missing data table in a multiple cache computer graphics environment |

| US7864999B2 (en) * | 2005-10-19 | 2011-01-04 | Siemens Medical Solutions Usa, Inc. | Devices systems and methods for processing images |

| KR101160837B1 (ko) * | 2005-10-26 | 2012-06-29 | 삼성전자주식회사 | 접촉 감지 기능이 있는 표시 장치 |

| JP2008070715A (ja) * | 2006-09-15 | 2008-03-27 | Renesas Technology Corp | 半導体集積回路及び携帯端末システム |

| US8739035B2 (en) * | 2006-10-11 | 2014-05-27 | Intel Corporation | Controls and indicators with on-screen cognitive aids |

| AR064274A1 (es) * | 2006-12-14 | 2009-03-25 | Panasonic Corp | Metodo de codificacion de imagenes en movimiento, dispositivo de codificacion de imagenes en movimiento, metodo de grabacion de imagenes en movimiento, medio de grabacion, metodo de reproduccion de imagenes en movimiento, dispositivo de reproduccion de imagenes en movimiento, y sistema de reproducci |

| KR101359917B1 (ko) * | 2006-12-15 | 2014-02-07 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| KR101393629B1 (ko) * | 2007-01-17 | 2014-05-09 | 삼성디스플레이 주식회사 | 표시 장치 및 그 구동 방법 |

| US8374383B2 (en) * | 2007-03-08 | 2013-02-12 | Microscan Systems, Inc. | Systems, devices, and/or methods for managing images |

| US20080278598A1 (en) * | 2007-05-11 | 2008-11-13 | Michael Philip Greenberg | Devices, Systems, and Methods Regarding Camera Imaging |

| US8736624B1 (en) * | 2007-08-15 | 2014-05-27 | Nvidia Corporation | Conditional execution flag in graphics applications |

| JP5320738B2 (ja) * | 2007-12-28 | 2013-10-23 | ソニー株式会社 | 発光制御システムおよび画像表示システム |

| US8890773B1 (en) * | 2009-04-01 | 2014-11-18 | Federal Law Enforcement Development Services, Inc. | Visible light transceiver glasses |

| CN102667404B (zh) * | 2009-10-29 | 2015-11-25 | 通腾北美有限公司 | 用探测数据来分析兴趣点的方法 |

| JP5501041B2 (ja) * | 2010-03-15 | 2014-05-21 | キヤノン株式会社 | 画像処理装置、画像処理方法、及びプログラム |

| JP5538993B2 (ja) * | 2010-04-28 | 2014-07-02 | キヤノン株式会社 | 画像処理装置、画像処理方法、プログラム、および記憶媒体 |

| JP5538996B2 (ja) * | 2010-04-30 | 2014-07-02 | キヤノン株式会社 | 画像処理装置、画像処理方法、プログラム、および記憶媒体 |

| JP2011254405A (ja) * | 2010-06-03 | 2011-12-15 | Canon Inc | 画像処理装置及びその処理方法 |

| JP5791392B2 (ja) * | 2011-06-30 | 2015-10-07 | 輝雄 岡田 | 電飾装置及び電飾方法 |

| TW201430809A (zh) * | 2013-01-11 | 2014-08-01 | Sony Corp | 顯示面板、像素晶片及電子機器 |

| US20150062294A1 (en) * | 2013-08-27 | 2015-03-05 | Thomas S. Sibley | Holoscope: Digital Virtual Object Projector |

| JP6115407B2 (ja) * | 2013-08-29 | 2017-04-19 | ソニー株式会社 | 表示パネル、その駆動方法、および電子機器 |

| JP6187039B2 (ja) * | 2013-08-29 | 2017-08-30 | ソニー株式会社 | 表示パネル、その駆動方法、および電子機器 |

-

2013

- 2013-12-04 JP JP2013250779A patent/JP6070524B2/ja active Active

-

2014

- 2014-11-05 US US14/533,532 patent/US9495911B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015108695A (ja) | 2015-06-11 |

| US9495911B2 (en) | 2016-11-15 |

| US20150154905A1 (en) | 2015-06-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6070524B2 (ja) | 表示パネル、駆動方法、および電子機器 | |

| CN108257559B (zh) | 具有栅极驱动器的显示面板 | |

| KR102328639B1 (ko) | 표시 장치 및 그의 구동 방법 | |

| US9454935B2 (en) | Organic light emitting diode display device | |

| US9111490B2 (en) | Gate driving circuit and organic electroluminescent display apparatus using the same | |

| JP2020021083A (ja) | 表示装置及びそのゲート駆動回路 | |

| US20120098826A1 (en) | Gate driver and organic light emitting diode display including the same | |

| CN108091304B (zh) | 栅极驱动器和使用该栅极驱动器的显示面板 | |

| US8497855B2 (en) | Scan driving apparatus and driving method for the same | |

| KR102651800B1 (ko) | 표시 장치 | |

| KR20180082698A (ko) | 표시 장치 및 그의 구동 방법 | |

| KR20180082692A (ko) | 표시 장치 및 그의 구동 방법 | |

| US11430368B2 (en) | Data driving device and display device using the same | |

| US10043438B2 (en) | Display device and method of driving the same with pixel shifting compensation data | |

| WO2016084544A1 (ja) | 画素ユニット、表示パネル、および信号伝送方法 | |

| JP2007114780A (ja) | 画素の制御システム | |

| US20100328364A1 (en) | Method of driving light emitting device, light emitting device and electronic apparatus | |

| KR102321802B1 (ko) | 게이트 쉬프트 레지스터 및 이를 이용한 표시 장치 | |

| US20180167070A1 (en) | Shift register and gate driver including the same | |

| US9336707B2 (en) | Gamma voltage supply device and display device using the same | |

| JP6102054B2 (ja) | 表示装置、及び電子機器 | |

| JP2005221566A (ja) | 表示コントローラ、表示システム及び表示制御方法 | |

| JP2010181516A (ja) | 集積回路装置、電気光学装置及び電子機器 | |

| KR102018762B1 (ko) | 유기발광 표시장치와 그 게이트 신호 생성방법 | |

| KR101009641B1 (ko) | 표시 장치 및 그 구동 방법, 표시 장치의 구동 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160114 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160114 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161021 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20161206 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20161219 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6070524 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |