JP6096991B2 - 感知遅延が低減され感知マージンが改善されたsramリードバッファ - Google Patents

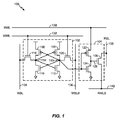

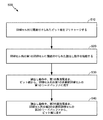

感知遅延が低減され感知マージンが改善されたsramリードバッファ Download PDFInfo

- Publication number

- JP6096991B2 JP6096991B2 JP2016531746A JP2016531746A JP6096991B2 JP 6096991 B2 JP6096991 B2 JP 6096991B2 JP 2016531746 A JP2016531746 A JP 2016531746A JP 2016531746 A JP2016531746 A JP 2016531746A JP 6096991 B2 JP6096991 B2 JP 6096991B2

- Authority

- JP

- Japan

- Prior art keywords

- switch

- read

- sram cell

- inverter

- sram

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/413—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction

- G11C11/417—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction for memory cells of the field-effect type

- G11C11/419—Read-write [R-W] circuits

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/39—Circuit design at the physical level

- G06F30/392—Floor-planning or layout, e.g. partitioning or placement

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/412—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger using field-effect transistors only

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/16—Multiple access memory array, e.g. addressing one storage element via at least two independent addressing line groups

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Architecture (AREA)

- Evolutionary Computation (AREA)

- Geometry (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Static Random-Access Memory (AREA)

- Semiconductor Memories (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/957,485 US9460777B2 (en) | 2013-08-02 | 2013-08-02 | SRAM read buffer with reduced sensing delay and improved sensing margin |

| US13/957,485 | 2013-08-02 | ||

| PCT/US2014/047455 WO2015017164A1 (en) | 2013-08-02 | 2014-07-21 | Sram read buffer with reduced sensing delay and improved sensing margin |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016527654A JP2016527654A (ja) | 2016-09-08 |

| JP2016527654A5 JP2016527654A5 (enExample) | 2017-02-02 |

| JP6096991B2 true JP6096991B2 (ja) | 2017-03-15 |

Family

ID=51293186

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016531746A Expired - Fee Related JP6096991B2 (ja) | 2013-08-02 | 2014-07-21 | 感知遅延が低減され感知マージンが改善されたsramリードバッファ |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9460777B2 (enExample) |

| EP (1) | EP3028281B1 (enExample) |

| JP (1) | JP6096991B2 (enExample) |

| KR (1) | KR101779553B1 (enExample) |

| CN (1) | CN105637589B (enExample) |

| WO (1) | WO2015017164A1 (enExample) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2887355A1 (en) * | 2013-12-20 | 2015-06-24 | IMEC vzw | Data storage cell and memory arrangement |

| US20210027833A1 (en) * | 2017-07-28 | 2021-01-28 | Masud H. Chowdhury | 8t static random access memory |

| US10438654B2 (en) * | 2017-09-22 | 2019-10-08 | Qualcomm Incorporated | Transpose static random access memory (SRAM) bit cells configured for horizontal and vertical read operations |

| WO2019220259A1 (ja) * | 2018-05-17 | 2019-11-21 | 株式会社半導体エネルギー研究所 | 記憶装置、半導体装置、および電子機器 |

| WO2020142743A1 (en) | 2019-01-05 | 2020-07-09 | Synopsys, Inc. | Enhanced read sensing margin and minimized vdd for sram cell arrays |

| CN109920459B (zh) * | 2019-01-10 | 2021-01-15 | 中国人民武装警察部队海警学院 | 一种完全非对称的亚阈值单端9管存储单元 |

| CN111883192B (zh) * | 2020-07-20 | 2023-02-03 | 安徽大学 | 基于9t sram单元在内存实现汉明距离计算的电路及9t sram单元 |

| CN112069768B (zh) * | 2020-09-08 | 2024-07-16 | 飞腾信息技术有限公司 | 一种针对双端口sram输入输出延时优化的方法 |

| CN112382326B (zh) * | 2020-12-11 | 2023-11-17 | 北京中科芯蕊科技有限公司 | 一种亚阈值双电源sram读辅助电路 |

| WO2022266541A2 (en) * | 2021-06-18 | 2022-12-22 | University Of Southern California | Augmented memory computing: a new pathway for efficient ai computations |

| US12249367B2 (en) | 2022-04-13 | 2025-03-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | Write assist circuit for memory device |

| CN114743580B (zh) * | 2022-06-13 | 2022-09-02 | 中科南京智能技术研究院 | 一种电荷共享存内计算装置 |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0636315B2 (ja) | 1983-12-23 | 1994-05-11 | 株式会社日立製作所 | 半導体メモリ |

| JP2004047003A (ja) * | 2002-07-15 | 2004-02-12 | Renesas Technology Corp | 記憶装置 |

| US7075842B2 (en) * | 2004-02-13 | 2006-07-11 | Fujitsu Limited | Differential current-mode sensing methods and apparatuses for memories |

| JP4528044B2 (ja) * | 2004-07-13 | 2010-08-18 | 富士通セミコンダクター株式会社 | 半導体装置 |

| US7106620B2 (en) * | 2004-12-30 | 2006-09-12 | International Business Machines Corporation | Memory cell having improved read stability |

| JP2007213699A (ja) * | 2006-02-09 | 2007-08-23 | Toshiba Corp | 半導体記憶装置 |

| US20070242498A1 (en) * | 2006-04-13 | 2007-10-18 | Anantha Chandrakasan | Sub-threshold static random access memory |

| US7400523B2 (en) * | 2006-06-01 | 2008-07-15 | Texas Instruments Incorporated | 8T SRAM cell with higher voltage on the read WL |

| US7502273B2 (en) * | 2006-09-27 | 2009-03-10 | Taiwan Semiconductor Manufacturing Co., Ltd. | Two-port SRAM with a high speed sensing scheme |

| US20090161410A1 (en) * | 2007-12-21 | 2009-06-25 | Texas Instruments Inc. | Seven transistor sram cell |

| US7660150B2 (en) * | 2007-12-31 | 2010-02-09 | Texas Instruments Incorporated | Memory cell having improved write stability |

| US7606062B2 (en) * | 2007-12-31 | 2009-10-20 | Intel Corporation | Ultra low voltage and minimum operating voltage tolerant register file |

| JP2009272023A (ja) | 2008-05-12 | 2009-11-19 | Toshiba Corp | 半導体記憶装置 |

| JP4954954B2 (ja) * | 2008-08-07 | 2012-06-20 | パナソニック株式会社 | 半導体記憶装置 |

| US7961499B2 (en) | 2009-01-22 | 2011-06-14 | Qualcomm Incorporated | Low leakage high performance static random access memory cell using dual-technology transistors |

| US7986566B2 (en) * | 2009-04-01 | 2011-07-26 | Texas Instruments Incorporated | SRAM cell with read buffer controlled for low leakage current |

| US8144540B2 (en) * | 2009-04-14 | 2012-03-27 | Taiwan Semiconductor Manufacturing Co., Ltd. | Two-port 8T SRAM design |

| EP2387039A1 (en) | 2010-05-12 | 2011-11-16 | Stichting IMEC Nederland | Hierarchical buffered segmented bit-lines based sram |

| US8208314B2 (en) * | 2010-06-01 | 2012-06-26 | Aptina Imaging Corporation | Sequential access memory elements |

| US8654575B2 (en) | 2010-07-16 | 2014-02-18 | Texas Instruments Incorporated | Disturb-free static random access memory cell |

| US8947912B2 (en) * | 2010-07-20 | 2015-02-03 | University Of Virginia Licensing & Ventures Group | Memory cell including unidirectional gate conductors and contacts |

| WO2012119988A1 (en) * | 2011-03-04 | 2012-09-13 | Imec | Local write and read assist circuitry for memory device |

| US8531873B2 (en) * | 2011-05-08 | 2013-09-10 | Ben-Gurion University Of The Negev Research And Development Authority | Ultra low power SRAM cell circuit with a supply feedback loop for near and sub threshold operation |

| JP2013206512A (ja) * | 2012-03-29 | 2013-10-07 | Kyushu Institute Of Technology | 半導体記憶装置 |

-

2013

- 2013-08-02 US US13/957,485 patent/US9460777B2/en active Active

-

2014

- 2014-07-21 EP EP14748067.7A patent/EP3028281B1/en active Active

- 2014-07-21 KR KR1020167004905A patent/KR101779553B1/ko active Active

- 2014-07-21 CN CN201480043596.1A patent/CN105637589B/zh active Active

- 2014-07-21 WO PCT/US2014/047455 patent/WO2015017164A1/en not_active Ceased

- 2014-07-21 JP JP2016531746A patent/JP6096991B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US9460777B2 (en) | 2016-10-04 |

| JP2016527654A (ja) | 2016-09-08 |

| CN105637589B (zh) | 2018-11-02 |

| WO2015017164A1 (en) | 2015-02-05 |

| EP3028281A1 (en) | 2016-06-08 |

| CN105637589A (zh) | 2016-06-01 |

| US20150036417A1 (en) | 2015-02-05 |

| KR20160037202A (ko) | 2016-04-05 |

| EP3028281B1 (en) | 2017-12-20 |

| KR101779553B1 (ko) | 2017-09-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6096991B2 (ja) | 感知遅延が低減され感知マージンが改善されたsramリードバッファ | |

| EP2620833B1 (en) | Clock gating system and method | |

| US8279659B2 (en) | System and method of operating a memory device | |

| US9336863B2 (en) | Dual write wordline memory cell | |

| CN102016749B (zh) | 时钟门控系统和方法 | |

| JP6199286B2 (ja) | 検知回路 | |

| US8760953B2 (en) | Sense amplifier with selectively powered inverter | |

| JP5808858B2 (ja) | 検知回路 | |

| KR20130018327A (ko) | 로컬 전류 싱크를 갖는 메모리 디바이스 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A529 | Written submission of copy of amendment under article 34 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A529 Effective date: 20160128 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161212 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161212 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20161212 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20170117 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170123 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170216 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6096991 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |