JP5911899B2 - 基板検査装置及び部品実装装置 - Google Patents

基板検査装置及び部品実装装置 Download PDFInfo

- Publication number

- JP5911899B2 JP5911899B2 JP2014027386A JP2014027386A JP5911899B2 JP 5911899 B2 JP5911899 B2 JP 5911899B2 JP 2014027386 A JP2014027386 A JP 2014027386A JP 2014027386 A JP2014027386 A JP 2014027386A JP 5911899 B2 JP5911899 B2 JP 5911899B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- solder

- backup pin

- arrangement position

- region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B23—MACHINE TOOLS; METAL-WORKING NOT OTHERWISE PROVIDED FOR

- B23K—SOLDERING OR UNSOLDERING; WELDING; CLADDING OR PLATING BY SOLDERING OR WELDING; CUTTING BY APPLYING HEAT LOCALLY, e.g. FLAME CUTTING; WORKING BY LASER BEAM

- B23K37/00—Auxiliary devices or processes, not specially adapted to a procedure covered by only one of the preceding main groups

- B23K37/04—Auxiliary devices or processes, not specially adapted to a procedure covered by only one of the preceding main groups for holding or positioning work

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01N—INVESTIGATING OR ANALYSING MATERIALS BY DETERMINING THEIR CHEMICAL OR PHYSICAL PROPERTIES

- G01N21/00—Investigating or analysing materials by the use of optical means, i.e. using sub-millimetre waves, infrared, visible or ultraviolet light

- G01N21/84—Systems specially adapted for particular applications

- G01N21/88—Investigating the presence of flaws or contamination

- G01N21/95—Investigating the presence of flaws or contamination characterised by the material or shape of the object to be examined

- G01N21/956—Inspecting patterns on the surface of objects

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/302—Contactless testing

- G01R31/308—Contactless testing using non-ionising electromagnetic radiation, e.g. optical radiation

- G01R31/309—Contactless testing using non-ionising electromagnetic radiation, e.g. optical radiation of printed or hybrid circuits or circuit substrates

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01N—INVESTIGATING OR ANALYSING MATERIALS BY DETERMINING THEIR CHEMICAL OR PHYSICAL PROPERTIES

- G01N21/00—Investigating or analysing materials by the use of optical means, i.e. using sub-millimetre waves, infrared, visible or ultraviolet light

- G01N21/84—Systems specially adapted for particular applications

- G01N21/88—Investigating the presence of flaws or contamination

- G01N21/95—Investigating the presence of flaws or contamination characterised by the material or shape of the object to be examined

- G01N21/956—Inspecting patterns on the surface of objects

- G01N2021/95638—Inspecting patterns on the surface of objects for PCB's

- G01N2021/95646—Soldering

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/2801—Testing of printed circuits, backplanes, motherboards, hybrid circuits or carriers for multichip packages [MCP]

- G01R31/281—Specific types of tests or tests for a specific type of fault, e.g. thermal mapping, shorts testing

- G01R31/2813—Checking the presence, location, orientation or value, e.g. resistance, of components or conductors

Description

前記基板の裏面を支持する基板支持装置を備えるとともに、

前記基板支持装置は、

上端部において前記基板の裏面を支持可能な複数のバックアップピンと、

前記バックアップピンの配置位置を決定する配置位置決定手段と、

前記配置位置決定手段により決定された前記バックアップピンの配置位置に、前記バックアップピンを配置するバックアップピン配置手段とを有し、

前記配置位置決定手段は、前記基板の裏面のうち、前記レジスト膜で前記電極が覆われた部位であり、かつ、前記電子部品及び前記半田の存在していない部位を支持する位置に前記バックアップピンの配置位置を決定することを特徴とする基板検査装置。

前記基板のうち、その表面において前記半田間の距離が設計上で所定値以下となる領域を含む半田近接領域を特定する近接領域特定手段を有し、

前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記半田近接領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記半田近接領域に対応する部位以外を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする手段3に記載の基板検査装置。

前記基板のうち、その表面において前記半田の単位面積当たりの数が設計上で所定数以上となる領域を含む半田多数領域を特定する多数領域特定手段を有し、

前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記半田多数領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記半田多数領域に対応する部位以外を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする手段3又は4に記載の基板検査装置。

前記基板のうち、その表面において設計上における面積が所定値以下となる前記半田を含む半田極小領域を特定する極小領域特定手段を有し、

前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記半田極小領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記半田極小領域に対応する部位以外を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする手段3乃至5のいずれかに記載の基板検査装置。

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち検査対象となる領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち検査対象とならない領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする手段3乃至6のいずれかに記載の基板検査装置。

前記基板の裏面を支持する基板支持装置を備えるとともに、

前記基板支持装置は、

上端部において前記基板の裏面を支持可能な複数のバックアップピンと、

前記バックアップピンの配置位置を決定する配置位置決定手段と、

前記配置位置決定手段により決定された前記バックアップピンの配置位置に、前記バックアップピンを配置するバックアップピン配置手段とを有し、

前記配置位置決定手段は、前記基板の裏面のうち、前記レジスト膜で前記電極が覆われた部位であり、かつ、前記電子部品及び前記半田の存在していない部位を支持する位置に前記バックアップピンの配置位置を決定することを特徴とする部品実装装置。

前記基板のうち、その表面において前記半田間の距離が設計上で所定値以下となる領域を含む半田近接領域を特定する近接領域特定手段を有し、

前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記半田近接領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記半田近接領域に対応する部位以外を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする手段10に記載の部品実装装置。

前記基板のうち、その表面において前記半田の単位面積当たりの数が設計上で所定数以上となる領域を含む半田多数領域を特定する多数領域特定手段を有し、

前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記半田多数領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記半田多数領域に対応する部位以外を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする手段10又は11に記載の部品実装装置。

前記基板のうち、その表面において設計上における面積が所定値以下となる前記半田を含む半田極小領域を特定する極小領域特定手段を有し、

前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記半田極小領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記半田極小領域に対応する部位以外を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする手段10乃至12のいずれかに記載の部品実装装置。

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記電子部品の実装領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記電子部品の非実装領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする手段10乃至13のいずれかに記載の部品実装装置。

Claims (14)

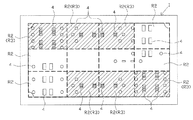

- 電極と、当該電極の所定部位を覆うレジスト膜とを有し、前記電極の所定部位に対して所定の電子部品を実装するための半田が設けられた基板の裏面を支持した状態で、前記基板の表面を検査する基板検査装置であって、

前記基板の裏面を支持する基板支持装置を備えるとともに、

前記基板支持装置は、

上端部において前記基板の裏面を支持可能な複数のバックアップピンと、

前記バックアップピンの配置位置を決定する配置位置決定手段と、

前記配置位置決定手段により決定された前記バックアップピンの配置位置に、前記バックアップピンを配置するバックアップピン配置手段とを有し、

前記配置位置決定手段は、前記基板の裏面のうち、前記レジスト膜で前記電極が覆われた部位であり、かつ、前記電子部品及び前記半田の存在していない部位を支持する位置に前記バックアップピンの配置位置を決定することを特徴とする基板検査装置。 - 前記配置位置決定手段は、前記基板の裏面における前記電子部品、前記半田、前記レジスト膜及び前記電極の設計上の配置領域に関するデータに基づいて、前記基板の裏面のうち、前記レジスト膜で前記電極が覆われた部位であり、かつ、前記電子部品及び前記半田の存在していない部位を特定し、前記特定された位置に前記バックアップピンの配置位置を決定することを特徴とする請求項1に記載の基板検査装置。

- 前記配置位置決定手段は、前記基板の表面における前記半田の設計上の配置情報、及び、前記基板の表面における検査領域に関する情報の少なくとも一方に基づいて、前記バックアップピンの配置位置を決定することを特徴とする請求項1又は2に記載の基板検査装置。

- 前記基板の表面には、前記半田が複数設けられ、

前記基板のうち、その表面において前記半田間の距離が設計上で所定値以下となる領域を含む半田近接領域を特定する近接領域特定手段を有し、

前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記半田近接領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記半田近接領域に対応する部位以外を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする請求項3に記載の基板検査装置。 - 前記基板の表面には、前記半田が複数設けられ、

前記基板のうち、その表面において前記半田の単位面積当たりの数が設計上で所定数以上となる領域を含む半田多数領域を特定する多数領域特定手段を有し、

前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記半田多数領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記半田多数領域に対応する部位以外を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする請求項3又は4に記載の基板検査装置。 - 前記基板の表面には、前記半田が複数設けられ、

前記基板のうち、その表面において設計上における面積が所定値以下となる前記半田を含む半田極小領域を特定する極小領域特定手段を有し、

前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記半田極小領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記半田極小領域に対応する部位以外を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする請求項3乃至5のいずれか1項に記載の基板検査装置。 - 前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち検査対象となる領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち検査対象とならない領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする請求項3乃至6のいずれか1項に記載の基板検査装置。 - 電極と、当該電極の所定部位を覆うレジスト膜とを有し、前記電極の所定部位に対して所定の電子部品を実装するための半田が設けられた基板の裏面を支持した状態で、前記基板の表面に設けられた前記半田に前記電子部品を押し込んで実装する部品実装装置であって、

前記基板の裏面を支持する基板支持装置を備えるとともに、

前記基板支持装置は、

上端部において前記基板の裏面を支持可能な複数のバックアップピンと、

前記バックアップピンの配置位置を決定する配置位置決定手段と、

前記配置位置決定手段により決定された前記バックアップピンの配置位置に、前記バックアップピンを配置するバックアップピン配置手段とを有し、

前記配置位置決定手段は、前記基板の裏面のうち、前記レジスト膜で前記電極が覆われた部位であり、かつ、前記電子部品及び前記半田の存在していない部位を支持する位置に前記バックアップピンの配置位置を決定することを特徴とする部品実装装置。 - 前記配置位置決定手段は、前記基板の裏面における前記電子部品、前記半田、前記レジスト膜及び前記電極の設計上の配置領域に関するデータに基づいて、前記基板の裏面のうち、前記レジスト膜で前記電極が覆われた部位であり、かつ、前記電子部品及び前記半田の存在していない部位を特定し、前記特定された位置に前記バックアップピンの配置位置を決定することを特徴とする請求項8に記載の部品実装装置。

- 前記配置位置決定手段は、前記基板の表面に実装される前記電子部品の情報、及び、前記基板の表面における前記半田の設計上の配置情報の少なくとも一方に基づいて、前記バックアップピンの配置位置を決定することを特徴とする請求項8又は9に記載の部品実装装置。

- 前記基板の表面には、前記半田が複数設けられ、

前記基板のうち、その表面において前記半田間の距離が設計上で所定値以下となる領域を含む半田近接領域を特定する近接領域特定手段を有し、

前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記半田近接領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記半田近接領域に対応する部位以外を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする請求項10に記載の部品実装装置。 - 前記基板の表面には、前記半田が複数設けられ、

前記基板のうち、その表面において前記半田の単位面積当たりの数が設計上で所定数以上となる領域を含む半田多数領域を特定する多数領域特定手段を有し、

前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記半田多数領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記半田多数領域に対応する部位以外を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする請求項10又は11に記載の部品実装装置。 - 前記基板の表面には、前記半田が複数設けられ、

前記基板のうち、その表面において設計上における面積が所定値以下となる前記半田を含む半田極小領域を特定する極小領域特定手段を有し、

前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記半田極小領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記半田極小領域に対応する部位以外を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする請求項10乃至12のいずれか1項に記載の部品実装装置。 - 前記配置位置決定手段は、

前記バックアップピンの配置位置の変更に伴い、前記バックアップピンの単位面積当たりの数を変更可能であり、

前記基板のうち前記電子部品の実装領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数が、前記基板のうち前記電子部品の非実装領域に対応する部位を支持する前記バックアップピンの単位面積当たりの数よりも大きくなるように前記バックアップピンの配置位置を決定することを特徴とする請求項10乃至13のいずれか1項に記載の部品実装装置。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014027386A JP5911899B2 (ja) | 2014-02-17 | 2014-02-17 | 基板検査装置及び部品実装装置 |

| TW104103654A TWI595814B (zh) | 2014-02-17 | 2015-02-04 | 基板檢查裝置及零件安裝裝置 |

| TW106121611A TWI626866B (zh) | 2014-02-17 | 2015-02-04 | 基板檢查方法、零件安裝方法及印刷基板的製造方法 |

| DE102015202610.8A DE102015202610B4 (de) | 2014-02-17 | 2015-02-13 | Substratinspektionseinrichtung und Komponentenmontageeinrichtung |

| CN201510079186.9A CN104853581B (zh) | 2014-02-17 | 2015-02-13 | 基板检查装置和部件安装装置 |

| US14/624,124 US9511455B2 (en) | 2014-02-17 | 2015-02-17 | Substrate inspection device and component mounting device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014027386A JP5911899B2 (ja) | 2014-02-17 | 2014-02-17 | 基板検査装置及び部品実装装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016066117A Division JP6333877B2 (ja) | 2016-03-29 | 2016-03-29 | 基板検査方法及びプリント基板の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015153935A JP2015153935A (ja) | 2015-08-24 |

| JP2015153935A5 JP2015153935A5 (ja) | 2015-11-26 |

| JP5911899B2 true JP5911899B2 (ja) | 2016-04-27 |

Family

ID=53797291

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014027386A Active JP5911899B2 (ja) | 2014-02-17 | 2014-02-17 | 基板検査装置及び部品実装装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9511455B2 (ja) |

| JP (1) | JP5911899B2 (ja) |

| CN (1) | CN104853581B (ja) |

| DE (1) | DE102015202610B4 (ja) |

| TW (2) | TWI626866B (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6670180B2 (ja) * | 2016-06-02 | 2020-03-18 | ヤマハ発動機株式会社 | バックアップピン配置位置決定装置、バックアップピン配置位置決定方法および基板作業システム |

| JP6306230B1 (ja) * | 2017-02-09 | 2018-04-04 | Ckd株式会社 | 半田印刷検査装置、半田印刷検査方法、及び、基板の製造方法 |

| JP6928527B2 (ja) * | 2017-10-03 | 2021-09-01 | ヤマハ発動機株式会社 | 高さ測定装置、高さ測定方法および基板作業装置 |

| WO2019138509A1 (ja) * | 2018-01-11 | 2019-07-18 | 株式会社Fuji | 部品実装システム |

| CN112119681B (zh) * | 2018-05-23 | 2022-02-18 | 雅马哈发动机株式会社 | 支承构件配置决定装置、支承构件配置决定方法 |

| EP3806611A4 (en) * | 2018-05-25 | 2021-06-02 | Fuji Corporation | DETERMINATION DEVICE, COMPONENT MOUNTING DEVICE PROVIDED THEREOF, AND DETERMINATION METHOD |

| WO2020003491A1 (ja) * | 2018-06-29 | 2020-01-02 | ヤマハ発動機株式会社 | 支持部材配置支援装置、印刷機、印刷システム、支持部材配置支援方法 |

| JP7169446B2 (ja) * | 2019-06-06 | 2022-11-10 | 株式会社Fuji | 対基板作業機および対基板作業システム |

| CN114287174B (zh) * | 2019-09-06 | 2023-07-14 | 株式会社富士 | 元件安装机的支撑销自动配置系统 |

| CN114535916B (zh) * | 2022-04-01 | 2023-12-22 | 长鑫存储技术有限公司 | 焊接对位设备以及采用该焊接设备进行焊接的方法 |

| CN117715405A (zh) * | 2024-02-01 | 2024-03-15 | 赛晶亚太半导体科技(浙江)有限公司 | 一种叠层结构贴片方法及叠层结构贴片系统 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3006964B2 (ja) | 1992-10-07 | 2000-02-07 | 山形カシオ株式会社 | バックアップピン自動入替装置 |

| JPH0758423A (ja) * | 1993-08-19 | 1995-03-03 | Sony Corp | バックアップピン受け部を設けたプリント基板 |

| JP4540838B2 (ja) | 2000-12-12 | 2010-09-08 | パナソニック株式会社 | 回路基板固定方法 |

| JP2003204198A (ja) | 2002-01-04 | 2003-07-18 | Hitachi Communication Technologies Ltd | プリント回路板のバックアップピン自動配置装置 |

| JP4452686B2 (ja) | 2003-05-16 | 2010-04-21 | 富士機械製造株式会社 | バックアップ装置における支持部位置決定方法およびその装置 |

| JP4349091B2 (ja) | 2003-11-12 | 2009-10-21 | パナソニック株式会社 | プリント基板支持装置及びプリント基板支持方法 |

| JP4051568B2 (ja) * | 2004-02-09 | 2008-02-27 | ソニー株式会社 | 部品実装基板検査装置 |

| JP3960346B2 (ja) * | 2004-12-27 | 2007-08-15 | オムロン株式会社 | 画像処理方法、基板検査方法、基板検査装置、および基板検査用の検査データ作成方法 |

| JP2007311711A (ja) * | 2006-05-22 | 2007-11-29 | Anritsu Corp | 基板バックアップ装置、該装置を備えた印刷半田検査装置及び方法 |

| JP4841460B2 (ja) * | 2007-02-27 | 2011-12-21 | ヤマハ発動機株式会社 | バックアップピン配設位置決定装置、バックアップユニット形成装置、及び基板処理装置 |

| JP5723221B2 (ja) * | 2011-05-31 | 2015-05-27 | ヤマハ発動機株式会社 | スクリーン印刷装置 |

| JP5747167B2 (ja) * | 2012-02-02 | 2015-07-08 | パナソニックIpマネジメント株式会社 | 下受けピンの配置方法および下受けピンの返戻方法 |

| JP5874508B2 (ja) * | 2012-04-17 | 2016-03-02 | オムロン株式会社 | はんだの濡れ上がり状態の検査方法およびこの方法を用いた自動外観検査装置ならびに基板検査システム |

-

2014

- 2014-02-17 JP JP2014027386A patent/JP5911899B2/ja active Active

-

2015

- 2015-02-04 TW TW106121611A patent/TWI626866B/zh active

- 2015-02-04 TW TW104103654A patent/TWI595814B/zh active

- 2015-02-13 CN CN201510079186.9A patent/CN104853581B/zh active Active

- 2015-02-13 DE DE102015202610.8A patent/DE102015202610B4/de active Active

- 2015-02-17 US US14/624,124 patent/US9511455B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| TW201737788A (zh) | 2017-10-16 |

| CN104853581B (zh) | 2018-06-15 |

| TW201543974A (zh) | 2015-11-16 |

| DE102015202610B4 (de) | 2023-10-26 |

| CN104853581A (zh) | 2015-08-19 |

| DE102015202610A1 (de) | 2015-09-03 |

| TWI595814B (zh) | 2017-08-11 |

| US9511455B2 (en) | 2016-12-06 |

| JP2015153935A (ja) | 2015-08-24 |

| TWI626866B (zh) | 2018-06-11 |

| US20150231744A1 (en) | 2015-08-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5911899B2 (ja) | 基板検査装置及び部品実装装置 | |

| US5471368A (en) | Module having vertical peripheral edge connection | |

| CN1715888B (zh) | 印刷电路板检查装置和印刷电路板装配检查线系统 | |

| JP2015153935A5 (ja) | ||

| JP2006220426A (ja) | 実装された電子部品の検査方法及び装置 | |

| JP2009192282A (ja) | 半田印刷検査装置及び部品実装システム | |

| JP6329667B1 (ja) | 部品実装システム及び接着剤検査装置 | |

| JP6318638B2 (ja) | プリント配線板および情報処理装置 | |

| WO2016189609A1 (ja) | 立体配線板および立体配線板の製造方法 | |

| JP2006319332A (ja) | 実装された電子部品の検査装置を備えた電子部品実装機 | |

| US20070164083A1 (en) | Alignment plate | |

| KR100758207B1 (ko) | 반자동 피씨비 다기능 검사장치 | |

| JP6182505B2 (ja) | 実装荷重測定装置 | |

| US9296056B2 (en) | Device for thermal management of surface mount devices during reflow soldering | |

| CN105164522A (zh) | 部件安装基板检查方法以及采用该检查方法的基板制造系统 | |

| JP4372719B2 (ja) | 部品搭載システム | |

| JP6333877B2 (ja) | 基板検査方法及びプリント基板の製造方法 | |

| JP2008171992A (ja) | 半導体部品の実装方法 | |

| JP5421409B2 (ja) | 外観検査装置及び外観検査方法 | |

| JP2008028213A (ja) | 回路基板及びその検査方法 | |

| JP6587871B2 (ja) | 部品実装装置および部品実装システム | |

| US20120292088A1 (en) | Electronic device with obliquely connected components | |

| JP3174536B2 (ja) | ハンダ付け状態の確認方法 | |

| JP5371730B2 (ja) | プリント基板、電子部品の実装方法 | |

| KR101177779B1 (ko) | 인쇄회로기판의 비아홀 막음 방법 및 이에 이용되는 공기정량흡입판 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151008 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20151008 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160218 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160315 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160330 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5911899 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |