JP5732827B2 - 記憶素子および記憶装置、並びに記憶装置の動作方法 - Google Patents

記憶素子および記憶装置、並びに記憶装置の動作方法 Download PDFInfo

- Publication number

- JP5732827B2 JP5732827B2 JP2010261517A JP2010261517A JP5732827B2 JP 5732827 B2 JP5732827 B2 JP 5732827B2 JP 2010261517 A JP2010261517 A JP 2010261517A JP 2010261517 A JP2010261517 A JP 2010261517A JP 5732827 B2 JP5732827 B2 JP 5732827B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- electrode

- resistance

- transition metal

- ion source

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices without a potential-jump barrier or surface barrier, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

- H10N70/24—Multistable switching devices, e.g. memristors based on migration or redistribution of ionic species, e.g. anions, vacancies

- H10N70/245—Multistable switching devices, e.g. memristors based on migration or redistribution of ionic species, e.g. anions, vacancies the species being metal cations, e.g. programmable metallization cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0009—RRAM elements whose operation depends upon chemical change

- G11C13/0011—RRAM elements whose operation depends upon chemical change comprising conductive bridging RAM [CBRAM] or programming metallization cells [PMCs]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/30—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having three or more electrodes, e.g. transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/80—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays

- H10B63/82—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays the switching components having a common active material layer

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices without a potential-jump barrier or surface barrier, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/011—Manufacture or treatment of multistable switching devices

- H10N70/021—Formation of the switching material, e.g. layer deposition

- H10N70/028—Formation of the switching material, e.g. layer deposition by conversion of electrode material, e.g. oxidation

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices without a potential-jump barrier or surface barrier, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/821—Device geometry

- H10N70/826—Device geometry adapted for essentially vertical current flow, e.g. sandwich or pillar type devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices without a potential-jump barrier or surface barrier, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/841—Electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices without a potential-jump barrier or surface barrier, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/841—Electrodes

- H10N70/8416—Electrodes adapted for supplying ionic species

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices without a potential-jump barrier or surface barrier, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/883—Oxides or nitrides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices without a potential-jump barrier or surface barrier, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/883—Oxides or nitrides

- H10N70/8833—Binary metal oxides, e.g. TaOx

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/161—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect details concerning the memory cell structure, e.g. the layers of the ferromagnetic memory cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/50—Resistive cell structure aspects

- G11C2213/51—Structure including a barrier layer preventing or limiting migration, diffusion of ions or charges or formation of electrolytes near an electrode

Description

み状態の抵抗値と消去状態の抵抗値との抵抗分離幅が不十分であり、繰り返し耐久性に改善の余地があった。

(A)テルル(Te),硫黄(S)およびセレン(Se)のうち少なくとも1種のカルコゲン元素と共にアルミニウム(Al)を含むイオン源層

(B)イオン源層と第1電極との間に設けられると共に、第1電極の側から順に第1層と第2層とが積層された構成を有し、第2層はアルミニウム酸化物を主成分とし、第1層はアルミニウム酸化物よりも抵抗の低い遷移金属酸化物および遷移金属酸窒化物のうち少なくとも一方よりなる抵抗変化層と

1.第1の実施の形態(記憶素子;抵抗変化層として遷移金属酸化物よりなる第1層およびアルミニウム酸化物を主成分とする第2層が順に積層されており、イオン源層が中間層とイオン供給層とを有する例)

2.変形例1(記憶素子;抵抗変化層がアルミニウム酸化物および遷移金属酸化物を混在した状態で含有しており、イオン源層が中間層とイオン供給層とを有する例)

3.変形例2(記憶素子;抵抗変化層として遷移金属酸化物よりなる第1層およびアルミニウム酸化物を主成分とする第2層が順に積層されており、イオン源層が単層である例)

4.変形例3(記憶素子;抵抗変化層がアルミニウム酸化物および遷移金属酸化物を混在した状態で含有しており、イオン源層が単層である例)

5.第2の実施の形態(記憶素子;抵抗変化層として遷移金属酸窒化物よりなる第1層およびアルミニウム酸化物を主成分とする第2層が順に積層されており、イオン源層が中間層とイオン供給層とを有する例)

6.変形例4(記憶素子;第1層が、遷移金属酸化物層と遷移金属酸窒化物層とを含む例)

7.第3の実施の形態(記憶素子;中間層に遷移金属を添加する例)

8.第4の実施の形態(記憶素子;中間層およびイオン供給層のうち少なくとも一方に酸素を添加する例)

9.記憶装置

10.実施例

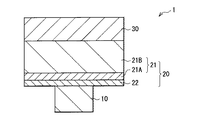

図1は、本発明の第1の実施の形態に係る記憶素子1の断面構成図である。この記憶素子1は、下部電極10(第1電極)、記憶層20および上部電極30(第2電極)を順に有するものである。記憶層20は、上部電極30の側から順に、イオン源層21と、抵抗変化層22とを有している。

過程のみで記録は完結する。

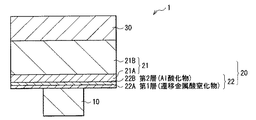

なお、上記実施の形態では、抵抗変化層22が、下部電極10の側から順に、遷移金属酸化物よりなる第1層22Aと、アルミニウム酸化物を主成分とする第2層22Bとを積層した構成を有している場合について説明したが、抵抗変化層22は、図3に示したように、アルミニウム酸化物および遷移金属酸化物を混在した状態で含有する単層構造であってもよい。

また、上記実施の形態では、イオン源層21が中間層21Aとイオン供給層21Bとの2層構造を有する場合について説明したが、イオン源層21は必ずしも中間層21Aを有する必要はなく、図4に示したように、イオン供給層21Bのみの単層構造を有していてもよい。

更に、図5に示したように、抵抗変化層22がアルミニウム酸化物および遷移金属酸化物を混在した状態で含有する単層であると共に、イオン源層21がイオン供給層21Bのみの単層であってもよい。

図6は、本発明の第2の実施の形態に係る記憶素子1の断面構成を表したものである。この記憶素子1は、抵抗変化層22の第1層22Aが遷移金属酸窒化物よりなることを除いては、上記第1の実施の形態と同様の構成・作用および効果を有し、第1の実施の形態と同様にして製造することができる。よって、対応する構成要素には同一の符号を付して説明する。

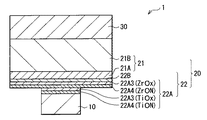

上記第1の実施の形態では第1層22Aが遷移金属酸化物よりなる場合、第2の実施の形態では第1層22Aが遷移金属酸窒化物よりなる場合について説明した。しかしながら、第1層22Aは、図7に示したように、遷移金属酸化物層22A3と遷移金属酸窒化物層22A4とを両方含んでいてもよい。

と共に、イオン源層21がイオン供給層21Bのみの単層であってもよい。

図9は、本発明の第3の実施の形態に係る記憶素子1の断面構成を表したものである。この記憶素子1は、イオン源層21の中間層21AにZr等の遷移金属が添加されていることを除いては、上記第1または第2の実施の形態と同様の構成・作用および効果を有し、第1または第2の実施の形態と同様にして製造することができる。よって、対応する構成要素には同一の符号を付して説明する。

図11は、本発明の第4の実施の形態に係る記憶素子1の断面構成を表したものである。この記憶素子1は、イオン源層21の中間層21Aおよびイオン供給層21Bのうち少なくとも一方に酸素(O)が添加されていることを除いては、上記第1ないし第3の実施の形態と同様の構成・作用および効果を有し、第1ないし第3の実施の形態と同様にして製造することができる。よって、対応する構成要素には同一の符号を付して説明する。

上記記憶素子1を多数、例えば列状やマトリクス状に配列することにより、記憶装置(メモリ)を構成することができる。このとき、各記憶素子1に、必要に応じて、素子選択用のMOSトランジスタ、或いはダイオードを接続してメモリセルを構成し、更に、配線を介して、センスアンプ、アドレスデコーダ、書き込み・消去・読み出し回路等に接続すればよい。

続されている。金属配線層46は、記憶素子1の他方のアドレス配線であるビット線BL(図14参照)に接続されている。なお、図14においては、MOSトランジスタTrのアクティブ領域48を鎖線で示しており、コンタクト部51は記憶素子1の下部電極10、コンタクト部52はビット線BLにそれぞれ接続されている。

上記第1の実施の形態と同様にして記憶素子1を備えたメモリセルアレイを作製した。まず、TiNよりなる下部電極10のプラグが形成してあるCMOS回路上に、スパッタリングによりTi膜を1nmの厚みで形成した。次いで、このTi膜を酸化プラズマで酸化してTiOxよりなる第1層22Aを形成した。

TiNよりなる下部電極10のプラグが形成してあるCMOS回路上で、下部電極10上に形成されている自然酸化皮膜を逆スパッタで十分に除去した。そののち、下部電極10を直接プラズマ酸化することによりTiOxよりなる第1層22Aを形成した。このことを除いては、実施例1と同様にして記録素子1を有するメモリセルアレイを作製した。実施例2の工程を簡略的に示すと以下のようになる。

Wよりなる下部電極10のプラグが形成してあるCMOS回路上で、下部電極10上に形成されている自然酸化皮膜を逆スパッタで十分に除去した。そののち、下部電極10を直接プラズマ酸化することにより酸化タングステン(WOx)よりなる第1層22Aを形成した。このことを除いては、実施例1と同様にして記録素子1を有するメモリセルアレイを作製した。実施例3の工程を簡略的に示すと以下のようになる。

TiNよりなる下部電極のプラグが形成してあるCMOS回路上に、スパッタリングによりガドリニウム(Gd)膜を1nmの厚みで形成した。このGd膜を酸化プラズマで酸化することにより、酸化ガドリニウム(GdOx)膜を形成した。そののち、CuZrTeAlGe(Cu11at%−Zr11%−Te30%−Al40%−Ge8%)よりなるイオン源層を60nmの厚みで形成し、Wよりなる上部電極を50nmの厚みで形成した。このことを除いては、実施例1と同様にして記録素子を有するメモリセルアレイを作製した。比較例1の工程を簡略的に示すと以下のようになる。

TiNよりなる下部電極のプラグが形成してあるCMOS回路上に、スパッタリングによりGd膜を1nmの厚みで形成した。このGd膜を酸化プラズマで酸化することにより、GdOx膜を形成した。続いて、Teよりなる中間層を4nmの厚みで成膜し、CuZrTeAlGe(Cu11at%−Zr11%−Te30%−Al40%−Ge8%)よりなるイオン供給層を60nmの厚みで形成した。そののち、Wよりなる上部電極を50nmの厚みで形成した。このことを除いては、実施例1と同様にして記録素子を有するメモリセルアレイを作製した。比較例2の工程を簡略的に示すと以下のようになる。

TiNよりなる下部電極のプラグが形成してあるCMOS回路上に、スパッタリングによりTeよりなる中間層を4nmの厚みで形成した。続いて、CuZrTeAlGe(Cu11at%−Zr11%−Te30%−Al40%−Ge8%)よりなるイオン供給層を60nmの厚みで形成し、Wよりなる上部電極を50nmの厚みで形成した。このことを除いては、実施例1と同様にして記録素子1を有するメモリセルアレイを作製した。比較例3の工程を簡略的に示すと以下のようになる。

図15(A)〜(C),図16(A)〜(C)および図20(A)〜(C)から分かるように、下部電極10上にTiOxよりなる第1層22Aを形成した実施例1,2ではいずれも良好な抵抗分離および繰り返し特性が得られた。これに対して、遷移金属酸化物よりなる第1層を設けず、下部電極の上に直接中間層およびイオン供給層を形成した比較例3では、高抵抗状態および低抵抗状態の分離が得られておらず、繰り返し特性に劣っていた。

図17(A)および図17(B)から分かるように、WOxよりなる第1層22Aを設けた実施例3では、実施例1,2と同様に良好な抵抗分離および繰り返し特性が得られた。

図18(B)および図18(C)から分かるように、下部電極上にGdOx)よりなる抵抗変化層を形成し、中間層を設けていない比較例1では、100μAの繰り返し後の抵抗分離は比較的良好であったものの、50μAの繰り返し特性は、中間層21Aを設けた実施例1〜3に比べて劣っていた。

上述した実施例2では、遷移金属酸化物よりなる第1層22Aを形成したのちTeよりなる中間層21AおよびCuZrTeAlGeよりなるイオン供給層21Bを順に形成した。しかしながら、実際には成膜後に、図22のTEM像、並びに図23および図24のEDXラインプロファイル結果から分かるように、イオン供給層21Bから中間層21AにAlが拡散し、中間層21AにもAlが存在している状態となっていた。ただし、TEM像からは中間層21Aではイオン供給層21Bよりもカルコゲン元素含有量に対するAl含有量の比(Al濃度)が低いことが分かり、このことが本実施例の効果を発揮させているものと考えられる。つまりは、中間層21AにTeがアニオンとして豊富に存在し、書き込み・消去、特に消去動作時のAlイオンの移動を妨げないことが必要である。また、中間層21A中のAlは、イオン供給層21Bとの濃度勾配による拡散によってもたらされると考えられるので、例えばAl2Te3の化学量論組成よりも少なくなると考えられ、中間層21Aに存在しているAlのほとんどはイオン状態で存在していると考えられ、印加した電位が効果的にイオン移動の駆動に用いられることがこのような特性向上に結びついていると考えられる。

図16(A)および図18(A)から分かるように、中間層を設けない比較例1では、繰り返し後の保持加速試験後において低抵抗状態のビットが高抵抗化し、分布が変化している様子が見られた。これに対して、中間層を有する実施例2では、低抵抗状態の分布に変化は見られず良好なデータ保持特性を示した。この原因は必ずしも明らかではないが、実施例2ではイオン供給層21BよりもAl濃度の低い中間層21Aが存在することで、書き込み動作時の還元反応によって、Alイオンが還元されてAlメタルが生成し、書き込み電圧バイアスを取り去ったときに再びAl酸化物となって素子抵抗を上昇させるのでなく、Alを溶解する余力のある中間層21AにメタルAlが溶解することによって抵抗上昇が生じないためと考えられる。

第1層22Aを、Ta膜をプラズマ酸化することにより形成したことを除いては、実施例1と同様にしてメモリセルアレイを作製した。得られたメモリセルアレイについて繰り返し書き換え特性および抵抗分離を調べたところ、図25(A)および図25(B)に示したように、実施例1と同等の結果が得られた。

第1層22Aを、Zr膜をプラズマ酸化することにより形成したことを除いては、実施例1と同様にしてメモリセルアレイを作製した。得られたメモリセルアレイについて繰り返し書き換え特性および抵抗分離を調べたところ、図26(A)および図26(B)に示したように、実施例1と同等の結果が得られた。

中間層21AをGeS、イオン供給層21BをCuZrTeAlGeにより構成したことを除いては、実施例1と同様にしてメモリセルアレイを作製した。得られたメモリセルアレイについて、繰り返し書き換え特性および抵抗分離を調べたところ、図27(A)および図27(B)に示したように、実施例1と同等の結果が得られた。

中間層21AをTe、イオン供給層21BをCuTiTeAlにより構成したことを除いては、実施例1と同様にしてメモリセルアレイを作製した。得られたメモリセルアレイについて、繰り返し書き換え特性および抵抗分離を調べたところ、実施例1と同等の結果が得られた。

中間層21AをTe(厚み5nm)、イオン供給層21BをAg7Zr14Te36Al43(厚み45nm)、上部電極30をZr(厚み50nm)により構成したことを除いては、実施例2と同様にしてメモリセルアレイを作製した。得られたメモリセルアレイについて、繰り返し書き換え特性および抵抗分離を調べたところ、図28(A)および図28(B)に示したように、実施例2と同等の結果が得られた。

中間層21AをTe(厚み5nm)、イオン供給層21BをNi13Zr13Te33Al40(厚み45nm)、上部電極30をZr(厚み50nm)により構成したことを除いては、実施例2と同様にしてメモリセルアレイを作製した。得られたメモリセルアレイについて、繰り返し書き換え特性および抵抗分離を調べたところ、図29(A)および図29(B)に示したように、実施例2と同等の結果が得られた。

中間層21AをTe(厚み5nm)、イオン供給層21BをCo7Zr14Te36Al43(厚み45nm)、上部電極30をZr(厚み50nm)により構成したことを除いては、実施例2と同様にしてメモリセルアレイを作製した。得られたメモリセルアレイについて、繰り返し書き換え特性および抵抗分離を調べたところ、図30(A)および図30(B)に示したように、実施例2と同等の結果が得られた。

中間層21AをTe(厚み5nm)、イオン供給層21BをMn13Zr13Te33Al40(厚み45nm)、上部電極30をZr(厚み50nm)により構成したことを除いては、実施例2と同様にしてメモリセルアレイを作製した。得られたメモリセルアレイについて、繰り返し書き換え特性および抵抗分離を調べたところ、図31(A)および図31(B)に示したように、実施例2と同等の結果が得られた。

中間層21AをTe(厚み5nm)、イオン供給層21BをFe10Zr16Te39Al35(厚み45nm)、上部電極30をZr(厚み50nm)により構成したことを除いては、実施例2と同様にしてメモリセルアレイを作製した。得られたメモリセルアレイについて、繰り返し書き換え特性および抵抗分離を調べたところ、図32(A)および図32(B)に示したように、実施例2と同等の結果が得られた。

イオン供給層21BをCu10Hf14Te37Al38により構成したことを除いては、実施例2と同様にしてメモリセルアレイを作製した。得られたメモリセルアレイについて、累積度数分布,繰り返し書き換え特性および抵抗分離を調べたところ、図33(A)ないし図33(C)に示したように、実施例2と同等の結果が得られた。

イオン供給層21BをCu10Ti14Te37Al38により構成したことを除いては、実施例2と同様にしてメモリセルアレイを作製した。得られたメモリセルアレイについて、累積度数分布,繰り返し書き換え特性および抵抗分離を調べたところ、図34(A)ないし図34(C)に示したように、実施例2と同等の結果が得られた。

中間層21AをAl1Te9(厚み3.2nm)、イオン供給層21BをCu12.5Hf7.5Te35.4Al38Ge6.6(厚み60nm)、上部電極30をタングステン(W)(厚み30nm)により構成したことを除いては、実施例2と同様にしてメモリセルアレイを作製した。得られたメモリセルアレイについて、累積度数分布,繰り返し書き換え特性および抵抗分離を調べたところ、図35(A)ないし図35(C)に示したように、実施例2と同等の結果が得られた。

実施例2と同様にして4kbitのメモリセルアレイを作製した。その際、窒化チタン(TiN)よりなる下部電極10の表面を直接プラズマ酸化することにより酸化チタン(TiOx)よりなる第1層22Aを形成した。得られた四つのサンプル(実施例8−1〜8−4)について、第1層22Aの厚みおよび密度を、X線反射率法を用いて調べた。その結果を表1に示す。

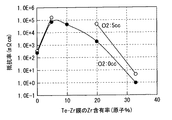

実施例1と同様にして4kbitのメモリセルアレイを作製した。その際、TiNよりなる下部電極10の上面に、遷移金属材料膜としてZr膜を形成し、このZr膜を酸化することにより、ZrOx層22A1を形成した。その際、結果としてTiOx層22A2も形成され、図2における第1層22Aが形成された。また、本実施例ではZrを用いてZrOx層22A1を形成したが、ZrNを酸化することにより、ZrOx層22A1を形成してもよい。(図2参照。)。

上記第2の実施の形態と同様にして記憶素子1を備えたメモリセルアレイを作製した。まず、TiNよりなる下部電極10のプラグが形成してあるCMOS回路上に、リアクティブスパッタによりZrN膜を0.5nmの厚みで形成した。成膜条件としては、Zrターゲットに印加する電圧は3.5kW、チャンバー内に流すアルゴン(Ar),窒素(N2)の流量はそれぞれ25sccm,300sccmとし、全体の圧力は2.1E-3(Torr)とした。このときのAr雰囲気の分圧は2.0E-4(Torr)、窒素雰囲気の分圧は1.9E-3(Torr)と見積もっている。次いで、このZrN膜を酸化プラズマで酸化してZrONよりなる第1層22Aを形成した。

上記第3の実施の形態と同様にして記憶素子1を備えたメモリセルアレイを作製した。まず、TiNよりなる下部電極10のプラグが形成してあるCMOS回路上に、実施例10と同様にしてリアクティブスパッタによりZrN膜を0.5nmの厚みで形成した。次いで、このZrN膜を酸化プラズマで酸化してZrONよりなる第1層22Aを形成した。

下部電極10にWNを用いた以外は,実施例11と同様にしてメモリセルアレイを作製した。本実施例の工程を簡略的に示すと以下のようになる。

実施例10と同様にして記憶素子1を備えたメモリセルアレイを作製した。その際、TiNよりなる下部電極10のプラグが形成してあるCMOS回路上に、実施例13−1ではTiN膜、実施例13−2では窒化タンタル(TaN)膜、実施例13−3では窒化ハフニウム(HfN)膜をそれぞれ形成した。それぞれの膜を酸化プラズマで酸化して、実施例13−1ではTiON、実施例13−2ではタンタルの酸窒化物(TaON)、実施例13−3ではハフニウムの酸窒化物(HfON)よりなる第1層22Aを形成した。

上記第4の実施の形態と同様にして記憶素子1を備えたメモリセルアレイを作製した。まず、TiNよりなる下部電極10のプラグが形成してあるCMOS回路上に、実施例10と同様にしてリアクティブスパッタによりZrN膜を0.5nmの厚みで形成した。次いで、このZrN膜を酸化プラズマで酸化してZrONよりなる第1層22Aを形成した。

上記第4の実施の形態と同様にして記憶素子1を備えたメモリセルアレイを作製した。まず、TiNよりなる下部電極10のプラグが形成してあるCMOS回路上に、実施例10と同様にしてリアクティブスパッタによりZrN膜を0.5nmの厚みで形成した。次いで、このZrN膜を酸化プラズマで酸化してZrONよりなる第1層22Aを形成した。

上記第4の実施の形態と同様にして記憶素子1を備えたメモリセルアレイを作製した。まず、TiNよりなる下部電極10のプラグが形成してあるCMOS回路上に、実施例10と同様にしてリアクティブスパッタによりZrN膜を0.5nmの厚みで形成した。次いで、このZrN膜を酸化プラズマで酸化してZrONよりなる第1層22Aを形成した。

上記第4の実施の形態と同様にして記憶素子1を備えたメモリセルアレイを作製した。まず、TiNよりなる下部電極10のプラグが形成してあるCMOS回路上に、実施例10と同様にしてリアクティブスパッタによりZrN膜を0.5nmの厚みで形成した。次いで、このZrN膜を酸化プラズマで酸化してZrONよりなる第1層22Aを形成した。

上記第4の実施の形態と同様にして記憶素子1を備えたメモリセルアレイを作製した。まず、CMOS回路上に露出しているTiNよりなる下部電極10を酸化プラズマで酸化することにより、TiOxよりなる第1層22Aを約1nmの厚みで形成した。

中間層21AをCrTeにより構成したことを除いては、実施例18と同様にして記録素子1を有するメモリセルアレイを作製した。本実施例の工程を簡略的に示すと以下のようになる。

中間層をTeにより構成したことを除いては、実施例18と同様にして記録素子を有するメモリセルアレイを作製した。比較例4の工程を簡略的に示すと以下のようになる。

Te 0.27Ωcm

CuZrTeOx 0.44Ωcm

CrTe 0.56Ωcm

中間層21AをMnTeにより構成したことを除いては、実施例19と同様にして記録素子1を有するメモリセルアレイを作製した。実施例20の工程を簡略的に示すと以下のようになる。

Claims (19)

- 第1電極、記憶層および第2電極をこの順に有し、

前記記憶層は、

テルル(Te),硫黄(S)およびセレン(Se)のうち少なくとも1種のカルコゲン元素と共にアルミニウム(Al)を含むイオン源層と、

前記イオン源層と前記第1電極との間に設けられると共に、前記第1電極の側から順に第1層と第2層とが積層された構成を有し、前記第2層はアルミニウム酸化物を主成分とし、前記第1層は前記アルミニウム酸化物よりも抵抗の低い遷移金属酸化物および遷移金属酸窒化物のうち少なくとも一方よりなる抵抗変化層と

を備えた記憶素子。 - 前記第1層は、1nm以上かつ前記第2層の抵抗値よりも低抵抗となる厚みを有する

請求項1記載の記憶素子。 - 前記抵抗変化層は、前記アルミニウム酸化物と、前記遷移金属酸化物および遷移金属酸窒化物のうち少なくとも一方とを混在した状態で含有する

請求項1記載の記憶素子。 - 前記遷移金属酸化物または遷移金属酸窒化物は、チタン(Ti),ジルコニウム(Zr),ハフニウム(Hf),バナジウム(V),ニオブ(Nb),タンタル(Ta),クロム(Cr),モリブデン(Mo)およびタングステン(W)からなる遷移金属の群のうち少なくとも1種の酸化物または酸窒化物である

請求項1ないし3のいずれか1項に記載の記憶素子。 - 前記イオン源層は、

アルミニウム(Al)と共に、テルル(Te),硫黄(S)およびセレン(Se)のうち少なくとも1種のカルコゲン元素を含む中間層と、

アルミニウム(Al)および前記カルコゲン元素と共に、銅(Cu),亜鉛(Zn),銀(Ag),ニッケル(Ni),コバルト(Co),マンガン(Mn),鉄(Fe),チタン(Ti),ジルコニウム(Zr),ハフニウム(Hf),バナジウム(V),ニオブ(Nb),タンタル(Ta),クロム(Cr),モリブデン(Mo)およびタングステン(W)からなる金属元素の群のうちの少なくとも1種を含むイオン供給層と

を有する請求項1ないし4のいずれか1項に記載の記憶素子。 - 前記中間層におけるカルコゲン元素含有量に対するアルミニウム含有量の比は、前記イオン供給層におけるカルコゲン元素含有量に対するアルミニウム含有量の比よりも小さい

請求項5記載の記憶素子。 - 前記中間層は、前記イオン供給層よりも高い抵抗を有する

請求項5または6記載の記憶素子。 - 前記中間層は、ジルコニウム(Zr),銅(Cu),クロム(Cr),マンガン(Mn),チタン(Ti)およびハフニウム(Hf)からなる遷移金属の群のうち少なくとも1種を含む

請求項5ないし7のいずれか1項に記載の記憶素子。 - 前記中間層および前記イオン供給層のうち少なくとも一方が、酸素(O)を含む

請求項5ないし7のいずれか1項に記載の記憶素子。 - 前記中間層は、酸素(O)と、銅(Cu),チタン(Ti),ジルコニウム(Zr),ハフニウム(Hf),Cr(クロム)およびMn(マンガン)からなる遷移金属の群のうち少なくとも1種とを含む

請求項5ないし7のいずれか1項に記載の記憶素子。 - 前記第1電極および前記第2電極への電圧印加による前記アルミニウム酸化物の酸化還元と前記イオン源層に含まれる金属元素のイオンの移動とのうち少なくとも一方による前記記憶層の電気特性の変化により情報を記憶する

請求項1ないし10のいずれか1項に記載の記憶素子。 - 前記イオン源層に含まれる金属元素は、銅(Cu),亜鉛(Zn),銀(Ag),ニッケル(Ni),コバルト(Co),マンガン(Mn),鉄(Fe),チタン(Ti),ジルコニウム(Zr),ハフニウム(Hf),バナジウム(V),ニオブ(Nb),タンタル(Ta),クロム(Cr),モリブデン(Mo)およびタングステン(W)からなる群のうちの少なくとも1種である

請求項11記載の記憶素子。 - 前記アルミニウム酸化物は、前記イオン源層に含まれるアルミニウム(Al)イオンの移動あるいは拡散、または前記第1電極および前記第2電極への電圧印加による、前記第1電極側での酸化反応により形成されたものである

請求項11または12記載の記憶素子。 - 前記第1電極は、チタン(Ti),ジルコニウム(Zr),ハフニウム(Hf),バナジウム(V),ニオブ(Nb),タンタル(Ta),クロム(Cr),モリブデン(Mo)およびタングステン(W)からなる遷移金属の群のうちの少なくとも1種の単体または窒化物により構成され、

前記遷移金属酸化物および遷移金属酸窒化物のうち少なくとも一方は、前記第1電極の表面を酸化することにより形成されたものである

請求項1ないし13のいずれか1項に記載の記憶素子。 - 前記遷移金属酸化物および遷移金属酸窒化物のうち少なくとも一方は、前記第1電極の上面にチタン(Ti),ジルコニウム(Zr),ハフニウム(Hf),バナジウム(V),ニオブ(Nb),タンタル(Ta),クロム(Cr),モリブデン(Mo)およびタングステン(W)からなる遷移金属の群のうちの少なくとも1種の単体または窒化物よりなる遷移金属材料膜を形成し、前記遷移金属材料膜と前記第1電極の表面とのうち少なくとも前記遷移金属材料膜を酸化することにより形成されたものである

請求項1ないし13のいずれか1項に記載の記憶素子。 - 第1電極、記憶層および第2電極をこの順に有する複数の記憶素子と、前記複数の記憶素子に対して選択的に電圧または電流のパルスを印加するパルス印加手段とを備え、

前記記憶層は、

テルル(Te),硫黄(S)およびセレン(Se)のうち少なくとも1種のカルコゲン元素と共にアルミニウム(Al)を含むイオン源層と、

前記イオン源層と前記第1電極との間に設けられると共に、前記第1電極の側から順に第1層と第2層とが積層された構成を有し、前記第2層はアルミニウム酸化物を主成分とし、前記第1層は前記アルミニウム酸化物よりも抵抗の低い遷移金属酸化物および遷移金属酸窒化物のうち少なくとも一方よりなる抵抗変化層と

を備えた記憶装置。 - 隣接する前記複数の記憶素子において、前記記憶素子を構成する少なくとも一部の層が同一層により共通に設けられている

請求項16記載の記憶装置。 - 前記複数の記憶素子における共通の層は、前記抵抗変化層、前記イオン源層および前記第2電極であり、前記第1電極は素子毎に個別に設けられている

請求項17記載の記憶装置。 - 第1電極、記憶層および第2電極をこの順に有する複数の記憶素子と、前記複数の記憶素子に対して選択的に電圧または電流のパルスを印加するパルス印加手段とを備え、前記記憶層は、テルル(Te),硫黄(S)およびセレン(Se)のうち少なくとも1種のカルコゲン元素と共にアルミニウム(Al)およびアルミニウム(Al)とは異なる金属元素を含むイオン源層と、 前記イオン源層と前記第1電極との間に設けられると共に、前記第1電極の側から順に第1層と第2層とが積層された構成を有し、前記第2層はアルミニウム酸化物を主成分とし、前記第1層は前記アルミニウム酸化物よりも抵抗の低い遷移金属酸化物および遷移金属酸窒化物のうち少なくとも一方よりなる抵抗変化層とを備えた記憶装置の動作方法であって、

前記第1電極および前記第2電極の間に電圧を印加することにより、前記イオン源層中ではアルミニウム(Al)イオンおよび前記イオン源層に含まれる金属元素のイオンが前記第1電極側に移動すると共に、前記抵抗変化層ではアルミニウム酸化物または前記金属元素のイオンの還元反応により導電パスが生じて低抵抗化し、

前記第1電極および前記第2電極の間に逆極性の電圧を印加することにより、前記イオン源層中ではアルミニウム(Al)イオンおよび前記イオン源層に含まれる金属元素のイオンが前記第2電極側へ移動すると共に、前記抵抗変化層ではアルミニウム(Al)イオンが酸化反応によりアルミニウム酸化物を形成して高抵抗化するか、または前記還元された金属元素がイオン化して前記イオン源層に移動することにより前記導電パスが消失して高抵抗化する

記憶装置の動作方法。

Priority Applications (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010261517A JP5732827B2 (ja) | 2010-02-09 | 2010-11-24 | 記憶素子および記憶装置、並びに記憶装置の動作方法 |

| TW099146694A TWI443821B (zh) | 2010-02-09 | 2010-12-29 | A memory element and a memory device, and a method of operating the memory device |

| KR1020110005337A KR101785727B1 (ko) | 2010-02-09 | 2011-01-19 | 기억 소자 및 기억 장치, 및 기억 장치의 동작 방법 |

| CN201110035461.9A CN102194512B (zh) | 2010-02-09 | 2011-02-01 | 存储元件、存储装置以及存储装置操作方法 |

| US13/018,744 US8427860B2 (en) | 2010-02-09 | 2011-02-01 | Memory component, memory device, and method of operating memory device |

| US13/846,193 US8730709B2 (en) | 2010-02-09 | 2013-03-18 | Memory component, memory device, and method of operating memory device |

| US14/201,376 US9240549B2 (en) | 2010-02-09 | 2014-03-07 | Memory component, memory device, and method of operating memory device |

| US14/950,512 US9543514B2 (en) | 2010-02-09 | 2015-11-24 | Memory component, memory device, and method of operating memory device |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010026573 | 2010-02-09 | ||

| JP2010026573 | 2010-02-09 | ||

| JP2010261517A JP5732827B2 (ja) | 2010-02-09 | 2010-11-24 | 記憶素子および記憶装置、並びに記憶装置の動作方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011187925A JP2011187925A (ja) | 2011-09-22 |

| JP2011187925A5 JP2011187925A5 (ja) | 2014-01-09 |

| JP5732827B2 true JP5732827B2 (ja) | 2015-06-10 |

Family

ID=44353600

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010261517A Expired - Fee Related JP5732827B2 (ja) | 2010-02-09 | 2010-11-24 | 記憶素子および記憶装置、並びに記憶装置の動作方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (4) | US8427860B2 (ja) |

| JP (1) | JP5732827B2 (ja) |

| KR (1) | KR101785727B1 (ja) |

| CN (1) | CN102194512B (ja) |

| TW (1) | TWI443821B (ja) |

Families Citing this family (87)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9570678B1 (en) | 2010-06-08 | 2017-02-14 | Crossbar, Inc. | Resistive RAM with preferental filament formation region and methods |

| US9012307B2 (en) | 2010-07-13 | 2015-04-21 | Crossbar, Inc. | Two terminal resistive switching device structure and method of fabricating |

| US9601692B1 (en) | 2010-07-13 | 2017-03-21 | Crossbar, Inc. | Hetero-switching layer in a RRAM device and method |

| US8946046B1 (en) | 2012-05-02 | 2015-02-03 | Crossbar, Inc. | Guided path for forming a conductive filament in RRAM |

| WO2011156787A2 (en) | 2010-06-11 | 2011-12-15 | Crossbar, Inc. | Pillar structure for memory device and method |

| US8374018B2 (en) | 2010-07-09 | 2013-02-12 | Crossbar, Inc. | Resistive memory using SiGe material |

| US8947908B2 (en) | 2010-11-04 | 2015-02-03 | Crossbar, Inc. | Hetero-switching layer in a RRAM device and method |

| US8569172B1 (en) | 2012-08-14 | 2013-10-29 | Crossbar, Inc. | Noble metal/non-noble metal electrode for RRAM applications |

| US8884261B2 (en) | 2010-08-23 | 2014-11-11 | Crossbar, Inc. | Device switching using layered device structure |

| US8168506B2 (en) | 2010-07-13 | 2012-05-01 | Crossbar, Inc. | On/off ratio for non-volatile memory device and method |

| US9401475B1 (en) | 2010-08-23 | 2016-07-26 | Crossbar, Inc. | Method for silver deposition for a non-volatile memory device |

| US8889521B1 (en) | 2012-09-14 | 2014-11-18 | Crossbar, Inc. | Method for silver deposition for a non-volatile memory device |

| US8492195B2 (en) | 2010-08-23 | 2013-07-23 | Crossbar, Inc. | Method for forming stackable non-volatile resistive switching memory devices |

| US8558212B2 (en) | 2010-09-29 | 2013-10-15 | Crossbar, Inc. | Conductive path in switching material in a resistive random access memory device and control |

| US8502185B2 (en) | 2011-05-31 | 2013-08-06 | Crossbar, Inc. | Switching device having a non-linear element |

| USRE46335E1 (en) | 2010-11-04 | 2017-03-07 | Crossbar, Inc. | Switching device having a non-linear element |

| US8930174B2 (en) | 2010-12-28 | 2015-01-06 | Crossbar, Inc. | Modeling technique for resistive random access memory (RRAM) cells |

| US8791010B1 (en) | 2010-12-31 | 2014-07-29 | Crossbar, Inc. | Silver interconnects for stacked non-volatile memory device and method |

| US8815696B1 (en) | 2010-12-31 | 2014-08-26 | Crossbar, Inc. | Disturb-resistant non-volatile memory device using via-fill and etchback technique |

| US9153623B1 (en) | 2010-12-31 | 2015-10-06 | Crossbar, Inc. | Thin film transistor steering element for a non-volatile memory device |

| JP2012199336A (ja) | 2011-03-18 | 2012-10-18 | Sony Corp | 記憶素子および記憶装置 |

| US8546781B2 (en) * | 2011-05-31 | 2013-10-01 | The Board Of Trustees Of The Leland Stanford Junior University | Nitrogen doped aluminum oxide resistive random access memory |

| US9620206B2 (en) | 2011-05-31 | 2017-04-11 | Crossbar, Inc. | Memory array architecture with two-terminal memory cells |

| US8618525B2 (en) * | 2011-06-09 | 2013-12-31 | Intermolecular, Inc. | Work function tailoring for nonvolatile memory applications |

| US8619459B1 (en) | 2011-06-23 | 2013-12-31 | Crossbar, Inc. | High operating speed resistive random access memory |

| US8946669B1 (en) | 2012-04-05 | 2015-02-03 | Crossbar, Inc. | Resistive memory device and fabrication methods |

| JP2013016530A (ja) * | 2011-06-30 | 2013-01-24 | Sony Corp | 記憶素子およびその製造方法ならびに記憶装置 |

| US9627443B2 (en) | 2011-06-30 | 2017-04-18 | Crossbar, Inc. | Three-dimensional oblique two-terminal memory with enhanced electric field |

| US9564587B1 (en) | 2011-06-30 | 2017-02-07 | Crossbar, Inc. | Three-dimensional two-terminal memory with enhanced electric field and segmented interconnects |

| US9166163B2 (en) | 2011-06-30 | 2015-10-20 | Crossbar, Inc. | Sub-oxide interface layer for two-terminal memory |

| JP5708930B2 (ja) * | 2011-06-30 | 2015-04-30 | ソニー株式会社 | 記憶素子およびその製造方法ならびに記憶装置 |

| EP2735028A4 (en) | 2011-07-22 | 2015-05-06 | Crossbar Inc | SEALING LAYER FOR SILICON-GERMANIUM P + MATERIAL FOR REMAINING MEMORY DEVICE AND ASSOCIATED METHOD |

| US8674724B2 (en) | 2011-07-29 | 2014-03-18 | Crossbar, Inc. | Field programmable gate array utilizing two-terminal non-volatile memory |

| US8866121B2 (en) | 2011-07-29 | 2014-10-21 | Sandisk 3D Llc | Current-limiting layer and a current-reducing layer in a memory device |

| US10056907B1 (en) | 2011-07-29 | 2018-08-21 | Crossbar, Inc. | Field programmable gate array utilizing two-terminal non-volatile memory |

| US9729155B2 (en) | 2011-07-29 | 2017-08-08 | Crossbar, Inc. | Field programmable gate array utilizing two-terminal non-volatile memory |

| US8659001B2 (en) | 2011-09-01 | 2014-02-25 | Sandisk 3D Llc | Defect gradient to boost nonvolatile memory performance |

| US8637413B2 (en) | 2011-12-02 | 2014-01-28 | Sandisk 3D Llc | Nonvolatile resistive memory element with a passivated switching layer |

| JP5480233B2 (ja) * | 2011-12-20 | 2014-04-23 | 株式会社東芝 | 不揮発性記憶装置、及びその製造方法 |

| US8698119B2 (en) | 2012-01-19 | 2014-04-15 | Sandisk 3D Llc | Nonvolatile memory device using a tunnel oxide as a current limiter element |

| JP6218388B2 (ja) * | 2012-02-06 | 2017-10-25 | アイメックImec | 自己絶縁型導電性ブリッジメモリデバイス |

| US8686386B2 (en) | 2012-02-17 | 2014-04-01 | Sandisk 3D Llc | Nonvolatile memory device using a varistor as a current limiter element |

| US9082971B2 (en) | 2012-02-20 | 2015-07-14 | Panasonic Intellectual Property Management Co., Ltd. | Nonvolatile memory device and method for manufacturing the same |

| JP2013187336A (ja) | 2012-03-07 | 2013-09-19 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2013201271A (ja) | 2012-03-23 | 2013-10-03 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US9099633B2 (en) | 2012-03-26 | 2015-08-04 | Adesto Technologies Corporation | Solid electrolyte memory elements with electrode interface for improved performance |

| US9087576B1 (en) | 2012-03-29 | 2015-07-21 | Crossbar, Inc. | Low temperature fabrication method for a three-dimensional memory device and structure |

| JP6050015B2 (ja) * | 2012-03-30 | 2016-12-21 | ソニーセミコンダクタソリューションズ株式会社 | 記憶素子および記憶装置 |

| US9685608B2 (en) | 2012-04-13 | 2017-06-20 | Crossbar, Inc. | Reduced diffusion in metal electrode for two-terminal memory |

| US8658476B1 (en) | 2012-04-20 | 2014-02-25 | Crossbar, Inc. | Low temperature P+ polycrystalline silicon material for non-volatile memory device |

| US8796658B1 (en) | 2012-05-07 | 2014-08-05 | Crossbar, Inc. | Filamentary based non-volatile resistive memory device and method |

| JP6162931B2 (ja) * | 2012-06-19 | 2017-07-12 | ソニーセミコンダクタソリューションズ株式会社 | 記憶素子および記憶装置 |

| JP5783961B2 (ja) * | 2012-07-09 | 2015-09-24 | 株式会社東芝 | 不揮発性記憶装置 |

| US9741765B1 (en) | 2012-08-14 | 2017-08-22 | Crossbar, Inc. | Monolithically integrated resistive memory using integrated-circuit foundry compatible processes |

| US9583701B1 (en) | 2012-08-14 | 2017-02-28 | Crossbar, Inc. | Methods for fabricating resistive memory device switching material using ion implantation |

| JP2014038675A (ja) * | 2012-08-15 | 2014-02-27 | Sony Corp | 記憶装置および駆動方法 |

| US8946673B1 (en) | 2012-08-24 | 2015-02-03 | Crossbar, Inc. | Resistive switching device structure with improved data retention for non-volatile memory device and method |

| US9312483B2 (en) | 2012-09-24 | 2016-04-12 | Crossbar, Inc. | Electrode structure for a non-volatile memory device and method |

| US9576616B2 (en) | 2012-10-10 | 2017-02-21 | Crossbar, Inc. | Non-volatile memory with overwrite capability and low write amplification |

| US11068620B2 (en) | 2012-11-09 | 2021-07-20 | Crossbar, Inc. | Secure circuit integrated with memory layer |

| US8982647B2 (en) | 2012-11-14 | 2015-03-17 | Crossbar, Inc. | Resistive random access memory equalization and sensing |

| US9412790B1 (en) | 2012-12-04 | 2016-08-09 | Crossbar, Inc. | Scalable RRAM device architecture for a non-volatile memory device and method |

| CN104871313B (zh) * | 2012-12-26 | 2018-12-11 | 索尼半导体解决方案公司 | 存储装置和存储装置制造方法 |

| US9406379B2 (en) | 2013-01-03 | 2016-08-02 | Crossbar, Inc. | Resistive random access memory with non-linear current-voltage relationship |

| US8921821B2 (en) | 2013-01-10 | 2014-12-30 | Micron Technology, Inc. | Memory cells |

| US9112145B1 (en) | 2013-01-31 | 2015-08-18 | Crossbar, Inc. | Rectified switching of two-terminal memory via real time filament formation |

| US9324942B1 (en) | 2013-01-31 | 2016-04-26 | Crossbar, Inc. | Resistive memory cell with solid state diode |

| CN105378959A (zh) * | 2013-03-03 | 2016-03-02 | Adesto技术公司 | 可编程的阻抗储存元件和相应的方法 |

| US9252359B2 (en) | 2013-03-03 | 2016-02-02 | Adesto Technologies Corporation | Resistive switching devices having a switching layer and an intermediate electrode layer and methods of formation thereof |

| US9412945B1 (en) | 2013-03-14 | 2016-08-09 | Adesto Technologies Corporation | Storage elements, structures and methods having edgeless features for programmable layer(s) |

| WO2014146003A1 (en) | 2013-03-15 | 2014-09-18 | Adesto Technologies Corporation | Nonvolatile memory with semimetal or semiconductors electrodes |

| CN103268917A (zh) * | 2013-05-28 | 2013-08-28 | 清华大学 | 应用于阻变存储器的Al-W-O堆叠结构 |

| US9105572B2 (en) * | 2013-09-09 | 2015-08-11 | Hiroyuki Kanaya | Magnetic memory and manufacturing method thereof |

| US9461242B2 (en) | 2013-09-13 | 2016-10-04 | Micron Technology, Inc. | Magnetic memory cells, methods of fabrication, semiconductor devices, memory systems, and electronic systems |

| US9608197B2 (en) | 2013-09-18 | 2017-03-28 | Micron Technology, Inc. | Memory cells, methods of fabrication, and semiconductor devices |

| US10290801B2 (en) | 2014-02-07 | 2019-05-14 | Crossbar, Inc. | Scalable silicon based resistive memory device |

| US10454024B2 (en) | 2014-02-28 | 2019-10-22 | Micron Technology, Inc. | Memory cells, methods of fabrication, and memory devices |

| US9281466B2 (en) | 2014-04-09 | 2016-03-08 | Micron Technology, Inc. | Memory cells, semiconductor structures, semiconductor devices, and methods of fabrication |

| US9548450B2 (en) | 2014-09-23 | 2017-01-17 | Micron Technology, Inc. | Devices containing metal chalcogenides |

| TWI696997B (zh) | 2014-10-07 | 2020-06-21 | 美商愛德斯托科技公司 | 具有導電性帽層的記憶體元件及其方法 |

| US9349945B2 (en) | 2014-10-16 | 2016-05-24 | Micron Technology, Inc. | Memory cells, semiconductor devices, and methods of fabrication |

| US9768377B2 (en) | 2014-12-02 | 2017-09-19 | Micron Technology, Inc. | Magnetic cell structures, and methods of fabrication |

| US10439131B2 (en) | 2015-01-15 | 2019-10-08 | Micron Technology, Inc. | Methods of forming semiconductor devices including tunnel barrier materials |

| US9431606B1 (en) * | 2015-08-12 | 2016-08-30 | Micron Technology, Inc. | Memory cells |

| US11393515B2 (en) * | 2018-06-14 | 2022-07-19 | Intel Corporation | Transition metal dichalcogenide based spin orbit torque memory device |

| KR102081020B1 (ko) * | 2019-04-05 | 2020-02-24 | 연세대학교 산학협력단 | 선택 소자 및 이의 제조 방법 |

| WO2022055197A1 (ko) * | 2020-09-09 | 2022-03-17 | 한양대학교 산학협력단 | 칼코겐 원소가 도핑된 선택 소자 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000048196A (ja) | 1998-07-27 | 2000-02-18 | Miyachi Technos Corp | 溶接状況状態記録方法および溶接状況状態記録装置 |

| EP1159743B1 (en) | 1999-02-11 | 2007-05-02 | Arizona Board of Regents | Programmable microelectronic devices and methods of forming and programming same |

| US6867996B2 (en) * | 2002-08-29 | 2005-03-15 | Micron Technology, Inc. | Single-polarity programmable resistance-variable memory element |

| JP4792714B2 (ja) | 2003-11-28 | 2011-10-12 | ソニー株式会社 | 記憶素子及び記憶装置 |

| KR100623177B1 (ko) * | 2005-01-25 | 2006-09-13 | 삼성전자주식회사 | 높은 유전율을 갖는 유전체 구조물, 이의 제조 방법, 이를포함하는 불휘발성 반도체 메모리 장치 및 그 제조 방법 |

| US7608848B2 (en) * | 2006-05-09 | 2009-10-27 | Macronix International Co., Ltd. | Bridge resistance random access memory device with a singular contact structure |

| US20080016684A1 (en) * | 2006-07-06 | 2008-01-24 | General Electric Company | Corrosion resistant wafer processing apparatus and method for making thereof |

| US7388771B2 (en) * | 2006-10-24 | 2008-06-17 | Macronix International Co., Ltd. | Methods of operating a bistable resistance random access memory with multiple memory layers and multilevel memory states |

| KR20080064353A (ko) * | 2007-01-04 | 2008-07-09 | 삼성전자주식회사 | 저항 메모리 소자 및 그 제조 방법 |

| US7663135B2 (en) * | 2007-01-31 | 2010-02-16 | Macronix International Co., Ltd. | Memory cell having a side electrode contact |

| JP2009043873A (ja) * | 2007-08-08 | 2009-02-26 | Sony Corp | 記憶素子および記憶装置 |

| JP2009043905A (ja) * | 2007-08-08 | 2009-02-26 | Hitachi Ltd | 半導体装置 |

| JP5557419B2 (ja) * | 2007-10-17 | 2014-07-23 | スパンション エルエルシー | 半導体装置 |

| JP2009135370A (ja) * | 2007-12-03 | 2009-06-18 | Panasonic Corp | 不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置 |

| JP4466738B2 (ja) * | 2008-01-09 | 2010-05-26 | ソニー株式会社 | 記憶素子および記憶装置 |

| US20090283739A1 (en) * | 2008-05-19 | 2009-11-19 | Masahiro Kiyotoshi | Nonvolatile storage device and method for manufacturing same |

| WO2009141857A1 (ja) * | 2008-05-22 | 2009-11-26 | パナソニック株式会社 | 抵抗変化型不揮発性記憶装置 |

| JP5191803B2 (ja) * | 2008-05-29 | 2013-05-08 | 株式会社東芝 | 不揮発性記憶装置の製造方法 |

| US8279650B2 (en) | 2009-04-20 | 2012-10-02 | Sandisk 3D Llc | Memory system with data line switching scheme |

-

2010

- 2010-11-24 JP JP2010261517A patent/JP5732827B2/ja not_active Expired - Fee Related

- 2010-12-29 TW TW099146694A patent/TWI443821B/zh not_active IP Right Cessation

-

2011

- 2011-01-19 KR KR1020110005337A patent/KR101785727B1/ko active IP Right Grant

- 2011-02-01 US US13/018,744 patent/US8427860B2/en not_active Expired - Fee Related

- 2011-02-01 CN CN201110035461.9A patent/CN102194512B/zh not_active Expired - Fee Related

-

2013

- 2013-03-18 US US13/846,193 patent/US8730709B2/en active Active

-

2014

- 2014-03-07 US US14/201,376 patent/US9240549B2/en active Active

-

2015

- 2015-11-24 US US14/950,512 patent/US9543514B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR20110093620A (ko) | 2011-08-18 |

| US20110194329A1 (en) | 2011-08-11 |

| US9543514B2 (en) | 2017-01-10 |

| US20160079528A1 (en) | 2016-03-17 |

| CN102194512B (zh) | 2015-05-20 |

| TW201143082A (en) | 2011-12-01 |

| JP2011187925A (ja) | 2011-09-22 |

| US20140183438A1 (en) | 2014-07-03 |

| US9240549B2 (en) | 2016-01-19 |

| CN102194512A (zh) | 2011-09-21 |

| TWI443821B (zh) | 2014-07-01 |

| US8427860B2 (en) | 2013-04-23 |

| KR101785727B1 (ko) | 2017-10-16 |

| US8730709B2 (en) | 2014-05-20 |

| US20130240818A1 (en) | 2013-09-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5732827B2 (ja) | 記憶素子および記憶装置、並びに記憶装置の動作方法 | |

| JP5088036B2 (ja) | 記憶素子および記憶装置 | |

| JP5397668B2 (ja) | 記憶素子および記憶装置 | |

| US8687404B2 (en) | Memory element and drive method for the same, and memory device | |

| JP4539885B2 (ja) | 記憶素子および記憶装置 | |

| US20140183437A1 (en) | Memory element and memory device | |

| JP5728919B2 (ja) | 記憶素子および記憶装置 | |

| JP5434921B2 (ja) | 記憶素子および記憶装置 | |

| JP2009043873A (ja) | 記憶素子および記憶装置 | |

| KR102040329B1 (ko) | 기억 소자 및 그 제조 방법 및 기억 장치 | |

| JP2011124511A (ja) | 記憶素子および記憶装置 | |

| JP6272235B2 (ja) | 記憶素子および記憶装置 | |

| JP2004342843A (ja) | 半導体記憶素子及びこれを用いた半導体記憶装置 | |

| JP4552752B2 (ja) | 記憶素子の製造方法、記憶装置の製造方法 | |

| JP2010278275A (ja) | 半導体記憶装置 | |

| JP6162931B2 (ja) | 記憶素子および記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131115 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20131115 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140718 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140729 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140926 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150317 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150330 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5732827 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |