JP5658287B2 - 光信号検出回路および光受信器 - Google Patents

光信号検出回路および光受信器 Download PDFInfo

- Publication number

- JP5658287B2 JP5658287B2 JP2012554815A JP2012554815A JP5658287B2 JP 5658287 B2 JP5658287 B2 JP 5658287B2 JP 2012554815 A JP2012554815 A JP 2012554815A JP 2012554815 A JP2012554815 A JP 2012554815A JP 5658287 B2 JP5658287 B2 JP 5658287B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- circuit

- output

- optical signal

- phase signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B10/00—Transmission systems employing electromagnetic waves other than radio-waves, e.g. infrared, visible or ultraviolet light, or employing corpuscular radiation, e.g. quantum communication

- H04B10/60—Receivers

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B10/00—Transmission systems employing electromagnetic waves other than radio-waves, e.g. infrared, visible or ultraviolet light, or employing corpuscular radiation, e.g. quantum communication

- H04B10/60—Receivers

- H04B10/66—Non-coherent receivers, e.g. using direct detection

- H04B10/69—Electrical arrangements in the receiver

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B10/00—Transmission systems employing electromagnetic waves other than radio-waves, e.g. infrared, visible or ultraviolet light, or employing corpuscular radiation, e.g. quantum communication

- H04B10/60—Receivers

- H04B10/66—Non-coherent receivers, e.g. using direct detection

- H04B10/69—Electrical arrangements in the receiver

- H04B10/697—Arrangements for reducing noise and distortion

Landscapes

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Amplifiers (AREA)

- Optical Communication System (AREA)

Description

ここで、初段増幅回路21Bにおいて、差動トランジスタ対Q21,Q22の負荷抵抗R25,R26の値を互いに異なる値にすれば、初段増幅回路21Bの出力のDCレベルはオフセット電圧を有することになる。

もし初段増幅回路21Bに入力される正相信号Tout+および逆相信号Tout−の振幅が小さければ、このオフセット電圧のために、トランジスタQ21からの反転出力とトランジスタQ22からの非反転出力は交差しない、すなわち、初段増幅回路21Bが差動信号を形成しない。この場合は、初段増幅回路21Bからの非反転出力および反転出力を入力とする次段増幅回路21Dからパルス状の比較出力信号Coutは出力されない。

この比較出力信号CoutはSRラッチ22で保持される。その結果、例えば光信号Pinの受信開始とともに、光信号入力の有無を示す光信号検出信号SDとしてHighレベルが出力される。SRラッチ22の特徴は、ひとたび比較出力信号CoutとしてHighレベルが出力されればそのレベルが光信号検出信号SDとして保持出力される。したがって、信号受信に即座に応答する高速な光信号検出回路20を実現できる。

これは、検出感度が高すぎれば、バースト信号のない区間においても、混入したノイズを有意パルスとして誤まって検出してしまい、一方、検出感度が低すぎれば、バースト信号の入力があっても、検出遅れが生じてしまうからである。

コンパレータ21の検出感度を調整する構成として、コンパレータ21内部に設けられた増幅回路の負荷抵抗値を、温度や電源電位Vccに応じて外部から自動調整する構成が考えられる。

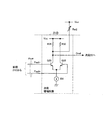

図11は、コンパレータの検出感度を調整する回路の構成例を示している。ここでは、コンパレータ21内の次段増幅回路21Dの負荷抵抗R29,R30のうち負荷抵抗R29に、感度調整用の可変抵抗Radjが並列接続されている。すなわち、可変抵抗Radjの一端が次段増幅回路21DのトランジスタQ25のコレクタ端子に接続され、他端が電源電位Vccに接続されている。このトランジスタQ25および負荷抵抗R29は、初段エミッタフォロワ回路21Cから出力された初段出力信号Foutの逆相信号Fout−の増幅に用いられる。

したがって、例えばSRラッチ22は、入力端子Sにおけるしきい値電圧と比較出力信号Coutのパルス振幅との比較結果により比較出力信号Coutに対するラッチ有無を判断するので、SRラッチ22のしきい値電圧に対する比較出力信号Coutのパルス振幅を調整することによって、結果として、コンパレータ21の検出感度が調整される。

これを換言するならば、本発明にかかる光信号検出回路は、光信号のパルス列に対応するパルスを含む電気信号の正相信号と逆相信号とを差動増幅して差動出力信号を出力する増幅回路と、前記差動出力信号の正相信号の電圧値と逆相信号の電圧値とを比較して、その比較結果に応じたパルス状の比較出力信号を出力するコンパレータと、前記パルス状の比較出力信号に基づいて前記光信号の入力有無を示す光信号検出信号を出力する保持回路とを備え、前記増幅回路は、一端がそれぞれ電源電位Vccに接続されて、前記差動出力信号の前記正相信号および前記逆相信号をそれぞれ生成する第1および第2の負荷抵抗と、前記第1および第2の負荷抵抗の少なくとも一方を流れる直流負荷電流を、外部の調整電圧源からの調整電圧値に応じて調整して、前記差動出力信号の前記正相信号の直流バイアスと前記逆相信号の直流バイアスとの差を調整する電流加算回路とを含むことを特徴とする。

[第1の実施の形態]

まず、図1を参照して、本発明の第1の実施の形態にかかる光受信器および光信号検出回路について説明する。図1は、第1の実施の形態にかかる光受信器および光信号検出回路の構成を示すブロック図である。

フォトダイオードPDは、パルス列からなる光信号光信号Pinを光電変換して光電流信号Iinを出力する光電変換素子である。

トランスインピーダンスアンプTIAは、光電流信号Iinを増幅して、光信号Pinのパルス列に対応するパルスを含む電気信号Toutを出力する。

リミッティングアンプLAは、トランスインピーダンスアンプTIAから出力される電気信号Toutを増幅して、一定振幅のパルスを含む受信出力Routを出力する。リミッティングアンプLAによって、様々な強度の光信号Pinに対して一定振幅の受信出力Routが出力される。

光信号検出回路10は、トランスインピーダンスアンプTIAから出力される電気信号に基づいて光信号の入力有無を検出する。

トランスインピーダンスアンプTIAの出力端子とリミッティングアンプLAの入力端子は、AC結合である場合もあればDC結合である場合もある。

一方、光信号検出回路10は、トランスインピーダンスアンプTIAに対して、リミッティングアンプLAと並列に接続されて、トランスインピーダンスアンプTIAからの電気信号に基づいて、光信号Pinの入力有無を検出する回路部である。

光信号検出回路10は、結合コンデンサCを介してトランスインピーダンスアンプTIAにAC結合されている。

なお、増幅回路11およびコンパレータ12の内部構成の詳細については、図2を参照して後述する。

アナログ保持回路13と出力バッファ14とは、パルス状の比較出力信号Coutに基づいて光信号Pinの入力有無を示す光信号検出信号SDを出力する保持回路を構成する。

このようなヒステリシスは、オペアンプを用いたヒステリシスコンパレータによっても実現でき、シュミットトリガインバータ14Aの代わりに用いてもよい。しかし、一般にオペアンプのスルー・レート(Slew Rate:最大応答速度)は100V/ms以下と遅いため、SDの応答性を示すAssert/Deassert時間を増大することになり、高速応答を実現するには好ましくない。また、ヒステリシスコンパレータを用いる場合は、別途、参照電圧の入力が必要となる。

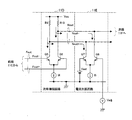

次に、図2および図4を参照して、本実施の形態にかかる光信号検出回路10で用いられる増幅回路11およびコンパレータ12の内部構成について詳細に説明する。

図2は、第1の実施の形態にかかる光信号検出回路10で用いられる増幅回路11およびコンパレータ12の構成例を示す回路図である。図4は、増幅回路12の要部を示す回路図である。

本発明の光信号検出回路では、正相信号と逆相信号に直流バイアスの差を与え、後段のコンパレータ回路を駆動できるか否かかによって受信信号の有無を判定する。そのため、検出感度の調整のためには、増幅回路11において検出対象信号の直流バイアスのみを可変させることが重要である。

具体的には、増幅回路11は、初段バイアス回路11A、初段増幅回路(前側増幅回路)11B、初段エミッタフォロア回路11C、次段増幅回路(後側増幅回路)11D、電流加算回路11E、および次段エミッタフォロア回路11Fを備えている。これらの回路は、半導体チップ上にそれぞれ集積化されている。

このような初段増幅回路11Bは、例えば、差動対をなすトランジスタQ1,Q2と、トランジスタQ1のコレクタ端子と電源電位Vccとの間に接続された抵抗素子R5と、トランジスタQ2のコレクタ端子と電源電位Vccとの間に接続された抵抗素子R6と、トランジスタQ1,Q2のエミッタ端子間に直列接続された抵抗素子R7,R8と、抵抗素子R7,R8の接続点と接地電位GNDとの間に接続された定電流源I1とで構成された差動増幅回路である。

このような初段エミッタフォロア回路11Cは、例えば、初段増幅回路11Bの差動トランジスタQ1,Q2のコレクタ端子にそれぞれ接続されたベース端子と電源電位Vccにそれぞれ接続されたコレクタ端子とを有する2つのトランジスタQ3,Q4と、これらトランジスタQ3,Q4のエミッタ端子と接地電位GNDとの間にそれぞれ接続された定電流源I2,I3とから構成することができる。

初段エミッタフォロア回路11Cは、初段増幅回路11Bの出力インピーダンスよりも低い出力インピーダンスを有するとともに、トランジスタQ3,Q4のベース端子にそれぞれ入力された初段増幅回路11Bの初段出力信号の正相信号および逆相信号を出力する。以下、初段エミッタフォロワ回路11Cを介して出力される初段増幅回路11Bの初段出力信号を「初段出力信号Fout」という。

このような次段増幅回路11Dは、例えば、差動対をなすトランジスタQ5,Q6と、トランジスタQ5のコレクタ端子と電源電位Vccとの間に接続された抵抗素子R9(第1の負荷抵抗)と、トランジスタQ6のコレクタ端子と電源電位Vccとの間に接続された抵抗素子R10(第2の負荷抵抗)と、トランジスタQ5,Q6のエミッタ端子の接続点と接地電位GNDとの間に接続された定電流源I4とで構成された差動増幅回路である。このような次段増幅回路11Dは、トランジスタQ5,Q6のベース端子に入力された、初段出力信号Foutの逆相信号Fout−と正相信号Fout+とを差動増幅し、次段増幅信号Noutを出力する。

このような電流加算回路11Eは、例えば、次段増幅回路11Dの第1の負荷抵抗R9の他端、すなわち、次段増幅回路11DのトランジスタQ5のコレクタ端子に接続されたコレクタ端子(第1の入出力端子)と、所定の電圧値Vsetが入力されるベース端子(制御端子)とを有するトランジスタQ7(第1のトランジスタ)と、第2の負荷抵抗R10の他端、すなわちトランジスタQ6のコレクタ端子に接続されたコレクタ端子と、調整電圧値Vadjが入力されるベース端子と、第1のトランジスタQ7のエミッタ端子(第2の入出力端子)と接続されたエミッタ端子とを備え、第1のトランジスタQ7と差動対をなす第2のトランジスタQ8と、第1のトランジスタQ7のエミッタ端子(第2の入出力端子)と第2のトランジスタQ8のエミッタ端子との接続点に接続された定電流源I5とを含む。

より具体的には、このような電流加算回路11Eは、コレクタ端子がトランジスタQ5のコレクタ端子(正相信号Nout+)に接続されたトランジスタQ7(第1のトランジスタ)と、このトランジスタQ7と差動対をなし、コレクタ端子がトランジスタQ6のコレクタ端子(逆相信号Nout−)に接続されたトランジスタQ8(第2のトランジスタ)と、Q7,Q8のエミッタ端子の接続点と接地電位GNDとの間に接続された定電流源I5と、Q7のベース端子と接地電位GNDとの間に接続された設定電圧源Vsetと、Q8のベース端子と接地電位GNDとの間に外部接続された調整電圧源Vadjとから構成することができる。

この電流加算回路11Eにおいては、差動対をなすトランジスタQ7,Q8のエミッタ端子に定電流源I5が共通接続されているので、トランジスタQ7,Q8に引き込まれる合計電流の大きさは一定であり、かつ、そのトランジスタQ7,Q8のそれぞれに引き込まれる電流は、設定電圧源Vsetと調整電圧源Vadjとの電圧差に応じて分配される。

したがって、調整電圧源Vadjを調整することによって、次段増幅信号Noutの正相信号Nout+の直流バイアスの低下量と逆相信号Nout−の直流バイアスの低下量との差、すなわちオフセット電圧の大きさを調整することができる。

なお、初段エミッタフォロア回路11Cおよび次段エミッタフォロア回路11Fは、出力インピーダンスの調整という、回路実装上の要請から設けられるものであり、本発明の目的を達成するために不可欠なものではない。

このコンパレータ12によって、増幅回路11の次段エミッタフォロア回路11Fから出力された差動出力信号Aoutの正相信号Aout+の電圧値と逆相信号Aout−の電圧値とが比較され、M4のドレイン端子からその比較結果を示す単相(シングルエンド)の比較出力信号Coutが出力される。

次に、図1〜図4を参照して、本実施の形態にかかる光信号検出回路10の動作について説明する。

トランスインピーダンスアンプTIAから入力されたバースト信号(電気信号Tout)は、結合コンデンサCを介して微分波形となって増幅回路11に入力され、初段増幅回路11Bで差動増幅される。この際、抵抗素子R5,R6の抵抗値として、基準値に応じた互いに異なる抵抗値が予め設定されているため、初段出力信号Foutのうち逆相信号Fout−の直流バイアスと正相信号Fout+の直流バイアスとの間には、基準値に相当するオフセット電圧が与えられる。

差動出力信号Aoutの正相信号Aout+と逆相信号Aout−とのオフセット電圧、すなわち両者の重なり具合は、電流加算回路11Eの設定電圧源Vsetと調整電圧源Vadjの電圧差に応じて変化する。

このとき、差動出力信号Aoutの振幅がオフセット電圧に比較して十分な大きさを有する場合は差動出力信号Aoutの正相信号Aout+と逆相信号Aout−が交差するので、正相信号Aout+の電位と逆相信号Aout−の電位が逆転している期間に応じて、コンパレータ12からはパルス状の比較出力信号Coutが出力される。

逆に、差動出力信号Aoutの振幅がオフセット電圧と比較して十分な大きさを有しない場合は、差動出力信号Aoutの正相信号Aout+と逆相信号Aout−が交差しないので、コンパレータ12からパルス状の比較出力信号Coutは出力されない。

すなわち、調整電圧源Vadjの調整電圧値を調整することによって、光信号Pinの検出感度を調整することができる。したがって、電気信号Toutがある一定の値以上の振幅を持つ有意パルスを含むときには、コンパレータ21がパルス状の比較出力信号Coutを出力する一方、バースト信号のない区間においてこの値に満たない振幅をもつノイズが混入しても、これを有意パルスとして誤まって検出することを避けることができる。

ここでは、光信号検出回路10を含む光受信器100が適用されるシステムとして、10G−EPONを想定しており、バースト信号として入力される電気信号Toutは、ビットレートが10Gbpsで、PN7段の信号から構成されている。このバースト信号は、約10mVの振幅(差動で約20mVの振幅)を持っている。この10mVという振幅は、一般的なトランスインピーダンスアンプTIAにおける最小受信感度(−30dBm程度)のときの出力振幅に相当する。ここでは、信号断区間において、バースト信号へのノイズ混入を想定し、約2mVの振幅があるものとした。

次段増幅信号Noutの正相信号Nout+と逆相信号Nout−には、約0.2V程度の直流オフセットが加えられている。また、図3に示すように、出力バッファ14に代えてシュミットトリガインバータ14Aが用いられている。

この後、バーストOFF状態になると、アナログ保持回路13の保持出力信号Houtは低下を開始し、開始から約55ns後に光信号検出信号SDがHighレベルとなり、信号断が表示されている。

このように、光信号検出信号SDの判定論理に1Vものヒステリシスを付与することで、連続同符号やノイズ入力に対して誤動作を防止することができる。

この応答の俊敏さは、光信号検出回路10をアラームではなくセンサとして用いるために重要な特性となる。例えば10G−EPONの物理層におけるプリアンブル長の国際標準規格は1200nsである。これに比べて18nsの応答時間は充分短いため、スリープ状態から自律的に信号受信を検出し、回路を起動するトリガの発出などに用いることができる。

このように、本実施の形態は、光信号検出回路10において、結合コンデンサCを介して入力された電気信号Toutの正相信号Tout+と逆相信号Tout−とを差動増幅して差動出力信号Aoutを出力する増幅回路11に電流加算回路11Eを設けて、差動出力信号Aoutの正相信号Aout+および逆相信号Aout−をそれぞれ生成する第1および第2の負荷抵抗R9,R10を流れる直流負荷電流を、外部の調整電圧源Vadjからの調整電圧値に応じて調整することにより、これら正相信号Aout+の直流バイアスと逆相信号Aout−の直流バイアスとの差を調整するようにしたものである。

なお、本発明においては、初段増幅回路11Bの2つの負荷抵抗R5,R6を同じ抵抗値としてもよい。この場合であっても、電流加算回路11Eによる直流負荷電流の調整によって感度を調整することができる。

次に、図6を参照して、本発明の第2の実施の形態にかかる光信号検出回路10について説明する。図6は、第2の実施の形態にかかる光信号検出回路で用いられる増幅回路の構成例を示す回路図である。

本実施の形態では、増幅回路11に次段バイアス回路11Gを設け、初段エミッタフォロワ回路11Cと次段増幅回路11Dとを直流的に遮断する場合について説明する。

なお、増幅回路11以外の回路については、第1の実施の形態と同一なので、これらの回路については同一の符号を用いて、その詳細な説明は省略する。

このように、本実施の形態は、初段エミッタフォロワ回路11Cと次段増幅回路11Dとの間に次段バイアス回路11Gを設け、初段エミッタフォロワ回路11Cからの初段出力信号Foutの逆相信号Fout−および正相信号Fout+をそれぞれ結合コンデンサC11およびC12を介して次段増幅回路11Dへ入力するものである。

これにより、初段増幅回路11Bを構成する素子にバラツキがあっても、次段増幅回路11Dに入力される初段出力信号Foutの正相信号Fout+と逆相信号のDC成分が除去されるので、素子のバラツキにより生じた初段出力信号Foutの正相信号Fout+の直流バイアスと逆相信号Fout−の直流バイアスとのバランス崩れを抑制することができる。

さらに、初段バイアス回路11Aおよび次段バイアス回路11Gにおいて、それぞれ1つの抵抗分割回路(ブリーダ抵抗)を用い、この抵抗分割回路で分圧した電圧を高抵抗を介して入力信号の正相信号および逆相信号にそれぞれ与えている。

これにより、バイアス回路においてオフセットの発生を抑えることができるので、初段増幅回路11Aの利得を大きくしても、安定しかつ精度の高い感度調整が可能となる。

次に、図7を参照して、本発明の第3の実施の形態にかかる光信号検出回路10について説明する。

なお、ラッチ回路13Aによって保持回路を構成することを除き、光信号検出回路10Aおよび光受信器100Aを構成する他の回路は、第1の実施の形態と同一なので、これらの回路については同一の符号を用い、その詳細な説明は省略する。

コンパレータ12で得られたパルス状の比較出力信号Coutに含まれるパルス信号を保持したラッチ回路13Aは、リセット信号RESETが入力されるまで比較出力信号CoutとしてHighレベルが出力され続ける。したがって、ラッチ回路13Aは、例えば光信号Pinの受信開始直後から、比較出力信号CoutとしてHighレベルを出力し続ける。

したがって、第1の実施の形態と同様に、光信号検出回路10Aの増幅回路11に電流加算回路11Eが設けられて、差動出力信号Aoutの正相信号Aout+および逆相信号Aout−を差動増幅する際に用いるそれぞれの直流負荷電流が、外部の調整電圧源Vadjからの調整電圧値に応じて調整されて、これら正相信号Aout+の直流バイアスおよび逆相信号Aout−の直流バイアスが調整される。

次に、図8を参照して、本発明の第4の実施の形態にかかる光信号検出回路について説明する。

光信号検出回路は、第1の実施の形態と同様に、増幅回路11とコンパレータ12を含む。図8に示すように、増幅回路11は、初段バイアス回路11A、初段増幅回路11B、初段エミッタフォロワ回路11C、次段増幅回路11D、電流加算回路11H、次段エミッタフォロワ回路11Fを含む。

ここで、第1の実施の形態においては、光信号検出回路10Bの増幅回路11に設けられる電流加算回路11Eは、差動対をなす2つのトランジスタQ7,Q8を含み、これらのトランジスタQ7,Q8のコレクタ端子が次段増幅回路11Dの差動トランジスタQ5,Q6のコレクタ端子に接続されていた。これに対し、本実施の形態にかかる光信号検出回路で用いられる増幅回路11の電流加算回路11Hは、次段増幅回路11Dの差動トランジスタQ5,Q6のいずれか一方のコレクタ端子に接続され、外部の調整電圧源Vadjからの調整電圧値に応じて電流値が制御される電流源I9を含む。

なお、電流加算回路11H以外の回路は、第1の実施の形態と同一なので、同一の符号を用い、その詳細な説明は省略する。

負荷抵抗R10を流れる直流負荷電流に加算される電流の大きさは、外部の調整電圧源Vadjからの調整電圧値に応じて調整できるので、逆相信号Aout−の直流バイアスを調整して、正相信号Aout+と逆相信号Aout−との差、すなわちオフセット電圧を変化させることができる。

以上、実施形態を参照して本発明を説明したが、本発明は上記実施形態に限定されるものではない。本発明の構成や詳細には、本発明のスコープ内で当業者が理解しうる様々な変更をすることができる。また、これら実施の形態は、任意に組み合わせて実施してもよい。

Claims (7)

- 光信号のパルス列に対応するパルスを含む電気信号の正相信号と逆相信号とを差動増幅して差動出力信号を出力する増幅回路と、

前記差動出力信号の正相信号の電圧値と逆相信号の電圧値とを比較して、その比較結果に応じたパルス状の比較出力信号を出力するコンパレータと、

前記パルス状の比較出力信号に基づいて前記光信号の入力有無を示す光信号検出信号を出力する保持回路と

を備え、

前記増幅回路は、

一端がそれぞれ電源電位に接続されて、前記差動出力信号の前記正相信号および前記逆相信号をそれぞれ生成する第1および第2の負荷抵抗と、

前記第1および第2の負荷抵抗の少なくとも一方を流れる直流負荷電流を、外部の調整電圧源からの調整電圧値に応じて調整して、前記差動出力信号の前記正相信号の直流バイアスと前記逆相信号の直流バイアスとの差を調整する電流加算回路とを含み、

前記保持回路は、

前記パルス状の比較出力信号によって充電される保持コンデンサと、前記保持コンデンサと並列に接続された放電抵抗とを含み、前記保持コンデンサに保持された電荷を前記放電抵抗で放電することにより、前記光信号の入力有無に応じて変化する保持出力信号を出力するアナログ保持回路と、

前記保持出力信号をデジタル論理信号へ整形して前記光信号検出信号を出力する出力バッファとを含む

ことを特徴とする光信号検出回路。 - 請求項1に記載の光信号検出回路において、

前記電流加算回路は、

前記第1および第2の負荷抵抗のいずれか一方の他端に接続され、前記調整電圧値に応じて電流値が制御される電流源を含む

ことを特徴とする光信号検出回路。 - 請求項1に記載の光信号検出回路において、

前記電流加算回路は、

前記第1および第2の負荷抵抗のいずれか一方の他端に接続された第1の入出力端子と、前記調整電圧値が入力される制御端子とを有する第1のトランジスタと、

前記第1および第2の負荷抵抗のいずれか他方の他端に接続された第1の入出力端子と、所定の電圧値が入力される制御端子と、前記第1のトランジスタの第2の入出力端子と接続された第2の入出力端子とを備え、前記第1のトランジスタと差動対をなす第2のトランジスタと、

前記第1のトランジスタの第2の入出力端子と前記第2のトランジスタの第2の入出力端子との接続点に接続された定電流源とを含む

ことを特徴とする光信号検出回路。 - 請求項1に記載の光信号検出回路において、

前記出力バッファは、

前記アナログ保持回路で得られた前記保持出力信号を、ヒステリシス特性に基づいて整形出力するシュミットトリガインバータである

ことを特徴とする光信号検出回路。 - 請求項1に記載の光信号検出回路において、

前記保持回路は、前記パルス状の比較出力信号をラッチして前記光信号検出信号を出力するラッチ回路である

ことを特徴とする光信号検出回路。 - 請求項1に記載の光信号検出回路において、

前記増幅回路は、

前記電気信号の正相信号と逆相信号とを差動増幅して初段出力信号を出力する初段増幅回路と、

前記初段増幅回路の出力インピーダンスよりも低い出力インピーダンスを有するとともに、前記初段増幅回路からの前記初段出力信号を出力するインピーダンス調整回路と、

前記インピーダンス調整回路と結合コンデンサによってAC結合され、前記結合コンデンサを介して入力される前記初段出力信号の正相信号および逆相信号のそれぞれに直流バイアスを与えて出力する次段バイアス回路と、

前記次段バイアス回路によって直流バイアスされた前記初段出力信号の正相信号と逆相信号とを差動増幅して前記差動出力信号を出力する次段増幅回路と

をさらに含み、

前記次段増幅回路は、

前記差動出力信号の前記正相信号および前記逆相信号をそれぞれ生成する前記第1および第2の負荷抵抗を含む

ことを特徴とする光信号検出回路。 - パルス列からなる光信号を光電変換して光電流信号を出力する光電変換素子と、

前記光電流信号を増幅して、前記パルス列に対応するパルスを含む電気信号を出力するトランスインピーダンスアンプと、

前記電気信号を増幅して、一定振幅のパルスを含む受信出力を出力するリミッティングアンプと、

前記電気信号に基づいて前記光信号の入力有無を検出する光信号検出回路と

を備え、

前記光信号検出回路は、

前記電気信号の正相信号と逆相信号とを差動増幅して差動出力信号を出力する増幅回路と、

前記差動出力信号の正相信号の電圧値と逆相信号の電圧値とを比較して、その比較結果に応じたパルス状の比較出力信号を出力するコンパレータと、

前記パルス状の比較出力信号に基づいて前記光信号の入力有無を示す光信号検出信号を出力する保持回路と

を備え、

前記増幅回路は、

一端がそれぞれ電源電位に接続されて、前記差動出力信号の前記正相信号および前記逆相信号をそれぞれ生成する第1および第2の負荷抵抗と、

前記第1および第2の負荷抵抗の少なくとも一方を流れる直流負荷電流を、外部の調整電圧源からの調整電圧値に応じて調整して、前記差動出力信号の前記正相信号の直流バイアスと前記逆相信号の直流バイアスとの差を調整する電流加算回路と

を含み、

前記保持回路は、

前記パルス状の比較出力信号によって充電される保持コンデンサと、前記保持コンデンサと並列に接続された放電抵抗とを含み、前記保持コンデンサに保持された電荷を前記放電抵抗で放電することにより、前記光信号の入力有無に応じて変化する保持出力信号を出力するアナログ保持回路と、

前記保持出力信号をデジタル論理信号へ整形して前記光信号検出信号を出力する出力バッファとを含む

ことを特徴とする光受信器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012554815A JP5658287B2 (ja) | 2011-01-25 | 2012-01-25 | 光信号検出回路および光受信器 |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011012736 | 2011-01-25 | ||

| JP2011012736 | 2011-01-25 | ||

| PCT/JP2012/051526 WO2012102300A1 (ja) | 2011-01-25 | 2012-01-25 | 光信号検出回路および光受信器 |

| JP2012554815A JP5658287B2 (ja) | 2011-01-25 | 2012-01-25 | 光信号検出回路および光受信器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2012102300A1 JPWO2012102300A1 (ja) | 2014-06-30 |

| JP5658287B2 true JP5658287B2 (ja) | 2015-01-21 |

Family

ID=46580865

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012554815A Active JP5658287B2 (ja) | 2011-01-25 | 2012-01-25 | 光信号検出回路および光受信器 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9160458B2 (ja) |

| JP (1) | JP5658287B2 (ja) |

| CN (1) | CN103460624B (ja) |

| WO (1) | WO2012102300A1 (ja) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6576291B2 (en) | 2000-12-08 | 2003-06-10 | Massachusetts Institute Of Technology | Preparation of nanocrystallites |

| JP4856771B2 (ja) * | 2010-02-15 | 2012-01-18 | 日本電信電話株式会社 | 光信号断検出回路および光受信器 |

| US9160458B2 (en) * | 2011-01-25 | 2015-10-13 | Nippon Telephone And Telegraph Corporation | Optical signal detection circuit and optical receiver |

| WO2015062015A1 (zh) * | 2013-10-31 | 2015-05-07 | 华为技术有限公司 | 一种光接收机的信号检测方法、装置及系统 |

| JP2015089047A (ja) * | 2013-10-31 | 2015-05-07 | 富士通オプティカルコンポーネンツ株式会社 | 光受信装置及び伝送装置 |

| JP2016058806A (ja) * | 2014-09-08 | 2016-04-21 | Necプラットフォームズ株式会社 | Onu、ponシステム、onu制御方法、およびonu制御プログラム |

| CN105223390B (zh) * | 2015-10-20 | 2019-01-18 | 天水七四九电子有限公司 | 一种电容耦合式隔离放大器 |

| US10397190B2 (en) * | 2016-02-05 | 2019-08-27 | Huawei Technologies Co., Ltd. | System and method for generating an obfuscated optical signal |

| CN106019201B (zh) * | 2016-05-05 | 2019-02-19 | 广东省计量科学研究院 | 一种具有高效滤波功能的光电耦合装置 |

| US20180062762A1 (en) * | 2016-08-29 | 2018-03-01 | Electronics And Telecommunications Research Institute | Optical signal receiving apparatus for receiving optical signal in burst mode |

| TWI630801B (zh) * | 2017-01-11 | 2018-07-21 | 義守大學 | 晶片間訊號傳輸系統與訊號接收電路 |

| CN107356937A (zh) * | 2017-08-25 | 2017-11-17 | 长春德信光电技术有限公司 | 一种基于激光探测技术的行走机器人碰撞预警装置 |

| CN109995436B (zh) * | 2017-12-29 | 2021-08-31 | 北京华为数字技术有限公司 | 光线路终端的单板及光线路终端 |

| JP6830079B2 (ja) * | 2018-03-30 | 2021-02-17 | 日本電信電話株式会社 | トラック・アンド・ホールド回路 |

| CN109143251B (zh) * | 2018-07-30 | 2023-04-25 | 南京理工大学 | 基于差分信号的脉冲激光测距时刻鉴别器 |

| CN108847897B (zh) * | 2018-08-03 | 2021-05-28 | 青岛海信宽带多媒体技术有限公司 | 一种光模块 |

| KR102472760B1 (ko) * | 2018-08-09 | 2022-11-30 | 에스케이하이닉스 주식회사 | 광 수신기 |

| JP2020077956A (ja) * | 2018-11-07 | 2020-05-21 | 住友電気工業株式会社 | 光受信回路 |

| KR102135332B1 (ko) * | 2019-05-23 | 2020-07-17 | 주식회사 알파홀딩스 | 적외선 수신 장치와 이를 포함하는 반도체 회로 및 전자기기 |

| CN114175531B (zh) * | 2019-08-09 | 2024-03-22 | 三菱电机株式会社 | 光接收器和站侧装置 |

| CN114975677B (zh) * | 2021-02-27 | 2024-03-01 | 华为技术有限公司 | 光接收装置、光接收封装装置、相关设备和方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0870223A (ja) * | 1994-08-30 | 1996-03-12 | Oki Electric Ind Co Ltd | オフセットキャンセル回路 |

| JP2009044228A (ja) * | 2007-08-06 | 2009-02-26 | Ntt Electornics Corp | 光受信回路 |

| JP2011166659A (ja) * | 2010-02-15 | 2011-08-25 | Nippon Telegr & Teleph Corp <Ntt> | 光信号断検出回路および光受信器 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4688260A (en) * | 1985-10-09 | 1987-08-18 | Westinghouse Electric Corp. | High-reliability fiber optic repeater |

| DE69721610T2 (de) * | 1996-02-23 | 2004-03-25 | Matsushita Electric Industrial Co., Ltd., Kadoma | Burstsignal-Verstärker und optische Empfangsschaltungsanordnung |

| JPH1084231A (ja) * | 1996-05-24 | 1998-03-31 | Toshiba Corp | デジタル信号受信回路 |

| JP2000241778A (ja) * | 1999-02-19 | 2000-09-08 | Fujitsu Ltd | 光通信装置および光分岐・挿入装置 |

| US7173551B2 (en) * | 2000-12-21 | 2007-02-06 | Quellan, Inc. | Increasing data throughput in optical fiber transmission systems |

| US7307569B2 (en) * | 2001-03-29 | 2007-12-11 | Quellan, Inc. | Increasing data throughput in optical fiber transmission systems |

| JP2003158493A (ja) * | 2001-11-21 | 2003-05-30 | Mitsubishi Electric Corp | 光遮断検出装置、光受信器、光送信器及び光遮断検出方法 |

| JP4569195B2 (ja) * | 2003-11-14 | 2010-10-27 | 富士ゼロックス株式会社 | 信号伝送装置 |

| WO2006013893A1 (ja) * | 2004-08-03 | 2006-02-09 | Nippon Telegraph And Telephone Corporation | トランスインピーダンスアンプ |

| US20060216042A1 (en) * | 2005-03-24 | 2006-09-28 | Yeo Kok S | Automatic gain control circuit for infrared receiver |

| JP4261514B2 (ja) * | 2005-06-22 | 2009-04-30 | 日本電信電話株式会社 | バースト先頭検出回路 |

| JP4588592B2 (ja) * | 2005-09-13 | 2010-12-01 | 株式会社フジクラ | バースト信号受信装置及びバースト信号検出方法 |

| CN101877572A (zh) * | 2009-04-30 | 2010-11-03 | 昂纳信息技术(深圳)有限公司 | 一种高速自动增益控制的装置和方法 |

| US9160458B2 (en) * | 2011-01-25 | 2015-10-13 | Nippon Telephone And Telegraph Corporation | Optical signal detection circuit and optical receiver |

| JP5724546B2 (ja) * | 2011-03-31 | 2015-05-27 | 富士通オプティカルコンポーネンツ株式会社 | 光送信機および光波形補償方法 |

-

2012

- 2012-01-25 US US13/981,313 patent/US9160458B2/en active Active

- 2012-01-25 WO PCT/JP2012/051526 patent/WO2012102300A1/ja not_active Ceased

- 2012-01-25 CN CN201280006341.9A patent/CN103460624B/zh active Active

- 2012-01-25 JP JP2012554815A patent/JP5658287B2/ja active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0870223A (ja) * | 1994-08-30 | 1996-03-12 | Oki Electric Ind Co Ltd | オフセットキャンセル回路 |

| JP2009044228A (ja) * | 2007-08-06 | 2009-02-26 | Ntt Electornics Corp | 光受信回路 |

| JP2011166659A (ja) * | 2010-02-15 | 2011-08-25 | Nippon Telegr & Teleph Corp <Ntt> | 光信号断検出回路および光受信器 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN103460624A (zh) | 2013-12-18 |

| WO2012102300A1 (ja) | 2012-08-02 |

| US9160458B2 (en) | 2015-10-13 |

| CN103460624B (zh) | 2016-05-04 |

| JPWO2012102300A1 (ja) | 2014-06-30 |

| US20140016949A1 (en) | 2014-01-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5658287B2 (ja) | 光信号検出回路および光受信器 | |

| JP4856771B2 (ja) | 光信号断検出回路および光受信器 | |

| US9853618B2 (en) | Transimpedance amplifier circuit | |

| US4724315A (en) | Optical receiver | |

| JP4927664B2 (ja) | 前置増幅回路 | |

| US9882539B1 (en) | Multi-data rate, burst-mode transimpedance amplifier (TIA) circuit | |

| JPH06177664A (ja) | ディジタル光受信回路とトランスインピーダンスアンプ回路とプリアンプ回路 | |

| JP3098461B2 (ja) | ディジタル受信回路 | |

| JP2003318681A (ja) | 増幅回路及び光通信装置 | |

| CN102067445B (zh) | 执行增益控制的放大器和光学模块 | |

| KR20160049922A (ko) | 차지 펌핑을 이용한 피크 검출 장치 및 버스트모드 트랜스 임피던스 증폭 장치 | |

| JP2010093353A (ja) | 光受信器 | |

| JP5944750B2 (ja) | 光信号検出回路 | |

| JP4248773B2 (ja) | 電流電圧変換装置 | |

| US20140333285A1 (en) | Optical receiver and light reception current monitoring method | |

| KR20040084620A (ko) | 수신된 광신호의 소광비 특성을 고려한 버스트 모드 광수신장치 | |

| KR100703428B1 (ko) | 버스트모드 광 수신기 및 그의 신호 크기 검출 장치 | |

| TWI279096B (en) | Optical receiver | |

| JPH08288757A (ja) | ディジタル受信回路 | |

| US8369714B2 (en) | Burst optical signal receiving device | |

| CN112304429B (zh) | 光电检测电路 | |

| CN115118255A (zh) | 一种峰值检波器和峰值检波方法 | |

| CN117595936A (zh) | 光接收器 | |

| JP2003152460A (ja) | 光受信器 | |

| CN218570208U (zh) | 一种峰值检波器、差分峰值检波器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140610 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140801 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141125 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141127 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5658287 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |