JP5638760B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP5638760B2 JP5638760B2 JP2009026135A JP2009026135A JP5638760B2 JP 5638760 B2 JP5638760 B2 JP 5638760B2 JP 2009026135 A JP2009026135 A JP 2009026135A JP 2009026135 A JP2009026135 A JP 2009026135A JP 5638760 B2 JP5638760 B2 JP 5638760B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- outer edge

- semiconductor device

- nmis

- pmis

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 125

- 238000009792 diffusion process Methods 0.000 claims description 131

- 239000000758 substrate Substances 0.000 claims description 25

- 239000010410 layer Substances 0.000 description 54

- 238000012546 transfer Methods 0.000 description 32

- 230000006870 function Effects 0.000 description 31

- 238000013461 design Methods 0.000 description 26

- 239000002184 metal Substances 0.000 description 23

- 229910052751 metal Inorganic materials 0.000 description 23

- 230000000052 comparative effect Effects 0.000 description 21

- 238000001459 lithography Methods 0.000 description 20

- 230000015654 memory Effects 0.000 description 20

- 238000012986 modification Methods 0.000 description 12

- 230000004048 modification Effects 0.000 description 12

- MHABMANUFPZXEB-UHFFFAOYSA-N O-demethyl-aloesaponarin I Natural products O=C1C2=CC=CC(O)=C2C(=O)C2=C1C=C(O)C(C(O)=O)=C2C MHABMANUFPZXEB-UHFFFAOYSA-N 0.000 description 10

- 238000010586 diagram Methods 0.000 description 10

- 238000004891 communication Methods 0.000 description 9

- 230000000694 effects Effects 0.000 description 9

- 238000000034 method Methods 0.000 description 8

- 229910021332 silicide Inorganic materials 0.000 description 8

- 238000012937 correction Methods 0.000 description 7

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 6

- 238000000059 patterning Methods 0.000 description 5

- 230000002093 peripheral effect Effects 0.000 description 5

- 238000012545 processing Methods 0.000 description 5

- 230000010354 integration Effects 0.000 description 4

- 230000001360 synchronised effect Effects 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 3

- 239000000945 filler Substances 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- 238000005452 bending Methods 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 2

- 238000002513 implantation Methods 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 229930091051 Arenine Natural products 0.000 description 1

- 101100490184 Drosophila melanogaster Ack gene Proteins 0.000 description 1

- 241001522296 Erithacus rubecula Species 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 230000006386 memory function Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 238000012795 verification Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

- H01L27/092—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate complementary MIS field-effect transistors

- H01L27/0928—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate complementary MIS field-effect transistors comprising both N- and P- wells in the substrate, e.g. twin-tub

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0207—Geometrical layout of the components, e.g. computer aided design; custom LSI, semi-custom LSI, standard cell technique

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

- H01L27/092—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate complementary MIS field-effect transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/118—Masterslice integrated circuits

- H01L27/11803—Masterslice integrated circuits using field effect technology

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/118—Masterslice integrated circuits

- H01L27/11898—Input and output buffer/driver structures

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Engineering & Computer Science (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

(実施の形態1)

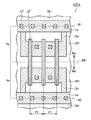

図1を参照して、半導体装置(たとえば半導体チップ)50は、その表面に、スタンダードセル領域51と、そのスタンダードセル領域51の周囲に配置されたI/O(Input/Output)セル領域52と、外部との入出力に用いられるパッド(図示せず)とを主に有する。

図9を参照して、本実施の形態においては、実施の形態1における電源配線VDおよび接地配線VSのそれぞれ代わりに、電源配線VDwおよび接地配線VSwを有する。電源配線VDwおよび接地配線VSの各々は、幅Wwを有する。幅Wwは、pMIS配線M1pおよびnMIS配線M1nの各々の幅Wsよりも大きい。

図10を参照して、本実施の形態の半導体装置は、スタンダードセルCiv、Cnd、Cnr、Cflを有する。スタンダードセルCiv、Cnd、Cnr、Cflは、複数の段に分かれて配列されており、各段において図中の方向Xに沿って配列されている。

図16を参照して、本実施の形態の半導体装置SDは半導体基板SBを有し、半導体基板SB上に、I/O領域101と、CPU・ロジック領域102と、メモリ領域103と、PLL(Phase-Locked Loop)領域104と、アナログ領域105とを有する。

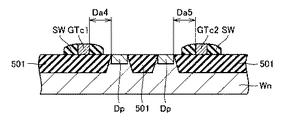

図23および図24を参照して、本比較例においては、Butting Diffusion構造が設けられていない。このため、n型導電領域Lnおよびp型拡散領域Dpの間の電気的接続と、p型導電領域Lpおよびn型拡散領域Dnとの間の電気的接続とは、メタル配線MTおよびコンタクトCTにより行なわれている。すなわち本実施の形態に比してコンタクトCTがより多く設けられている。この結果ゲート電極GTzの配置に制約が生じるので、複数のゲート電極GTzの配置を第1ピッチP1に統一することができない。すなわち第1ピッチP1よりも大きい第2ピッチP2や、第2ピッチP2よりも大きい第3ピッチP3が第1ピッチP1と混在している。このため本比較例においては高集積化が困難となっている。

図30および図31を参照して、本実施の形態の半導体装置は、ゲート電極GTが形成された層LD2(図30)を有する。この層LD2の部分Xa〜Xfの各々におけるゲート電極GTの配置について、比較例と対比しつつ、以下に詳しく説明する。

図44および図45を参照して、本実施の形態の半導体装置は、ゲート電極GTが形成された層LD3を有する。この層LD3は、セルYa〜Yeの各々に対応する部分を有する。セルYa〜Yeのそれぞれは、半導体装置のうち、インバータ、NAND、NOR、トライステートバッファ、およびフリップフロップとして機能する部分を区画している。セルYa〜Yeの各々は、第1の方向(図44および図45における横方向)に沿って第1ピッチP1の整数倍の幅を有する。たとえばセルYaおよびYbのそれぞれは、第1ピッチP1の2倍および3倍の幅UaおよびUbを有する。

図47〜図49を参照して、本実施の形態の半導体装置は、論理回路として使用されるセルと、論理回路として使用されないダミーセル(フィラーセル)FGとを有する。論理回路として使用されるセルと、論理回路として使用されないダミーセルFGとの各々のゲート電極GTは、第1の方向(図47〜図49における横方向)に第1ピッチで配置されている。

図51および図52を参照して、本実施の形態の半導体装置は、論理回路として使用されるセルと、論理回路として使用されないダミーセル(フィラーセル)FMとを有する。論理回路として使用されるセルと、論理回路として使用されないダミーセルFGとのそれぞれは、メタル配線MTとして、メタル配線MTdと、メタル配線MTfとを有する。メタル配線MTは、第1の方向(図51の横方向)に延び、かつ第2の方向(図51の縦方向)に第2ピッチで配置されている。よってメタル配線MTfの各々は、第1の方向(図51の横方向)に延び、かつダミーセルFMにおいて第2の方向に第2ピッチで配置されている。

図54を参照して、本実施の形態の半導体装置は、容量セルFCaを有する。容量セルFCaは、半導体装置において、電源電位Vccおよび接地電位Vss間に配置されたデカップリング・コンデンサとして機能する部分を区画している。ゲート電極GTは、p型拡散領域Dpおよびn型拡散領域Dnと対向することにより静電容量をなしている。すなわちゲート電極GTは、デカップリング・コンデンサの電極の一部をなしている。

Claims (1)

- 第1の方向に沿って配列された複数のスタンダードセルを有する半導体装置であって、

前記複数のスタンダードセルの各々は、第1の方向に沿って延びかつ互いに正対する第1および第2の外縁を有し、

前記第1の方向に沿って前記複数のスタンダードセルの各々を通りn型ウエルおよびp型ウエルの境となる境界と前記第1の外縁との間に形成されたpMIS領域と、前記境界と前記第2の外縁との間に形成されたnMIS領域とを有する半導体基板と、

前記第1の方向に直交する第2の方向に沿って延びる複数のゲート配線を有し、かつ前記半導体基板上に設けられた第1の層と、

前記第1の層上に設けられた第2の層とを備え、

前記pMIS領域は、n型ウエルと、前記n型ウエル上に形成されたp型拡散領域とを含み、

前記p型拡散領域は、前記pMIS領域におけるソース/ドレイン領域と、前記pMIS領域におけるソース/ドレイン領域の一方の領域に連なり前記第1の外縁と重なって延びる第1接続領域とを有し、

前記nMIS領域は、p型ウエルと、前記p型ウエル上に形成されたn型拡散領域とを含み、

前記n型拡散領域は、前記nMIS領域におけるソース/ドレイン領域と、前記nMIS領域におけるソース/ドレイン領域の一方の領域に連なり前記第2の外縁と重なって延びる第2接続領域とを有し、

前記第2の層は、

前記第1の外縁上に重なるように配置されるとともに前記第1の外縁に沿って延び、かつ前記pMIS領域に電気的に接続された第1の電源配線と、

前記第2の外縁上に重なるように配置されるととに前記第2の外縁に沿って延び、かつ前記nMIS領域に電気的に接続された第2の電源配線と、

前記第1および第2の電源配線の間の前記pMIS領域上において、前記第1の方向に沿って延びかつ前記第2の方向に沿って一のピッチで配置された複数の第1の仮想ラインのそれぞれの上に配置された複数のpMIS配線と、

前記第1および第2の電源配線の間の前記nMIS領域上において、前記第1の方向に沿って延びかつ前記第2の方向に沿って前記一のピッチで配置された複数の第2の仮想ラインのそれぞれの上に配置された複数のnMIS配線とを含み、

前記複数の第1の仮想ラインのうち前記境界に最も近いものと、前記複数の第2の仮想ラインのうち前記境界に最も近いものとの間隔は、前記一のピッチよりも大きく、

前記複数の第1の仮想ラインのうち前記第1の外縁に最も近いものと、前記第1の外縁との間隔は、前記一のピッチより大きく、

前記複数の第1の仮想ラインのうち前記第2の外縁に最も近いものと、前記第2の外縁との間隔は、前記一のピッチより大きく、

前記第1の電源配線は、コンタクトを介して前記第1接続領域と接続され、

前記第2の電源配線は、コンタクトを介して前記第2接続領域と接続されている、半導体装置。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009026135A JP5638760B2 (ja) | 2008-08-19 | 2009-02-06 | 半導体装置 |

| TW098126391A TWI446198B (zh) | 2008-08-19 | 2009-08-05 | 半導體裝置 |

| US12/536,319 US8237203B2 (en) | 2008-08-19 | 2009-08-05 | Semiconductor device |

| CN2009101654632A CN101656253B (zh) | 2008-08-19 | 2009-08-18 | 半导体器件 |

| US13/538,602 US8710552B2 (en) | 2008-08-19 | 2012-06-29 | Semiconductor device |

| US14/185,801 US9035392B2 (en) | 2008-08-19 | 2014-02-20 | Semiconductor device |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008210332 | 2008-08-19 | ||

| JP2008210332 | 2008-08-19 | ||

| JP2009026135A JP5638760B2 (ja) | 2008-08-19 | 2009-02-06 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014215529A Division JP5944464B2 (ja) | 2008-08-19 | 2014-10-22 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010074125A JP2010074125A (ja) | 2010-04-02 |

| JP2010074125A5 JP2010074125A5 (ja) | 2012-03-08 |

| JP5638760B2 true JP5638760B2 (ja) | 2014-12-10 |

Family

ID=41695538

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009026135A Expired - Fee Related JP5638760B2 (ja) | 2008-08-19 | 2009-02-06 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US8237203B2 (ja) |

| JP (1) | JP5638760B2 (ja) |

| CN (1) | CN101656253B (ja) |

| TW (1) | TWI446198B (ja) |

Families Citing this family (43)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5292005B2 (ja) * | 2008-07-14 | 2013-09-18 | ルネサスエレクトロニクス株式会社 | 半導体集積回路 |

| JP5944464B2 (ja) * | 2008-08-19 | 2016-07-05 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP5537078B2 (ja) * | 2009-07-23 | 2014-07-02 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP5331195B2 (ja) * | 2009-10-19 | 2013-10-30 | パナソニック株式会社 | 半導体装置 |

| JP5364015B2 (ja) | 2010-03-05 | 2013-12-11 | パナソニック株式会社 | 半導体装置 |

| JP5581795B2 (ja) * | 2010-05-07 | 2014-09-03 | ルネサスエレクトロニクス株式会社 | スタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法 |

| JP2011242541A (ja) * | 2010-05-17 | 2011-12-01 | Panasonic Corp | 半導体集積回路装置、および標準セルの端子構造 |

| JP2012255704A (ja) * | 2011-06-08 | 2012-12-27 | Elpida Memory Inc | 半導体装置 |

| US8533641B2 (en) * | 2011-10-07 | 2013-09-10 | Baysand Inc. | Gate array architecture with multiple programmable regions |

| CN104303263B (zh) * | 2012-01-13 | 2016-12-14 | 特拉创新公司 | 具有线形翅片场效应结构的电路 |

| JP6010308B2 (ja) * | 2012-02-27 | 2016-10-19 | ローム株式会社 | 半導体集積回路および電子機器 |

| KR101913316B1 (ko) * | 2012-06-04 | 2018-10-31 | 삼성전자주식회사 | 디커플링 커패시터 및 더미 트랜지스터를 갖는 반도체 소자 |

| CN104517963B (zh) * | 2013-09-27 | 2018-09-18 | 恩智浦美国有限公司 | 状态保持电源选通单元 |

| KR102122458B1 (ko) | 2013-11-19 | 2020-06-12 | 삼성전자주식회사 | 반도체 소자의 패턴을 디자인하는 방법 |

| JP6449082B2 (ja) | 2014-08-18 | 2019-01-09 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| CN107112280B (zh) * | 2014-10-24 | 2020-08-04 | 株式会社索思未来 | 半导体集成电路装置 |

| US9646960B2 (en) | 2015-02-26 | 2017-05-09 | Samsung Electronics Co., Ltd. | System-on-chip devices and methods of designing a layout therefor |

| US9710404B2 (en) | 2015-03-23 | 2017-07-18 | Intel Corporation | Dynamic configuration and peripheral access in a processor |

| US9825024B2 (en) | 2015-09-30 | 2017-11-21 | Samsung Electronics Co., Ltd. | Semiconductor device |

| US9935100B2 (en) * | 2015-11-09 | 2018-04-03 | Qualcomm Incorporated | Power rail inbound middle of line (MOL) routing |

| US9871046B2 (en) | 2016-02-24 | 2018-01-16 | Taiwan Semiconductor Manufacturing Company, Ltd. | SRAM circuits with aligned gate electrodes |

| CN107578986B (zh) * | 2016-07-04 | 2019-11-01 | 中芯国际集成电路制造(上海)有限公司 | 半导体结构及其形成方法和光刻偏移的测量方法 |

| JP6974743B2 (ja) | 2016-08-01 | 2021-12-01 | 株式会社ソシオネクスト | 半導体集積回路装置 |

| US11251124B2 (en) | 2016-11-29 | 2022-02-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Power grid structures and method of forming the same |

| US10740531B2 (en) | 2016-11-29 | 2020-08-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integrated circuit, system for and method of forming an integrated circuit |

| US10671547B2 (en) | 2016-12-19 | 2020-06-02 | Intel Corporation | Lightweight trusted tasks |

| JP6776192B2 (ja) * | 2017-06-28 | 2020-10-28 | ルネサスエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| US10692808B2 (en) | 2017-09-18 | 2020-06-23 | Qualcomm Incorporated | High performance cell design in a technology with high density metal routing |

| KR102362016B1 (ko) | 2017-09-19 | 2022-02-10 | 삼성전자주식회사 | 마스터 슬레이브 플립 플롭 |

| US10559558B2 (en) * | 2017-09-29 | 2020-02-11 | Taiwan Semiconductor Manufacturing Co., Ltd. | Pin modification for standard cells |

| DE102018122541A1 (de) | 2017-09-29 | 2019-04-04 | Taiwan Semiconductor Manufacturing Co., Ltd. | Stiftmodifizierung für standardzellen |

| JP6965721B2 (ja) * | 2017-12-18 | 2021-11-10 | 富士通株式会社 | 回路素子及び回路素子の使用方法 |

| WO2019138546A1 (ja) * | 2018-01-12 | 2019-07-18 | 株式会社ソシオネクスト | 半導体集積回路装置 |

| CN110349947A (zh) | 2018-04-02 | 2019-10-18 | 台湾积体电路制造股份有限公司 | 半导体装置、其设计方法及包括其的系统 |

| JP7365159B2 (ja) * | 2019-08-06 | 2023-10-19 | ローム株式会社 | 半導体集積回路 |

| US10796061B1 (en) | 2019-08-29 | 2020-10-06 | Advanced Micro Devices, Inc. | Standard cell and power grid architectures with EUV lithography |

| KR20210029966A (ko) | 2019-09-09 | 2021-03-17 | 삼성전자주식회사 | 집적된 표준 셀 구조를 포함하는 집적 회로 |

| CN111244064A (zh) * | 2020-01-19 | 2020-06-05 | 比特大陆科技有限公司 | 半导体芯片、半导体装置和数据处理设备 |

| US11342326B2 (en) * | 2020-04-28 | 2022-05-24 | Taiwan Semiconductor Manufacturing Co., Ltd. | Self-aligned etch in semiconductor devices |

| US11606084B2 (en) * | 2020-05-26 | 2023-03-14 | Taiwan Semiconductor Manufacturing Company Ltd. | Oscillation circuit, semiconductor device for oscillation circuit and method for manufacturing the same |

| KR20220124767A (ko) | 2021-02-05 | 2022-09-14 | 창신 메모리 테크놀로지즈 아이엔씨 | 표준 셀 레이아웃 템플릿 및 반도체 구조물 |

| US11798809B2 (en) * | 2021-06-17 | 2023-10-24 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor device and method of manufacturing |

| KR20230037103A (ko) * | 2021-09-08 | 2023-03-16 | 삼성전자주식회사 | 반도체 소자 및 그의 제조 방법 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02280353A (ja) * | 1989-04-20 | 1990-11-16 | Nec Corp | 半導体集積回路 |

| JPH0685062A (ja) * | 1992-09-04 | 1994-03-25 | Fujitsu Ltd | セルベースレイアウト設計方法 |

| JP3281234B2 (ja) * | 1995-11-08 | 2002-05-13 | 富士通株式会社 | 半導体集積回路装置及びその製造方法 |

| JP2991147B2 (ja) * | 1997-01-30 | 1999-12-20 | 日本電気株式会社 | スタンダードセルのレイアウト方式 |

| JP3758876B2 (ja) | 1999-02-02 | 2006-03-22 | Necマイクロシステム株式会社 | 半導体装置のレイアウト方法 |

| JP2000277620A (ja) | 1999-03-29 | 2000-10-06 | Nec Ic Microcomput Syst Ltd | 標準セル及びそれを用いた電源配線レイアウト方法 |

| JP2003203993A (ja) * | 2002-01-10 | 2003-07-18 | Mitsubishi Electric Corp | 半導体記憶装置及びその製造方法 |

| US7053424B2 (en) * | 2002-10-31 | 2006-05-30 | Yamaha Corporation | Semiconductor integrated circuit device and its manufacture using automatic layout |

| KR100532464B1 (ko) | 2003-08-28 | 2005-12-01 | 삼성전자주식회사 | 액티브를 이용한 반도체 셀의 전원선 레이아웃 |

| JP2005236107A (ja) * | 2004-02-20 | 2005-09-02 | Toshiba Corp | 上層メタル電源スタンダードセル、面積圧縮装置および回路最適化装置 |

| JP4827422B2 (ja) * | 2005-03-10 | 2011-11-30 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置の設計方法と装置並びにプログラム |

-

2009

- 2009-02-06 JP JP2009026135A patent/JP5638760B2/ja not_active Expired - Fee Related

- 2009-08-05 US US12/536,319 patent/US8237203B2/en not_active Expired - Fee Related

- 2009-08-05 TW TW098126391A patent/TWI446198B/zh not_active IP Right Cessation

- 2009-08-18 CN CN2009101654632A patent/CN101656253B/zh not_active Expired - Fee Related

-

2012

- 2012-06-29 US US13/538,602 patent/US8710552B2/en active Active

-

2014

- 2014-02-20 US US14/185,801 patent/US9035392B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN101656253B (zh) | 2013-12-11 |

| TW201017453A (en) | 2010-05-01 |

| US20140239406A1 (en) | 2014-08-28 |

| US20120261723A1 (en) | 2012-10-18 |

| US9035392B2 (en) | 2015-05-19 |

| CN101656253A (zh) | 2010-02-24 |

| US20100044755A1 (en) | 2010-02-25 |

| US8710552B2 (en) | 2014-04-29 |

| TWI446198B (zh) | 2014-07-21 |

| JP2010074125A (ja) | 2010-04-02 |

| US8237203B2 (en) | 2012-08-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5638760B2 (ja) | 半導体装置 | |

| JP5944464B2 (ja) | 半導体装置 | |

| US7492013B2 (en) | Systems and arrangements to interconnect components of a semiconductor device | |

| US9934347B2 (en) | Integrated circuit and method of designing layout of integrated circuit | |

| JP6066542B2 (ja) | 半導体装置 | |

| JP2006173478A (ja) | 半導体集積回路装置及びその設計方法 | |

| US20210183768A1 (en) | Integrated circuits including via array and methods of manufacturing the same | |

| KR20200018135A (ko) | 다중 높이 셀을 포함하는 집적 회로 및 이를 제조하기 위한 방법 | |

| US11869884B2 (en) | Semiconductor devices, methods of designing layouts of semiconductor devices and methods of fabricating semiconductor devices | |

| US11386254B2 (en) | Semiconductor circuit and semiconductor circuit layout system | |

| JP2008042050A (ja) | 半導体記憶装置 | |

| US4652992A (en) | Topography of integrated circuit CMOS microprocessor chip | |

| CN117999651A (zh) | 用于利用减小的接触栅极多晶硅间距和双高度单元来减小电压降的标准单元设计架构 | |

| US4739475A (en) | Topography for sixteen bit CMOS microprocessor with eight bit emulation and abort capability | |

| US5097413A (en) | Abort circuitry for microprocessor | |

| US20240169137A1 (en) | Integrated circuit including standard cells and method of designing the same | |

| JP2007041774A (ja) | 半導体集積回路の基本セル及びそのレイアウト方法 | |

| US20230290784A1 (en) | Integrated circuit including active pattern having variable width and method of designing the same | |

| US20240128257A1 (en) | Integrated circuit including standard cells and method of designing the same | |

| US20230297752A1 (en) | Integrated circuits including abutted blocks and methods of designing layouts of the integrated circuits | |

| JP5539156B2 (ja) | 半導体集積回路装置 | |

| JP3160227B2 (ja) | 半導体集積回路およびシステム | |

| JP2008258328A (ja) | 半導体装置、および集積回路の設計方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100602 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120120 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120120 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131018 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131022 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131224 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140225 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140425 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140520 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140718 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140924 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141023 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |