JP5630552B2 - 炭化珪素半導体装置およびその製造方法 - Google Patents

炭化珪素半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP5630552B2 JP5630552B2 JP2013215126A JP2013215126A JP5630552B2 JP 5630552 B2 JP5630552 B2 JP 5630552B2 JP 2013215126 A JP2013215126 A JP 2013215126A JP 2013215126 A JP2013215126 A JP 2013215126A JP 5630552 B2 JP5630552 B2 JP 5630552B2

- Authority

- JP

- Japan

- Prior art keywords

- conductivity type

- base layer

- region

- layer

- type base

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Electrodes Of Semiconductors (AREA)

Description

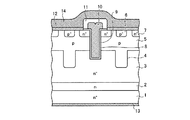

まず、実施の形態1にかかる半導体装置について説明する。図1は、実施の形態1にかかる半導体装置の断面構造について示す断面図である。実施の形態1にかかる半導体装置は、エピタキシャルウエハーを用いて作製される。エピタキシャルウエハーは、n+型4

H−SiC基板1の上に、n型バッファー層2と、n-型ドリフト層3とが、この順に積

層されている。

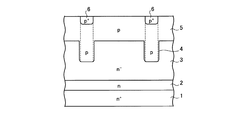

つぎに、実施の形態2にかかる半導体装置について説明する。図4は、実施の形態2にかかる半導体装置の断面構造について示す断面図である。図4に示すように、実施の形態2にかかる半導体装置は、第1トレンチが形成されず、p型ベース層5の一部が、第1主面から突き出た形状である。そして、p型ベース層5における突出領域15の表面層に、p+型ボディコンタクト領域6が設けられている。その他の構成は、実施の形態1と同様のため説明を省略する。

2 n型バッファー層

3 n-型ドリフト層

4 第1トレンチ

5 p型ベース層

6 p+型ボディコンタクト領域

7 n+型ソース領域

8 第2トレンチ

9 ゲート酸化膜

10 ゲート電極

11 層間絶縁膜

12 ソース電極

13 ドレイン電極

14 メタル

Claims (4)

- 第1導電型炭化珪素半導体基板のおもて面側の全面に設けられた第1導電型ドリフト層と、

前記第1導電型ドリフト層の全面に設けられた第2導電型ベース層と、

前記第2導電型ベース層の表面層に選択的に設けられた第2導電型不純物領域と、

前記第2導電型ベース層の表面層に、前記第2導電型不純物領域と離れて設けられたトレンチと、

前記トレンチの内部に、ゲート酸化膜を介して埋め込まれたゲート電極と、

前記第2導電型ベース層の表面層に、前記トレンチと接し、前記第2導電型不純物領域と離れて設けられた第1導電型ソース領域と、

前記ゲート電極を覆うように設けられた絶縁膜と、

前記第2導電型不純物領域および前記第1導電型ソース領域に接するように設けられたソース電極と、

前記第1導電型炭化珪素半導体基板の裏面側に設けられたドレイン電極と、

を備え、

前記第2導電型ベース層の、前記第2導電型不純物領域と前記第1導電型ドリフト層とに挟まれた部分の厚さは、前記第2導電型ベース層の、前記第2導電型不純物領域と前記第1導電型ドリフト層とに挟まれた部分以外の領域の厚さよりも厚く、

前記第2導電型ベース層の、前記第2導電型不純物領域と前記第1導電型ドリフト層とに挟まれた部分は、前記第2導電型ベース層の、前記第2導電型不純物領域と前記第1導電型ドリフト層とに挟まれた部分以外の領域よりも前記ソース電極側に突出していることを特徴とする炭化珪素半導体装置。 - 前記第2導電型不純物領域の底部から前記第2導電型ベース層と前記第1導電型ドリフト層との界面までの距離は、4μm以上であることを特徴とする請求項1に記載の炭化珪素半導体装置。

- 第1導電型炭化珪素半導体基板のおもて面側の全面に第1導電型ドリフト層を積層する工程と、

前記第1導電型ドリフト層の全面に第2導電型ベース層を積層する工程と、

前記第2導電型ベース層を所定深さでかつ選択的にエッチングし、前記第2導電型ベース層の一部を突出領域として残す工程と、

前記突出領域の表面層に第2導電型不純物領域を形成する工程と、

前記第2導電型ベース層の表面層の、前記突出領域以外の領域に第1導電型ソース領域を形成する工程と、

前記第1導電型ソース領域および前記第2導電型ベース層を貫通するように第2トレンチを形成する工程と、

前記第2トレンチの内部に、ゲート酸化膜を介してゲート電極を形成する工程と、

前記第1導電型ソース領域および前記第2導電型不純物領域に接するようにソース電極を形成する工程と、

前記第1導電型炭化珪素半導体基板の裏面側にドレイン電極を形成する工程と、

を含むことを特徴とする炭化珪素半導体装置の製造方法。 - 前記第2導電型ベース層を積層する工程においては、厚さが4μm以上となるように、前記第1導電型ドリフト層の全面に前記第2導電型ベース層を積層することを特徴とする請求項3に記載の炭化珪素半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013215126A JP5630552B2 (ja) | 2013-10-15 | 2013-10-15 | 炭化珪素半導体装置およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013215126A JP5630552B2 (ja) | 2013-10-15 | 2013-10-15 | 炭化珪素半導体装置およびその製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009109994A Division JP5613995B2 (ja) | 2009-04-28 | 2009-04-28 | 炭化珪素半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014033223A JP2014033223A (ja) | 2014-02-20 |

| JP5630552B2 true JP5630552B2 (ja) | 2014-11-26 |

Family

ID=50282767

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013215126A Expired - Fee Related JP5630552B2 (ja) | 2013-10-15 | 2013-10-15 | 炭化珪素半導体装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5630552B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6428489B2 (ja) | 2014-09-16 | 2018-11-28 | 株式会社デンソー | 炭化珪素半導体装置およびその製造方法 |

| JP6453634B2 (ja) | 2014-12-10 | 2019-01-16 | トヨタ自動車株式会社 | 半導体装置 |

| JP6822088B2 (ja) | 2016-11-15 | 2021-01-27 | 富士電機株式会社 | 炭化珪素半導体装置および炭化珪素半導体装置の製造方法 |

| US11075295B2 (en) * | 2018-07-13 | 2021-07-27 | Cree, Inc. | Wide bandgap semiconductor device |

| CN116110957A (zh) * | 2023-04-17 | 2023-05-12 | 深圳平创半导体有限公司 | 一种SiC多级阶梯分裂栅沟槽MOSFET器件及其制作方法 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE3380136D1 (en) * | 1982-04-12 | 1989-08-03 | Gen Electric | Semiconductor device having a diffused region of reduced length and method of fabricating the same |

| DE69631995T2 (de) * | 1995-06-02 | 2005-02-10 | Siliconix Inc., Santa Clara | Bidirektional sperrender Graben-Leistungs-MOSFET |

| JPH0997904A (ja) * | 1995-10-02 | 1997-04-08 | Denso Corp | 半導体装置 |

| GB2347014B (en) * | 1999-02-18 | 2003-04-16 | Zetex Plc | Semiconductor device |

| JP4655340B2 (ja) * | 2000-07-10 | 2011-03-23 | 株式会社デンソー | 半導体装置の製造方法 |

| JP3707424B2 (ja) * | 2001-11-22 | 2005-10-19 | 株式会社デンソー | 炭化珪素半導体装置及びその製造方法 |

| TWI268549B (en) * | 2002-05-10 | 2006-12-11 | General Semiconductor Inc | A surface geometry for a MOS-gated device that allows the manufacture of dice having different sizes and method for using same |

| JP4366938B2 (ja) * | 2003-01-16 | 2009-11-18 | トヨタ自動車株式会社 | 半導体装置 |

| JP4450241B2 (ja) * | 2007-03-20 | 2010-04-14 | 株式会社デンソー | 炭化珪素半導体装置の製造方法 |

-

2013

- 2013-10-15 JP JP2013215126A patent/JP5630552B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014033223A (ja) | 2014-02-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5613995B2 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP7241848B2 (ja) | 絶縁ゲート型炭化珪素半導体装置 | |

| CN108735817B (zh) | 具有沟槽底部中的偏移的SiC半导体器件 | |

| JP3979788B2 (ja) | 炭化ケイ素ディバイス | |

| JP6241958B2 (ja) | 高耐圧半導体装置およびその製造方法 | |

| US9048215B2 (en) | Semiconductor device having a high breakdown voltage | |

| JP2008016747A (ja) | トレンチmos型炭化珪素半導体装置およびその製造方法 | |

| WO2013001677A1 (ja) | 半導体装置とその製造方法 | |

| US9018633B2 (en) | Semiconductor device | |

| JP5463725B2 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP2016115847A (ja) | 半導体装置 | |

| WO2012131768A1 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP2017092355A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP7150609B2 (ja) | 短チャネルのトレンチパワーmosfet | |

| JP5630552B2 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP2018022852A (ja) | 半導体装置およびその製造方法 | |

| JP6160216B2 (ja) | 半導体装置 | |

| JPWO2017094339A1 (ja) | 炭化珪素半導体装置 | |

| JP6550869B2 (ja) | 半導体装置 | |

| JP2018082056A (ja) | 半導体装置および半導体装置の製造方法 | |

| KR20140044075A (ko) | 반도체 소자 및 그 제조 방법 | |

| WO2013146329A1 (ja) | 高耐圧半導体装置 | |

| JP5556862B2 (ja) | トレンチmos型炭化珪素半導体装置の製造方法 | |

| US7626232B2 (en) | Voltage-controlled semiconductor device | |

| JP2017092364A (ja) | 半導体装置および半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140909 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140911 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140922 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5630552 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |