JP5322408B2 - 半導体装置及びその作製方法 - Google Patents

半導体装置及びその作製方法 Download PDFInfo

- Publication number

- JP5322408B2 JP5322408B2 JP2007185597A JP2007185597A JP5322408B2 JP 5322408 B2 JP5322408 B2 JP 5322408B2 JP 2007185597 A JP2007185597 A JP 2007185597A JP 2007185597 A JP2007185597 A JP 2007185597A JP 5322408 B2 JP5322408 B2 JP 5322408B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- insulating film

- region

- gate insulating

- semiconductor film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 286

- 238000004519 manufacturing process Methods 0.000 title claims description 40

- 239000000758 substrate Substances 0.000 claims abstract description 48

- 239000010408 film Substances 0.000 claims description 766

- 230000015572 biosynthetic process Effects 0.000 claims description 72

- 238000000034 method Methods 0.000 claims description 68

- 239000010409 thin film Substances 0.000 claims description 41

- 238000000926 separation method Methods 0.000 abstract description 13

- 239000010410 layer Substances 0.000 description 80

- 239000012535 impurity Substances 0.000 description 62

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 38

- 239000000463 material Substances 0.000 description 38

- 239000010936 titanium Substances 0.000 description 33

- 229910052581 Si3N4 Inorganic materials 0.000 description 29

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 29

- 229910052782 aluminium Inorganic materials 0.000 description 28

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 28

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 25

- 229910052710 silicon Inorganic materials 0.000 description 25

- 239000010703 silicon Substances 0.000 description 25

- 239000010949 copper Substances 0.000 description 23

- 230000004888 barrier function Effects 0.000 description 21

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 21

- 229910052721 tungsten Inorganic materials 0.000 description 21

- 239000010937 tungsten Substances 0.000 description 21

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 19

- 229910052751 metal Inorganic materials 0.000 description 19

- 239000002184 metal Substances 0.000 description 19

- 229910052750 molybdenum Inorganic materials 0.000 description 19

- 239000011733 molybdenum Substances 0.000 description 19

- 229910052719 titanium Inorganic materials 0.000 description 19

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 18

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 18

- CSDREXVUYHZDNP-UHFFFAOYSA-N alumanylidynesilicon Chemical compound [Al].[Si] CSDREXVUYHZDNP-UHFFFAOYSA-N 0.000 description 18

- 238000004544 sputter deposition Methods 0.000 description 18

- 239000000956 alloy Substances 0.000 description 17

- 238000005530 etching Methods 0.000 description 17

- 229920005989 resin Polymers 0.000 description 17

- 239000011347 resin Substances 0.000 description 17

- 229910052814 silicon oxide Inorganic materials 0.000 description 17

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 17

- 230000009977 dual effect Effects 0.000 description 16

- 239000002356 single layer Substances 0.000 description 16

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 15

- 230000006870 function Effects 0.000 description 15

- 239000010931 gold Substances 0.000 description 15

- 229910052759 nickel Inorganic materials 0.000 description 15

- 229910052715 tantalum Inorganic materials 0.000 description 15

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 13

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 12

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 12

- 229910052799 carbon Inorganic materials 0.000 description 12

- 238000005229 chemical vapour deposition Methods 0.000 description 12

- 229910052802 copper Inorganic materials 0.000 description 12

- 238000002425 crystallisation Methods 0.000 description 12

- 239000011651 chromium Substances 0.000 description 11

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 11

- 230000008569 process Effects 0.000 description 11

- 229910052709 silver Inorganic materials 0.000 description 11

- 239000004332 silver Substances 0.000 description 11

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 11

- 239000002216 antistatic agent Substances 0.000 description 10

- 230000008025 crystallization Effects 0.000 description 10

- 238000010438 heat treatment Methods 0.000 description 10

- 239000010955 niobium Substances 0.000 description 10

- 239000002245 particle Substances 0.000 description 10

- -1 tungsten nitride Chemical class 0.000 description 10

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 9

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 9

- 239000003990 capacitor Substances 0.000 description 9

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 9

- 230000000694 effects Effects 0.000 description 8

- 239000010419 fine particle Substances 0.000 description 8

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 8

- 229910052737 gold Inorganic materials 0.000 description 8

- 239000011368 organic material Substances 0.000 description 8

- 238000000206 photolithography Methods 0.000 description 8

- 229910000679 solder Inorganic materials 0.000 description 8

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 7

- 229910052804 chromium Inorganic materials 0.000 description 7

- 150000001875 compounds Chemical class 0.000 description 7

- 239000013078 crystal Substances 0.000 description 7

- 229910052698 phosphorus Inorganic materials 0.000 description 7

- 239000011574 phosphorus Substances 0.000 description 7

- 229910052697 platinum Inorganic materials 0.000 description 7

- 238000007650 screen-printing Methods 0.000 description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- 239000004952 Polyamide Substances 0.000 description 6

- 239000004642 Polyimide Substances 0.000 description 6

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 6

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 6

- 239000004020 conductor Substances 0.000 description 6

- 238000005224 laser annealing Methods 0.000 description 6

- 239000011572 manganese Substances 0.000 description 6

- 239000001301 oxygen Substances 0.000 description 6

- 229910052760 oxygen Inorganic materials 0.000 description 6

- 229920002120 photoresistant polymer Polymers 0.000 description 6

- 229920002647 polyamide Polymers 0.000 description 6

- 229920001721 polyimide Polymers 0.000 description 6

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 5

- 229910052779 Neodymium Inorganic materials 0.000 description 5

- 229910021417 amorphous silicon Inorganic materials 0.000 description 5

- 239000012298 atmosphere Substances 0.000 description 5

- 235000013305 food Nutrition 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- 230000036541 health Effects 0.000 description 5

- 229910010272 inorganic material Inorganic materials 0.000 description 5

- 239000011147 inorganic material Substances 0.000 description 5

- 230000001678 irradiating effect Effects 0.000 description 5

- 229910052758 niobium Inorganic materials 0.000 description 5

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 5

- 229910052763 palladium Inorganic materials 0.000 description 5

- 239000004593 Epoxy Substances 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 4

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 4

- 239000003814 drug Substances 0.000 description 4

- 238000000605 extraction Methods 0.000 description 4

- 239000002923 metal particle Substances 0.000 description 4

- 230000010355 oscillation Effects 0.000 description 4

- 238000004806 packaging method and process Methods 0.000 description 4

- 238000007639 printing Methods 0.000 description 4

- 230000008054 signal transmission Effects 0.000 description 4

- 229910021332 silicide Inorganic materials 0.000 description 4

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 4

- 238000007725 thermal activation Methods 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 3

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 3

- 229920001665 Poly-4-vinylphenol Polymers 0.000 description 3

- 229910001362 Ta alloys Inorganic materials 0.000 description 3

- 229910001080 W alloy Inorganic materials 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 3

- 238000000137 annealing Methods 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 238000006356 dehydrogenation reaction Methods 0.000 description 3

- 229940079593 drug Drugs 0.000 description 3

- 230000005611 electricity Effects 0.000 description 3

- 230000005674 electromagnetic induction Effects 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 229910052739 hydrogen Inorganic materials 0.000 description 3

- 238000007689 inspection Methods 0.000 description 3

- 150000002500 ions Chemical class 0.000 description 3

- 229910052748 manganese Inorganic materials 0.000 description 3

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 3

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 3

- 229910021334 nickel silicide Inorganic materials 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 230000003068 static effect Effects 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- 125000001424 substituent group Chemical group 0.000 description 3

- 229910021341 titanium silicide Inorganic materials 0.000 description 3

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 3

- 229910021342 tungsten silicide Inorganic materials 0.000 description 3

- 229910052691 Erbium Inorganic materials 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- 229910004283 SiO 4 Inorganic materials 0.000 description 2

- 229910052775 Thulium Inorganic materials 0.000 description 2

- 229910052769 Ytterbium Inorganic materials 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 239000011230 binding agent Substances 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 239000002270 dispersing agent Substances 0.000 description 2

- 239000002019 doping agent Substances 0.000 description 2

- 239000003822 epoxy resin Substances 0.000 description 2

- 125000001153 fluoro group Chemical group F* 0.000 description 2

- 229910052839 forsterite Inorganic materials 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 238000007646 gravure printing Methods 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- HCWCAKKEBCNQJP-UHFFFAOYSA-N magnesium orthosilicate Chemical compound [Mg+2].[Mg+2].[O-][Si]([O-])([O-])[O-] HCWCAKKEBCNQJP-UHFFFAOYSA-N 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- 239000002105 nanoparticle Substances 0.000 description 2

- 125000000962 organic group Chemical group 0.000 description 2

- 238000002294 plasma sputter deposition Methods 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 229920003023 plastic Polymers 0.000 description 2

- 238000007747 plating Methods 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920000647 polyepoxide Polymers 0.000 description 2

- 239000010948 rhodium Substances 0.000 description 2

- 229920002050 silicone resin Polymers 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- 241001465754 Metazoa Species 0.000 description 1

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 229910004205 SiNX Inorganic materials 0.000 description 1

- 229910004286 SiNxOy Inorganic materials 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 239000003905 agrochemical Substances 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- 239000002280 amphoteric surfactant Substances 0.000 description 1

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 1

- 235000013361 beverage Nutrition 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 230000036760 body temperature Effects 0.000 description 1

- 125000003178 carboxy group Chemical group [H]OC(*)=O 0.000 description 1

- 239000003093 cationic surfactant Substances 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- 239000012943 hotmelt Substances 0.000 description 1

- 238000005984 hydrogenation reaction Methods 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000009545 invasion Effects 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 238000004898 kneading Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 244000144972 livestock Species 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 150000002751 molybdenum Chemical class 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 239000002736 nonionic surfactant Substances 0.000 description 1

- 229910052762 osmium Inorganic materials 0.000 description 1

- SYQBFIAQOQZEGI-UHFFFAOYSA-N osmium atom Chemical compound [Os] SYQBFIAQOQZEGI-UHFFFAOYSA-N 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 125000001453 quaternary ammonium group Chemical group 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- 239000010979 ruby Substances 0.000 description 1

- 229910001750 ruby Inorganic materials 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 1

- 238000007711 solidification Methods 0.000 description 1

- 230000008023 solidification Effects 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000004094 surface-active agent Substances 0.000 description 1

- OFIYHXOOOISSDN-UHFFFAOYSA-N tellanylidenegallium Chemical compound [Te]=[Ga] OFIYHXOOOISSDN-UHFFFAOYSA-N 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 238000004506 ultrasonic cleaning Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1262—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate

- H01L27/1266—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate the substrate on which the devices are formed not being the final device substrate, e.g. using a temporary substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/127—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement

- H01L27/1274—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor

- H01L27/1277—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor using a crystallisation promoting species, e.g. local introduction of Ni catalyst

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

- H01L29/78648—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate arranged on opposing sides of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41733—Source or drain electrodes for field effect devices for thin film transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

- H01L29/78621—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Ceramic Engineering (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

Description

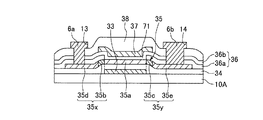

このデュアルゲートTFTは、基板本体10A、下部ゲート電極33、下部ゲート絶縁膜34、半導体膜35、第1及び第2絶縁層36a、36bからなる上部ゲート絶縁膜36、上部ゲート電極37及び層間絶縁膜38を有し、半導体膜35は、チャネル領域35a、低濃度ソース領域35bと高濃度ソース領域35dからなるソース領域35x、低濃度ドレイン領域35cと高濃度ドレイン領域35eからなるドレイン領域35yを備えている。上部ゲート絶縁膜36及び層間絶縁膜38にはコンタクトホール13,14が設けられており、このコンタクトホール13,14を介してデータ線6a及びソース線6bそれぞれが半導体膜35の高濃度ソース領域35d及び高濃度ドレイン領域35eに電気的に接続されている。

前記剥離層上に絶縁膜を形成し、

前記絶縁膜上に下部ゲート絶縁膜を形成し、

前記下部ゲート絶縁膜上に非晶質半導体膜を形成し、

前記非晶質半導体膜を結晶化することにより前記下部ゲート絶縁膜上に結晶質半導体膜を形成し、

前記結晶質半導体膜上に上部ゲート絶縁膜を形成し、

前記上部ゲート絶縁膜上に上部ゲート電極を形成し、

前記剥離層を前記絶縁膜から剥離し、

前記絶縁膜を加工することにより前記下部ゲート絶縁膜を露出させ、

前記露出した下部ゲート絶縁膜に接する下部ゲート電極を形成することを特徴とする。

また、本発明に係る半導体装置の作製方法において、前記結晶質半導体膜は、チャネル形成領域及び該チャネル形成領域の外側に形成された低濃度不純物領域を有しており、前記下部ゲート電極が前記下部ゲート絶縁膜に接する領域は、前記チャネル形成領域と前記低濃度不純物領域とに対応する領域の内側に位置していることも可能である。

前記剥離層上に絶縁膜を形成し、

前記絶縁膜上に非晶質半導体膜を形成し、

前記非晶質半導体膜を結晶化することにより前記絶縁膜上に結晶質半導体膜を形成し、

前記結晶質半導体膜上に上部ゲート絶縁膜を形成し、

前記上部ゲート絶縁膜上に上部ゲート電極を形成し、

前記剥離層を前記絶縁膜から剥離し、

前記絶縁膜に開口部を形成することにより該開口部によって前記結晶質半導体膜を露出させ、

前記露出した結晶質半導体膜に接する下部ゲート絶縁膜を形成し、

前記下部ゲート絶縁膜に接する下部ゲート電極を形成することを特徴とする。

また、本発明に係る半導体装置の作製方法において、前記結晶質半導体膜は、チャネル形成領域及び該チャネル形成領域の外側に形成された低濃度不純物領域を有しており、前記開口部によって前記結晶質半導体膜が露出した領域は、前記チャネル形成領域と前記低濃度不純物領域とに対応する領域の内側に位置していることも可能である。

前記剥離層上に絶縁膜を形成し、

前記絶縁膜上に非晶質半導体膜を形成し、

前記非晶質半導体膜を結晶化することにより前記絶縁膜上に結晶質半導体膜を形成し、

前記結晶質半導体膜上に上部ゲート絶縁膜を形成し、

前記上部ゲート絶縁膜上に上部ゲート電極を形成し、

前記剥離層を前記絶縁膜から剥離し、

前記絶縁膜を加工することにより前記結晶質半導体膜を露出させ、

前記露出した結晶質半導体膜を加工することにより、前記結晶質半導体膜にその膜厚を薄くした薄膜領域を形成し、

前記薄膜領域に接する下部ゲート絶縁膜を形成し、

前記下部ゲート絶縁膜に接する下部ゲート電極を形成することを特徴とする。

前記絶縁膜上に形成された下部ゲート絶縁膜と、

前記下部ゲート絶縁膜上に形成され、非晶質半導体膜が結晶化された結晶質半導体膜と、

前記結晶質半導体膜上に形成された上部ゲート絶縁膜と、

前記上部ゲート絶縁膜上に形成された上部ゲート電極と、

前記絶縁膜に形成され、前記下部ゲート絶縁膜下に位置された開口部と、

前記開口部内に形成され、前記下部ゲート絶縁膜に接して形成された下部ゲート電極と、

を具備することを特徴とする。

また、絶縁膜が平面上に形成されていることが好ましいことは以下の半導体装置においても同様である。

前記絶縁膜上に形成され、非晶質半導体膜が結晶化された結晶質半導体膜と、

前記結晶質半導体膜上に形成された上部ゲート絶縁膜と、

前記上部ゲート絶縁膜上に形成された上部ゲート電極と、

前記絶縁膜に形成され、前記結晶質半導体膜下に位置された開口部と、

前記開口部内に形成され、前記結晶質半導体膜に接して形成された下部ゲート絶縁膜と、

前記開口部内に形成され、前記下部ゲート絶縁膜に接して形成された下部ゲート電極と、

を具備することを特徴とする。

また、本発明に係る半導体装置において、前記結晶質半導体膜は、チャネル形成領域及び該チャネル形成領域の外側に形成された低濃度不純物領域を有しており、前記下部ゲート電極が前記下部ゲート絶縁膜に接する領域は、前記チャネル形成領域と前記低濃度不純物領域とに対応する領域の内側に位置していることも可能である。

前記絶縁膜上に形成され、非晶質半導体膜が結晶化された結晶質半導体膜と、

前記結晶質半導体膜上に形成された上部ゲート絶縁膜と、

前記上部ゲート絶縁膜上に形成された上部ゲート電極と、

前記絶縁膜に形成され、前記結晶質半導体膜下に位置された開口部と、

前記開口部に繋げられ、前記結晶質半導体膜内に形成された凹部と、

前記凹部上に形成され、前記結晶質半導体膜の膜厚が薄くされた薄膜領域と、

前記凹部内に形成され、前記薄膜領域に接して形成された下部ゲート絶縁膜と、

前記凹部内及び前記開口部内に形成され、前記下部ゲート絶縁膜に接して形成された下部ゲート電極と、

を具備することを特徴とする。

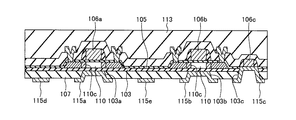

図1〜図3は、本発明の実施の形態1による半導体装置の作製方法を示す断面図である。

なお、本実施の形態では、素子形成層114を基板101から剥離しているが、これに限定されるものではなく、基板101及び剥離層102を、研削処理、研磨処理又は化学処理によるエッチングを行うことにより除去しても良い。

詳細には、絶縁膜107の露出面にフォトレジスト膜(図示せず)を塗布し、このフォトレジスト膜を露光、現像することにより、絶縁膜107の露出面にはレジストパターンが形成される。このレジストパターンをマスクとして絶縁膜107をエッチングすることにより、絶縁膜107には下部ゲート絶縁膜103を介してチャネル形成領域110上に位置する開口部103a,103bが形成される。開口部103a,103bによって露出される下部ゲート絶縁膜103は、チャネル形成領域110に対応する領域と同じかそれより内側にあって小さい領域である。

次いで、前記レジストパターンを剥離する。

上記のようにしてデュアルゲートTFTを作製することができる。

図4は、本発明の実施の形態2による半導体装置の作製方法を説明する断面図である。図4に示す工程は、図3(A)に示す工程に対応するものであり、図3と同一部分には同一符号を付し、実施の形態1と異なる部分についてのみ説明する。

図5(A),(B)は、本発明の実施の形態3による半導体装置の作製方法を説明する断面図である。図5に示す工程は、図3(A)に示す工程に対応するものであり、図3と同一部分には同一符号を付し、実施の形態1と異なる部分についてのみ説明する。

また、上記実施の形態3では、下部ゲート絶縁膜103fの膜厚を実施の形態1におけるそれより薄くしているため、実施の形態1に比べてデバイスの消費電力を低くすることができる。

これに対し、実施の形態3のように図5(A)に示す工程で膜厚の薄い下部ゲート絶縁膜103fを形成し、この下部ゲート絶縁膜103f上に下部ゲート電極115a,115bを形成した場合、前記膜厚の薄い下部ゲート絶縁膜103fを確実に形成することが可能となる。

図6(A),(B)は、本発明の実施の形態4による半導体装置の作製方法を説明する断面図である。図6(A),(B)に示す工程は、図5(A),(B)に示す工程に対応するものであり、図5と同一部分には同一符号を付し、実施の形態3と異なる部分についてのみ説明する。

図7(A),(B)は、本発明の実施の形態5による半導体装置の作製方法を説明する断面図である。図7(A),(B)に示す工程は、図5(A),(B)に示す工程に対応するものであり、図5と同一部分には同一符号を付し、実施の形態3と異なる部分についてのみ説明する。

また、上記実施の形態5では、チャネル形成領域110に対応する領域の結晶質半導体膜に、その膜厚を薄くした薄膜領域110aを形成することにより、S値を小さくすることができ、その結果、実施の形態3に比べてデバイスの消費電力を低くすることができる。

実施の形態6では、上記実施の形態1〜5で示した半導体装置の使用形態の一例について説明する。具体的には、非接触でデータの入出力が可能である半導体装置の適用例に関して図8及び図9を参照して以下に説明する。非接触でデータの入出力が可能である半導体装置は利用の形態によっては、RFIDタグ、IDタグ、ICタグ、ICチップ、RFタグ、無線タグ、電子タグまたは無線チップともよばれる。

本実施の形態では、上記実施の形態6で示した非接触でデータの入出力が可能である半導体装置の作製方法に関して図10〜図13を参照して説明する。なお、本実施の形態では、薄膜トランジスタ等の素子を一度支持基板(仮基板)に設けた後、可撓性を有する基板に転置して半導体装置を作製する場合に関して説明する。

なお、本実施の形態では、図12(B)に示す工程でレーザーアニールを行っているが、図12(B)の工程は必ずしも必要ではなく、この工程を省略することも可能である。

上記のようにしてデュアルゲートTFTを作製することができる。

81 高周波回路

82 電源回路

83 リセット回路

84 クロック発生回路

85 データ復調回路

86 データ変調回路

87 制御回路

88 記憶回路

89 アンテナ

91 コード抽出回路

92 コード判定回路

93 CRC判定回路

94 出力ユニット回路

101 基板

102 剥離層

103 下部ゲート絶縁膜

103a〜103c 開口部

103f 下部ゲート絶縁膜

104 半導体膜

104a,104b 結晶質半導体膜

105 上部ゲート絶縁膜

106 導電膜

106a,106b 導電膜(上部ゲート電極)

106c 導電膜(配線)

107 絶縁膜

108 低濃度不純物領域

109 絶縁膜

110 チャネル形成領域

110b 高濃度不純物領域

110c 低濃度不純物領域

111,113,116 絶縁膜

112 導電膜

114 素子形成層

115a,115b 導電膜(下部ゲート電極)

115c〜115e,117 導電膜(配線)

120a,120b 薄膜トランジスタ

300a〜300c,300e 薄膜トランジスタ

300f 容量素子

301 基板

302,304 絶縁膜

303 剥離層

304a〜304f 開口部

305,305a〜305f 半導体膜

306 ゲート絶縁膜

307 ゲート電極

307a,307b 導電膜

308,309 不純物領域

310,312a,312b,314,318,323 絶縁膜

311 不純物領域

313,316,317 導電膜

319 素子形成層

320,321 シート材

322a〜322e 導電膜(下部ゲート電極)

322f 導電膜

3200 リーダ/ライタ

3210 表示部

3220 品物

3230,3250 半導体装置

3240 リーダ/ライタ

3260 商品

Claims (4)

- 基板上に剥離層を形成し、

前記剥離層上に絶縁膜を形成し、

前記絶縁膜上に第1のゲート絶縁膜を形成し、

前記第1のゲート絶縁膜上に非晶質半導体膜を形成し、

前記非晶質半導体膜を結晶化して、前記第1のゲート絶縁膜上に結晶質半導体膜を形成し、

前記結晶質半導体膜上に第2のゲート絶縁膜を形成し、

前記第2のゲート絶縁膜上に、前記結晶質半導体膜と重なる第2のゲート電極を形成し、

前記基板及び前記剥離層を前記絶縁膜から剥離し、

前記絶縁膜に開口部を形成して、前記第1のゲート絶縁膜の一部を露出させ、

前記露出した第1のゲート絶縁膜に接する第1のゲート電極を形成し、

前記結晶質半導体膜は、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域との間にチャネル形成領域と、を有し、

前記第1のゲート電極と前記第1のゲート絶縁膜とが接する領域は、前記チャネル形成領域と重なることを特徴とする半導体装置の作製方法。 - 基板上に剥離層を形成し、

前記剥離層上に絶縁膜を形成し、

前記絶縁膜上に非晶質半導体膜を形成し、

前記非晶質半導体膜を結晶化して、前記絶縁膜上に結晶質半導体膜を形成し、

前記結晶質半導体膜上に第2のゲート絶縁膜を形成し、

前記第2のゲート絶縁膜上に、前記結晶質半導体膜と重なる第2のゲート電極を形成し、

前記基板及び前記剥離層を前記絶縁膜から剥離し、

前記絶縁膜に開口部を形成して、前記結晶質半導体膜の一部を露出させ、

前記露出した結晶質半導体膜に接する第1のゲート絶縁膜を形成し、

前記第1のゲート絶縁膜に接する第1のゲート電極を形成し、

前記結晶質半導体膜は、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域との間にチャネル形成領域と、を有し、

前記結晶質半導体膜と前記第1のゲート絶縁膜とが接する領域は、前記チャネル形成領域と重なることを特徴とする半導体装置の作製方法。 - 基板上に剥離層を形成し、

前記剥離層上に絶縁膜を形成し、

前記絶縁膜上に非晶質半導体膜を形成し、

前記非晶質半導体膜を結晶化して、前記絶縁膜上に結晶質半導体膜を形成し、

前記結晶質半導体膜上に第2のゲート絶縁膜を形成し、

前記第2のゲート絶縁膜上に、前記結晶質半導体膜と重なる第2のゲート電極を形成し、

前記基板及び前記剥離層を前記絶縁膜から剥離し、

前記絶縁膜に開口部を形成して、前記結晶質半導体膜の一部を露出させ、

前記露出した結晶質半導体膜を部分的に除去して、前記結晶質半導体膜に薄膜領域を形成し、

前記薄膜領域に接する第1のゲート絶縁膜を形成し、

前記第1のゲート絶縁膜に接する第1のゲート電極を形成し、

前記結晶質半導体膜は、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域との間にチャネル形成領域と、を有し、

前記薄膜領域と前記第1のゲート絶縁膜とが接する領域は、前記チャネル形成領域と重なることを特徴とする半導体装置の作製方法。 - 絶縁膜と、

前記絶縁膜上に設けられた結晶質半導体膜と、

前記結晶質半導体膜上に設けられた第2のゲート絶縁膜と、

前記第2のゲート絶縁膜上に設けられ、かつ前記結晶質半導体膜と重なる第2のゲート電極と、

前記絶縁膜に設けられ、かつ前記結晶質半導体膜と重なる開口部と、

前記結晶質半導体膜に設けられた第1の膜厚を有する第1の領域と、

前記結晶質半導体膜に設けられ、かつ前記開口部と重なり、かつ前記第1の膜厚より小さい第2の膜厚を有する第2の領域と、

前記開口部及び前記第2の領域に接して設けられた第1のゲート絶縁膜と、

前記第1のゲート絶縁膜に接して設けられ、かつ前記第1のゲート絶縁膜を介して前記第2の領域と重なる第1のゲート電極と、を具備し、

前記結晶質半導体膜は、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域との間にチャネル形成領域と、を有し、

前記第2の領域は前記チャネル形成領域と重なることを特徴とする半導体装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007185597A JP5322408B2 (ja) | 2007-07-17 | 2007-07-17 | 半導体装置及びその作製方法 |

| US12/174,252 US8012812B2 (en) | 2007-07-17 | 2008-07-16 | Semiconductor device and method for manufacturing the same |

| US13/190,506 US8674360B2 (en) | 2007-07-17 | 2011-07-26 | Semiconductor device having first gate electrode and second gate electrode |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007185597A JP5322408B2 (ja) | 2007-07-17 | 2007-07-17 | 半導体装置及びその作製方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013147447A Division JP5657069B2 (ja) | 2013-07-16 | 2013-07-16 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009026800A JP2009026800A (ja) | 2009-02-05 |

| JP2009026800A5 JP2009026800A5 (ja) | 2010-08-05 |

| JP5322408B2 true JP5322408B2 (ja) | 2013-10-23 |

Family

ID=40264103

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007185597A Expired - Fee Related JP5322408B2 (ja) | 2007-07-17 | 2007-07-17 | 半導体装置及びその作製方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US8012812B2 (ja) |

| JP (1) | JP5322408B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5487625B2 (ja) * | 2009-01-22 | 2014-05-07 | ソニー株式会社 | 半導体装置 |

| FR2970811B1 (fr) * | 2011-01-24 | 2013-01-25 | Commissariat Energie Atomique | Dispositif a effet de champ muni d'une contre-électrode amincie et procédé de réalisation |

| KR101962499B1 (ko) | 2011-10-28 | 2019-03-26 | 코닝 인코포레이티드 | 적외선 반사도를 갖는 유리 제품 및 이의 제조방법 |

| JP2014045175A (ja) | 2012-08-02 | 2014-03-13 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US8890247B2 (en) * | 2012-10-15 | 2014-11-18 | International Business Machines Corporation | Extremely thin semiconductor-on-insulator with back gate contact |

| KR102091485B1 (ko) * | 2013-12-30 | 2020-03-20 | 엘지디스플레이 주식회사 | 유기 발광 표시 장치 및 그의 구동 방법 |

| KR102368997B1 (ko) | 2014-06-27 | 2022-02-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 발광 장치, 모듈, 전자 기기, 발광 장치의 제작 방법 |

| WO2016176096A1 (en) | 2015-04-30 | 2016-11-03 | Corning Incorporated | Electrically conductive articles with discrete metallic silver layers and methods for making same |

| KR102397799B1 (ko) | 2015-06-30 | 2022-05-16 | 엘지디스플레이 주식회사 | 박막 트랜지스터 기판 및 이를 포함하는 표시장치 |

| US9780210B1 (en) * | 2016-08-11 | 2017-10-03 | Qualcomm Incorporated | Backside semiconductor growth |

| US20220115479A1 (en) * | 2018-09-18 | 2022-04-14 | Sharp Kabushiki Kaisha | Display device |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3209600B2 (ja) * | 1992-12-24 | 2001-09-17 | キヤノン株式会社 | 薄膜トランジスタの製造方法 |

| JP3253808B2 (ja) * | 1994-07-07 | 2002-02-04 | 株式会社半導体エネルギー研究所 | 半導体装置およびその作製方法 |

| JP3364081B2 (ja) * | 1995-02-16 | 2003-01-08 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JPH09116036A (ja) * | 1995-10-23 | 1997-05-02 | Oki Electric Ind Co Ltd | 不揮発性メモリセルトランジスタ |

| JP2877103B2 (ja) * | 1996-10-21 | 1999-03-31 | 日本電気株式会社 | 不揮発性半導体記憶装置およびその製造方法 |

| JP2001051292A (ja) | 1998-06-12 | 2001-02-23 | Semiconductor Energy Lab Co Ltd | 半導体装置および半導体表示装置 |

| JP2001028354A (ja) * | 1999-05-12 | 2001-01-30 | Sony Corp | 半導体装置の製造方法 |

| US6562723B1 (en) * | 1999-10-29 | 2003-05-13 | Advanced Micro Devices, Inc. | Hybrid stack method for patterning source/drain areas |

| US7189997B2 (en) * | 2001-03-27 | 2007-03-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US6906344B2 (en) * | 2001-05-24 | 2005-06-14 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor with plural channels and corresponding plural overlapping electrodes |

| TW564471B (en) * | 2001-07-16 | 2003-12-01 | Semiconductor Energy Lab | Semiconductor device and peeling off method and method of manufacturing semiconductor device |

| US6952023B2 (en) * | 2001-07-17 | 2005-10-04 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| JP3761168B2 (ja) * | 2002-09-30 | 2006-03-29 | 株式会社東芝 | 薄膜トランジスタ及びその製造方法 |

| KR101026644B1 (ko) * | 2003-01-08 | 2011-04-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| JP2004343018A (ja) * | 2003-03-20 | 2004-12-02 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| US7307317B2 (en) * | 2003-04-04 | 2007-12-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, CPU, image processing circuit and electronic device, and driving method of semiconductor device |

| JP2005079283A (ja) | 2003-08-29 | 2005-03-24 | Seiko Epson Corp | 薄膜半導体装置及びその製造方法、電気光学装置、並びに電子機器 |

| JP4554180B2 (ja) * | 2003-09-17 | 2010-09-29 | ソニー株式会社 | 薄膜半導体デバイスの製造方法 |

| JP4554344B2 (ja) * | 2003-12-02 | 2010-09-29 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| WO2005059990A1 (en) | 2003-12-02 | 2005-06-30 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device and semiconductor device and method for manufacturing the same |

| US7452786B2 (en) * | 2004-06-29 | 2008-11-18 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing thin film integrated circuit, and element substrate |

| JP4130186B2 (ja) * | 2004-11-12 | 2008-08-06 | 三洋電機株式会社 | パック電池 |

| US7736964B2 (en) * | 2004-11-22 | 2010-06-15 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and method for manufacturing the same |

| US7482248B2 (en) * | 2004-12-03 | 2009-01-27 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device |

-

2007

- 2007-07-17 JP JP2007185597A patent/JP5322408B2/ja not_active Expired - Fee Related

-

2008

- 2008-07-16 US US12/174,252 patent/US8012812B2/en not_active Expired - Fee Related

-

2011

- 2011-07-26 US US13/190,506 patent/US8674360B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20110278573A1 (en) | 2011-11-17 |

| US8012812B2 (en) | 2011-09-06 |

| US8674360B2 (en) | 2014-03-18 |

| JP2009026800A (ja) | 2009-02-05 |

| US20090020761A1 (en) | 2009-01-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5322408B2 (ja) | 半導体装置及びその作製方法 | |

| US7767516B2 (en) | Semiconductor device, manufacturing method thereof, and manufacturing method of antenna | |

| US7683838B2 (en) | Semiconductor device | |

| JP5252947B2 (ja) | 半導体装置の作製方法 | |

| JP5422138B2 (ja) | 半導体装置の作製方法 | |

| JP4942998B2 (ja) | 半導体装置及び半導体装置の作製方法 | |

| JP4827618B2 (ja) | アンテナの作製方法、半導体装置の作製方法 | |

| JP5264280B2 (ja) | 半導体装置の作製方法及び電子機器 | |

| JP5089033B2 (ja) | 半導体装置の作製方法 | |

| KR101377426B1 (ko) | 반도체 장치 | |

| JP5100012B2 (ja) | 半導体装置及びその作製方法 | |

| JP5657069B2 (ja) | 半導体装置 | |

| JP5388433B2 (ja) | 半導体装置の作製方法 | |

| JP5350616B2 (ja) | 半導体装置 | |

| JP5030470B2 (ja) | 半導体装置の作製方法 | |

| JP4908936B2 (ja) | 半導体装置の作製方法 | |

| JP5105918B2 (ja) | 半導体装置の作製方法 | |

| JP5137424B2 (ja) | 半導体装置及びその作製方法 | |

| JP5259977B2 (ja) | 半導体装置及び半導体装置の作製方法 | |

| KR20080074800A (ko) | 반도체 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100617 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100617 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121122 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121127 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130123 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130702 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130716 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5322408 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |