JP5224784B2 - 配線基板及びその製造方法 - Google Patents

配線基板及びその製造方法 Download PDFInfo

- Publication number

- JP5224784B2 JP5224784B2 JP2007290789A JP2007290789A JP5224784B2 JP 5224784 B2 JP5224784 B2 JP 5224784B2 JP 2007290789 A JP2007290789 A JP 2007290789A JP 2007290789 A JP2007290789 A JP 2007290789A JP 5224784 B2 JP5224784 B2 JP 5224784B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor element

- wiring board

- insulating layer

- stiffener

- electronic component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 74

- 239000004065 semiconductor Substances 0.000 claims description 302

- 239000003351 stiffener Substances 0.000 claims description 242

- 239000000463 material Substances 0.000 claims description 150

- 239000000758 substrate Substances 0.000 claims description 108

- 239000000853 adhesive Substances 0.000 claims description 106

- 230000001070 adhesive effect Effects 0.000 claims description 105

- 238000005520 cutting process Methods 0.000 claims description 52

- 238000000034 method Methods 0.000 claims description 45

- 230000000149 penetrating effect Effects 0.000 claims description 33

- 230000002093 peripheral effect Effects 0.000 claims description 15

- 238000003860 storage Methods 0.000 claims 2

- 229910000679 solder Inorganic materials 0.000 description 30

- 238000012986 modification Methods 0.000 description 20

- 230000004048 modification Effects 0.000 description 20

- 229910052751 metal Inorganic materials 0.000 description 18

- 239000002184 metal Substances 0.000 description 18

- 239000011347 resin Substances 0.000 description 14

- 229920005989 resin Polymers 0.000 description 14

- 239000004593 Epoxy Substances 0.000 description 11

- 239000011521 glass Substances 0.000 description 11

- 238000007747 plating Methods 0.000 description 10

- 229910000881 Cu alloy Inorganic materials 0.000 description 9

- 230000015572 biosynthetic process Effects 0.000 description 8

- 239000003822 epoxy resin Substances 0.000 description 7

- 230000035515 penetration Effects 0.000 description 7

- 229920000647 polyepoxide Polymers 0.000 description 7

- 238000005530 etching Methods 0.000 description 6

- 230000000694 effects Effects 0.000 description 5

- 229920001721 polyimide Polymers 0.000 description 4

- 239000009719 polyimide resin Substances 0.000 description 4

- 238000007796 conventional method Methods 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 2

- 239000003795 chemical substances by application Substances 0.000 description 2

- 238000009713 electroplating Methods 0.000 description 2

- 239000011888 foil Substances 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 238000003672 processing method Methods 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 238000007772 electroless plating Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49833—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers the chip support structure consisting of a plurality of insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/561—Batch processing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

- H01L23/13—Mountings, e.g. non-detachable insulating substrates characterised by the shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

- H01L23/14—Mountings, e.g. non-detachable insulating substrates characterised by the material or its electrical properties

- H01L23/15—Ceramic or glass substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/16—Fillings or auxiliary members in containers or encapsulations, e.g. centering rings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3121—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed a substrate forming part of the encapsulation

- H01L23/3128—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed a substrate forming part of the encapsulation the substrate having spherical bumps for external connection

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/562—Protection against mechanical damage

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2221/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof covered by H01L21/00

- H01L2221/67—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere

- H01L2221/683—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L2221/68304—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L2221/68345—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support used as a support during the manufacture of self supporting substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05571—Disposition the external layer being disposed in a recess of the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05573—Single external layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/061—Disposition

- H01L2224/0612—Layout

- H01L2224/0615—Mirror array, i.e. array having only a reflection symmetry, i.e. bilateral symmetry

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01046—Palladium [Pd]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

- H01L2924/15155—Shape the die mounting substrate comprising a recess for hosting the device the shape of the recess being other than a cuboid

- H01L2924/15157—Top view

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19041—Component type being a capacitor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19042—Component type being an inductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19043—Component type being a resistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19105—Disposition of discrete passive components in a side-by-side arrangement on a common die mounting substrate

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/4913—Assembling to base an electrical component, e.g., capacitor, etc.

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Geometry (AREA)

- Chemical & Material Sciences (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Structure Of Printed Boards (AREA)

Description

本発明のその他の観点によれば、絶縁層と、該絶縁層上に設けられた、半導体素子が搭載される半導体素子搭載用パッドと、前記半導体素子が搭載される半導体素子搭載領域よりも外側に形成された、電子部品が搭載される電子部品搭載用パッドとを有する配線基板本体と、前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に接着され、前記半導体素子搭載領域を露出する半導体素子搭載用貫通部と前記電子部品搭載用パッドを露出する電子部品搭載用貫通部とを有するスティフナーと、を備えた配線基板の製造方法であって、前記電子部品搭載用パッドに前記電子部品を搭載する電子部品搭載工程と、該電子部品搭載工程の後に、接着剤を介して前記スティフナーを前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に密着させて、余分な接着剤を前記電子部品搭載用貫通部内にはみ出させる接着工程と、を含むことを特徴とする配線基板の製造方法が提供される。

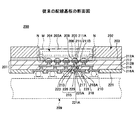

図10は、本発明の第1の実施の形態に係る配線基板の断面図であり、図11は、図10に示す配線基板の平面図である。図11では、図10に示すはんだ17の図示を省略する。

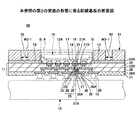

図31は、本発明の第2の実施の形態に係る配線基板の断面図であり、図32は、図31に示す配線基板の平面図である。図31及び図32において、第1の実施の形態の配線基板10と同一構成部分には同一符号を付す。また、図32では、図31に示すはんだ17の図示を省略する。

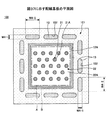

図39は、本発明の第3の実施の形態に係る配線基板の断面図であり、図40は、図39に示す配線基板の平面図である。図39及び図40において、第1の実施の形態の配線基板10と同一構成部分には同一符号を付す。また、図40では、図39に示すはんだ17の図示を省略する。

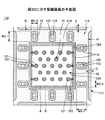

図49は、本発明の第4の実施の形態に係る配線基板の断面図であり、図50は、図49に示す配線基板の平面図である。図49及び図50において、第3の実施の形態の配線基板110と同一構成部分には同一符号を付す。また、図50では、図49に示すはんだ17の図示を省略する。

11,111 配線基板本体

12,61,71,91,101,114,151 スティフナー

12A,72 半導体素子搭載用貫通部

12B,61A 側壁

13 接着剤

14 半導体素子

15 電極パッド

16 内部接続端子

17 はんだ

18 実装基板

19,35 パッド

20 外部接続端子

21,121 半導体素子搭載用パッド

21A,118A,121A,122A 搭載面

21B,22A,22B,26A,35A 面

22,26 絶縁層

23,27 ビア

25,117 配線パターン

28 外部接続用パッド

28A 端子配設面

31 ソルダーレジスト層

31A,33,38,45A 開口部

36,123 配線

41,63,75 切り欠き部

43 支持体

43A 上面

45 めっき用レジストパターン

50,130 基板

55,67,80,95,132,155 スティフナー母材

55A,67A,92,102 貫通部

74 収容部

112 電子部品

118,122 電子部品搭載用パッド

125,141,152 電子部品搭載用貫通部

A 半導体素子搭載領域

B,F 領域

C,G 距離

D 配線基板本体形成領域

E 切断位置

W1−1,W1−2,W2−1,W2−2,W3−1,W3−2,W4−1,W4−2,W5−1,W5−2,W6−1,W6−2 幅

Claims (10)

- 半導体素子が搭載される半導体素子搭載用パッドと、前記半導体素子搭載用パッドが設けられる絶縁層と、前記半導体素子が搭載される半導体素子搭載領域とを有する配線基板本体と、

前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に接着され、前記半導体素子搭載領域を露出する半導体素子搭載用貫通部を有するスティフナーと、を備えた配線基板であって、

前記スティフナーに前記半導体素子搭載領域よりも外側に位置する部分の前記絶縁層の面を露出する貫通部が設けられ、

前記貫通部は、前記スティフナーの前記配線基板本体の各辺に対応する部分ごとに、複数設けられ、かつ、

前記貫通部の平面視における形状は、長方形において短辺が略半円となる形状であり、前記形状の長辺は、前記半導体素子搭載領域の1つの辺と対向するように設けられることを特徴とする配線基板。 - 前記配線基板本体は、前記絶縁層に設けられ、電子部品が搭載される電子部品搭載用パッドを有し、

前記スティフナーに、前記電子部品が搭載される領域に対応する部分の前記絶縁層の面を露出する電子部品搭載用貫通部を設けたことを特徴とする請求項1記載の配線基板。 - 前記貫通部と前記電子部品搭載用貫通部とを一体的に構成したことを特徴とする請求項2記載の配線基板。

- 前記半導体素子搭載用貫通部は、前記半導体素子を収容する収容部と、前記収容部の側壁に対応する部分のスティフナーに設けられ、前記絶縁層の面を露出する他の切り欠き部とを有することを特徴とする請求項1ないし3のうち、いずれか一項記載の配線基板。

- 半導体素子が搭載される半導体素子搭載用パッドと、前記半導体素子搭載用パッドが設けられる絶縁層と、前記半導体素子が搭載される半導体素子搭載領域とを有する配線基板本体と、

前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に接着され、前記半導体素子搭載領域を露出する半導体素子搭載用貫通部を有するスティフナーと、を備えた配線基板の製造方法であって、

複数の前記配線基板本体が隣接するように配置され、前記複数の配線基板本体が一体的に構成された基板を形成する基板形成工程と、

前記半導体素子搭載領域に対応する部分の前記基板を露出する前記半導体素子搭載用貫通部と、前記半導体素子搭載領域よりも外側に位置する部分の前記絶縁層の面を露出する貫通部とを備え、複数の前記スティフナーの母材となるスティフナー母材を形成するスティフナー母材形成工程と、

接着剤により、前記基板に設けられた前記絶縁層の面に前記スティフナー母材を接着する接着工程と、

前記接着工程後に、前記基板及び前記スティフナー母材を切断して、前記複数の配線基板本体及び前記複数のスティフナーを個片化する切断工程と、を含むことを特徴とする配線基板の製造方法。 - 前記貫通部は、前記配線基板本体の外周部に対応する部分の前記絶縁層の面から隣り合う他の前記配線基板本体の外周部に対応する部分の前記絶縁層の面に亘る領域の前記絶縁層の面を露出するように形成することを特徴とする請求項5記載の配線基板の製造方法。

- 前記スティフナー母材形成工程では、前記半導体素子搭載用貫通部及び前記貫通部を同時に形成することを特徴とする請求項5又は6に記載の配線基板の製造方法。

- 前記基板は、前記絶縁層に設けられ、電子部品が搭載される電子部品搭載用パッドを有し、

前記スティフナー母材は、前記電子部品搭載用パッドが形成される領域に対応する部分の前記絶縁層の面を露出する電子部品搭載用貫通部を備え、

前記スティフナー母材形成工程では、前記電子部品搭載用貫通部と前記半導体素子搭載用貫通部及び前記貫通部とを同時に形成することを特徴とする請求項5又は6記載の配線基板の製造方法。 - 前記接着工程の前に、前記電子部品を前記電子部品搭載用パッドに搭載する電子部品搭載工程を設けたことを特徴とする請求項8記載の配線基板の製造方法。

- 絶縁層と、該絶縁層上に設けられた、半導体素子が搭載される半導体素子搭載用パッドと、前記半導体素子が搭載される半導体素子搭載領域よりも外側に形成された、電子部品が搭載される電子部品搭載用パッドとを有する配線基板本体と、

前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に接着され、前記半導体素子搭載領域を露出する半導体素子搭載用貫通部と前記電子部品搭載用パッドを露出する電子部品搭載用貫通部とを有するスティフナーと、を備えた配線基板の製造方法であって、

前記電子部品搭載用パッドに前記電子部品を搭載する電子部品搭載工程と、

該電子部品搭載工程の後に、接着剤を介して前記スティフナーを前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に密着させて、余分な接着剤を前記電子部品搭載用貫通部内にはみ出させる接着工程と、を含むことを特徴とする配線基板の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007290789A JP5224784B2 (ja) | 2007-11-08 | 2007-11-08 | 配線基板及びその製造方法 |

| KR1020080109006A KR101499974B1 (ko) | 2007-11-08 | 2008-11-04 | 배선기판 및 그의 제조방법 |

| US12/266,193 US8119929B2 (en) | 2007-11-08 | 2008-11-06 | Wiring board and method for manufacturing the same |

| TW097143010A TWI442860B (zh) | 2007-11-08 | 2008-11-07 | 佈線板及其製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007290789A JP5224784B2 (ja) | 2007-11-08 | 2007-11-08 | 配線基板及びその製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013016918A Division JP5386647B2 (ja) | 2013-01-31 | 2013-01-31 | 配線基板 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009117703A JP2009117703A (ja) | 2009-05-28 |

| JP2009117703A5 JP2009117703A5 (ja) | 2010-10-28 |

| JP5224784B2 true JP5224784B2 (ja) | 2013-07-03 |

Family

ID=40640740

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007290789A Active JP5224784B2 (ja) | 2007-11-08 | 2007-11-08 | 配線基板及びその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8119929B2 (ja) |

| JP (1) | JP5224784B2 (ja) |

| KR (1) | KR101499974B1 (ja) |

| TW (1) | TWI442860B (ja) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100704919B1 (ko) * | 2005-10-14 | 2007-04-09 | 삼성전기주식회사 | 코어층이 없는 기판 및 그 제조 방법 |

| US20110084375A1 (en) * | 2009-10-13 | 2011-04-14 | Freescale Semiconductor, Inc | Semiconductor device package with integrated stand-off |

| JP2011138868A (ja) * | 2009-12-28 | 2011-07-14 | Ngk Spark Plug Co Ltd | 多層配線基板 |

| JP2011138869A (ja) * | 2009-12-28 | 2011-07-14 | Ngk Spark Plug Co Ltd | 多層配線基板の製造方法及び多層配線基板 |

| JP5302234B2 (ja) * | 2010-02-08 | 2013-10-02 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2011181542A (ja) | 2010-02-26 | 2011-09-15 | Ngk Spark Plug Co Ltd | 多層配線基板及びその製造方法 |

| US8609995B2 (en) | 2010-07-22 | 2013-12-17 | Ngk Spark Plug Co., Ltd. | Multilayer wiring board and manufacturing method thereof |

| TWI419277B (zh) * | 2010-08-05 | 2013-12-11 | Advanced Semiconductor Eng | 線路基板及其製作方法與封裝結構及其製作方法 |

| WO2012029549A1 (ja) * | 2010-08-30 | 2012-03-08 | 住友ベークライト株式会社 | 半導体パッケージおよび半導体装置 |

| WO2012029579A1 (ja) * | 2010-08-30 | 2012-03-08 | 住友ベークライト株式会社 | 半導体パッケージおよび半導体装置 |

| JPWO2012029526A1 (ja) * | 2010-08-30 | 2013-10-28 | 住友ベークライト株式会社 | 半導体パッケージおよび半導体装置 |

| JP2012069739A (ja) | 2010-09-24 | 2012-04-05 | Shinko Electric Ind Co Ltd | 配線基板の製造方法 |

| CN103270819B (zh) * | 2010-10-20 | 2016-12-07 | Lg伊诺特有限公司 | 印刷电路板及其制造方法 |

| US20130241058A1 (en) * | 2012-03-16 | 2013-09-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Wire Bonding Structures for Integrated Circuits |

| JP2014045025A (ja) * | 2012-08-24 | 2014-03-13 | Sony Corp | 配線基板及び配線基板の製造方法 |

| TWI473552B (zh) * | 2012-11-21 | 2015-02-11 | Unimicron Technology Corp | 具有元件設置區之基板結構及其製程 |

| US9263376B2 (en) * | 2013-04-15 | 2016-02-16 | Intel Deutschland Gmbh | Chip interposer, semiconductor device, and method for manufacturing a semiconductor device |

| US9832860B2 (en) * | 2014-09-26 | 2017-11-28 | Intel Corporation | Panel level fabrication of package substrates with integrated stiffeners |

| KR102359873B1 (ko) * | 2015-06-16 | 2022-02-08 | 삼성전자주식회사 | 패키지 기판 및 이를 포함하는 반도체 패키지 |

| US10177060B2 (en) | 2016-10-21 | 2019-01-08 | Powertech Technology Inc. | Chip package structure and manufacturing method thereof |

| KR20220008097A (ko) * | 2020-07-13 | 2022-01-20 | 삼성전자주식회사 | 반도체 패키지 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1050877A (ja) * | 1996-07-30 | 1998-02-20 | Toshiba Corp | 半導体パッケージ |

| US5900312A (en) * | 1996-11-08 | 1999-05-04 | W. L. Gore & Associates, Inc. | Integrated circuit chip package assembly |

| US5940277A (en) * | 1997-12-31 | 1999-08-17 | Micron Technology, Inc. | Semiconductor device including combed bond pad opening, assemblies and methods |

| US6224711B1 (en) * | 1998-08-25 | 2001-05-01 | International Business Machines Corporation | Assembly process for flip chip package having a low stress chip and resulting structure |

| US6569710B1 (en) * | 1998-12-03 | 2003-05-27 | International Business Machines Corporation | Panel structure with plurality of chip compartments for providing high volume of chip modules |

| JP2000243869A (ja) | 1999-02-18 | 2000-09-08 | Ngk Spark Plug Co Ltd | 配線基板 |

| JP3635219B2 (ja) | 1999-03-11 | 2005-04-06 | 新光電気工業株式会社 | 半導体装置用多層基板及びその製造方法 |

| US6437436B2 (en) * | 2000-01-20 | 2002-08-20 | Ang Technologies Inc. | Integrated circuit chip package with test points |

| US6407334B1 (en) * | 2000-11-30 | 2002-06-18 | International Business Machines Corporation | I/C chip assembly |

| KR100394809B1 (ko) * | 2001-08-09 | 2003-08-14 | 삼성전자주식회사 | 반도체 패키지 및 그 제조 방법 |

| JP4390541B2 (ja) * | 2003-02-03 | 2009-12-24 | Necエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| US20050121757A1 (en) * | 2003-12-04 | 2005-06-09 | Gealer Charles A. | Integrated circuit package overlay |

| US7189929B2 (en) * | 2004-01-16 | 2007-03-13 | Hewlett-Packard Development Company, L.P. | Flexible circuit with cover layer |

| JP4528062B2 (ja) * | 2004-08-25 | 2010-08-18 | 富士通株式会社 | 半導体装置およびその製造方法 |

| US20080099910A1 (en) * | 2006-08-31 | 2008-05-01 | Ati Technologies Inc. | Flip-Chip Semiconductor Package with Encapsulant Retaining Structure and Strip |

-

2007

- 2007-11-08 JP JP2007290789A patent/JP5224784B2/ja active Active

-

2008

- 2008-11-04 KR KR1020080109006A patent/KR101499974B1/ko active IP Right Grant

- 2008-11-06 US US12/266,193 patent/US8119929B2/en active Active

- 2008-11-07 TW TW097143010A patent/TWI442860B/zh active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009117703A (ja) | 2009-05-28 |

| KR101499974B1 (ko) | 2015-03-06 |

| US8119929B2 (en) | 2012-02-21 |

| TWI442860B (zh) | 2014-06-21 |

| TW200934347A (en) | 2009-08-01 |

| KR20090048328A (ko) | 2009-05-13 |

| US20090126981A1 (en) | 2009-05-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5224784B2 (ja) | 配線基板及びその製造方法 | |

| JP4551321B2 (ja) | 電子部品実装構造及びその製造方法 | |

| US8445790B2 (en) | Coreless substrate having filled via pad and method of manufacturing the same | |

| KR100595889B1 (ko) | 상하도전층의 도통부를 갖는 반도체장치 및 그 제조방법 | |

| KR101168263B1 (ko) | 반도체 패키지 및 그 제조 방법 | |

| JP4146864B2 (ja) | 配線基板及びその製造方法、並びに半導体装置及び半導体装置の製造方法 | |

| JP5101169B2 (ja) | 配線基板とその製造方法 | |

| JP5144222B2 (ja) | 配線基板及びその製造方法 | |

| JP5231340B2 (ja) | 配線基板の製造方法 | |

| JP4980295B2 (ja) | 配線基板の製造方法、及び半導体装置の製造方法 | |

| KR20000029352A (ko) | 반도체 장치 및 그 제조 방법 | |

| TW201351514A (zh) | 具有內建加強層之凹穴基板之製造方法 | |

| JP5357239B2 (ja) | 配線基板、半導体装置、及び配線基板の製造方法 | |

| KR20030064635A (ko) | 플립칩형 반도체장치 및 그 제조방법 | |

| US9899235B2 (en) | Fabrication method of packaging substrate | |

| KR20060053087A (ko) | 기판, 반도체 장치, 기판 제조 방법, 및 반도체 장치 제조방법 | |

| US20120126423A1 (en) | Semiconductor device manufacturing method and semiconductor device | |

| JP4955259B2 (ja) | 配線基板、半導体装置、及び配線基板の製造方法 | |

| JP2009111358A (ja) | 配線基板 | |

| JP2009231635A (ja) | 配線基板及びその製造方法、及び半導体装置及びその製造方法 | |

| CN105304580A (zh) | 半导体装置及其制造方法 | |

| JP5386647B2 (ja) | 配線基板 | |

| JP5653144B2 (ja) | 半導体パッケージの製造方法 | |

| JP4549499B2 (ja) | 半導体チップ搭載用基板の製造方法、および半導体チップ搭載用基板と半導体装置 | |

| JP2005191157A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100913 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100913 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110519 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120821 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121012 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20121106 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130131 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20130207 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130226 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130312 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5224784 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160322 Year of fee payment: 3 |