JP5208918B2 - フィンを有する半導体デバイスを形成する方法 - Google Patents

フィンを有する半導体デバイスを形成する方法 Download PDFInfo

- Publication number

- JP5208918B2 JP5208918B2 JP2009507865A JP2009507865A JP5208918B2 JP 5208918 B2 JP5208918 B2 JP 5208918B2 JP 2009507865 A JP2009507865 A JP 2009507865A JP 2009507865 A JP2009507865 A JP 2009507865A JP 5208918 B2 JP5208918 B2 JP 5208918B2

- Authority

- JP

- Japan

- Prior art keywords

- gate

- layer

- forming

- fin

- spacer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

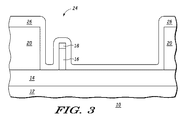

- H10D30/024—Manufacture or treatment of FETs having insulated gates [IGFET] of fin field-effect transistors [FinFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/62—Fin field-effect transistors [FinFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/017—Manufacture or treatment using dummy gates in processes wherein at least parts of the final gates are self-aligned to the dummy gates, i.e. replacement gate processes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/27—Electrodes not carrying the current to be rectified, amplified, oscillated or switched, e.g. gates

- H10D64/311—Gate electrodes for field-effect devices

- H10D64/411—Gate electrodes for field-effect devices for FETs

- H10D64/511—Gate electrodes for field-effect devices for FETs for IGFETs

- H10D64/517—Gate electrodes for field-effect devices for FETs for IGFETs characterised by the conducting layers

Landscapes

- Thin Film Transistor (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/380,530 US7442590B2 (en) | 2006-04-27 | 2006-04-27 | Method for forming a semiconductor device having a fin and structure thereof |

| US11/380,530 | 2006-04-27 | ||

| PCT/US2007/063966 WO2007127533A2 (en) | 2006-04-27 | 2007-03-14 | Method for forming a semiconductor device having a fin and structure thereof |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009535820A JP2009535820A (ja) | 2009-10-01 |

| JP2009535820A5 JP2009535820A5 (enExample) | 2010-04-30 |

| JP5208918B2 true JP5208918B2 (ja) | 2013-06-12 |

Family

ID=38648827

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009507865A Active JP5208918B2 (ja) | 2006-04-27 | 2007-03-14 | フィンを有する半導体デバイスを形成する方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7442590B2 (enExample) |

| JP (1) | JP5208918B2 (enExample) |

| KR (1) | KR20090005066A (enExample) |

| CN (1) | CN101432877B (enExample) |

| TW (1) | TWI404206B (enExample) |

| WO (1) | WO2007127533A2 (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9283273B2 (en) | 1995-07-27 | 2016-03-15 | Genentech, Inc. | Protein formulation |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8202780B2 (en) * | 2009-07-31 | 2012-06-19 | International Business Machines Corporation | Method for manufacturing a FinFET device comprising a mask to define a gate perimeter and another mask to define fin regions |

| JP5569243B2 (ja) * | 2010-08-09 | 2014-08-13 | ソニー株式会社 | 半導体装置及びその製造方法 |

| US8901665B2 (en) * | 2011-12-22 | 2014-12-02 | Taiwan Semiconductor Manufacturing Company, Ltd. | Gate structure for semiconductor device |

| US8987823B2 (en) | 2012-11-07 | 2015-03-24 | International Business Machines Corporation | Method and structure for forming a localized SOI finFET |

| US8766363B2 (en) | 2012-11-07 | 2014-07-01 | International Business Machines Corporation | Method and structure for forming a localized SOI finFET |

| US20140167162A1 (en) * | 2012-12-13 | 2014-06-19 | International Business Machines Corporation | Finfet with merge-free fins |

| US8981496B2 (en) | 2013-02-27 | 2015-03-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | Metal gate and gate contact structure for FinFET |

| US9018054B2 (en) | 2013-03-15 | 2015-04-28 | Applied Materials, Inc. | Metal gate structures for field effect transistors and method of fabrication |

| US8969155B2 (en) | 2013-05-10 | 2015-03-03 | International Business Machines Corporation | Fin structure with varying isolation thickness |

| US9287372B2 (en) * | 2013-12-27 | 2016-03-15 | Taiwan Semiconductor Manufacturing Company Limited | Method of forming trench on FinFET and FinFET thereof |

| US9679985B1 (en) * | 2016-06-20 | 2017-06-13 | Globalfoundries Inc. | Devices and methods of improving device performance through gate cut last process |

| CN109427664B (zh) * | 2017-08-24 | 2021-08-06 | 中芯国际集成电路制造(上海)有限公司 | 半导体结构及其形成方法 |

| US11973143B2 (en) | 2019-03-28 | 2024-04-30 | Intel Corporation | Source or drain structures for germanium N-channel devices |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4044276B2 (ja) * | 2000-09-28 | 2008-02-06 | 株式会社東芝 | 半導体装置及びその製造方法 |

| US6800905B2 (en) * | 2001-12-14 | 2004-10-05 | International Business Machines Corporation | Implanted asymmetric doped polysilicon gate FinFET |

| US6803631B2 (en) * | 2003-01-23 | 2004-10-12 | Advanced Micro Devices, Inc. | Strained channel finfet |

| US6855582B1 (en) * | 2003-06-12 | 2005-02-15 | Advanced Micro Devices, Inc. | FinFET gate formation using reverse trim and oxide polish |

| US6855989B1 (en) * | 2003-10-01 | 2005-02-15 | Advanced Micro Devices, Inc. | Damascene finfet gate with selective metal interdiffusion |

| US6951783B2 (en) | 2003-10-28 | 2005-10-04 | Freescale Semiconductor, Inc. | Confined spacers for double gate transistor semiconductor fabrication process |

| US6936516B1 (en) | 2004-01-12 | 2005-08-30 | Advanced Micro Devices, Inc. | Replacement gate strained silicon finFET process |

| US7041542B2 (en) * | 2004-01-12 | 2006-05-09 | Advanced Micro Devices, Inc. | Damascene tri-gate FinFET |

| JP4796329B2 (ja) * | 2004-05-25 | 2011-10-19 | 三星電子株式会社 | マルチ−ブリッジチャンネル型mosトランジスタの製造方法 |

-

2006

- 2006-04-27 US US11/380,530 patent/US7442590B2/en active Active

-

2007

- 2007-03-14 CN CN200780015277XA patent/CN101432877B/zh active Active

- 2007-03-14 WO PCT/US2007/063966 patent/WO2007127533A2/en not_active Ceased

- 2007-03-14 KR KR1020087026162A patent/KR20090005066A/ko not_active Withdrawn

- 2007-03-14 JP JP2009507865A patent/JP5208918B2/ja active Active

- 2007-03-22 TW TW096109944A patent/TWI404206B/zh active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9283273B2 (en) | 1995-07-27 | 2016-03-15 | Genentech, Inc. | Protein formulation |

Also Published As

| Publication number | Publication date |

|---|---|

| US20070254435A1 (en) | 2007-11-01 |

| CN101432877A (zh) | 2009-05-13 |

| WO2007127533A3 (en) | 2008-06-26 |

| KR20090005066A (ko) | 2009-01-12 |

| CN101432877B (zh) | 2011-09-28 |

| JP2009535820A (ja) | 2009-10-01 |

| TWI404206B (zh) | 2013-08-01 |

| US7442590B2 (en) | 2008-10-28 |

| WO2007127533A2 (en) | 2007-11-08 |

| TW200742070A (en) | 2007-11-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5208918B2 (ja) | フィンを有する半導体デバイスを形成する方法 | |

| CN103050515B (zh) | 晶体管及其制造方法 | |

| CN100448023C (zh) | 具有u字型栅极结构的半导体器件 | |

| CN101490857B (zh) | 形成半导体器件的方法及其结构 | |

| CN103858215B (zh) | 非平坦晶体管以及其制造的方法 | |

| US9859375B2 (en) | Stacked planar double-gate lamellar field-effect transistor | |

| CN100530690C (zh) | 包括多-沟道鳍形场效应晶体管的半导体器件及其制造方法 | |

| JP5409997B2 (ja) | FinFETデバイス中にゲートを形成する方法、および半導体デバイスの製造方法 | |

| US9472407B2 (en) | Replacement metal gate FinFET | |

| US8742508B2 (en) | Three dimensional FET devices having different device widths | |

| US10170634B2 (en) | Wire-last gate-all-around nanowire FET | |

| KR20110121630A (ko) | 나노와이어 메시 디바이스와 그 제조 방법 | |

| US9123654B2 (en) | Trilayer SIT process with transfer layer for FINFET patterning | |

| US8053348B2 (en) | Method of forming a semiconductor device using a sacrificial uniform vertical thickness spacer structure | |

| CN113130311B (zh) | 半导体结构及其形成方法 | |

| US20140084371A1 (en) | Multi-gate field effect transistor devices | |

| CN111668309A (zh) | 具有扩散阻挡间隙件部分的场效应晶体管 | |

| CN111799222A (zh) | 一种用于形成半导体器件的方法 | |

| TWI502649B (zh) | 於共同基底上製造雙閘極與三閘極電晶體的方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100310 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100310 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20120228 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120918 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121217 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130129 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130220 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160301 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5208918 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |