JP5190205B2 - 半導体素子の製造方法 - Google Patents

半導体素子の製造方法 Download PDFInfo

- Publication number

- JP5190205B2 JP5190205B2 JP2007027870A JP2007027870A JP5190205B2 JP 5190205 B2 JP5190205 B2 JP 5190205B2 JP 2007027870 A JP2007027870 A JP 2007027870A JP 2007027870 A JP2007027870 A JP 2007027870A JP 5190205 B2 JP5190205 B2 JP 5190205B2

- Authority

- JP

- Japan

- Prior art keywords

- contact

- film

- contact hole

- contact holes

- axis direction

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 33

- 238000004519 manufacturing process Methods 0.000 title claims description 19

- 239000011229 interlayer Substances 0.000 claims description 26

- 239000010410 layer Substances 0.000 claims description 22

- 239000000758 substrate Substances 0.000 claims description 13

- 238000005530 etching Methods 0.000 claims description 9

- 238000001020 plasma etching Methods 0.000 claims description 6

- 238000011049 filling Methods 0.000 claims description 3

- 238000000034 method Methods 0.000 description 17

- 229910052751 metal Inorganic materials 0.000 description 14

- 239000002184 metal Substances 0.000 description 14

- 230000002093 peripheral effect Effects 0.000 description 11

- 239000007789 gas Substances 0.000 description 9

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 8

- 229920005591 polysilicon Polymers 0.000 description 8

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 7

- 150000002500 ions Chemical class 0.000 description 7

- 238000009792 diffusion process Methods 0.000 description 5

- 238000002955 isolation Methods 0.000 description 4

- 230000002265 prevention Effects 0.000 description 4

- 125000006850 spacer group Chemical group 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- NBVXSUQYWXRMNV-UHFFFAOYSA-N fluoromethane Chemical compound FC NBVXSUQYWXRMNV-UHFFFAOYSA-N 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- 239000012495 reaction gas Substances 0.000 description 2

- 229910001936 tantalum oxide Inorganic materials 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 2

- 229910021342 tungsten silicide Inorganic materials 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 208000032368 Device malfunction Diseases 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 125000001475 halogen functional group Chemical group 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5226—Via connections in a multilevel interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76804—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics by forming tapered via holes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76816—Aspects relating to the layout of the pattern or to the size of vias or trenches

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/09—Manufacture or treatment with simultaneous manufacture of the peripheral circuit region and memory cells

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/318—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor the storage electrode having multiple segments

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Memories (AREA)

Description

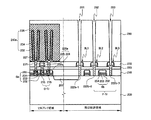

本発明の利点及び特徴、そしてそれらを達成する方法は添付する図面と共に詳細に後述している実施形態を参照すれば明確になる。しかしながら、本発明は、以下で開示される実施形態に限定されるものではなく、相異なる多様な形態で具現されるものであり、本実施形態は、本発明の開示が完全となり、当業者に発明の範疇を完全に知らせるために提供されるものであり、本発明は、特許請求の範囲の記載に基づいて決められなければならない。なお、明細書全体にかけて同一参照符号は同一構成要素を示すものとする。

Claims (5)

- 半導体基板上に下部導電層を形成する段階と、

前記下部導電層を覆う層間絶縁膜を形成する段階と、

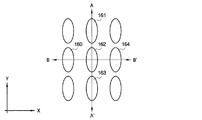

前記層間絶縁膜内に前記下部導電層を露出させ、短軸方向に比べて長軸方向に近接して配列された複数の楕円形コンタクトホールを形成する段階と、

前記コンタクトホールを埋め込んでコンタクトプラグを形成する段階と、

を含み、

前記コンタクトホールを形成する段階は、C x F y 、O 2 及びArの反応ガスを用いるプラズマエッチングを行い、C x H y F z を用いて付加的なエッチングを行うことを特徴とする半導体素子の製造方法。 - 前記コンタクトホールの短軸対長軸比は、0.5:1〜0.95:1に形成することを特徴とする請求項1に記載の半導体素子の製造方法。

- 前記コンタクトホールの縦横比は、10:1〜40:1に形成することを特徴とする請求項1に記載の半導体素子の製造方法。

- 前記コンタクトホールの深さは、1.5μm以上に形成することを特徴とする請求項1に記載の半導体素子の製造方法。

- 前記複数のコンタクトホールの長軸方向における相互の間隔は20nm〜100nmに形成することを特徴とする請求項1に記載の半導体素子の製造方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060011569A KR100809324B1 (ko) | 2006-02-07 | 2006-02-07 | 반도체 소자 및 그 제조 방법 |

| KR10-2006-0011569 | 2006-02-07 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007214567A JP2007214567A (ja) | 2007-08-23 |

| JP2007214567A5 JP2007214567A5 (ja) | 2010-03-25 |

| JP5190205B2 true JP5190205B2 (ja) | 2013-04-24 |

Family

ID=38333213

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007027870A Expired - Fee Related JP5190205B2 (ja) | 2006-02-07 | 2007-02-07 | 半導体素子の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7622759B2 (ja) |

| JP (1) | JP5190205B2 (ja) |

| KR (1) | KR100809324B1 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090302479A1 (en) * | 2008-06-06 | 2009-12-10 | Avago Technologies Wireless Ip (Singapore) Pte. Ltd. | Semiconductor structures having vias |

| KR101094380B1 (ko) * | 2008-12-29 | 2011-12-15 | 주식회사 하이닉스반도체 | 금속콘택을 갖는 반도체장치 제조 방법 |

| JP4945619B2 (ja) * | 2009-09-24 | 2012-06-06 | 株式会社東芝 | 半導体記憶装置 |

| KR101123804B1 (ko) * | 2009-11-20 | 2012-03-12 | 주식회사 하이닉스반도체 | 반도체 칩 및 이를 갖는 적층 반도체 패키지 |

| KR101824735B1 (ko) * | 2010-12-15 | 2018-02-01 | 에스케이하이닉스 주식회사 | 반도체 소자의 제조 방법 |

| TWI447858B (zh) * | 2012-02-03 | 2014-08-01 | Inotera Memories Inc | 隨機存取記憶體的製造方法 |

| US8759977B2 (en) | 2012-04-30 | 2014-06-24 | International Business Machines Corporation | Elongated via structures |

| KR20150109466A (ko) * | 2013-01-24 | 2015-10-01 | 피에스5 뤽스코 에스.에이.알.엘. | 반도체 장치의 제조 방법 |

| JP2015053337A (ja) | 2013-09-05 | 2015-03-19 | マイクロン テクノロジー, インク. | 半導体装置及びその製造方法 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR970000384B1 (ko) | 1994-01-10 | 1997-01-09 | 삼영전자공업 주식회사 | 키틴 및 키토산계 액상복합비료 |

| KR970003848A (ko) * | 1995-06-28 | 1997-01-29 | 김주용 | 반도체 소자의 콘택 제조방법 |

| KR100291414B1 (ko) * | 1998-05-04 | 2001-07-12 | 김영환 | 반도체장치의캐패시터및그제조방법 |

| KR100307528B1 (ko) | 1998-05-28 | 2001-11-02 | 김영환 | 반도체소자의다층배선구조제조방법 |

| KR20010059181A (ko) | 1999-12-30 | 2001-07-06 | 박종섭 | 반도체 소자의 콘택 플러그 형성방법 |

| KR20010095943A (ko) * | 2000-04-14 | 2001-11-07 | 윤종용 | 반도체 장치 |

| JP4223189B2 (ja) * | 2000-12-26 | 2009-02-12 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| JP3976703B2 (ja) | 2003-04-30 | 2007-09-19 | エルピーダメモリ株式会社 | 半導体装置の製造方法 |

| JP2006024831A (ja) * | 2004-07-09 | 2006-01-26 | Sony Corp | 半導体装置および半導体装置の製造方法 |

| JP2007103410A (ja) * | 2005-09-30 | 2007-04-19 | Elpida Memory Inc | 密集コンタクトホールを有する半導体デバイス |

-

2006

- 2006-02-07 KR KR1020060011569A patent/KR100809324B1/ko active IP Right Grant

-

2007

- 2007-02-05 US US11/702,210 patent/US7622759B2/en not_active Expired - Fee Related

- 2007-02-07 JP JP2007027870A patent/JP5190205B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007214567A (ja) | 2007-08-23 |

| KR100809324B1 (ko) | 2008-03-05 |

| US20070182017A1 (en) | 2007-08-09 |

| KR20070080346A (ko) | 2007-08-10 |

| US7622759B2 (en) | 2009-11-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5190205B2 (ja) | 半導体素子の製造方法 | |

| US7579233B2 (en) | Method of fabricating semiconductor device for reducing parasitic capacitance between bit lines and semiconductor device fabricated thereby | |

| JP2007180493A (ja) | 半導体装置の製造方法 | |

| JP2004274025A (ja) | 半導体装置及び半導体装置の製造方法 | |

| US20060284277A1 (en) | Semiconductor device including bit line formed using damascene technique and method of fabricating the same | |

| JP2004128395A (ja) | 半導体装置及び半導体装置の製造方法 | |

| US7560370B2 (en) | Method for manufacturing semiconductor device | |

| US20220223600A1 (en) | Manufacturing method for memory structure | |

| US6074952A (en) | Method for forming multi-level contacts | |

| JP2004128188A (ja) | 半導体装置の製造方法 | |

| US20060118886A1 (en) | Method of forming bit line contact via | |

| US6982199B2 (en) | Bitline of semiconductor device having stud type capping layer and method for fabricating the same | |

| JP2005236135A (ja) | 半導体装置の製造方法 | |

| KR100859831B1 (ko) | 매립형 비트라인을 구비한 반도체 소자의 제조 방법 | |

| JP2005072176A (ja) | 半導体装置とその製造方法 | |

| JP4499679B2 (ja) | 半導体装置及びその製造方法 | |

| KR20030041550A (ko) | 반도체소자의 제조 방법 | |

| US20070010089A1 (en) | Method of forming bit line of semiconductor device | |

| KR100955263B1 (ko) | 반도체 소자의 제조방법 | |

| KR100582354B1 (ko) | 반도체 소자의 도전패턴 및 그 형성 방법 | |

| TW202320065A (zh) | 半導體記憶體裝置 | |

| KR20050002075A (ko) | 반도체소자 제조 방법 | |

| JP2012256950A (ja) | 半導体装置及び半導体装置の製造方法 | |

| CN113555323A (zh) | 动态随机存取存储器及其制作方法 | |

| KR20080060598A (ko) | 반도체 소자의 비트 라인 형성방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100204 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100204 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110128 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120824 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20121126 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20121129 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121221 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130115 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130128 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160201 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5190205 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |