JP5165306B2 - 多孔質低k誘電体層内に特徴を形成するための装置 - Google Patents

多孔質低k誘電体層内に特徴を形成するための装置 Download PDFInfo

- Publication number

- JP5165306B2 JP5165306B2 JP2007213685A JP2007213685A JP5165306B2 JP 5165306 B2 JP5165306 B2 JP 5165306B2 JP 2007213685 A JP2007213685 A JP 2007213685A JP 2007213685 A JP2007213685 A JP 2007213685A JP 5165306 B2 JP5165306 B2 JP 5165306B2

- Authority

- JP

- Japan

- Prior art keywords

- computer readable

- readable code

- processing chamber

- plasma processing

- containing gas

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000005530 etching Methods 0.000 claims description 33

- 238000012545 processing Methods 0.000 claims description 29

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 claims description 17

- 229910052731 fluorine Inorganic materials 0.000 claims description 17

- 239000011737 fluorine Substances 0.000 claims description 17

- 239000000758 substrate Substances 0.000 claims description 13

- 239000010410 layer Substances 0.000 description 56

- 239000007789 gas Substances 0.000 description 47

- 229920002120 photoresistant polymer Polymers 0.000 description 20

- 238000000034 method Methods 0.000 description 16

- 239000000463 material Substances 0.000 description 10

- 230000008569 process Effects 0.000 description 9

- 230000004888 barrier function Effects 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 230000009977 dual effect Effects 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 239000012044 organic layer Substances 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- 241000699666 Mus <mouse, genus> Species 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 238000006467 substitution reaction Methods 0.000 description 2

- 241000699670 Mus sp. Species 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 230000003667 anti-reflective effect Effects 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- NBVXSUQYWXRMNV-UHFFFAOYSA-N fluoromethane Chemical compound FC NBVXSUQYWXRMNV-UHFFFAOYSA-N 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 230000001902 propagating effect Effects 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76807—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures

- H01L21/76808—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures involving intermediate temporary filling with material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Drying Of Semiconductors (AREA)

Description

Claims (1)

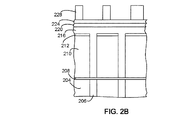

- 誘電体層内にトレンチを形成するための装置であって、前記誘電体層内には、ビアが形成され、前記誘電体層の上には、前記ビアを満たすと共に平坦化表面を形成するために有機平坦化層が形成され、前記平坦表面の上には、酸化物キャップ、BARC、およびトレンチマスクが形成されており、前記装置は、

プラズマ処理チャンバであって、

プラズマ処理チャンバエンクロージャを形成するチャンバ壁と、

前記プラズマ処理チャンバエンクロージャ内で基板を支えるための基板サポートと、

前記プラズマ処理チャンバエンクロージャ内の圧力を調整するための圧力レギュレータと、

プラズマを維持するために前記プラズマ処理チャンバエンクロージャに電力を提供するための少なくとも1つの電極と、

前記プラズマ処理チャンバエンクロージャにガスを提供するためのガス注入口と、

前記プラズマ処理チャンバエンクロージャからガスを排出させるためのガス排出口と、を含むプラズマ処理チャンバと、

CO2 ガス源とフッ素含有ガス源とを含み、前記ガス注入口に流体接続されたガス源と、

前記ガス源および前記少なくとも1つの電極に可制御式に接続されたコントローラであって、少なくとも1つのプロセッサおよびコンピュータ可読媒体を含むコントローラと、

を備え、

前記コンピュータ可読媒体は、

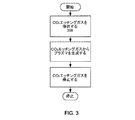

前記BARCおよび前記酸化物キャップ層をエッチングするためのコンピュータ可読コードであって、

前記フッ素含有ガス源から前記プラズマ処理チャンバの内部へとフッ素含有ガスを提供するためのコンピュータ可読コードと、

前記フッ素含有ガスをプラズマに変換するためのコンピュータ可読コードと、

前記フッ素含有ガスを停止するためのコンピュータ可読コードと

を含むコンピュータ可読コードと、

前記有機平坦化層をエッチングするためのコンピュータ可読コードであって、

前記CO2 ガス源からCO2 含有ガスを提供するためのコンピュータ可読コードと、

前記CO2 含有ガスからプラズマを形成するためのコンピュータ可読コードと、

前記CO2 含有ガスを停止するためのコンピュータ可読コードと

を含む、コンピュータ可読コードと、

前記有機平坦化層を通して前記誘電体層内にトレンチをエッチングし、該トレンチのエッチングの後に、前記ビア内に前記有機平坦化層が残存するように前記トレンチをエッチングするためのコンピュータ可読コードであって、

前記フッ素含有ガス源から前記プラズマ処理チャンバの内部へとフッ素含有ガスを提供するためのコンピュータ可読コードと、

前記フッ素含有ガスをプラズマに変換するためのコンピュータ可読コードと

を含むコンピュータ可読コードと、

前記有機平坦化層を剥ぎ取るためのコンピュータ可読コードであって、前記CO2 ガス源から前記プラズマ処理チャンバの内部へと前記CO2 含有ガスを提供し、前記ビア内に残存していた前記有機平坦化層を剥ぎ取るためのコンピュータ可読コードと

を含む装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/507,862 US8124516B2 (en) | 2006-08-21 | 2006-08-21 | Trilayer resist organic layer etch |

| US11/507,862 | 2006-08-21 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008060565A JP2008060565A (ja) | 2008-03-13 |

| JP2008060565A5 JP2008060565A5 (ja) | 2010-10-07 |

| JP5165306B2 true JP5165306B2 (ja) | 2013-03-21 |

Family

ID=39101865

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007213685A Expired - Fee Related JP5165306B2 (ja) | 2006-08-21 | 2007-08-20 | 多孔質低k誘電体層内に特徴を形成するための装置 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US8124516B2 (ja) |

| JP (1) | JP5165306B2 (ja) |

| KR (1) | KR101392570B1 (ja) |

| CN (1) | CN101131928B (ja) |

| MY (1) | MY150187A (ja) |

| SG (1) | SG140537A1 (ja) |

| TW (1) | TWI427696B (ja) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8193096B2 (en) | 2004-12-13 | 2012-06-05 | Novellus Systems, Inc. | High dose implantation strip (HDIS) in H2 base chemistry |

| US7595005B2 (en) * | 2006-12-11 | 2009-09-29 | Tokyo Electron Limited | Method and apparatus for ashing a substrate using carbon dioxide |

| US8435895B2 (en) | 2007-04-04 | 2013-05-07 | Novellus Systems, Inc. | Methods for stripping photoresist and/or cleaning metal regions |

| US8003488B2 (en) * | 2007-09-26 | 2011-08-23 | International Business Machines Corporation | Shallow trench isolation structure compatible with SOI embedded DRAM |

| JP5710267B2 (ja) | 2007-12-21 | 2015-04-30 | ラム リサーチ コーポレーションLam Research Corporation | シリコン構造体の製造及びプロファイル制御を伴うシリコンディープエッチング |

| KR101791685B1 (ko) * | 2008-10-14 | 2017-11-20 | 노벨러스 시스템즈, 인코포레이티드 | 수소 이용 화학 반응으로 고용량 주입 스트립(hdis) 방법 및 장치 |

| US8173547B2 (en) * | 2008-10-23 | 2012-05-08 | Lam Research Corporation | Silicon etch with passivation using plasma enhanced oxidation |

| US8394722B2 (en) * | 2008-11-03 | 2013-03-12 | Lam Research Corporation | Bi-layer, tri-layer mask CD control |

| CN101958277B (zh) * | 2009-07-16 | 2013-01-23 | 中芯国际集成电路制造(上海)有限公司 | 金属布线沟槽的形成方法 |

| US7637269B1 (en) | 2009-07-29 | 2009-12-29 | Tokyo Electron Limited | Low damage method for ashing a substrate using CO2/CO-based process |

| JP5532826B2 (ja) * | 2009-11-04 | 2014-06-25 | 富士通セミコンダクター株式会社 | 半導体素子の製造方法 |

| CN102652351B (zh) | 2009-12-11 | 2016-10-05 | 诺发系统有限公司 | 在高剂量植入剥除前保护硅的增强式钝化工艺 |

| US20110143548A1 (en) * | 2009-12-11 | 2011-06-16 | David Cheung | Ultra low silicon loss high dose implant strip |

| CN102208333A (zh) * | 2011-05-27 | 2011-10-05 | 中微半导体设备(上海)有限公司 | 等离子体刻蚀方法 |

| US9613825B2 (en) | 2011-08-26 | 2017-04-04 | Novellus Systems, Inc. | Photoresist strip processes for improved device integrity |

| CN102364670B (zh) * | 2011-09-15 | 2013-06-12 | 上海华力微电子有限公司 | 金属铜大马士革互联结构的制造方法 |

| US9666414B2 (en) | 2011-10-27 | 2017-05-30 | Applied Materials, Inc. | Process chamber for etching low k and other dielectric films |

| CN103227108B (zh) * | 2012-01-31 | 2016-01-06 | 中微半导体设备(上海)有限公司 | 一种有机物层刻蚀方法 |

| CN102915959B (zh) * | 2012-10-08 | 2015-06-17 | 上海华力微电子有限公司 | 一种简化存储器中字线介电质膜刻蚀成型工艺的方法 |

| US9385000B2 (en) * | 2014-01-24 | 2016-07-05 | United Microelectronics Corp. | Method of performing etching process |

| US9514954B2 (en) | 2014-06-10 | 2016-12-06 | Lam Research Corporation | Peroxide-vapor treatment for enhancing photoresist-strip performance and modifying organic films |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4376672A (en) | 1981-10-26 | 1983-03-15 | Applied Materials, Inc. | Materials and methods for plasma etching of oxides and nitrides of silicon |

| US4484979A (en) | 1984-04-16 | 1984-11-27 | At&T Bell Laboratories | Two-step anisotropic etching process for patterning a layer without penetrating through an underlying thinner layer |

| US4659426A (en) | 1985-05-03 | 1987-04-21 | Texas Instruments Incorporated | Plasma etching of refractory metals and their silicides |

| US4772488A (en) * | 1987-03-23 | 1988-09-20 | General Electric Company | Organic binder removal using CO2 plasma |

| US4791073A (en) | 1987-11-17 | 1988-12-13 | Motorola Inc. | Trench isolation method for semiconductor devices |

| US4923828A (en) | 1989-07-07 | 1990-05-08 | Eastman Kodak Company | Gaseous cleaning method for silicon devices |

| US5756256A (en) * | 1992-06-05 | 1998-05-26 | Sharp Microelectronics Technology, Inc. | Silylated photo-resist layer and planarizing method |

| US5874201A (en) | 1995-06-05 | 1999-02-23 | International Business Machines Corporation | Dual damascene process having tapered vias |

| US6037266A (en) * | 1998-09-28 | 2000-03-14 | Taiwan Semiconductor Manufacturing Company | Method for patterning a polysilicon gate with a thin gate oxide in a polysilicon etcher |

| US6258732B1 (en) * | 1999-02-04 | 2001-07-10 | International Business Machines Corporation | Method of forming a patterned organic dielectric layer on a substrate |

| JP3803528B2 (ja) * | 2000-03-31 | 2006-08-02 | 株式会社東芝 | 半導体装置の製造方法及び半導体装置 |

| US6794293B2 (en) * | 2001-10-05 | 2004-09-21 | Lam Research Corporation | Trench etch process for low-k dielectrics |

| US7109119B2 (en) * | 2002-10-31 | 2006-09-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Scum solution for chemically amplified resist patterning in cu/low k dual damascene |

| US6995087B2 (en) | 2002-12-23 | 2006-02-07 | Chartered Semiconductor Manufacturing Ltd. | Integrated circuit with simultaneous fabrication of dual damascene via and trench |

| US6914007B2 (en) * | 2003-02-13 | 2005-07-05 | Taiwan Semiconductor Manufacturing Company, Ltd. | In-situ discharge to avoid arcing during plasma etch processes |

| JP2004253659A (ja) | 2003-02-20 | 2004-09-09 | Renesas Technology Corp | 半導体装置の製造方法 |

| KR100483838B1 (ko) | 2003-02-28 | 2005-04-15 | 삼성전자주식회사 | 금속배선의 듀얼 다마신 방법 |

| JP4681217B2 (ja) * | 2003-08-28 | 2011-05-11 | 株式会社アルバック | 層間絶縁膜のドライエッチング方法 |

| JP2005079192A (ja) * | 2003-08-28 | 2005-03-24 | Ulvac Japan Ltd | 有機膜のドライエッチング方法 |

| CN1282237C (zh) * | 2003-08-29 | 2006-10-25 | 华邦电子股份有限公司 | 双镶嵌式开口结构的制作方法 |

| JP4651956B2 (ja) * | 2004-03-03 | 2011-03-16 | 株式会社アルバック | 層間絶縁膜のドライエッチング方法 |

| US7396769B2 (en) * | 2004-08-02 | 2008-07-08 | Lam Research Corporation | Method for stripping photoresist from etched wafer |

| JP2006128543A (ja) * | 2004-11-01 | 2006-05-18 | Nec Electronics Corp | 電子デバイスの製造方法 |

| US7651942B2 (en) * | 2005-08-15 | 2010-01-26 | Infineon Technologies Ag | Metal interconnect structure and method |

| US20070134917A1 (en) * | 2005-12-13 | 2007-06-14 | Taiwan Semiconductor Manufacturing Co., Ltd. | Partial-via-first dual-damascene process with tri-layer resist approach |

| JP4940722B2 (ja) * | 2006-03-24 | 2012-05-30 | 東京エレクトロン株式会社 | 半導体装置の製造方法及びプラズマ処理装置並びに記憶媒体 |

| US7695897B2 (en) * | 2006-05-08 | 2010-04-13 | International Business Machines Corporation | Structures and methods for low-k or ultra low-k interlayer dielectric pattern transfer |

-

2006

- 2006-08-21 US US11/507,862 patent/US8124516B2/en active Active

-

2007

- 2007-08-07 SG SG200705770-6A patent/SG140537A1/en unknown

- 2007-08-07 MY MYPI20071311A patent/MY150187A/en unknown

- 2007-08-08 TW TW096129260A patent/TWI427696B/zh not_active IP Right Cessation

- 2007-08-20 JP JP2007213685A patent/JP5165306B2/ja not_active Expired - Fee Related

- 2007-08-20 CN CN2007101426514A patent/CN101131928B/zh active Active

- 2007-08-21 KR KR1020070084189A patent/KR101392570B1/ko active IP Right Grant

Also Published As

| Publication number | Publication date |

|---|---|

| KR20080017287A (ko) | 2008-02-26 |

| TWI427696B (zh) | 2014-02-21 |

| SG140537A1 (en) | 2008-03-28 |

| CN101131928B (zh) | 2011-11-02 |

| TW200830405A (en) | 2008-07-16 |

| US8124516B2 (en) | 2012-02-28 |

| MY150187A (en) | 2013-12-13 |

| US20080044995A1 (en) | 2008-02-21 |

| KR101392570B1 (ko) | 2014-05-08 |

| CN101131928A (zh) | 2008-02-27 |

| JP2008060565A (ja) | 2008-03-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5165306B2 (ja) | 多孔質低k誘電体層内に特徴を形成するための装置 | |

| KR101094681B1 (ko) | 레지스트 박리 동안 다공성 로우-k 재료의 손상을방지하는 방법 | |

| JP5081917B2 (ja) | フッ素除去プロセス | |

| KR101209535B1 (ko) | 에칭 프로파일 제어 | |

| US7491647B2 (en) | Etch with striation control | |

| KR101083622B1 (ko) | 피쳐 임계 치수의 감소 | |

| JP5048055B2 (ja) | エッチング層内に特徴を設けるための方法 | |

| KR101442269B1 (ko) | 무한 선택적 포토레지스트 마스크 식각 | |

| KR101711669B1 (ko) | 측벽 형성 공정 | |

| KR101144022B1 (ko) | 에칭된 웨이퍼로부터 포토레지스트 스트립 방법 | |

| JP2008524851A (ja) | エッチマスクの特徴部の限界寸法の低減 | |

| TWI467651B (zh) | 活性硬遮罩電漿蝕刻時之現場光阻剝除 | |

| TWI393997B (zh) | 用於蝕刻基板上之低k介電層的方法、半導體裝置以及用於在低k介電層中形成特徵的設備 | |

| US8470715B2 (en) | CD bias loading control with ARC layer open | |

| KR101155843B1 (ko) | 균일성 제어에 의한 에칭 | |

| US20070181530A1 (en) | Reducing line edge roughness | |

| KR20070046095A (ko) | 유전층 에칭 방법 | |

| TW200805494A (en) | Mask profile control for controlling feature profile |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100819 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100819 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111124 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111129 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120228 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120302 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120528 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120619 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121017 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20121017 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20121108 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121127 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121219 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151228 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5165306 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |