JP5038148B2 - 巡回冗長検査を実行するためのシステム及び方法 - Google Patents

巡回冗長検査を実行するためのシステム及び方法 Download PDFInfo

- Publication number

- JP5038148B2 JP5038148B2 JP2007543424A JP2007543424A JP5038148B2 JP 5038148 B2 JP5038148 B2 JP 5038148B2 JP 2007543424 A JP2007543424 A JP 2007543424A JP 2007543424 A JP2007543424 A JP 2007543424A JP 5038148 B2 JP5038148 B2 JP 5038148B2

- Authority

- JP

- Japan

- Prior art keywords

- crc

- data

- mddi

- packet

- link

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/04—Speed or phase control by synchronisation signals

- H04L7/10—Arrangements for initial synchronisation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B7/00—Radio transmission systems, i.e. using radiation field

- H04B7/24—Radio transmission systems, i.e. using radiation field for communication between two or more posts

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/003—Details of a display terminal, the details relating to the control arrangement of the display terminal and to the interfaces thereto

- G09G5/006—Details of the interface to the display terminal

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/04—Speed or phase control by synchronisation signals

- H04L7/048—Speed or phase control by synchronisation signals using the properties of error detecting or error correcting codes, e.g. parity as synchronisation signal

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2370/00—Aspects of data communication

- G09G2370/04—Exchange of auxiliary data, i.e. other than image data, between monitor and graphics controller

- G09G2370/045—Exchange of auxiliary data, i.e. other than image data, between monitor and graphics controller using multiple communication channels, e.g. parallel and serial

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2370/00—Aspects of data communication

- G09G2370/10—Use of a protocol of communication by packets in interfaces along the display data pipeline

Description

本発明の典型的な実施形態が示された。本発明は、これらの例に限定されない。これらの例は、本明細書において、例示目的で表されており、限定のために表されているのではない。本明細書に含まれる教示に基づいて、代替例(本明細書の記載の等価物、拡張、変形、変更等)が、関連技術における熟練者に明らかになるであろう。そのような代替例は、本発明の範囲及び精神内にある。

Claims (4)

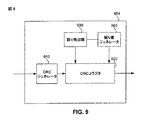

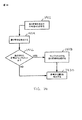

- 巡回冗長検査(CRC)チェッカであって、

デジタル送信リンクによって受信したデータストリーム内のユニークパターンを検出するユニークパターン検出器と、

前記受信したデータストリームに基づいてCRC値を生成するCRCジェネレータと、

リンクが初期化されると、前記CRCジェネレータに、前記ユニークパターンに関連するCRC値を事前入力するCRCイニシャライザと、

受信したデータストリームに基づいて生成されたCRC値の、前記受信したデータストリーム内で送られたCRC値に対する相違を検出するCRCベリファイヤと

を備えるCRCチェッカ。 - 前記CRCイニシャライザは、前記CRCベリファイヤに、前記ユニークパターンに関連するCRC値を事前入力する請求項1のCRCチェッカ。

- 前記デジタル送信リンクはMDDI送信リンクである請求項1のCRCチェッカ。

- 前記ユニークパターンは、パケット長フィールド、パケットタイプフィールド、及びユニークワードフィールドをサブフレームヘッダパケット内に含む請求項1のCRCチェッカ。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US63085304P | 2004-11-24 | 2004-11-24 | |

| US60/630,853 | 2004-11-24 | ||

| US63282504P | 2004-12-02 | 2004-12-02 | |

| US60/632,825 | 2004-12-02 | ||

| PCT/US2005/042412 WO2006058050A2 (en) | 2004-11-24 | 2005-11-23 | Systems and methods for implementing cyclic redundancy checks |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010253017A Division JP5226758B2 (ja) | 2004-11-24 | 2010-11-11 | 巡回冗長検査を実行するためのシステム及び方法 |

| JP2011128441A Division JP2011250419A (ja) | 2004-11-24 | 2011-06-08 | 巡回冗長検査を実行するためのシステム及び方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008522494A JP2008522494A (ja) | 2008-06-26 |

| JP5038148B2 true JP5038148B2 (ja) | 2012-10-03 |

Family

ID=36498487

Family Applications (8)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007543424A Expired - Fee Related JP5038148B2 (ja) | 2004-11-24 | 2005-11-23 | 巡回冗長検査を実行するためのシステム及び方法 |

| JP2007543436A Expired - Fee Related JP4750799B2 (ja) | 2004-11-24 | 2005-11-23 | デジタルデータ送信レート制御のためのシステム及び方法 |

| JP2007543500A Expired - Fee Related JP5048510B2 (ja) | 2004-11-24 | 2005-11-23 | デジタルデータインタフェースデバイスメッセージフォーマット |

| JP2007543422A Pending JP2008522493A (ja) | 2004-11-24 | 2005-11-23 | デジタルデータインタフェースデバイス |

| JP2010253017A Expired - Fee Related JP5226758B2 (ja) | 2004-11-24 | 2010-11-11 | 巡回冗長検査を実行するためのシステム及び方法 |

| JP2011128441A Pending JP2011250419A (ja) | 2004-11-24 | 2011-06-08 | 巡回冗長検査を実行するためのシステム及び方法 |

| JP2011171755A Expired - Fee Related JP5356469B2 (ja) | 2004-11-24 | 2011-08-05 | デジタルデータインタフェースデバイス |

| JP2012250168A Pending JP2013081190A (ja) | 2004-11-24 | 2012-11-14 | 巡回冗長検査を実行するためのシステム及び方法 |

Family Applications After (7)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007543436A Expired - Fee Related JP4750799B2 (ja) | 2004-11-24 | 2005-11-23 | デジタルデータ送信レート制御のためのシステム及び方法 |

| JP2007543500A Expired - Fee Related JP5048510B2 (ja) | 2004-11-24 | 2005-11-23 | デジタルデータインタフェースデバイスメッセージフォーマット |

| JP2007543422A Pending JP2008522493A (ja) | 2004-11-24 | 2005-11-23 | デジタルデータインタフェースデバイス |

| JP2010253017A Expired - Fee Related JP5226758B2 (ja) | 2004-11-24 | 2010-11-11 | 巡回冗長検査を実行するためのシステム及び方法 |

| JP2011128441A Pending JP2011250419A (ja) | 2004-11-24 | 2011-06-08 | 巡回冗長検査を実行するためのシステム及び方法 |

| JP2011171755A Expired - Fee Related JP5356469B2 (ja) | 2004-11-24 | 2011-08-05 | デジタルデータインタフェースデバイス |

| JP2012250168A Pending JP2013081190A (ja) | 2004-11-24 | 2012-11-14 | 巡回冗長検査を実行するためのシステム及び方法 |

Country Status (11)

| Country | Link |

|---|---|

| EP (5) | EP2317688A3 (ja) |

| JP (8) | JP5038148B2 (ja) |

| KR (4) | KR100923170B1 (ja) |

| CN (2) | CN101931503B (ja) |

| AU (2) | AU2005309680C1 (ja) |

| BR (1) | BRPI0518264A2 (ja) |

| CA (7) | CA2588714C (ja) |

| ES (1) | ES2395434T3 (ja) |

| IL (4) | IL183409A0 (ja) |

| SG (1) | SG160337A1 (ja) |

| WO (4) | WO2006058067A2 (ja) |

Families Citing this family (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6760772B2 (en) | 2000-12-15 | 2004-07-06 | Qualcomm, Inc. | Generating and implementing a communication protocol and interface for high data rate signal transfer |

| US8812706B1 (en) | 2001-09-06 | 2014-08-19 | Qualcomm Incorporated | Method and apparatus for compensating for mismatched delays in signals of a mobile display interface (MDDI) system |

| ATE509459T1 (de) | 2003-06-02 | 2011-05-15 | Qualcomm Inc | Erzeugung und umsetzung eines signalprotokolls und schnittstelle für höhere datenraten |

| KR101178080B1 (ko) | 2003-08-13 | 2012-08-30 | 퀄컴 인코포레이티드 | 더 높은 데이터 레이트를 위한 신호 인터페이스 |

| CN101764804A (zh) | 2003-09-10 | 2010-06-30 | 高通股份有限公司 | 高数据速率接口 |

| EP2244437B1 (en) | 2003-10-15 | 2013-09-04 | Qualcomm Incorporated | High data rate interface |

| RU2331160C2 (ru) | 2003-10-29 | 2008-08-10 | Квэлкомм Инкорпорейтед | Интерфейс с высокой скоростью передачи данных |

| KR20060108709A (ko) | 2003-11-12 | 2006-10-18 | 콸콤 인코포레이티드 | 향상된 링크 제어를 제공하는 고속 데이터 레이트인터페이스 |

| RU2006122542A (ru) | 2003-11-25 | 2008-01-10 | Квэлкомм Инкорпорейтед (US) | Интерфейс с высокой скоростью передачи данных с улучшенной синхронизацией линии связи |

| EP2247070B1 (en) | 2003-12-08 | 2013-09-25 | QUALCOMM Incorporated | High data rate interface with improved link synchronization |

| CA2775734C (en) | 2004-03-10 | 2014-01-07 | Qualcomm Incorporated | High data rate interface apparatus and method |

| CA2560067C (en) | 2004-03-17 | 2011-08-23 | Qualcomm Incorporated | High data rate interface apparatus and method |

| CN1993948A (zh) | 2004-06-04 | 2007-07-04 | 高通股份有限公司 | 高数据速率接口设备和方法 |

| US8650304B2 (en) | 2004-06-04 | 2014-02-11 | Qualcomm Incorporated | Determining a pre skew and post skew calibration data rate in a mobile display digital interface (MDDI) communication system |

| US8723705B2 (en) | 2004-11-24 | 2014-05-13 | Qualcomm Incorporated | Low output skew double data rate serial encoder |

| US8667363B2 (en) | 2004-11-24 | 2014-03-04 | Qualcomm Incorporated | Systems and methods for implementing cyclic redundancy checks |

| US8692838B2 (en) | 2004-11-24 | 2014-04-08 | Qualcomm Incorporated | Methods and systems for updating a buffer |

| ES2395434T3 (es) * | 2004-11-24 | 2013-02-12 | Qualcomm, Incorporated | Sistemas y procedimientos para el control de la tasa de transmisión de datos digitales |

| US8873584B2 (en) | 2004-11-24 | 2014-10-28 | Qualcomm Incorporated | Digital data interface device |

| US8699330B2 (en) | 2004-11-24 | 2014-04-15 | Qualcomm Incorporated | Systems and methods for digital data transmission rate control |

| US8539119B2 (en) | 2004-11-24 | 2013-09-17 | Qualcomm Incorporated | Methods and apparatus for exchanging messages having a digital data interface device message format |

| US8730069B2 (en) | 2005-11-23 | 2014-05-20 | Qualcomm Incorporated | Double data rate serial encoder |

| US8692839B2 (en) | 2005-11-23 | 2014-04-08 | Qualcomm Incorporated | Methods and systems for updating a buffer |

| CN102387485B (zh) | 2007-04-27 | 2015-07-29 | 华为技术有限公司 | 发送控制信令的方法和装置 |

| DE102007028767B4 (de) | 2007-06-22 | 2016-01-28 | Continental Teves Ag & Co. Ohg | Buskommunikationsschaltung zur sicheren seriellen Übertragung von Daten sowie deren Verwendung |

| DE102007028766A1 (de) | 2007-06-22 | 2008-12-24 | Continental Teves Ag & Co. Ohg | Prüfverfahren und elektronische Schaltung zur sicheren seriellen Übertragung von Daten |

| KR100898542B1 (ko) * | 2008-02-28 | 2009-05-20 | 주식회사 유비콘테크놀로지 | 무선 usb 시스템의 패킷구조 |

| US8223796B2 (en) * | 2008-06-18 | 2012-07-17 | Ati Technologies Ulc | Graphics multi-media IC and method of its operation |

| CN102460564B (zh) * | 2009-06-30 | 2015-02-11 | 诺基亚公司 | 用于提供移动设备互操作性的方法及装置 |

| US8812140B2 (en) | 2011-05-16 | 2014-08-19 | Jogtek Corp. | Signal transforming method, transforming device through audio interface and application program for executing the same |

| DE102013020522A1 (de) | 2013-12-11 | 2015-06-11 | Lukusa Didier Kabulepa | Kommunikationssystem, Testeinrichtung und Vorrichtung zur Prüfung von fehlererkennenden Sicherheitsmechanismen eines Kommunikationsteilnehmers |

| US9996439B2 (en) * | 2015-09-23 | 2018-06-12 | Qualcomm Incorporated | Self-error injection technique for point-to-point interconnect to increase test coverage |

| US11044183B2 (en) * | 2015-12-29 | 2021-06-22 | Xilinx, Inc. | Network interface device |

| US11165683B2 (en) | 2015-12-29 | 2021-11-02 | Xilinx, Inc. | Network interface device |

| CN109308058B (zh) * | 2018-10-25 | 2021-07-06 | 深圳丹弗科技有限公司 | 成功率改进的基于物联网的智能车床控制方法及系统 |

| DE102019218715A1 (de) | 2019-12-02 | 2021-06-02 | Robert Bosch Gmbh | Teilnehmerstation für ein serielles Bussystem und Verfahren zur Kommunikation in einem seriellen Bussystem |

| CN112612638A (zh) * | 2020-12-29 | 2021-04-06 | 芯启源电子科技有限公司 | 基于usb3.2协议16比特循环冗余校验的硬件实现方法 |

Family Cites Families (54)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4042783A (en) * | 1976-08-11 | 1977-08-16 | International Business Machines Corporation | Method and apparatus for byte and frame synchronization on a loop system coupling a CPU channel to bulk storage devices |

| JPS6013538B2 (ja) * | 1977-04-22 | 1985-04-08 | 日本電気株式会社 | 可変演算方式 |

| US4720831A (en) * | 1985-12-02 | 1988-01-19 | Advanced Micro Devices, Inc. | CRC calculation machine with concurrent preset and CRC calculation function |

| JPH04167715A (ja) * | 1990-10-31 | 1992-06-15 | Nec Corp | 多重処理型crc符号生成回路 |

| JP3007926B2 (ja) * | 1990-11-15 | 2000-02-14 | オムロン株式会社 | データキャリア及び識別システム |

| US5258999A (en) * | 1991-10-03 | 1993-11-02 | Motorola, Inc. | Circuit and method for receiving and transmitting control and status information |

| US5867501A (en) * | 1992-12-17 | 1999-02-02 | Tandem Computers Incorporated | Encoding for communicating data and commands |

| JP3467324B2 (ja) * | 1994-07-26 | 2003-11-17 | 富士通株式会社 | 簡易型携帯電話システムにおける送・受信制御方式 |

| DE19539343C2 (de) * | 1995-10-23 | 1997-12-11 | Siemens Ag | Verfahren zur Fehlererkennung eines digitalen Bitdatenstroms, der von einem Sender zu einem Empfänger übertragen wird |

| EP0781068A1 (en) * | 1995-12-20 | 1997-06-25 | International Business Machines Corporation | Method and system for adaptive bandwidth allocation in a high speed data network |

| JPH09261232A (ja) * | 1996-03-19 | 1997-10-03 | Fujitsu Ltd | Atm交換機における複数応答通信制御方法 |

| US5862160A (en) * | 1996-12-31 | 1999-01-19 | Ericsson, Inc. | Secondary channel for communication networks |

| JP3390618B2 (ja) * | 1997-01-13 | 2003-03-24 | 三菱電機株式会社 | 基地局決定装置 |

| JPH10234038A (ja) * | 1997-02-21 | 1998-09-02 | Hitachi Ltd | データ処理装置、データ形式変換装置、データ通信方法及びデータ処理システム |

| US6631402B1 (en) * | 1997-09-26 | 2003-10-07 | Worldcom, Inc. | Integrated proxy interface for web based report requester tool set |

| JPH11122234A (ja) * | 1997-10-16 | 1999-04-30 | Nec Ic Microcomput Syst Ltd | 受信データ処理回路 |

| JPH11225372A (ja) * | 1998-02-05 | 1999-08-17 | Sanyo Electric Co Ltd | 時刻調整方法及びその装置 |

| US6833863B1 (en) * | 1998-02-06 | 2004-12-21 | Intel Corporation | Method and apparatus for still image capture during video streaming operations of a tethered digital camera |

| US6850282B1 (en) * | 1998-06-02 | 2005-02-01 | Canon Kabushiki Kaisha | Remote control of image sensing apparatus |

| KR100350607B1 (ko) * | 1999-03-31 | 2002-08-28 | 삼성전자 주식회사 | 음성 및 화상 송수신을 위한 휴대용 복합 통신단말기 및 그 동작방법과 통신시스템 |

| JP2001025010A (ja) * | 1999-07-09 | 2001-01-26 | Mitsubishi Electric Corp | マルチメディア情報通信装置およびその方法 |

| JP2001044960A (ja) * | 1999-07-28 | 2001-02-16 | Toyo Commun Equip Co Ltd | 時分割方向制御インタフェースにおけるエラー試験装置 |

| US6804257B1 (en) * | 1999-11-25 | 2004-10-12 | International Business Machines Corporation | System and method for framing and protecting variable-lenght packet streams |

| JP4191869B2 (ja) * | 1999-12-20 | 2008-12-03 | 富士フイルム株式会社 | ディジタルカメラを用いたコンピュータシステム |

| JP2001282714A (ja) * | 2000-03-30 | 2001-10-12 | Olympus Optical Co Ltd | マルチカメラデータ転送方式及びデータ転送方式 |

| JP2001319745A (ja) * | 2000-05-08 | 2001-11-16 | Honda Tsushin Kogyo Co Ltd | 変換用アダプタ |

| JP4292685B2 (ja) * | 2000-05-23 | 2009-07-08 | 日本電気株式会社 | データ転送システム、データ送受信システム、データ送受信方法、フォーマット変換装置、フォーマット変換方法およびフォーマット変換プログラムを記録したコンピュータ読み取り可能な記録媒体 |

| US6754179B1 (en) * | 2000-06-13 | 2004-06-22 | Lsi Logic Corporation | Real time control of pause frame transmissions for improved bandwidth utilization |

| JP2002062990A (ja) * | 2000-08-15 | 2002-02-28 | Fujitsu Media Device Kk | インターフェイス装置 |

| MXPA03005310A (es) * | 2000-12-15 | 2004-03-26 | Qualcomm Inc | Generar e implementar un protocolo de comunicaciones e interfase para transferencia de senal de alta velocidad de datos. |

| US6760772B2 (en) * | 2000-12-15 | 2004-07-06 | Qualcomm, Inc. | Generating and implementing a communication protocol and interface for high data rate signal transfer |

| JP3497834B2 (ja) * | 2001-03-30 | 2004-02-16 | 株式会社東芝 | ルートリピータ、usb通信システム、usb通信制御方法 |

| JP2003069544A (ja) * | 2001-08-23 | 2003-03-07 | Hitachi Kokusai Electric Inc | 通信制御方法及び通信制御装置 |

| JP4322451B2 (ja) * | 2001-09-05 | 2009-09-02 | 日本電気株式会社 | Dspメモリ間あるいはdspメモリとcpu用メモリ(dpram)間データ転送方式 |

| IL160770A0 (en) * | 2001-09-06 | 2004-08-31 | Qualcomm Inc | Generating and implementing a communication protocol and interface for high data rate signal transfer |

| KR100408525B1 (ko) * | 2001-10-31 | 2003-12-06 | 삼성전자주식회사 | 네트워크에 적응적인 실시간 멀티미디어 스트리밍 시스템및 방법 |

| JP2003167680A (ja) * | 2001-11-30 | 2003-06-13 | Hitachi Ltd | ディスク装置 |

| US20030135863A1 (en) * | 2002-01-17 | 2003-07-17 | Koninklijke Philips Electronics N.V. | Targeted scalable multicast based on client bandwidth or capability |

| JP2004021613A (ja) * | 2002-06-17 | 2004-01-22 | Seiko Epson Corp | データ転送制御装置、電子機器及びデータ転送制御方法 |

| KR100469427B1 (ko) * | 2002-06-24 | 2005-02-02 | 엘지전자 주식회사 | 이동통신 시스템의 동영상 재생 방법 |

| DE10234991B4 (de) * | 2002-07-31 | 2008-07-31 | Advanced Micro Devices, Inc., Sunnyvale | Hostcontrollerdiagnose für einen seriellen Bus |

| JP4028356B2 (ja) * | 2002-10-31 | 2007-12-26 | 京セラ株式会社 | 通信システム、無線通信端末、データ配信装置及び通信方法 |

| GB0226014D0 (en) * | 2002-11-08 | 2002-12-18 | Nokia Corp | Camera-LSI and information device |

| KR100448635B1 (ko) * | 2002-11-27 | 2004-09-13 | 한국전자통신연구원 | 이더넷 기반의 수동 광통신망에서의 통신 노드 시스템,제어 노드 시스템, 및 이를 이용한 통신 시스템 |

| US7047475B2 (en) * | 2003-02-04 | 2006-05-16 | Hewlett-Packard Development Company, L.P. | CRC encoding scheme for conveying status information |

| US7477604B2 (en) * | 2003-05-14 | 2009-01-13 | Ntt Docomo, Inc. | Packet communications system |

| ATE509459T1 (de) * | 2003-06-02 | 2011-05-15 | Qualcomm Inc | Erzeugung und umsetzung eines signalprotokolls und schnittstelle für höhere datenraten |

| CN101764804A (zh) * | 2003-09-10 | 2010-06-30 | 高通股份有限公司 | 高数据速率接口 |

| US7340548B2 (en) * | 2003-12-17 | 2008-03-04 | Microsoft Corporation | On-chip bus |

| US7158536B2 (en) * | 2004-01-28 | 2007-01-02 | Rambus Inc. | Adaptive-allocation of I/O bandwidth using a configurable interconnect topology |

| US20050248685A1 (en) * | 2004-04-21 | 2005-11-10 | Samsung Electronics Co., Ltd. | Multidata processing device and method in a wireless terminal |

| ES2395434T3 (es) * | 2004-11-24 | 2013-02-12 | Qualcomm, Incorporated | Sistemas y procedimientos para el control de la tasa de transmisión de datos digitales |

| WO2006058052A2 (en) * | 2004-11-24 | 2006-06-01 | Qualcomm Incorporated | Double data rate serial encoder |

| JP5958338B2 (ja) * | 2011-04-15 | 2016-07-27 | 三菱レイヨン株式会社 | 微細凹凸構造体、撥水性物品、モールド、及び微細凹凸構造体の製造方法 |

-

2005

- 2005-11-23 ES ES05824686T patent/ES2395434T3/es active Active

- 2005-11-23 CA CA2588714A patent/CA2588714C/en not_active Expired - Fee Related

- 2005-11-23 KR KR1020077013825A patent/KR100923170B1/ko active IP Right Grant

- 2005-11-23 CN CN2010102939177A patent/CN101931503B/zh not_active Expired - Fee Related

- 2005-11-23 WO PCT/US2005/042436 patent/WO2006058067A2/en active Application Filing

- 2005-11-23 SG SG201001266-4A patent/SG160337A1/en unknown

- 2005-11-23 EP EP11155762A patent/EP2317688A3/en not_active Withdrawn

- 2005-11-23 CN CN201210449348.XA patent/CN102983937B/zh not_active Expired - Fee Related

- 2005-11-23 BR BRPI0518264-6A patent/BRPI0518264A2/pt not_active IP Right Cessation

- 2005-11-23 KR KR1020077013823A patent/KR100886297B1/ko not_active IP Right Cessation

- 2005-11-23 CA CA2588717A patent/CA2588717C/en not_active Expired - Fee Related

- 2005-11-23 JP JP2007543424A patent/JP5038148B2/ja not_active Expired - Fee Related

- 2005-11-23 CA CA2651781A patent/CA2651781C/en not_active Expired - Fee Related

- 2005-11-23 JP JP2007543436A patent/JP4750799B2/ja not_active Expired - Fee Related

- 2005-11-23 CA CA002588845A patent/CA2588845A1/en not_active Abandoned

- 2005-11-23 KR KR1020077013822A patent/KR100930270B1/ko active IP Right Grant

- 2005-11-23 EP EP05852047A patent/EP1815624B1/en not_active Not-in-force

- 2005-11-23 JP JP2007543500A patent/JP5048510B2/ja not_active Expired - Fee Related

- 2005-11-23 WO PCT/US2005/042412 patent/WO2006058050A2/en active Search and Examination

- 2005-11-23 CA CA2649646A patent/CA2649646C/en not_active Expired - Fee Related

- 2005-11-23 KR KR1020077012323A patent/KR100972877B1/ko active IP Right Grant

- 2005-11-23 EP EP05852044A patent/EP1825600A4/en not_active Withdrawn

- 2005-11-23 EP EP05824693A patent/EP1825623A4/en not_active Withdrawn

- 2005-11-23 EP EP05824686A patent/EP1815627B1/en not_active Not-in-force

- 2005-11-23 JP JP2007543422A patent/JP2008522493A/ja active Pending

- 2005-11-23 WO PCT/US2005/042643 patent/WO2006058173A2/en active Search and Examination

- 2005-11-23 CA CA2698730A patent/CA2698730C/en not_active Expired - Fee Related

- 2005-11-23 WO PCT/US2005/042402 patent/WO2006058045A2/en active Application Filing

- 2005-11-23 AU AU2005309680A patent/AU2005309680C1/en not_active Ceased

- 2005-11-23 CA CA2588722A patent/CA2588722C/en not_active Expired - Fee Related

-

2007

- 2007-05-24 IL IL183409A patent/IL183409A0/en unknown

- 2007-05-24 IL IL183414A patent/IL183414A0/en unknown

- 2007-05-24 IL IL183410A patent/IL183410A0/en unknown

- 2007-05-24 IL IL183413A patent/IL183413A0/en unknown

-

2010

- 2010-06-18 AU AU2010202545A patent/AU2010202545A1/en not_active Abandoned

- 2010-11-11 JP JP2010253017A patent/JP5226758B2/ja not_active Expired - Fee Related

-

2011

- 2011-06-08 JP JP2011128441A patent/JP2011250419A/ja active Pending

- 2011-08-05 JP JP2011171755A patent/JP5356469B2/ja not_active Expired - Fee Related

-

2012

- 2012-11-14 JP JP2012250168A patent/JP2013081190A/ja active Pending

Also Published As

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5038148B2 (ja) | 巡回冗長検査を実行するためのシステム及び方法 | |

| US8667363B2 (en) | Systems and methods for implementing cyclic redundancy checks | |

| US7548736B2 (en) | Transmitter, receiver, data transfer system, transmission method, reception method, computer program for transmission, computer program for reception, and recording medium | |

| KR101166734B1 (ko) | 고속 데이터 레이트를 위한 신호 프로토콜 및 인터페이스의 생성 및 구현 | |

| US8611215B2 (en) | Systems and methods for digital data transmission rate control | |

| EP1934761B1 (en) | Dma transfer and hardware acceleration of ppp frame processing | |

| JP2006285378A (ja) | データ転送装置 | |

| CN107733568B (zh) | 基于fpga实现crc并行计算的方法及装置 | |

| TWI400889B (zh) | 循環冗餘檢查之實施系統及方法 | |

| EP2337420A2 (en) | A packet structure for a mobile display digital interface | |

| KR100801884B1 (ko) | 플래시 메모리, 플래시 메모리의 제어 방법 및 직렬인터페이스 장치 | |

| WO2015151779A1 (ja) | 電子機器およびケーブル適合性判断方法 | |

| KR20070066868A (ko) | 데이터 패킷 전송 방법 및 장치 | |

| TW200948008A (en) | A packet structure for a mobile display digital interface |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100511 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100811 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100818 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101111 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110208 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120705 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150713 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5038148 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |