JP5000847B2 - 半導体素子のセルチャンネルイオン注入方法 - Google Patents

半導体素子のセルチャンネルイオン注入方法 Download PDFInfo

- Publication number

- JP5000847B2 JP5000847B2 JP2004361472A JP2004361472A JP5000847B2 JP 5000847 B2 JP5000847 B2 JP 5000847B2 JP 2004361472 A JP2004361472 A JP 2004361472A JP 2004361472 A JP2004361472 A JP 2004361472A JP 5000847 B2 JP5000847 B2 JP 5000847B2

- Authority

- JP

- Japan

- Prior art keywords

- ion implantation

- region

- cell

- channel ion

- cell channel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H10P30/20—

-

- H10P30/21—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/48—Data lines or contacts therefor

- H10B12/485—Bit line contacts

-

- H10P30/204—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

- H10B12/0335—Making a connection between the transistor and the capacitor, e.g. plug

Landscapes

- Semiconductor Memories (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

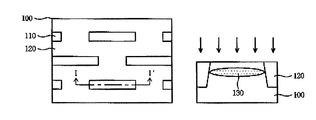

110 活性領域

120 素子分離膜

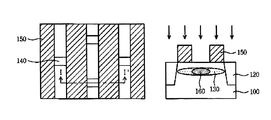

130、160 不純物注入領域

140 チャンネル領域のエッジ部

150 感光膜パターン

170 ワードライン

Claims (7)

- セル領域を備えた半導体基板を含む半導体素子のセルチャンネルイオン注入方法において、

前記セル領域のうち、ビットラインコンタクト領域及び前記ビットラインコンタクト領域と隣接したチャンネル領域のエッジ部にはセルチャンネルイオン注入工程を2回行ない、前記セル領域の他の領域には1回行なって前記ビットラインコンタクト領域及びチャンネル領域のエッジ部の不純物濃度を、前記他の領域より増加させる方法であって、

1次セルチャンネルイオン注入工程を行なって前記セル領域の半導体基板表面に不純物を注入する段階、

前記ビットラインコンタクト領域及びチャンネル領域のエッジ部を露出させる感光膜パターンを形成する段階、

前記感光膜パターンをイオン注入マスクとして2次セルチャンネルイオン注入工程を行ない、前記露出したビットラインコンタクト領域及びチャンネル領域のエッジ部に不純物を注入する段階、

前記感光膜パターンを除去する段階、

前記1次セルチャンネルイオン注入工程及び前記2次セルチャンネルイオン注入工程によって不純物が注入された前記半導体基板にワードラインを形成する段階、

前記ワードラインが形成された後、前記ワードラインをマスクとして前記半導体基板にソース/ドレインを形成する段階

を含むことを特徴とする半導体素子のセルチャンネルイオン注入方法。 - セル領域を備えた半導体基板を含む半導体素子のセルチャンネルイオン注入方法において、

前記セル領域のうち、ビットラインコンタクト領域及び前記ビットラインコンタクト領域と隣接したチャンネル領域のエッジ部にはセルチャンネルイオン注入工程を2回行ない、前記セル領域の他の領域には1回行なって前記ビットラインコンタクト領域及びチャンネル領域のエッジ部の不純物濃度を、前記他の領域より増加させる方法であって、

前記セル領域の半導体基板表面に前記ビットラインコンタクト領域及びチャンネル領域のエッジ部を露出させる感光膜パターンを形成する段階、

前記感光膜パターンをイオン注入マスクとして1次セルチャンネルイオン注入工程を行ない、前記露出したビットラインコンタクト領域及びチャンネル領域のエッジ部に不純物を注入する段階、

前記感光膜パターンを除去する段階、

2次セルチャンネルイオン注入工程を行なって前記セル領域の半導体基板表面に不純物を注入する段階、

前記1次セルチャンネルイオン注入工程及び前記2次セルチャンネルイオン注入工程によって不純物が注入された前記半導体基板にワードラインを形成する段階、

前記ワードラインが形成された後、前記ワードラインをマスクとして前記半導体基板にソース/ドレインを形成する段階

を含むことを特徴とする半導体素子のセルチャンネルイオン注入方法。 - 前記感光膜パターンは、ライン様であることを特徴とする請求項1又は2に記載の半導体素子のセルチャンネルイオン注入方法。

- 前記露出するチャンネル領域のエッジ部の幅は、ワードラインの幅より小さいことを特徴とする請求項1又は2に記載の半導体素子のセルチャンネルイオン注入方法。

- 前記2次セルチャンネルイオン注入工程のドーズ量は、前記1次セルチャンネルイオン注入工程のドーズ量の0.1〜10倍であることを特徴とする請求項1に記載の半導体素子のセルチャンネルイオン注入方法。

- 前記1次セルチャンネルイオン注入工程のドーズ量は、前記2次セルチャンネルイオン注入工程のドーズ量の0.1〜10倍であることを特徴とする請求項2に記載の半導体素子のセルチャンネルイオン注入方法。

- 前記1次セルチャンネルイオン注入工程の不純物は、前記2次セルチャンネルイオン注入工程の不純物と同一であるか、異なることを特徴とする請求項1又は2に記載の半導体素子のセルチャンネルイオン注入方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR2004-070016 | 2004-09-02 | ||

| KR1020040070016A KR100596851B1 (ko) | 2004-09-02 | 2004-09-02 | 반도체 소자의 셀 채널 이온 주입 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006073981A JP2006073981A (ja) | 2006-03-16 |

| JP5000847B2 true JP5000847B2 (ja) | 2012-08-15 |

Family

ID=36139598

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004361472A Expired - Fee Related JP5000847B2 (ja) | 2004-09-02 | 2004-12-14 | 半導体素子のセルチャンネルイオン注入方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7393767B2 (ja) |

| JP (1) | JP5000847B2 (ja) |

| KR (1) | KR100596851B1 (ja) |

| CN (1) | CN100364055C (ja) |

| TW (1) | TWI294150B (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100596851B1 (ko) * | 2004-09-02 | 2006-07-05 | 주식회사 하이닉스반도체 | 반도체 소자의 셀 채널 이온 주입 방법 |

| WO2012098759A1 (ja) * | 2011-01-17 | 2012-07-26 | 住友電気工業株式会社 | 炭化珪素半導体装置の製造方法 |

| US10074605B2 (en) * | 2016-06-30 | 2018-09-11 | Taiwan Semiconductor Manufacturing Co., Ltd. | Memory cell and array structure having a plurality of bit lines |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2555027B2 (ja) * | 1986-05-26 | 1996-11-20 | 株式会社日立製作所 | 半導体記憶装置 |

| JP2577093B2 (ja) * | 1989-09-14 | 1997-01-29 | 三星電子株式会社 | マルチゲート型mos トランジスタ構造を具備した半導体素子のセルフアライメントイオン注入方法 |

| KR960012303B1 (ko) * | 1992-08-18 | 1996-09-18 | 삼성전자 주식회사 | 불휘발성 반도체메모리장치 및 그 제조방법 |

| JP3181773B2 (ja) * | 1993-10-29 | 2001-07-03 | シャープ株式会社 | 半導体装置の製造方法 |

| TW304301B (ja) * | 1994-12-01 | 1997-05-01 | At & T Corp | |

| US5672521A (en) * | 1995-11-21 | 1997-09-30 | Advanced Micro Devices, Inc. | Method of forming multiple gate oxide thicknesses on a wafer substrate |

| KR0167271B1 (ko) * | 1995-11-30 | 1998-12-15 | 문정환 | 비균등 도우프 채널 구조를 갖는 반도체소자의 제조방법 |

| CN1057867C (zh) * | 1995-12-20 | 2000-10-25 | 台湾茂矽电子股份有限公司 | 注入磷形成补偿的器件沟道区的半导体器件的制造方法 |

| JPH1098176A (ja) * | 1996-09-19 | 1998-04-14 | Toshiba Corp | 固体撮像装置 |

| JP3777000B2 (ja) * | 1996-12-20 | 2006-05-24 | 富士通株式会社 | 半導体装置とその製造方法 |

| TW417256B (en) * | 1997-01-31 | 2001-01-01 | Seiko Epson Corp | Semiconductor MOS device and its manufacturing method |

| JP3390319B2 (ja) * | 1997-02-03 | 2003-03-24 | シャープ株式会社 | 半導体装置及びその製造方法 |

| EP1008178B1 (de) * | 1997-07-29 | 2003-11-12 | Infineon Technologies AG | Verfahren zur herstellung eines nur lese-speichers |

| US6274912B1 (en) * | 1997-10-29 | 2001-08-14 | Sony Corporation | Semiconductor memory cell and method of manufacturing the same |

| JP3147847B2 (ja) * | 1998-02-24 | 2001-03-19 | 日本電気株式会社 | 半導体装置及びその製造方法 |

| US6362049B1 (en) * | 1998-12-04 | 2002-03-26 | Advanced Micro Devices, Inc. | High yield performance semiconductor process flow for NAND flash memory products |

| JP2000236074A (ja) * | 1998-12-17 | 2000-08-29 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JP2000260962A (ja) * | 1999-03-10 | 2000-09-22 | Hitachi Ltd | 半導体集積回路装置 |

| CN1159576C (zh) * | 1999-05-10 | 2004-07-28 | 三星电子株式会社 | 制造磁共振成像系统用的主磁体总成的方法 |

| KR100351055B1 (ko) * | 2000-06-27 | 2002-09-05 | 삼성전자 주식회사 | 채널 이온 주입용 마스크 패턴을 이용한 반도체 메모리소자의 제조 방법 |

| JP2002184879A (ja) * | 2000-12-19 | 2002-06-28 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JP2002198500A (ja) * | 2000-12-27 | 2002-07-12 | Mitsubishi Electric Corp | 半導体集積回路装置およびその製造方法 |

| KR20040000772A (ko) * | 2002-06-25 | 2004-01-07 | 삼성전자주식회사 | 반도체 장치의 트랜지스터 제조 방법 |

| KR100460067B1 (ko) * | 2002-07-19 | 2004-12-04 | 주식회사 하이닉스반도체 | 반도체소자의 리프레시특성 개선방법 |

| US6933557B2 (en) * | 2003-08-11 | 2005-08-23 | Atmel Corporation | Fowler-Nordheim block alterable EEPROM memory cell |

| JP2005123384A (ja) * | 2003-10-16 | 2005-05-12 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| KR100596851B1 (ko) * | 2004-09-02 | 2006-07-05 | 주식회사 하이닉스반도체 | 반도체 소자의 셀 채널 이온 주입 방법 |

-

2004

- 2004-09-02 KR KR1020040070016A patent/KR100596851B1/ko not_active Expired - Fee Related

- 2004-12-07 US US11/004,835 patent/US7393767B2/en not_active Expired - Fee Related

- 2004-12-14 JP JP2004361472A patent/JP5000847B2/ja not_active Expired - Fee Related

- 2004-12-15 TW TW093138959A patent/TWI294150B/zh not_active IP Right Cessation

- 2004-12-24 CN CNB2004101049168A patent/CN100364055C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR20060021160A (ko) | 2006-03-07 |

| CN100364055C (zh) | 2008-01-23 |

| US7393767B2 (en) | 2008-07-01 |

| US20060046404A1 (en) | 2006-03-02 |

| JP2006073981A (ja) | 2006-03-16 |

| TW200610062A (en) | 2006-03-16 |

| TWI294150B (en) | 2008-03-01 |

| KR100596851B1 (ko) | 2006-07-05 |

| CN1744280A (zh) | 2006-03-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5000847B2 (ja) | 半導体素子のセルチャンネルイオン注入方法 | |

| JP5000863B2 (ja) | 半導体素子の製造方法 | |

| JP2006270044A (ja) | フラッシュメモリ素子の製造方法 | |

| US7223661B2 (en) | Method of manufacturing semiconductor device | |

| JP4376325B2 (ja) | 半導体記憶装置およびその製造方法 | |

| JP3854290B2 (ja) | 半導体装置およびその製造方法 | |

| KR100567074B1 (ko) | 반도체 소자의 제조방법 | |

| CN115424984B (zh) | 一种提高mtp编程能力的工艺方法 | |

| KR100650773B1 (ko) | 돌기형 트랜지스터 및 그의 형성방법 | |

| KR100905182B1 (ko) | 반도체 소자 형성 방법 | |

| KR20070081271A (ko) | 반도체 소자의 제조방법 | |

| KR20040062276A (ko) | 플래시 메모리 소자의 주변 트랜지스터 형성방법 | |

| KR100680488B1 (ko) | 플래쉬 메모리 소자의 제조방법 | |

| KR20070025573A (ko) | 셀-할로 이온주입을 이용한 스텝게이트 비대칭 리세스 셀의제조방법 | |

| KR20060076369A (ko) | 반도체 소자의 제조방법 | |

| KR100972859B1 (ko) | 이온 주입시 산란현상에 의해 변화하는 트랜지스터의 문턱전압의 제어방법 | |

| KR20050002507A (ko) | 플래쉬 메모리셀 제조 방법 | |

| KR20050088687A (ko) | 비대칭적인 소오스/드레인을 갖는 반도체 메모리 소자의제조방법 | |

| JP2005038875A (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| KR20060023340A (ko) | 반도체 소자의 트랜지스터 형성방법 | |

| KR20080074573A (ko) | 온 셀 영역에서 단채널을 갖는 마스크롬의 제조 방법 및이에 의해 제조된 마스크롬 | |

| KR20070003341A (ko) | 반도체 소자의 제조방법 | |

| KR20080016197A (ko) | 플래시 메모리 소자의 고전압 트랜지스터 형성방법 | |

| KR20070025575A (ko) | 균일한 문턱전압을 갖도록 하는 스텝게이트 비대칭 리세스셀 형성방법 | |

| KR20090022781A (ko) | 반도체 소자의 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071017 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100114 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110614 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110914 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20111115 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120315 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20120323 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120508 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120517 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150525 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |