JP4959080B2 - 反射マスク基板のコーティング - Google Patents

反射マスク基板のコーティング Download PDFInfo

- Publication number

- JP4959080B2 JP4959080B2 JP2001501941A JP2001501941A JP4959080B2 JP 4959080 B2 JP4959080 B2 JP 4959080B2 JP 2001501941 A JP2001501941 A JP 2001501941A JP 2001501941 A JP2001501941 A JP 2001501941A JP 4959080 B2 JP4959080 B2 JP 4959080B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- substrate

- silicon

- surface side

- mask substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y40/00—Manufacture or treatment of nanostructures

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F1/00—Originals for photomechanical production of textured or patterned surfaces, e.g., masks, photo-masks, reticles; Mask blanks or pellicles therefor; Containers specially adapted therefor; Preparation thereof

- G03F1/22—Masks or mask blanks for imaging by radiation of 100nm or shorter wavelength, e.g. X-ray masks, extreme ultraviolet [EUV] masks; Preparation thereof

- G03F1/24—Reflection masks; Preparation thereof

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F1/00—Originals for photomechanical production of textured or patterned surfaces, e.g., masks, photo-masks, reticles; Mask blanks or pellicles therefor; Containers specially adapted therefor; Preparation thereof

- G03F1/38—Masks having auxiliary features, e.g. special coatings or marks for alignment or testing; Preparation thereof

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F1/00—Originals for photomechanical production of textured or patterned surfaces, e.g., masks, photo-masks, reticles; Mask blanks or pellicles therefor; Containers specially adapted therefor; Preparation thereof

- G03F1/38—Masks having auxiliary features, e.g. special coatings or marks for alignment or testing; Preparation thereof

- G03F1/46—Antireflective coatings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P76/00—Manufacture or treatment of masks on semiconductor bodies, e.g. by lithography or photolithography

- H10P76/40—Manufacture or treatment of masks on semiconductor bodies, e.g. by lithography or photolithography of masks comprising inorganic materials

- H10P76/408—Manufacture or treatment of masks on semiconductor bodies, e.g. by lithography or photolithography of masks comprising inorganic materials characterised by their sizes, orientations, dispositions, behaviours or shapes

- H10P76/4085—Manufacture or treatment of masks on semiconductor bodies, e.g. by lithography or photolithography of masks comprising inorganic materials characterised by their sizes, orientations, dispositions, behaviours or shapes characterised by the processes involved to create the masks

-

- G—PHYSICS

- G21—NUCLEAR PHYSICS; NUCLEAR ENGINEERING

- G21K—HANDLING OF PARTICLES OR IONISING RADIATION NOT OTHERWISE PROVIDED FOR; IRRADIATION DEVICES; GAMMA RAY OR X-RAY MICROSCOPES

- G21K2201/00—Arrangements for handling radiation or particles

- G21K2201/06—Arrangements for handling radiation or particles using diffractive, refractive or reflecting elements

- G21K2201/067—Construction details

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Nanotechnology (AREA)

- Crystallography & Structural Chemistry (AREA)

- Mathematical Physics (AREA)

- Theoretical Computer Science (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Preparing Plates And Mask In Photomechanical Process (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

Description

米国政府は、Lawrence Livermore National Laboratoryの事業に関する米国エネルギー省とカリフォルニア大学との契約No.W‐7405‐ENG‐48に従い、この発明に権利を有している。

【0002】

【関連出願】

この出願は6/7/99付で出願されたUS仮出願60/138,158およびそのクレイム優先権と関連している。

【0003】

【発明の背景】

本発明はリソグラフィー用の反射マスク基板、具体的には極紫外線リソグラフィー用の反射マスク基板、更に具体的には、マスク基板として低熱膨張性物質の使用を可能にして、このような基板で多層膜応力作用を相殺するコーティングをマスク基板の表面(フロント)および/または裏面(バック)へ施すこと、追加コーティングがマスク基板の表面(フロント)および/または裏面(バック)へ適用されることに関する。

【0004】

極紫外線リソグラフィー(EUVL)は、半導体マイクロエレクトロニクスを加工する次世代リソグラフィーシステム用の筆頭候補である。EUVLと従来のリソグラフィーとの主要な差異は、EUVLが13.4nm光を用いるため、多層膜(ML)、典型的にはMo/Siでコートされた反射光素子およびマスクを要することである。欠陥を容易に精査しうる低熱膨張性物質(LTEM)透明マスク基板の開発は、現在発展中の重要な面である。

【0005】

EUVリソグラフィーマスクまたはレチクルの熱管理は、極紫外線リソグラフィー(EUVL)システムに関する現在の開発努力からみて重要な分野になっている。S.E.Gianoulakis et al.,”Thermal-mechanical performance of extreme ultraviolet lithographic rectiles”,J.Vac.Sci.Technol.B16(6)3440-3,Nov./Dec.1998およびS.E.Gianoulakis et al.,”Thermal management of EUV lithographymasks using low expansion glass substrates”,Emerging Lithographic Technologies III,SPIE Proceedings,Vol.3676,1999参照。

【0006】

現在、epi-Si(100)ウェハが、少ない欠陥、優れた平面性および仕上げ並びに精査および超清浄取扱い機器の存在のようなそれらの望ましい性質のおかげで、EUVLマスクブランク用の基板として用いられている。しかしながら、シリコンは許容し得ないほど大きな熱膨張率を有している。印刷中に、EUV光の〜40%はマスクに吸収されてしまい、加熱により生じた熱膨張は大きな画像たわみを引き起こして、エラー・バジェット(error budget)を超えることがある。低熱膨張性物質(LTEM)はEUVLマスク用の基板物質として提案されてきた。W.M.Tong et al.,”Mask substrated requirements and development for extreme ultraviolet lithography(EUVL)” ,SPIE,Vol.3873,Sept.1999参照。しかしながら、LTEM基板の使用には次の面で新たな挑戦を克服する必要がある。

【0007】

1.精査

欠陥数はEUVLマスク加工にとり主要な関心事であり、欠陥精査は欠陥を減らす上で重要なステップである。光散乱が最新の欠陥精査機器で用いられている。欠陥の散乱断面積は可視波長で反射性の表面により高められる:ULEのような透明LTEM基板で最少の検出可能な欠陥サイズ検知閾値(〜0.12μm)はシリコン表面の場合(〜60nm)よりも高い。透明基板で欠陥検知を高める手段が必要とされる。

【0008】

2.表面仕上げ

EUVLマスクでは、画像配置エラーおよび反射能の喪失を最少に抑えるために、低い平面性エラーおよび低い面粗性を各々要求する。平面性および面粗性の要件を果たす上で役立ついかなる方法も望ましい。

【0009】

3.欠陥

現在、非シリコン基板の欠陥数はシリコンウェハよりもかなり多いが、シリコンウェハで欠陥を少なくという半導体産業の要望が欠陥を減らす上でシリコン基板製造業者に何十億ドルもの投資を余儀なくさせていたからである。最新の欠陥精査、クリーニングおよび他の欠陥減少プロセスを行う現行機器とより適合しうるようにLTEM基板を作ることが高度に望ましい。

【0010】

4.静電マスクチャック

マスクの静電チャッキングはEUVLマスク加工の様々な段階で必要とされている。多層膜コーティングに際する静電チャッキングは機械的チャッキングよりもマスクへ加える欠陥が少ないことが証明された。更に、静電チャッキングはマスクのパターン化、精査および暴露に際してマスクをマウントする上で評価をうけている2つのオプションのうち1つである。しかしながら、ほとんどのLTEMはシリコンと異なり低い誘電率を有しており、同様のチャッキング力を得る上でかなり高い電圧を要する。高電圧は可能性としてプロセッシングステップを妨げる電界を生み出すか、または真空中で絶縁破壊を生じることがある。LTEM基板は低電圧静電チャックと適合するよう作製されねばならない。

【0011】

5.応力バランシング

どのような種類のコーティングを有する基板も、2者間の応力アンバランスのせいでたわむことがある。EUVLマスクの場合、基板はほぼゼロの膨張であって、シリコンのような典型的コーティングが大きさで大抵1または2程度高いCTEを有していることから、この問題は特に激しい。応力形成で1つの可能なメカニズムは次のとおりである:LTEM基板へのML付着は約70℃で行われる。付着後、温度は環境に戻って、MLは収縮する。LTEM基板は収縮しないため、これは応力アンバランスを生じて、たわんだ基板をもたらす。応力アンバランスによるこのたわみを克服するための技術は必須である。

【0012】

本発明は上記の問題に対する解決法を提供するもので、EUVLマスク用の基板物質として低熱膨張性物質(LTEM)の使用を可能とする。本発明では基本的にLTEM基板の表面および/または裏面表面へコーティングを施す。表面コーティングは基板の欠陥精査、欠陥減少、表面仕上げおよび応力バランスを高めるが、裏面コーティングは基板の静電チャッキングおよび応力バランスを高める。

【0013】

【発明の要旨】

フォトリソグラフィー用のマスク基板として低熱膨張性物質の使用を可能とさせることが、本発明の目的である。

本発明の別な目的は、透明でもまたはそうでなくてもよい、低熱膨張性物質から構成されているEUVLマスク基板を加工するために、シリコン、金属または多層膜のようなコーティングを用いるプロセスを提供することである。

本発明のもう1つの目的は、改善された欠陥精査を行えるように、シリコンのようなコーティングを有した透明または非反射性低熱膨張性物質マスク基板を提供することである。

本発明のもう1つの目的は、改善された表面仕上げを行えるように、平滑化効果をもつおよび/または研磨しうる表面コーティングを有したマスク基板を提供することである。

本発明のもう1つの目的は、表面欠陥の減少を行えるように、シリコンおよびモリブデンのような表面コーティングを有したマスク基板を提供することである。

本発明のもう1つの目的は、基板の静電チャッキングを促すために、シリコン、モリブデン、クロム、オキシ窒化クロムまたはTaSiのような、基板よりも高い誘電率の物質の裏面コーティングを有したマスク基板を提供することである。

本発明のもう1つの目的は、コーティングがシリコン、モリブデン、クロム、オキシ窒化クロム、TaSiおよびMo/Si多層膜スタックのような物質を含有している、基板の応力誘導性たわみを直すために、表面および/または裏面にコーティングを有したマスク基板を提供することである。

【0014】

本発明の他の目的および利点は、以下の記載および添付した図面から明らかになるであろう。基本的に、本発明では表面、裏面および/または双方においてコーティングでマスク基板をコートする。マスクの表面におけるコーティングは、欠陥精査を高め、表面仕上げを改善し、欠陥レベルを減らし、および/または他のコーティングとマスク基板との応力アンバランスによる基板のたわみを直すためである。基板の裏面における高誘電性コーティングは、静電チャッキングを促し、欠陥精査を高め、および/またはマスク基板の表面における付着シリコン層および/またはMLコーティングで生じた応力アンバランスによる基板のたわみを直すためである。更に詳しくは、本発明は、表面側でシリコンのような物質でコートされ、裏面側で金属のような少くとも高誘電性のコーティングでコートされた、低熱膨張性物質(LTEM)基板から構成されている、マスク基板に関する。LTEMの片側または両側におけるシリコンコーティングは、欠陥精査、表面仕上げおよび欠陥レベルが改善された透明EUVLマスク基板を供する。基板の裏面側における、付加コーティングおよび高誘電率を有するコーティングは、静電チャッキングを促して、マスク基板の表面側で多層膜コーティングに付着するシリコン層で生じた応力アンバランスによる基板のたわみを直すためにある。加えて、LTEM基板の表面側とシリコンコーティングとの中間またはシリコンコーティングと多層膜との間に、非晶質でもよい膜を形成することは、応力バランスをとる上で役立つ。本発明の透明マスク基板は、EUVLマスク応用に加えて、集積回路製造用の半導体ダイをパターン化する上で他のリソグラフィーシステムにも応用できる。

【0015】

【発明の具体的な説明】

本発明は、EUVLシステムで利用されるような反射マスク基板を用いるフォトリソグラフィー向けに、低熱膨張性物質(LTEM)マスク基板のようなマスク基板上における、シリコンおよび金属コーティングのようなコーティングの使用に関する。本発明では、欠陥精査、表面仕上げおよび欠陥レベルを改善するために、LTEMマスク基板の片側または両側に1以上のコーティングを施し;静電チャッキングを促して、マスク基板の表面側および/または裏面側に付着されたシリコン層または多層膜コーティングで生じた応力アンバランスによるたわみを直すために、基板の裏面側に導電性コーティングを施す。付着コーティングはシリコン、モリブデン、クロム、オキシ窒化クロム、TaSiまたはSi/Mo多層膜から構成しうる。しかも、TaSiのような物質の非晶質膜は、応力バランスをとるために、LTEMとSi膜との間にはさむことができる。低熱膨張性物質は熱膨張率<1ppm/Kの物質として規定され、選択されたガラス、ガラス‐セラミック、プラスチック、セラミック、複合材などから構成しうる。LTEMの例には、Schott Glass Technologies,Duryea,PA製のZerodur;Corning,Inc.,Corning,NY製のULE;Ohara Corp.,相模原,日本製のClearCeram;SiC、石英およびドライシリカがある。ここで記載されているマスクの表面または表面側とは、パターン化される側である。

【0016】

少くとも1つの表面側上層および/または1つの裏面側物質でLTEM基板をコーティングすると、先に記載され、後でも個別に記載されて、表1でまとめられた問題を解決しうる。

【0017】

1.精査:シリコンのような反射コーティングを有する透明または半透明マスク基板は、今日の最新シリコン欠陥精査機器で欠陥精査を行える。これらの機器の精査の感度および速度は、非反射基板を精査する対応機器の場合よりも現在はかなり高い。

【0018】

2.表面仕上げ:シリコン上層ではシリコン産業の成熟した仕上げ力を利用しうる。非晶質、多結晶質またはその他である1〜5μmシリコンのコーティングは、シリコンウェハと同程度の平面性および低面粗性になるまで研磨および加工することができる。これはシリコンウェハと同じように仕上げを行える手法をマスク基板へもたらす。

【0019】

3.欠陥減少:表面コーティングを有する利点は3倍である:第一に、そのコーティングはLTEM基板自体よりもきれいにしやすい物質から作製しうる。例えば、シリコンの表面コーティングを有したマスク基板では、シリコンウェハ用に開発された現行の洗練されたクリーニングテクノロジーおよびプロセスを利用しうる。第二に、シリコンまたはクロムのようなコーティングは、最新の低欠陥プロセス装置で用いられる自動操作装置でセンサーに用いられている可視光に対して基板を不透明にさせうる。そのため、本プロセッシング機器との適合性は有意に高められる。第三に、基板上のいかなる汚染物もオーバーコートで覆われるため、それらはプロセス機器に入れず、それらの機器で行われる他のプロセスを損なうことがない。更に、シリコン基板を仕上げる技術水準がより発達したおかげで、シリコンの表面コーティングは元のLTEM基板表面よりも良い仕上げおよびクリーン度となるまで容易に再研磨しうる。

【0020】

4.静電チャック:静電チャックはパターン化、精査および暴露のためにマスク基板をマウントする上で提案されており、その使用は高誘電率の基板物質により促されるであろう。ほとんどのマスク基板物質、例えばLTEMおよび石英は低い誘電率を有している。限定されないが、シリコン、TiN、モリブデン、クロム、TaSiおよび/またはMo/Si MLスタックを含めた、基板の裏面側における高誘電率のコーティングは、静電チャックの使用を促すようになる。

【0021】

5.応力バランシング:裏面側のコーティングも表面でMLによるたわみを直すために用いうる。裏面コーティングの厚さは、基板とその他のコーティングとの応力アンバランスを直すために必要とされるものに依存する。シリコン、モリブデン、クロム、オキシ窒化クロム、TaSiまたはMo/Si MLスタックのコーティングが用いうる。特に、応力がアニーリングにより調整しうるTaSiおよびオキシ窒化クロムのようなコーティングは、個別マスクの応力バランシングニーズを満たすように仕上げることもできる。

【0022】

【0023】

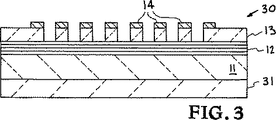

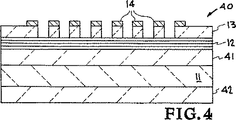

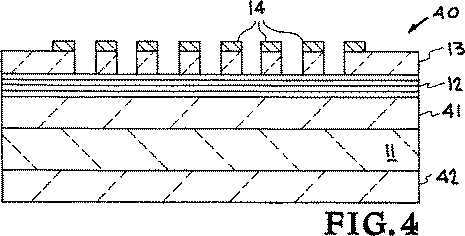

ここで図面を参考にしてみると、図1は全体として10で示された従来型EUVLマスク基板の態様を表わしており、LTEMのマスク基板11、例えばMo/Siのような多層膜12、二酸化ケイ素のようなマスクパターン修復用の緩衝層13、並びにTiNおよびCrのような吸収体パターン14から構成されている。

【0024】

図2〜4は、図1の場合と類似しているが、図1の基板11の表面、裏面または両側に1以上の物質層を付着させた、EUVLマスク基板の態様を表わしている。図1の場合に相当する部分は対応した参照番号で示されている。図2において、EUVLマスク基板20は図1のように基板11、多層膜12、緩衝層13および吸収体パターン14からなるが、欠陥精査、応力バランス、欠陥平滑性を高めておよび/または再研磨するために、基板11と多層膜12との間に表面コーティング21を付加している。表面コーティング21はSi、Mo、Cr、オキシ窒化クロム、TaSiまたはMo/Si多層膜のような物質から構成されている。

【0025】

図3は、図1のように基板11、多層膜12、緩衝層13および吸収体パターン14からなるが、静電チャッキングおよび/または応力バランスを促す裏面コーティング31を基板11に付加した、EUVLマスク基板30について示している。裏面コーティング31はSi、Mo、Cr、オキシ窒化クロム、TaSiまたはMo/Si多層膜のような物質から構成されている。

【0026】

図4は、図1のように基板11、多層膜12、緩衝層13および吸収体パターン14からなるが、図2のように基板11と多層膜12との間に表面コーティング41、および図3のように基板11に裏面コーティング42を付加した、EUVLマスク基板40について示しており、こうすると表面コーティング41は図2のように欠陥精査、応力バランス、欠陥平滑性を高めておよび/または再研磨しうるようになり、裏面コーティング42は図3のように静電チャッキングおよび/または応力バランスを促す。コーティング41および42は各々Si、Mo、Cr、オキシ窒化クロム、TaSiまたはMo/Si多層膜のような物質から構成されうる。

【0027】

表面コーティングおよび21および41と裏面コーティング31および42は単層コーティングとして示されているが、各コーティングは単層および/または多層構造でもよい。

【0028】

本発明は、集積回路製造用の半導体ダイをパターン化するEUVLシステムまたは他のリソグラフィーシステムのように、マスク基板の形成で精査、表面仕上げ、欠陥、応力バランシングおよび静電チャック保持に伴う以前の問題に対する解決法を提供していることが、こうして示された。欠陥精査を高め、表面仕上げを改善して、欠陥を減らし、静電チャッキングを促し、および/または応力アンバランスを直すために、マスク基板表面の表面および/または裏面でコーティングの適用により、本発明はフォトリソグラフィーマスク加工技術の水準をかなり発達させている。

【0029】

低熱膨張性物質を利用するマスク基板の具体的態様が、本発明の原理を例示および記載するために、特定の物質およびパラメーターと共に説明および記載されてきたが、このようなことは制限するためではない。修正および変更は当業者に明らかとなるであろうが、本発明が添付された請求の範囲のみに限定されるわけではない。

【図面の簡単な説明】

添付図面は本開示に組み込まれてその一部を形成するものであって、本発明の態様を図解しており、その記載と一緒にすると本発明の原理を説明する上で役立つ。

【図1】 従来のEUVLマスク基板の態様の横断面図である。

【図2】 本発明に従い作製された、1以上の表面コーティングを有するEUVLマスク基板の態様を示している。

【図3】 本発明に従い1以上の裏面コーティングを有するEUVLマスク基板の態様を示している。

【図4】 本発明に従い1以上の表面コーティングおよび1以上の裏面コーティングを有するEUVLマスク基板の態様を示している。

Claims (20)

- 熱膨張率<1ppm/Kの物質として規定される低熱膨張性物質から構成されてなる単層基板、

前記単層基板の表面側に少なくとも一つの物質層、および

前記単層基板の裏面側に少なくとも一つの物質層

を含んでなり、前記表面側の物質層および前記裏面側の物質層の両方が、前記基板における応力アンバランスを直して前記基板上の応力バランスをとるために用いられ、前記裏面側の物質層が、前記裏面側の物質層の厚さを制御すること又は前記裏面側の物質層にアニーリング工程を施すことにより、前記基板の表面側の多層(ML)コーティングによって引き起こされる前記基板上の応力を直すために用いられる、マスク基板。 - 基板の裏面側と物質層との中間に物質層を更に含んでなる、請求項1に記載のマスク基板。

- 基板の裏面側における物質が、非晶質シリコンまたは多結晶質シリコンから構成されてなるシリコンの層を含んでいる、請求項2に記載のマスク基板。

- 基板の表面側と物質層との中間に応力バランシング物質の層を更に含んでなる、請求項1に記載のマスク基板。

- 応力バランシング物質の層が、TaSiまたはオキシ窒化クロムから構成されてなる、請求項4に記載のマスク基板。

- 表面側の物質層上に多層構造を更に含んでなる、請求項1に記載のマスク基板。

- 表面側の物質層が、Si、Mo、Cr、オキシ窒化クロム、TaSi、およびMo/Si多層膜の群から選択される、請求項1に記載のマスク基板。

- 表面側の物質層がシリコンであって、非晶質または多結晶質シリコンから構成されてなる、請求項1に記載のマスク基板。

- 裏面側の物質層が、Si、Mo、Cr、オキシ窒化クロム、TaSi、およびMo/Si多層膜からなる群より選択される、請求項1に記載のマスク基板。

- 裏面側の物質が、MoおよびCrからなる群より選択される金属、またはTiN、TaSiおよびオキシ窒化クロムからなる群より選択される高誘電率の物質である、請求項9に記載のマスク基板。

- 低熱膨張性物質が、ガラス、プラスチック、セラミック、ガラス‐セラミック、複合材、プラスチックス、SiC、石英、およびドライシリカからなる群より選択される、請求項1に記載のマスク基板。

- 基板の表面側に少なくとも多層構造を含んだマスク基板を製造するための方法であって、熱膨張率<1ppm/Kの物質として規定される低熱膨張性物質の基板を形成し、

欠陥精査を高め、表面仕上げを改善し、欠陥レベルを減らし、応力アンバランスを直すために、基板と多層構造との中間に物質層を形成し、該物質層がシリコン、モリブデン、クロム、オキシ窒化クロム、TaSi、およびMo/Si多層膜からなる群より選択され、

静電チャッキング、欠陥精査を高めること、および応力アンバランスによる基材のたわみを直すことからなる群の少なくとも一つを促進するために、基板の裏面側に少なくとも一つの物質層を形成する

ことを含んでなり、

前記裏面側の物質層の厚さを設定すること又は前記裏面側の物質層にアニーリング工程を施すことのいずれかの手法を用いることにより、前記基板における応力アンバランスを直すように前記裏面側の物質層が仕上げられる、方法。 - 前記裏面側への前記層の形成が、誘電率を有する物質から該層を形成することによって行われる、請求項12に記載の方法。

- 前記裏面側への前記層の形成が、前記基板の裏面側にシリコン層を形成して、それにより該シリコン層で高誘電性物質の層を形成することによって行われる、請求項12に記載の方法。

- 高誘電性物質の層を形成することが、金属および導電性化合物からなる群より選択される物質を用いて行われる、請求項14に記載の方法。

- 前記基板と前記多層構造との中間の物質層がシリコンからなり、基板の表面側とシリコン層との間に応力バランシング物質の層を形成することを更に含んでなる、請求項12に記載の方法。

- 熱膨張率<1ppm/Kの物質として規定される低熱膨張性物質から構成されてなる基板、

前記基板の表面側におけるシリコンの第一層、

前記シリコンの第一層上における多層構造、

前記基板の裏面側におけるシリコンの第二層、および

前記シリコンの第二層上における導電性物質の層

を含んでなり、

前記第一層および前記第二層の両方が、前記基板における応力アンバランスを直すために用いられ、

前記裏面側の層の厚さを設定すること又は前記裏面側の層にアニーリング工程を施すことのいずれかの手法を用いることにより、前記基板における応力アンバランスを直すように前記裏面側の層が仕上げられてなる、透明EUVLマスク基板。 - 基板の表面側とシリコンの第一層との間に応力バランシング物質の膜を更に含んでいる、請求項17に記載のマスク基板。

- 低熱膨張性物質が、ガラス、プラスチック、複合材、ガラス‐セラミック、およびセラミックからなる群より選択され、シリコンの第一層が非晶質または多結晶質シリコンから構成されており、導電性物質の層が金属および高誘電性物質からなる群より選択され、前記高誘電性物質が、シリコン、TiN、モリブデン、クロム、TaSi、および/またはMo/Si多層スタックから選択される、請求項17に記載のマスク基板。

- 応力バランシング物質膜がTaSiからなる、請求項18に記載のマスク基板。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13815899P | 1999-06-07 | 1999-06-07 | |

| US60/138,158 | 1999-06-07 | ||

| PCT/US2000/015578 WO2000075727A2 (en) | 1999-06-07 | 2000-06-06 | Coatings on reflective mask substrates |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003501823A JP2003501823A (ja) | 2003-01-14 |

| JP2003501823A5 JP2003501823A5 (ja) | 2007-06-07 |

| JP4959080B2 true JP4959080B2 (ja) | 2012-06-20 |

Family

ID=22480708

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001501941A Expired - Lifetime JP4959080B2 (ja) | 1999-06-07 | 2000-06-06 | 反射マスク基板のコーティング |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6352803B1 (ja) |

| EP (1) | EP1190276A2 (ja) |

| JP (1) | JP4959080B2 (ja) |

| KR (1) | KR100805360B1 (ja) |

| AU (1) | AU5597000A (ja) |

| WO (1) | WO2000075727A2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20200011859A (ko) * | 2018-07-25 | 2020-02-04 | 주식회사 야스 | 유리 마스크 |

Families Citing this family (70)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2797060B1 (fr) * | 1999-07-29 | 2001-09-14 | Commissariat Energie Atomique | Structure pour masque de lithographie en reflexion et procede pour sa realisation |

| US6319635B1 (en) * | 1999-12-06 | 2001-11-20 | The Regents Of The University Of California | Mitigation of substrate defects in reticles using multilayer buffer layers |

| US6368942B1 (en) * | 2000-03-31 | 2002-04-09 | Euv Llc | Method for fabricating an ultra-low expansion mask blank having a crystalline silicon layer |

| US6524881B1 (en) * | 2000-08-25 | 2003-02-25 | Micron Technology, Inc. | Method and apparatus for marking a bare semiconductor die |

| US6821682B1 (en) * | 2000-09-26 | 2004-11-23 | The Euv Llc | Repair of localized defects in multilayer-coated reticle blanks for extreme ultraviolet lithography |

| JP3939132B2 (ja) * | 2000-11-22 | 2007-07-04 | Hoya株式会社 | 多層膜付き基板、露光用反射型マスクブランク、露光用反射型マスクおよびその製造方法、並びに半導体の製造方法 |

| US6737201B2 (en) * | 2000-11-22 | 2004-05-18 | Hoya Corporation | Substrate with multilayer film, reflection type mask blank for exposure, reflection type mask for exposure and production method thereof as well as production method of semiconductor device |

| US6749973B2 (en) * | 2001-02-14 | 2004-06-15 | Hoya Corporation | Reflection type mask blank for EUV exposure and reflection type mask for EUV exposure as well as method of producing the mask |

| JP2002299228A (ja) * | 2001-04-03 | 2002-10-11 | Nikon Corp | レチクル、それを用いた露光装置及び露光方法 |

| DE10164112A1 (de) * | 2001-12-24 | 2003-07-03 | Inst Oberflaechenmodifizierung | Verfahren zur Defektanalyse an reflektiven Optiken |

| US7169685B2 (en) * | 2002-02-25 | 2007-01-30 | Micron Technology, Inc. | Wafer back side coating to balance stress from passivation layer on front of wafer and be used as die attach adhesive |

| KR100455383B1 (ko) * | 2002-04-18 | 2004-11-06 | 삼성전자주식회사 | 반사 포토마스크, 반사 포토마스크의 제조방법 및 이를이용한 집적회로 제조방법 |

| US6777137B2 (en) * | 2002-07-10 | 2004-08-17 | International Business Machines Corporation | EUVL mask structure and method of formation |

| US7129010B2 (en) * | 2002-08-02 | 2006-10-31 | Schott Ag | Substrates for in particular microlithography |

| US7056627B2 (en) * | 2002-08-23 | 2006-06-06 | Hoya Corporation | Method of manufacturing a reflection type mask blank and method of manufacturing a reflection type mask |

| DE10255605B4 (de) * | 2002-11-28 | 2005-07-07 | Infineon Technologies Ag | Reflektionsmaske zur Projektion einer Struktur auf einen Halbleiterwafer sowie Verfahren zu deren Herstellung |

| DE10302342A1 (de) * | 2003-01-17 | 2004-08-05 | Schott Glas | Substrat für die EUV-Mikrolithographie und Herstellverfahren hierfür |

| DE10317792A1 (de) * | 2003-04-16 | 2004-11-11 | Schott Glas | Maskenrohling zur Verwendung in der EUV-Lithographie und Verfahren zu dessen Herstellung |

| JP4232018B2 (ja) * | 2003-07-25 | 2009-03-04 | 信越化学工業株式会社 | フォトマスクブランク用基板の選定方法 |

| US7075103B2 (en) * | 2003-12-19 | 2006-07-11 | General Electric Company | Multilayer device and method of making |

| JP2005210093A (ja) * | 2003-12-25 | 2005-08-04 | Hoya Corp | 多層反射膜付き基板、露光用反射型マスクブランクス及び露光用反射型マスク、並びにそれらの製造方法 |

| US20050238922A1 (en) * | 2003-12-25 | 2005-10-27 | Hoya Corporation | Substrate with a multilayer reflection film, reflection type mask blank for exposure, reflection type mask for exposure and methods of manufacturing them |

| US7198872B2 (en) * | 2004-05-25 | 2007-04-03 | International Business Machines Corporation | Light scattering EUVL mask |

| DE102004031079B4 (de) * | 2004-06-22 | 2008-11-13 | Qimonda Ag | Verfahren zur Herstellung einer Reflexionsmaske |

| US20060008749A1 (en) * | 2004-07-08 | 2006-01-12 | Frank Sobel | Method for manufacturing of a mask blank for EUV photolithography and mask blank |

| US7407729B2 (en) * | 2004-08-05 | 2008-08-05 | Infineon Technologies Ag | EUV magnetic contrast lithography mask and manufacture thereof |

| DE102004038548A1 (de) * | 2004-08-06 | 2006-03-16 | Schott Ag | Verfahren zur Herstellung eines Maskenblank für photolithographische Anwendungen und Maskenblank |

| JP4604140B2 (ja) * | 2004-09-13 | 2010-12-22 | マニー株式会社 | 医療用針又は刃物 |

| JP5042456B2 (ja) * | 2005-03-03 | 2012-10-03 | 凸版印刷株式会社 | ステンシルマスクの製造方法 |

| US20070093038A1 (en) * | 2005-10-26 | 2007-04-26 | Andreas Koenig | Method for making microchips and microchip made according to this method |

| EP1962326B1 (en) | 2005-12-12 | 2012-06-06 | Asahi Glass Company, Limited | Reflection-type mask blank for euv lithography, and substrate with electrically conductive film for the mask blank |

| US7678511B2 (en) * | 2006-01-12 | 2010-03-16 | Asahi Glass Company, Limited | Reflective-type mask blank for EUV lithography |

| KR100755395B1 (ko) | 2006-08-31 | 2007-09-04 | 삼성전자주식회사 | 반사 마스크, 반사 마스크 고정 장치 및 방법 |

| JP4958147B2 (ja) * | 2006-10-18 | 2012-06-20 | Hoya株式会社 | 露光用反射型マスクブランク及び露光用反射型マスク、多層反射膜付き基板、並びに半導体装置の製造方法 |

| JP4978626B2 (ja) | 2006-12-15 | 2012-07-18 | 旭硝子株式会社 | Euvリソグラフィ用反射型マスクブランク、および該マスクブランク用の機能膜付基板 |

| EP1973147B1 (en) * | 2006-12-27 | 2011-09-28 | Asahi Glass Company, Limited | Reflective mask blanc for euv lithography |

| WO2008093534A1 (ja) * | 2007-01-31 | 2008-08-07 | Asahi Glass Company, Limited | Euvリソグラフィ用反射型マスクブランク |

| JP5040996B2 (ja) | 2007-04-17 | 2012-10-03 | 旭硝子株式会社 | Euvリソグラフィ用反射型マスクブランク |

| KR101771380B1 (ko) * | 2008-05-09 | 2017-08-24 | 호야 가부시키가이샤 | 반사형 마스크, 반사형 마스크 블랭크 및 그 제조 방법 |

| JP2010135732A (ja) | 2008-08-01 | 2010-06-17 | Asahi Glass Co Ltd | Euvマスクブランクス用基板 |

| NL2003305A (en) | 2008-08-21 | 2010-03-10 | Asml Holding Nv | Euv reticle substrates with high thermal conductivity. |

| EP2333816A4 (en) | 2008-09-05 | 2014-01-22 | Asahi Glass Co Ltd | REFLECTING MASK ROLLING FOR EUV LITHOGRAPHY AND METHOD OF MANUFACTURING THEREOF |

| JP2010122304A (ja) * | 2008-11-17 | 2010-06-03 | Dainippon Printing Co Ltd | 反射型マスクブランクス、反射型マスク、反射型マスクブランクスの製造方法、および、反射型マスクの製造方法 |

| KR20120034074A (ko) | 2009-07-08 | 2012-04-09 | 아사히 가라스 가부시키가이샤 | Euv 리소그래피용 반사형 마스크 블랭크 |

| WO2011008964A1 (en) * | 2009-07-16 | 2011-01-20 | Kla-Tencor Corporation | Optical defect amplification for improved sensitivity on patterned layers |

| EP2509102A1 (en) | 2009-12-04 | 2012-10-10 | Asahi Glass Company, Limited | Optical member for euv lithography, and process for production of reflective-layer-attached substrate for euv lithography |

| CN102687071B (zh) | 2009-12-09 | 2013-12-11 | 旭硝子株式会社 | 带反射层的euv光刻用衬底、euv光刻用反射型掩模坯料、euv光刻用反射型掩模、和该带反射层的衬底的制造方法 |

| WO2011071086A1 (ja) | 2009-12-09 | 2011-06-16 | 旭硝子株式会社 | Euvリソグラフィ用光学部材 |

| JP5533395B2 (ja) * | 2010-07-26 | 2014-06-25 | 旭硝子株式会社 | Euvリソグラフィ用反射型マスクブランクの製造方法 |

| WO2012014904A1 (ja) | 2010-07-27 | 2012-02-02 | 旭硝子株式会社 | Euvリソグラフィ用反射層付基板、およびeuvリソグラフィ用反射型マスクブランク |

| US8192901B2 (en) | 2010-10-21 | 2012-06-05 | Asahi Glass Company, Limited | Glass substrate-holding tool |

| DE112012000658T5 (de) | 2011-02-04 | 2013-11-07 | Asahi Glass Company, Limited | Substrat mit leitendem Film, Substrat mit Mehrschicht-Reflexionsfilm und Reflexionsmaskenrohling für eine EUV-Lithographie |

| JP2011211250A (ja) * | 2011-07-29 | 2011-10-20 | Toppan Printing Co Ltd | ステンシルマスクブランク、ステンシルマスク、及びその製造方法、並びにパターン露光方法 |

| KR101993322B1 (ko) | 2011-09-28 | 2019-06-26 | 호야 가부시키가이샤 | 마스크블랭크용 유리기판, 다층 반사막 부착 기판, 마스크블랭크 및 마스크, 그리고 그것들의 제조방법 |

| US9354508B2 (en) | 2013-03-12 | 2016-05-31 | Applied Materials, Inc. | Planarized extreme ultraviolet lithography blank, and manufacturing and lithography systems therefor |

| US9417515B2 (en) * | 2013-03-14 | 2016-08-16 | Applied Materials, Inc. | Ultra-smooth layer ultraviolet lithography mirrors and blanks, and manufacturing and lithography systems therefor |

| US20140272684A1 (en) | 2013-03-12 | 2014-09-18 | Applied Materials, Inc. | Extreme ultraviolet lithography mask blank manufacturing system and method of operation therefor |

| KR20160140895A (ko) * | 2014-04-02 | 2016-12-07 | 지고 코포레이션 | 리소그래피용 포토마스크 |

| US9618836B2 (en) | 2014-04-22 | 2017-04-11 | Asahi Glass Company, Limited | Reflective mask blank for EUV lithography, substrate with funtion film for the mask blank, and methods for their production |

| TWI694304B (zh) | 2015-06-08 | 2020-05-21 | 日商Agc股份有限公司 | Euv微影術用反射型光罩基底 |

| KR102380156B1 (ko) * | 2015-06-30 | 2022-03-29 | 삼성디스플레이 주식회사 | 플라즈마 화학 기상 증착 장치 |

| US10539884B2 (en) | 2018-02-22 | 2020-01-21 | International Business Machines Corporation | Post-lithography defect inspection using an e-beam inspection tool |

| US10578981B2 (en) | 2018-07-25 | 2020-03-03 | International Business Machines Corporation | Post-lithography defect inspection using an e-beam inspection tool |

| DE102019100839B4 (de) * | 2019-01-14 | 2024-11-14 | Advanced Mask Technology Center Gmbh & Co. Kg | Fotomaskenanordnung mit reflektierender fotomaske und verfahren zum herstellen einer reflektierenden fotomaske |

| JP7350571B2 (ja) | 2019-08-30 | 2023-09-26 | Hoya株式会社 | 導電膜付基板、反射型マスクブランク及び反射型マスク、並びに半導体デバイスの製造方法 |

| JP7318607B2 (ja) | 2020-07-28 | 2023-08-01 | Agc株式会社 | Euvリソグラフィ用反射型マスクブランク、euvリソグラフィ用反射型マスク、およびそれらの製造方法 |

| KR20240036124A (ko) | 2021-02-16 | 2024-03-19 | 에이지씨 가부시키가이샤 | Euv 리소그래피용 반사형 마스크 블랭크, euv 리소그래피용 반사형 마스크 및 그것들의 제조 방법 |

| KR102674790B1 (ko) | 2022-04-28 | 2024-06-14 | 에이지씨 가부시키가이샤 | 반사형 마스크 블랭크, 반사형 마스크, 반사형 마스크의 제조 방법 |

| JP2024142243A (ja) | 2023-03-29 | 2024-10-10 | Hoya株式会社 | 導電膜付き基板、多層反射膜付き基板、反射型マスクブランク、反射型マスク、および半導体装置の製造方法 |

| WO2025226454A1 (en) * | 2024-04-26 | 2025-10-30 | Lam Research Corporation | Methods to enhance glass substrate handling in semiconductor processing |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS59154452A (ja) * | 1983-02-21 | 1984-09-03 | Dainippon Printing Co Ltd | 軟x線転写用マスク及びその製造法 |

| JPS61116358A (ja) * | 1984-11-09 | 1986-06-03 | Mitsubishi Electric Corp | フオトマスク材料 |

| US4868093A (en) * | 1987-05-01 | 1989-09-19 | American Telephone And Telegraph Company, At&T Bell Laboratories | Device fabrication by X-ray lithography utilizing stable boron nitride mask |

| JP2779221B2 (ja) * | 1989-08-25 | 1998-07-23 | 沖電気工業株式会社 | 位相差レチクルを用いた露光及び検査方法 |

| JP2751981B2 (ja) * | 1992-07-22 | 1998-05-18 | 株式会社日立製作所 | 電子線描画装置 |

| US5500312A (en) * | 1994-10-11 | 1996-03-19 | At&T Corp. | Masks with low stress multilayer films and a process for controlling the stress of multilayer films |

| US5521031A (en) * | 1994-10-20 | 1996-05-28 | At&T Corp. | Pattern delineating apparatus for use in the EUV spectrum |

| JP3578872B2 (ja) * | 1995-10-26 | 2004-10-20 | 三菱電機株式会社 | X線マスクの製造方法および加熱装置 |

| JPH09232216A (ja) * | 1996-02-27 | 1997-09-05 | Fujitsu Ltd | X線マスクの製造方法及び製造装置 |

| KR100223023B1 (ko) * | 1996-08-21 | 1999-10-01 | 정선종 | X-선 마스크 |

| US6027815A (en) * | 1996-11-06 | 2000-02-22 | Taiwan Semiconductor Manufacturing Company | Non-absorbing anti-reflective coated (ARC) reticle using thin dielectric films and method of forming reticle |

| JP3437389B2 (ja) * | 1996-11-08 | 2003-08-18 | 信越化学工業株式会社 | 電子線およびx線リソグラフィ用マスクメンブレン |

| JPH10177943A (ja) * | 1996-12-18 | 1998-06-30 | Hitachi Ltd | 投影露光方法 |

| US6042995A (en) * | 1997-12-09 | 2000-03-28 | Lucent Technologies Inc. | Lithographic process for device fabrication using a multilayer mask which has been previously inspected |

| US5958629A (en) * | 1997-12-22 | 1999-09-28 | Intel Corporation | Using thin films as etch stop in EUV mask fabrication process |

| US6048652A (en) * | 1998-12-04 | 2000-04-11 | Advanced Micro Devices, Inc. | Backside polish EUV mask and method of manufacture |

| US6159643A (en) * | 1999-03-01 | 2000-12-12 | Advanced Micro Devices, Inc. | Extreme ultraviolet lithography reflective mask |

-

2000

- 2000-06-06 JP JP2001501941A patent/JP4959080B2/ja not_active Expired - Lifetime

- 2000-06-06 KR KR1020017014245A patent/KR100805360B1/ko not_active Expired - Lifetime

- 2000-06-06 US US09/587,836 patent/US6352803B1/en not_active Expired - Lifetime

- 2000-06-06 EP EP00941241A patent/EP1190276A2/en not_active Withdrawn

- 2000-06-06 AU AU55970/00A patent/AU5597000A/en not_active Abandoned

- 2000-06-06 WO PCT/US2000/015578 patent/WO2000075727A2/en not_active Ceased

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20200011859A (ko) * | 2018-07-25 | 2020-02-04 | 주식회사 야스 | 유리 마스크 |

| KR102146162B1 (ko) * | 2018-07-25 | 2020-08-19 | 주식회사 야스 | 유리 마스크 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20020010912A (ko) | 2002-02-06 |

| EP1190276A2 (en) | 2002-03-27 |

| JP2003501823A (ja) | 2003-01-14 |

| WO2000075727A2 (en) | 2000-12-14 |

| KR100805360B1 (ko) | 2008-02-20 |

| US6352803B1 (en) | 2002-03-05 |

| WO2000075727A3 (en) | 2001-05-17 |

| AU5597000A (en) | 2000-12-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4959080B2 (ja) | 反射マスク基板のコーティング | |

| US6737201B2 (en) | Substrate with multilayer film, reflection type mask blank for exposure, reflection type mask for exposure and production method thereof as well as production method of semiconductor device | |

| KR101388828B1 (ko) | 노광용 반사형 마스크 블랭크, 노광용 반사형 마스크,반도체 장치의 제조 방법, 및 다층 반사막 부착 기판 | |

| US9354510B2 (en) | EUV mask and method for forming the same | |

| CN100474105C (zh) | 金属镶嵌极端远紫外线光刻术用交替型相移光掩模及制造方法 | |

| US10578961B2 (en) | Mask blank substrate, multi-layer reflective film coated substrate, and mask blank | |

| US11360393B2 (en) | Mirror, in particular for a microlithographic projection exposure system | |

| US6048652A (en) | Backside polish EUV mask and method of manufacture | |

| JP4372178B2 (ja) | 光反射型マスクと光反射型マスクの作製方法及び半導体装置の製造方法 | |

| US20130011547A1 (en) | Optical Component Fabrication Using Coated Substrates | |

| US6368942B1 (en) | Method for fabricating an ultra-low expansion mask blank having a crystalline silicon layer | |

| JP2002222764A (ja) | 多層膜付き基板、露光用反射型マスクブランク、露光用反射型マスクおよびその製造方法、並びに半導体の製造方法 | |

| JP6186962B2 (ja) | Euvリソグラフィ用反射型マスクブランク、および、euvリソグラフィ用反射型マスク | |

| KR20140104375A (ko) | Euv 리소그래피용 반사형 마스크 블랭크 및 그 마스크 블랭크용 반사층 형성 기판 | |

| US20060292459A1 (en) | EUV reflection mask and method for producing it | |

| JP7404348B2 (ja) | マスクブランク用基板、多層反射膜付き基板、反射型マスクブランク、反射型マスク、透過型マスクブランク、透過型マスク、及び半導体装置の製造方法 | |

| US6593036B1 (en) | Structure for a reflection lithography mask and method for making same | |

| US9411222B2 (en) | Photo-masks for lithography | |

| Shoki et al. | Improvement of total quality on EUV mask blanks toward volume production | |

| JP7168573B2 (ja) | 多層反射膜付き基板、反射型マスクブランク、反射型マスク、及び半導体装置の製造方法 | |

| JP4769844B2 (ja) | コーティングされた基板を使用した光学コンポーネントの製造 | |

| Wasson et al. | Extreme ultraviolet mask fabrication with high inspection contrast TaSiN x absorber stack | |

| Mickan et al. | The first full-field EUV masks ready for printing | |

| KR20230129012A (ko) | 마스크 블랭크용 기판, 다층 반사막 부착 기판, 마스크블랭크, 전사용 마스크의 제조 방법, 및 반도체 디바이스의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070416 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070416 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100112 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100406 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100413 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100512 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100820 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101220 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20110207 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20110301 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20110311 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20110311 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20110415 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20111024 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20111027 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20111122 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20111128 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120321 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150330 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4959080 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |