JP4744591B2 - 遊技機 - Google Patents

遊技機 Download PDFInfo

- Publication number

- JP4744591B2 JP4744591B2 JP2008331880A JP2008331880A JP4744591B2 JP 4744591 B2 JP4744591 B2 JP 4744591B2 JP 2008331880 A JP2008331880 A JP 2008331880A JP 2008331880 A JP2008331880 A JP 2008331880A JP 4744591 B2 JP4744591 B2 JP 4744591B2

- Authority

- JP

- Japan

- Prior art keywords

- control device

- game

- power failure

- data

- discharge control

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Pinball Game Machines (AREA)

Description

前記遊技制御装置は、バックアップ電源によって停電時にも情報を保持可能とするメモリと、遊技の進行を制御する遊技用マイクロコンピュータと、前記排出制御データを出力するための出力ポートと、を備え、

前記排出制御装置は、バックアップ電源によって停電時にも情報を保持可能とするメモリと、前記遊技制御装置からの排出制御データに基づいて所定数の遊技媒体を排出させる制御を行う制御用マイクロコンピュータと、を備え、

前記遊技制御装置及び前記排出制御装置に電源を供給する電源供給装置が設けられ、

前記電源供給装置は、

24ボルトの交流電源電圧に基づいて、前記遊技制御装置及び前記排出制御装置で用いられる32ボルトの直流電源電圧を生成するDC32V生成回路と、前記遊技制御装置及び前記排出制御装置の各々にリセット信号を出力する第2の回路と、前記DC32V生成回路により生成された直流電源電圧に基づいて、32ボルトよりも低い直流電源電圧を生成する第3の回路と、を備えるとともに、

前記DC32V生成回路により生成された直流電源電圧が、前記第3の回路により生成される直流電源電圧よりも高く設定された所定の電圧まで低下すると、停電と判定して停電検出信号を出力し、その後、前記第2の回路からリセット信号を出力し、

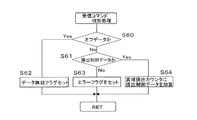

前記遊技用マイクロコンピュータ及び前記制御用マイクロコンピュータは、前記停電検出信号によって、停電が発生したことを示す停電フラグを前記メモリにそれぞれ保存して待機状態となった後に、電源が完全に断になるまで前記第2の回路からのリセット信号によってハード的に停止状態にロックされ、

前記電源供給装置から出力される前記停電検出信号は、前記遊技用マイクロコンピュータ及び前記制御用マイクロコンピュータの双方へ同時に出力され、且つ該停電検出信号の出力後に出力される前記第2の回路からのリセット信号も前記遊技用マイクロコンピュータ及び前記制御用マイクロコンピュータの双方へ同時に出力される一方で、

当該遊技機の停電復旧時には、前記第2の回路からのリセット信号がアクティブな状態となって前記出力ポートにオフデータが設定された後に、前記制御用マイクロコンピュータが制御動作を開始し、次いで、前記遊技用マイクロコンピュータが前記出力ポートに前記排出制御データを設定するようにした。

認識することができる。

なお、図9(b)においてスタート信号STTが立ち下がった後で停電が発生した場合には、停電復帰後に遊技制御装置210からのスタート信号STTが再度立ち上げられることはないので、排出制御装置220側では排出制御データD0〜D7が変化した後に直ちに中断した処理を再開しても何ら問題はない。

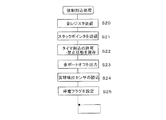

(1)遊技領域における遊技の進行を制御するための遊技制御装置と、排出制御データに基づいて遊技媒体を排出する球排出装置を制御する排出制御装置とを備え、前記遊技制御装置および排出制御装置はそれぞれ制御上使用しているデータを停電発生時に保存可能に構成されているとともに、前記遊技制御装置から排出制御装置へ単一方向に通信可能に構成された遊技機であって、前記遊技制御装置は、前記排出制御装置へ排出制御データを送信中に停電発生を検出した場合には、実行している送信処理を中断し、出力している排出制御データ及び中断時の制御状態を保存する遊技制御側停電処理手段と、停電復帰時に、保存していた制御状態を復元するとともに保存していた排出制御データの出力を行なう遊技制御側処理再開手段とを備え、前記排出制御装置は、前記遊技制御装置から排出制御データを受信中に停電発生を検出した場合には、実行している受信処理を中断し、中断時の制御状態または中断時の制御状態と受信データを保存する排出制御側停電処理手段と、停電復帰時に、保存していた制御状態を復元した後、保存していた制御状態に応じて停電復帰後に入力される排出制御データまたは保存していた排出制御データに基づいて、停電発生時に中断した箇所から処理を再開する排出制御側処理再開手段とを備えたことを特徴とする遊技機。

(2)前記遊技制御装置は、電源が復旧してから制御を開始する停電復帰までの準備期間に亘って、前記排出制御装置との間の通信線が接続された出力ポートを準備期間論理値に固定する出力固定手段を備え、前記遊技制御側停電処理手段は、排出制御データを保存した後に前記出力ポートに前記準備期間論理値と同一のオフデータを設定し、前記遊技制御側処理再開手段は、排出制御データを送信中に停電が発生した場合には中断時の送信状態にかかわらず保存していた排出制御データを前記出力ポートに設定してから中断した送信処理を再開し、前記排出制御側処理再開手段は、停電復帰時に、前記通信線より入力される排出制御データがオフデータ以外になったことを条件として中断した受信処理を再開することを特徴とする(1)に記載の遊技機。

(3)前記排出制御側処理再開手段は、停電復帰時に、前記通信線より入力される排出制御データが所定時間以上オフデータである場合には、保存していた排出制御データを無効として中断した受信処理を再開することを特徴とする(2)に記載の遊技機。

(4)前記出力固定手段が前記出力ポートを準備期間論理値に固定する前記準備期間は、前記排出制御装置が電源復旧から制御を開始する停電復帰までに要する期間よりも長くなるように設定されていることを特徴とする(2)又は(3)に記載の遊技機。

(5)前記遊技制御装置は、前記遊技制御側停電処理手段および出力固定手段の能動中以外は、排出制御データとしてオフデータ以外のデータを前記出力ポートより出力することを特徴とする(2)から(4)のいずれかに記載の遊技機。

(1)に記載の発明では、遊技制御装置と排出制御装置は、各々停電発生を検出した場合に実行している処理を中断して中断時の制御状態を保存するため、停電復帰時に停電発生時に中断した処理を正確に再開することができる。しかも、遊技制御装置と排出制御装置は、各々通信中に停電発生した場合には送信中または受信した排出制御データも保存するため、停電復帰後に送信処理や受信処理をやり直す必要がなく直ちに中断した箇所から処理を再開することができる。その結果、送受信処理のプログラムが簡単になるとともに、停電復帰後の制御再開までの時間が短縮され、例えば持ち球が少ない状態で大当りが発生したときに停電が発生したような場合にも、停電復帰後速やかに賞球が排出されるようになり、遊技店と遊技者との間のトラブルの発生を回避することができる。

(2)に記載の発明では、遊技制御装置は電源復旧してから制御を開始するまで通信線が接続された出力ポートを準備期間論理値に固定し、制御を開始すると保存されていた排出制御データを元の出力ポートに設定するため、排出制御装置は、遊技制御装置に接続された通信線のデータがオフデータからオフデータ以外のデータに変わったことを検出することで遊技制御装置が制御を再開したことを確認することができ、これによって遊技制御装置と排出制御装置との間の通信が遊技制御装置から排出制御装置への単一方向通信であっても排出制御装置は停電復帰時に遊技制御装置が制御を再開したことをいち早く知ることができ、排出制御の開始を早めることができる。しかも、遊技制御装置と排出制御装置との間の通信が遊技制御装置から排出制御装置への単一方向通信であるため、排出制御装置に対して直接不正を行なって不当に賞球を排出させることが困難であるとともに、遊技制御装置からの指令によって動作する排出制御装置の側から遊技制御装置に対してアクセスが行なえないので、遊技制御装置に対する不正も行ないにくくなる。

(3)に記載の発明では、排出制御側処理再開手段は、停電復帰時に、前記通信線より入力される排出制御データが所定時間以上オフデータである場合には、保存していた排出制御データを無効として中断した受信処理を再開するように構成する。これにより、何らかの原因で遊技制御装置側の電源復帰処理が遅れても排出制御装置は速やかに制御を再開することができる。また、好ましくは、前記出力固定手段が出力ポートをオフデータに固定する前記準備期間(図3のT2+T4)は、前記排出制御装置が電源復旧から制御を開始する停電復帰までに要する期間(図3のT2+T3)よりも長くなるように設定する。これによって、停電復旧時に排出制御装置が遊技制御装置よりも先に停電復帰して通信線すなわち遊技制御装置の出力ポートのデータがオフデータからオフデータ以外のデータに変わるのを確実に検出することができ、システムの信頼性が向上する。

(4)に記載の発明では、前記遊技制御装置は、前記遊技制御側停電処理手段および出力固定手段の能動中以外は、排出制御データとしてオフデータ以外のデータを前記出力ポートより出力するようにする。これによって、停電復帰すると通信線すなわち遊技制御装置の出力ポートのデータが速やかにオフデータからオフデータ以外のデータに変わるようになり、これを受けて排出制御装置が停電発生時に中断した処理を再開するので、停電復旧時のシステムの立ち上がりが早くなる。

(5)に記載の発明では、前記排出制御データは0又は1の2値データで構成され、前記オフデータは全てが0又は全てが1のデータであり、前記遊技制御装置は、電源立ち上がり時に前記出力ポートに前記オフデータ以外のデータを設定するようにする。これによって、遊技制御装置は出力ポートのデータをオフデータからオフデータ以外のデータに変える処理を簡単に行なえるとともに、排出制御装置側においても通信線のデータがオフデータからオフデータ以外のデータに変化したことを容易かつ正確に判定することができる。

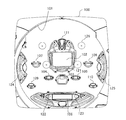

101 ガイドレール

102 特別図柄表示装置

103 特図始動入賞口

104,105 普図始動入賞口

106 変動入賞装置

107,108,109,110,111 一般入賞口

121 特図始動入賞記憶表示器

122 普通図柄表示器

123 普図始動入賞記憶表示器

124,125 装飾ランプ

126 打球方向変換部材

210 遊技制御装置

211 マイクロコンピュータ

212 リセット信号第1遅延回路

213 クロック生成回路

214 入出力インターフェース

220 排出制御装置

221 マイクロコンピュータ

222 リセット信号第2遅延回路

223 クロック生成回路

224 入出力インターフェース

230 表示制御装置

240 装飾制御装置

250 音制御装置

260 電源供給装置

261,262,263 DC生成回路

264 VBB生成回路(バックアップ電源)

265 停電検出回路

270 発射制御装置

301 オーバーフロー検出器

302 半端球検出器

303 金枠開放検出器

311 データ出力端子

312 試験用出力端子

313 普通電動役物表示駆動信号出力端子

314 アタッカーソレノイド

315 普通電動役物駆動ソレノイド

400 球排出装置

401,402 賞球検出センサ

403,404 貸し球検出器

411 排出モータ

412 ストッパソレノイド

413 流路切換ソレノイド

500 カード式球貸しユニット

Claims (1)

- 遊技領域における遊技の進行を制御するための遊技制御装置と、該遊技制御装置から送信される排出制御データに基づいて、遊技媒体を排出する制御を行なう排出制御装置と、を備えた遊技機であって、

前記遊技制御装置は、バックアップ電源によって停電時にも情報を保持可能とするメモリと、遊技の進行を制御する遊技用マイクロコンピュータと、前記排出制御データを出力するための出力ポートと、を備え、

前記排出制御装置は、バックアップ電源によって停電時にも情報を保持可能とするメモリと、前記遊技制御装置からの排出制御データに基づいて所定数の遊技媒体を排出させる制御を行う制御用マイクロコンピュータと、を備え、

前記遊技制御装置及び前記排出制御装置に電源を供給する電源供給装置が設けられ、

前記電源供給装置は、

24ボルトの交流電源電圧に基づいて、前記遊技制御装置及び前記排出制御装置で用いられる32ボルトの直流電源電圧を生成するDC32V生成回路と、

前記遊技制御装置及び前記排出制御装置の各々にリセット信号を出力する第2の回路と、

前記DC32V生成回路により生成された直流電源電圧に基づいて、32ボルトよりも低い直流電源電圧を生成する第3の回路と、

を備えるとともに、

前記DC32V生成回路により生成された直流電源電圧が、前記第3の回路により生成される直流電源電圧よりも高く設定された所定の電圧まで低下すると、停電と判定して停電検出信号を出力し、その後、前記第2の回路からリセット信号を出力し、

前記遊技用マイクロコンピュータ及び前記制御用マイクロコンピュータは、前記停電検出信号によって、停電が発生したことを示す停電フラグを前記メモリにそれぞれ保存して待機状態となった後に、電源が完全に断になるまで前記第2の回路からのリセット信号によってハード的に停止状態にロックされ、

前記電源供給装置から出力される前記停電検出信号は、前記遊技用マイクロコンピュータ及び前記制御用マイクロコンピュータの双方へ同時に出力され、且つ該停電検出信号の出力後に出力される前記第2の回路からのリセット信号も前記遊技用マイクロコンピュータ及び前記制御用マイクロコンピュータの双方へ同時に出力される一方で、

当該遊技機の停電復旧時には、前記第2の回路からのリセット信号がアクティブな状態となって前記出力ポートにオフデータが設定された後に、前記制御用マイクロコンピュータが制御動作を開始し、次いで、前記遊技用マイクロコンピュータが前記出力ポートに前記排出制御データを設定することを特徴とする遊技機。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008331880A JP4744591B2 (ja) | 2008-12-26 | 2008-12-26 | 遊技機 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008331880A JP4744591B2 (ja) | 2008-12-26 | 2008-12-26 | 遊技機 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008229488A Division JP4744574B2 (ja) | 2008-09-08 | 2008-09-08 | 遊技機 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009061346A JP2009061346A (ja) | 2009-03-26 |

| JP4744591B2 true JP4744591B2 (ja) | 2011-08-10 |

Family

ID=40556451

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008331880A Expired - Fee Related JP4744591B2 (ja) | 2008-12-26 | 2008-12-26 | 遊技機 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4744591B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10453299B2 (en) | 2009-12-23 | 2019-10-22 | Aristocrat Technologies Australia Pty Limited | Method of enabling restoration of games and a method of restoring games |

| AU2011202309A1 (en) | 2010-05-27 | 2011-12-15 | Aristocrat Technologies Australia Pty Limited | A gaming machine and a method of gaming |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2954384B2 (ja) * | 1991-04-26 | 1999-09-27 | 株式会社ソフィア | 遊技機 |

| JPH056310A (ja) * | 1991-06-27 | 1993-01-14 | Toshiba Corp | 電子装置 |

| JPH05317505A (ja) * | 1992-05-15 | 1993-12-03 | Ace Denken:Kk | 停電時データ処理装置 |

| JPH0612153A (ja) * | 1992-06-25 | 1994-01-21 | Matsushita Electric Works Ltd | プログラマブルコントローラ |

| JP3343998B2 (ja) * | 1993-05-19 | 2002-11-11 | 株式会社三洋物産 | 制御装置 |

| JP3251390B2 (ja) * | 1993-07-21 | 2002-01-28 | 株式会社ソフィア | 液晶表示装置を備えた遊技機 |

| JPH07248858A (ja) * | 1994-03-11 | 1995-09-26 | Tec Corp | 停電処理機能を有する電子機器 |

| JP3756532B2 (ja) * | 1994-04-20 | 2006-03-15 | 株式会社ニフコ | 画像表示装置 |

| JPH09173569A (ja) * | 1995-12-26 | 1997-07-08 | Sophia Co Ltd | 遊技機 |

| JPH09220318A (ja) * | 1996-02-20 | 1997-08-26 | Daiichi Shokai Co Ltd | パチンコ機におけるノイズ除去装置 |

| JP2650024B2 (ja) * | 1996-03-11 | 1997-09-03 | 株式会社平和 | パチンコ機 |

| JP2741504B2 (ja) * | 1996-09-24 | 1998-04-22 | 日本パルスモーター株式会社 | パチンコ遊技機の発射装置 |

| JPH10113446A (ja) * | 1996-10-11 | 1998-05-06 | Sankyo Kk | 遊技用装置 |

| JPH10155981A (ja) * | 1996-11-26 | 1998-06-16 | Sophia Co Ltd | 弾球遊技機及び弾球遊技機の賞球排出数制御方法 |

| JP3885367B2 (ja) * | 1997-06-24 | 2007-02-21 | 株式会社三洋物産 | 乱数生成回路、および、その乱数生成回路を備えた遊技機 |

| JPH1147408A (ja) * | 1997-08-08 | 1999-02-23 | Sankyo Kk | 遊技機 |

| JPH11104312A (ja) * | 1997-09-30 | 1999-04-20 | Sankyo Kk | 遊技機 |

| JPH11299968A (ja) * | 1998-04-22 | 1999-11-02 | Sansei | パチンコ機 |

| JP3444485B2 (ja) * | 1999-10-22 | 2003-09-08 | 株式会社高尾 | 遊技機 |

| JP4118480B2 (ja) * | 1999-12-01 | 2008-07-16 | 株式会社三共 | 遊技機 |

-

2008

- 2008-12-26 JP JP2008331880A patent/JP4744591B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009061346A (ja) | 2009-03-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5250804B2 (ja) | 遊技機 | |

| JP4264593B2 (ja) | 遊技機 | |

| JP4656110B2 (ja) | 遊技機 | |

| JP4431819B2 (ja) | 遊技機 | |

| JP4249358B2 (ja) | 遊技機 | |

| JP2010158575A (ja) | 遊技機 | |

| JP4191351B2 (ja) | 遊技機 | |

| JP4744591B2 (ja) | 遊技機 | |

| JP2009000241A (ja) | 遊技機 | |

| JP4023767B2 (ja) | 遊技機 | |

| JP2009061345A (ja) | 遊技機 | |

| JP2009061347A (ja) | 遊技機 | |

| JP2009061348A (ja) | 遊技機 | |

| JP2009061344A (ja) | 遊技機 | |

| JP4948622B2 (ja) | 遊技機 | |

| JP4877860B2 (ja) | 遊技機 | |

| JP4632375B2 (ja) | 遊技機 | |

| JP4744575B2 (ja) | 遊技機 | |

| JP4744574B2 (ja) | 遊技機 | |

| JP4877859B2 (ja) | 遊技機 | |

| JP4679545B2 (ja) | 遊技機 | |

| JP2009006167A (ja) | 遊技機 | |

| JP2010162390A (ja) | 遊技機 | |

| JP2010162391A (ja) | 遊技機 | |

| JP2002045478A (ja) | 遊技機 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081226 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100713 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100903 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110104 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20110218 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110304 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110510 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110510 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140520 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4744591 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140520 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |